# Switch-Mode Single Cell Li-Ion Charger with USB-OTG

### **General Description**

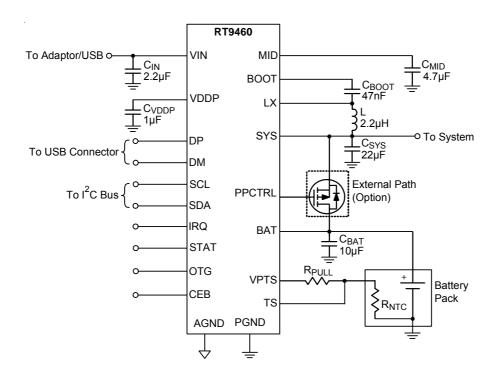

The RT9460 is a switch-mode single cell Li-lon/Li-Polymer battery charger for portable applications. It integrates a synchronous PWM controller, power MOSFETs, input current sensing and regulation, and high accuracy voltage regulation and charge termination circuits. Besides, the charging current is regulated through the integrated sensing resistors. The RT9460 also features USB On-The-Go (OTG) support.

The RT9460 optimizes the charging task by using a control algorithm to vary the charge rate via different modes, including pre-charge mode, fast charge mode, and constant voltage mode. The key charge parameters are programmable via the I<sup>2</sup>C interface. The RT9460 resumes the charge cycle whenever the battery voltage falls below an internal recharge threshold, and automatically enters sleep mode when the input power supply is removed.

Other features include under-voltage protection, overvoltage protection, thermal regulation and reverse leakage protection.

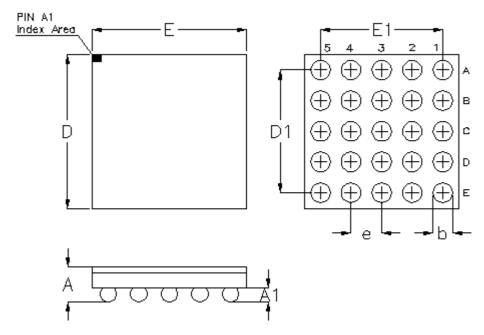

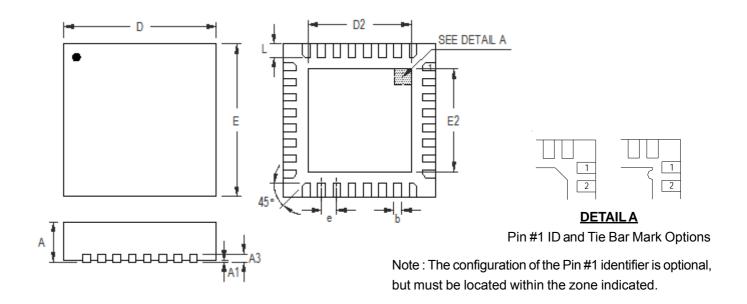

The RT9460 is available in the small WL-CSP-25B 2.52x2.52 and WQFN-32L 4x4 packages.

### **Applications**

- · Cellular Telephones

- Personal Information Appliances

- Tablet PC, Power Bank

- Portable Instruments

#### **Features**

- High Accuracy Voltage/Current Regulation

- Average Input Current Regulation (AICR): 0.1/0.15/

0.5/ to 3A per 0.1A

- Minimum Input Voltage Regulation

- For 5V Adaptor: 4V/4.25V/4.5V/4.75V

- ▶ For 9V Adaptor: 7V/7.5V/8V/8.5V

- ▶ For 12V Adaptor : 9.5V/10V/10.5V/11V

- Charge Current Regulation Accuracy: ±5%

- Charge Voltage Regulation Accuracy : ± 1% ( 0 to 85°C)

- Integrated Power MOSFETS for up to 3.125A Charge Rate

- Support USB Charging Detection

- Battery Temperature Sensing

- Synchronous 0.75/1.5MHz Fixed Frequency PWM Controller with up to 95% Duty Cycle

- Reverse Leakage Protection to Prevent Battery Drainage

- Thermal Regulation and Protection

- Over Temperature Protection

- Input Over Voltage Protection

- IRQ Output for Communication with I<sup>2</sup>C

- Automatic Charging

- RoHS Compliant and Halogen Free

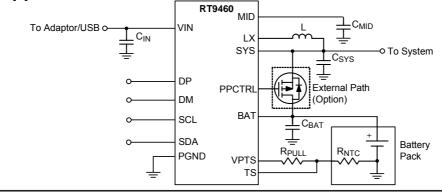

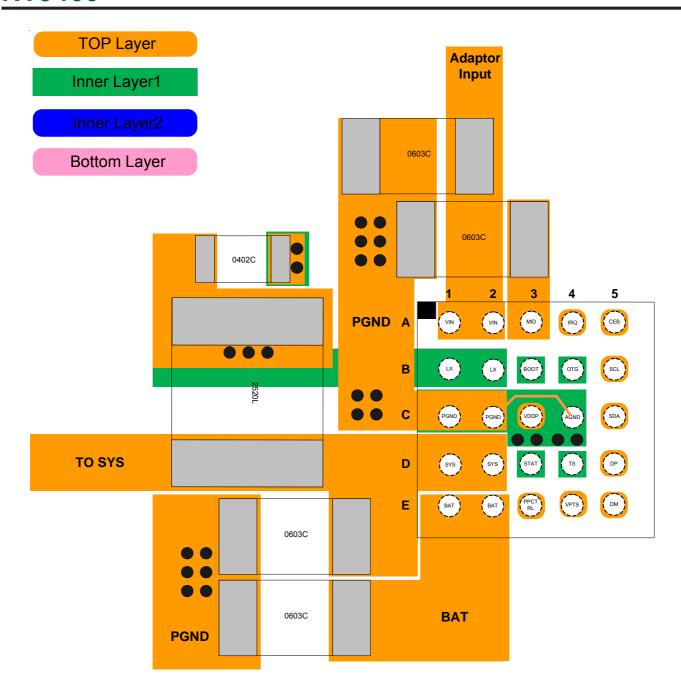

**Simplified Application Circuit**

Copyright@2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9460-03 December 2016

## **Ordering Information**

Package Type

WSC: WL-CSP-25B 2.52x2.52 (BSC)

QW: WQFN-32L 4x4 (W-Type)

Lead Plating System

G: Green (Halogen Free and Pb Free)

(For WQFN-32L 4x4 Only)

#### Note:

#### Richtek products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Marking Information**

#### RT9460WSC

0E : Product Code YMDNN : Date Code

#### RT9460GQW

4F= : Product Code YMDNN : Date Code

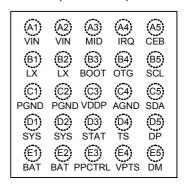

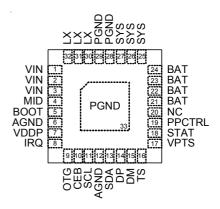

### **Pin Configuration**

#### (TOP VIEW)

WL-CSP-25B 2.52x2.52 (BSC)

WQFN-32L 4x4

# **Functional Pin Description**

| Pin N                         | lo.                 |          |                                                                                                              |  |  |  |  |

|-------------------------------|---------------------|----------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| WL-CSP-25B<br>2.52x2.52 (BSC) | WQFN-32L<br>4x4     | Pin Name | Pin Description                                                                                              |  |  |  |  |

| A1, A2                        | 1, 2, 3             | VIN      | Power input.                                                                                                 |  |  |  |  |

| A3                            | 4                   | MID      | Connection point between reverse blocking MOSFET and high-side switching MOSFET.                             |  |  |  |  |

| A4                            | 8                   | IRQ      | IRQ output node.                                                                                             |  |  |  |  |

| A5                            | 10                  | CEB      | Enable control input. Low active.                                                                            |  |  |  |  |

| B1, B2                        | 30, 31, 32          | LX       | Switch node. Connect to an external inductor.                                                                |  |  |  |  |

| В3                            | 5                   | воот     | Bootstrap supply for high-side MOSFET. Connect a capacitor between BOOT and LX.                              |  |  |  |  |

| B4                            | 9                   | OTG      | Setting input pin OTG boost mode.                                                                            |  |  |  |  |

| B5                            | 11                  | SCL      | Clock input for I <sup>2</sup> C. Open-drain output. Connect a pull-up resistor.                             |  |  |  |  |

| C1, C2                        | 28, 29              | PGND     | Power ground for switching charger.                                                                          |  |  |  |  |

| C3                            | 7                   | VDDP     | Internal power for power stage.                                                                              |  |  |  |  |

| C4                            | 6, 12               | AGND     | Analog ground.                                                                                               |  |  |  |  |

| C5                            | 13                  | SDA      | Data input for I <sup>2</sup> C. Open drain output. Connect a pull-up Resistor.                              |  |  |  |  |

| D1, D2                        | 25, 26, 27          | SYS      | System voltage regulator node.                                                                               |  |  |  |  |

| D3                            | 18                  | STAT     | Charge status indicator (open drain).                                                                        |  |  |  |  |

| D4                            | 16                  | TS       | Battery temperature detection pin.                                                                           |  |  |  |  |

| D5                            | 14                  | DP       | USB charger type detection pin.                                                                              |  |  |  |  |

| E1, E2                        | 21, 22, 23, 24      | BAT      | Charging current output node. Battery charging voltage regulation feedback pin with power path.              |  |  |  |  |

| E3                            | 19                  | PPCTRL   | Power path control pin (connect to external P-MOSFET gate).                                                  |  |  |  |  |

| E4                            | 17                  | VPTS     | Supply voltage for battery temperature detection.                                                            |  |  |  |  |

| E5                            | 15                  | DM       | USB charger type detection pin.                                                                              |  |  |  |  |

|                               | 20                  | NC       | No internal connection.                                                                                      |  |  |  |  |

|                               | 33<br>(Exposed Pad) | PGND     | Ground. The exposed pad must be soldered to a large PCB and connected to PGND for maximum power dissipation. |  |  |  |  |

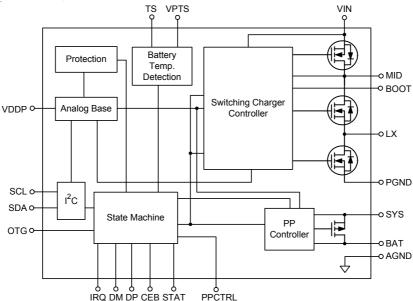

### **Functional Block Diagram**

### **Operation**

The RT9460 is an integrated single cell Li-ion battery switching charger with power path controller.

#### **Base Circuits**

Base circuits provide the internal power, VDDP and reference voltage and bias current.

#### **Protection Circuits**

The protection circuits include the VINOVP, VINUVLO, BATOVP and OTP circuits. The protection circuits turn off the charging when the input power or die temperature is in abnormal level.

# Buck Regulator for charging and Boost Regulator as OTG

The multi-loop controller controls the operation of charging process and current supply to the system. It also controls the circuits as a Boost converter for OTG applications.

#### **Battery Detection**

The RT9460 is capable of doing the battery absence detection. The detection protects the charger when battery is removed accidentally.

#### **Adaptor Detection**

If the poor input power source is connected to RT9460, the operation is shut down by the adaptor detection.

#### **Power Path Management and Control**

Once the battery voltage increase to a defined system minimum regulation voltage, the internal path between SYS and BAT will be fully turned on (Cool PPM operation). That is, a better charging efficiency can be derived. When end of charge occurs, the charing stops and the internal path will be off.

#### **USB Charger Detection**

The RT9460 detects and distinguishes SONY, APPLE NIKON and USB Charger (Standard Charger Port, Charging Downstream Port and Dedicated Charger Port) via DP and DM pins.

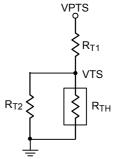

#### **TS Detection**

The RT9460 detects the temperature of the battery pack via TS and VPTS pins. The VPTS pin provides a constant voltage source used to drive the voltage divider composed of a pulled-high resister and a NTC resister. The RT9460 reports the sensing results via IRQ and status bits for COLD, COOL, WARM and HOT.

#### I<sup>2</sup>C Controller

The key parameters of charging and OTG are programmable through  $I^2C$  commands.

# Absolute Maximum Ratings (Note 1)

| • Supply Input Voltage, VIN                                                 | 0.3V to 28V      |

|-----------------------------------------------------------------------------|------------------|

| • MID, BOOT                                                                 | 0.3V to 28V      |

| • LX                                                                        | 0.3V to 20V      |

| • MID – VIN, BOOT – LX                                                      | 0.3V to 6V       |

| • Other Pins                                                                | 0.3V to 6V       |

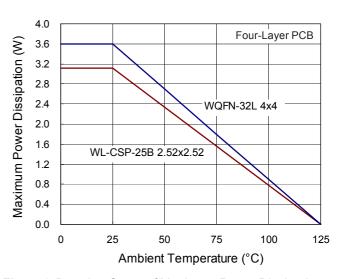

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                  |

| WL-CSP-25B 2.52x2.52 (BSC)                                                  | - 3.11W          |

| WQFN-32L 4x4                                                                | - 3.59W          |

| Package Thermal Resistance (Note 2)                                         |                  |

| WL-CSP-25B 2.52x2.52 (BSC), $\theta_{JA}$                                   | - 32.1°C/W       |

| WQFN-32L 4x4, $\theta_{JA}$                                                 | - 27.8°C/W       |

| WQFN-32L 4x4, $\theta_{JC}$                                                 | - 7°C/W          |

| • Lead Temperature (Soldering, 10 sec.)                                     |                  |

| • Junction Temperature                                                      |                  |

| Storage Temperature Range                                                   | - −65°C to 150°C |

| ESD Susceptibility (Note 3)                                                 |                  |

| HBM (Human Body Model)                                                      | - 2kV            |

| MM (Machine Model)                                                          | - 200V           |

|                                                                             |                  |

| <b>Recommended Operating Conditions</b> (Note 4)                            |                  |

#### **Electrical Characteristics**

$(V_{IN} = 5V, V_{BAT} = 4.2V, L = 2.2\mu H, C_{IN} = 2.2\mu F, C_{BATS} = 10\mu F, T_A = 25^{\circ}C$ , unless otherwise specified)

| , , , , , , , , , , , , , , , , , , , |                      | · · · · · · · · · · · · · · · · · · · | · · · | 1   |     |      |

|---------------------------------------|----------------------|---------------------------------------|-------|-----|-----|------|

| Parameter                             | Symbol               | Test Conditions                       | Min   | Тур | Max | Unit |

| Protection                            |                      |                                       |       |     |     |      |

| V <sub>IN</sub> OVP Threshold Voltage |                      |                                       | 15    | 16  | 17  | V    |

| V <sub>IN</sub> OVP Hysteresis        |                      |                                       |       | 200 |     | mV   |

| Battery OVP                           |                      |                                       | 110   | 117 | 124 | %    |

| Battery OVP Hysteresis                |                      |                                       |       | 10  |     | %    |

| Over-Temperature Protection           | OTP                  |                                       |       | 165 |     | °C   |

| OTP Hysteresis                        |                      |                                       |       | 10  |     | °C   |

| Thermal Regulation Threshold          |                      | Charge Current Begins To Reduce       |       | 120 |     | °C   |

| System UVP Threshold Voltage          | V <sub>SYS_UVP</sub> |                                       |       | 2.4 |     | ٧    |

| Parameter                                                      | Symbol               | Test Conditions                                                          | Min  | Тур  | Max   | Unit |

|----------------------------------------------------------------|----------------------|--------------------------------------------------------------------------|------|------|-------|------|

| Sleep Mode Comparator                                          | 1                    |                                                                          |      | l    |       |      |

| Sleep Mode Entry Threshold<br>VIN - VBATS                      | V <sub>SLP</sub>     | 2.5V < V <sub>BATx</sub> < V <sub>BATREG</sub> , V <sub>IN</sub> Falling | 0    | 0.04 | 0.1   | V    |

| Sleep Mode Exit Hysteresis V <sub>IN</sub> – V <sub>BATS</sub> | V <sub>SLPEXIT</sub> | 2.5V < V <sub>BATx</sub> < V <sub>BATREG</sub>                           | 40   | 100  | 200   | mV   |

| Sleep Mode Deglitch Time                                       | T <sub>SLP</sub>     | V <sub>IN</sub> Rising Above V <sub>SLP</sub> + V <sub>SLPEXIT</sub>     |      | 128  |       | ms   |

| Under-Voltage Lockout The                                      | reshold              |                                                                          |      |      |       |      |

| IC Active Threshold Voltage                                    | V <sub>UVLO</sub>    | V <sub>IN</sub> Rising                                                   | 3.05 | 3.3  | 3.55  | V    |

| IC Active Hysteresis                                           | ΔVυνιο               | V <sub>IN</sub> Falling From UVLO                                        |      | 150  |       | mV   |

| Input Currents                                                 |                      |                                                                          |      |      |       |      |

|                                                                |                      | PWM switching, I <sub>CHG</sub> = I <sub>BAT</sub> = 0mA                 |      | 10   |       | mA   |

| VIN Supply Current                                             | IQ                   | PWM Is Not Switching.<br>I <sub>CHG</sub> = I <sub>BAT</sub> = 0mA       |      |      | 5     | mA   |

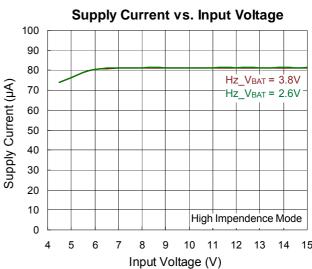

|                                                                |                      | High Impendence Mode                                                     |      |      | 150   | μΑ   |

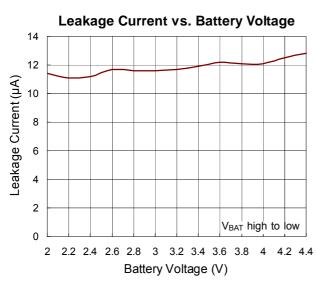

| Leakage Current from Battery                                   | Іват                 | V <sub>IN</sub> = 0V, charger off.                                       |      |      | 25    | μΑ   |

| Input Power Regulation                                         |                      |                                                                          |      |      |       |      |

| Input Voltage Regulation                                       | V <sub>MI</sub> VR   | I <sup>2</sup> C Programmable refer to Reg0x21[3:0]                      | 4    |      | 11    | ٧    |

| VMIVR Accuracy                                                 |                      |                                                                          | -5   |      | 5     | %    |

|                                                                |                      | USB Charge Mode, I <sub>AICR</sub> = 100mA                               | 80   |      | 100   |      |

| Average Input Current Regulation Accuracy                      | IAICR                | USB Charge Mode, I <sub>AICR</sub> = 500mA                               | 400  |      | 500   | mA   |

| Thegulation Accuracy                                           |                      | USB Charge Mode, I <sub>AICR</sub> = 1A                                  | 800  |      | 1000  |      |

| Battery Voltage Regulation                                     |                      |                                                                          |      |      |       |      |

| Battery Voltage Regulation                                     | Voreg                | I <sup>2</sup> C Programmable Per 20mV.                                  | 3.5  |      | 4.62  | V    |

| VBATREG Accuracy                                               |                      | 0 to 85°C                                                                | -1   |      | 1     | %    |

| Re-Charge Threshold                                            | VRECH                | VBATx Falling, Below VBATREG                                             |      | 125  |       | mV   |

| Re-Charge Deglitch                                             | T <sub>RECH</sub>    |                                                                          |      | 128  |       | ms   |

| System Minimum Regulation                                      | on Voltage           |                                                                          | •    |      |       |      |

| System Minimum<br>Regulation Voltage                           | V <sub>SYS</sub>     | I <sup>2</sup> C Programmable Per 0.1V                                   | 3.5  |      | 3.8   | V    |

| Charging Current Regulati                                      | on                   |                                                                          |      |      |       |      |

| Output Charging Current                                        | Ichg                 | I <sup>2</sup> C Programmable Per 0.125A                                 | 1.25 |      | 3.125 | Α    |

| ICHG Accuracy                                                  |                      |                                                                          | -5   |      | 5     | %    |

| Pre-Charge Threshold                                           | V <sub>PREC</sub>    | I <sup>2</sup> C Programmable Per 0.2V                                   | 2    |      | 3     | V    |

| VPREC Accuracy                                                 |                      |                                                                          | -5   |      | 5     | %    |

| Pre-Charge Current                                             | I <sub>PREC</sub>    | I <sup>2</sup> C Programmable Per 50mA                                   | 100  |      | 850   | mA   |

| IPREC Accuracy                                                 |                      |                                                                          | -30  |      | 30    | %    |

| Parameter                             |             | Symbol           | Test Conditions                                                           | Min  | Тур  | Max | Unit |

|---------------------------------------|-------------|------------------|---------------------------------------------------------------------------|------|------|-----|------|

| Charge Termination                    | on Detectio | n                |                                                                           |      | •    |     |      |

| End of Charge Cur                     | rent        | I <sub>EOC</sub> | I <sup>2</sup> C Programmable Per 50mA                                    | 100  |      | 450 | mA   |

| Fixed IEOC                            |             |                  | As I <sub>AICR</sub> = 100mA                                              |      | 50   |     | mA   |

| IEOC Accuracy                         |             |                  |                                                                           | -100 |      | 100 | mA   |

| Deglitch Time for E                   | OC.         | T <sub>EOC</sub> | I <sub>CHG</sub> < I <sub>EOC</sub> , V <sub>BAT</sub> > V <sub>REC</sub> |      | 2    |     | ms   |

| PWM                                   |             |                  |                                                                           | ·    |      |     |      |

| High-Side On-Resi                     | stance      |                  | From VIN to LX,<br>Exclude I <sub>AICR</sub> = 100mA                      |      | 90   | 150 | mΩ   |

| Low-Side On-Resis                     | stance      |                  | From LX to PGND                                                           |      | 60   | 100 | mΩ   |

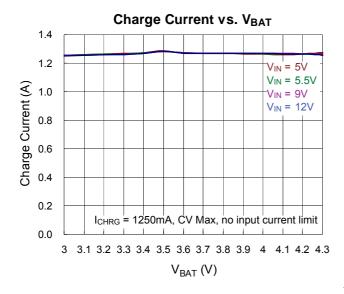

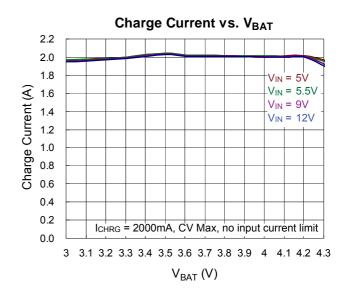

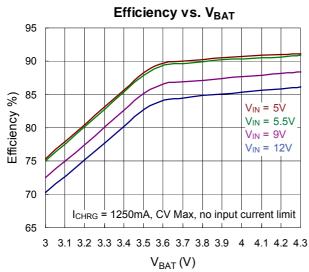

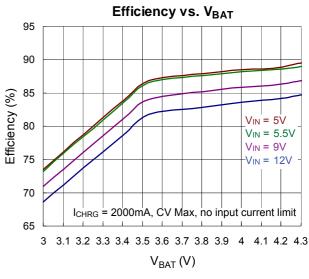

| Charging Efficiency                   | /           |                  | $V_{BATx}$ = 4V, and $I_{CHG}$ = 2A,                                      |      | 85   |     | %    |

| Oscillator Frequence                  | су          | osc              | I <sup>2</sup> C Programmable 0.75/1.5 MHz                                |      | 1.5  |     | MHz  |

| Frequency Accurac                     | СУ          |                  |                                                                           | -10  |      | 10  | %    |

| Maximum Duty Cyo                      | cle         |                  | At Minimum Voltage Input                                                  |      | 95   |     | %    |

| Minimum Duty Cyc                      | le          |                  |                                                                           | 0    |      |     | %    |

| Peak OCP as Char                      | rger Mode   | ICHGOCP          |                                                                           |      | 4.5  | 1   | Α    |

| Power Path On-Re                      | sistance    |                  | From SYS to VBAT                                                          |      | 35   | 60  | mΩ   |

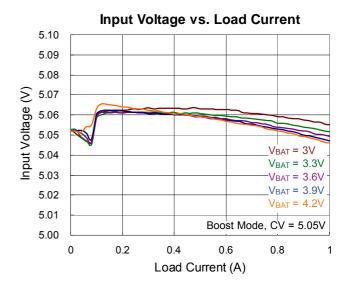

| <b>Boost Mode Oper</b>                | ation       |                  |                                                                           |      |      |     |      |

| Output Voltage Lev                    | ⁄el         | V <sub>OTG</sub> | To VIN                                                                    |      | 5.05 |     | V    |

| Output Voltage Acc                    | curacy      |                  |                                                                           | -3   |      | 3   | %    |

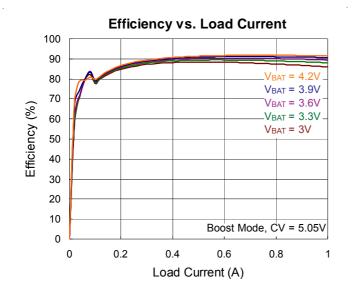

| Efficiency                            |             |                  | $V_{BATx}$ = 4V, and $I_{IN}$ = 0.8A,                                     |      | 85   |     | %    |

| MAX Output Curre                      | nt          |                  | I <sup>2</sup> C Programmable, 0.5A/1A                                    | 1    |      |     | Α    |

| Peak Over-Current                     | Protection  |                  |                                                                           |      | 4.5  |     | Α    |

| VIN OVP as OTG I                      | Boost       |                  |                                                                           |      | 6    |     | V    |

| VIN OVP Hysteres                      |             |                  |                                                                           |      | 250  | -   | mV   |

| Minimum Battery V<br>Boost            | oltage for  | VBATMIN          | As Boost Start-Up                                                         |      | 2.9  |     | V    |

| Minimum Battery Voltage<br>Hysteresis |             |                  |                                                                           |      | 400  |     | mV   |

| I <sup>2</sup> C Characteristic       | s           |                  | <del></del>                                                               |      |      |     |      |

| Output Low Voltage                    | е           | V <sub>OL</sub>  | I <sub>DS</sub> = 10mA                                                    |      |      | 0.4 | V    |

| SCL, SDA Input Logic-High             |             | VIH              |                                                                           | 1.3  |      |     | \/   |

| Threshold Voltage                     | Logic-Low   | VIL              |                                                                           |      |      | 0.4 | V    |

| SCL Clock                             |             |                  |                                                                           |      |      | 400 | kHz  |

| Paramete                       | r          | Symbol                | Test Conditions                                               | Min | Тур | Max | Unit  |

|--------------------------------|------------|-----------------------|---------------------------------------------------------------|-----|-----|-----|-------|

| DP DM Detection                |            |                       |                                                               |     |     |     |       |

| D+ Voltage Source              |            | V <sub>DP_SCR</sub>   |                                                               | 0.5 | 0.6 | 0.7 | V     |

| D+ Voltage Source O<br>Current | utput      |                       |                                                               | 200 |     |     | μА    |

| D- Current Sink                |            | I <sub>DM_SINK</sub>  |                                                               | 50  | 100 | 150 | μΑ    |

| Innut Conscitones              |            | C.                    | DM pin, Switch Open                                           |     | 4.5 | 5   | n۲    |

| Input Capacitance              |            | Cı                    | DP pin, Switch Open                                           |     | 4.5 | 5   | pF    |

| Innut lookaga                  |            | 1.                    | DM pin, Switch Open                                           | -1  |     | 1   |       |

| Input leakage                  |            | lı                    | DP pin, Switch Open                                           | -1  |     | 1   | μΑ    |

| DP Low Comparator              | Threshold  | V <sub>DP_LOW</sub>   |                                                               | 0.8 |     |     | V     |

| DM High Comparator             | Threshold  | V <sub>DM_HIGH</sub>  |                                                               | 0.8 |     |     | V     |

| DM Low Comparator              | Threshold  | V <sub>DM_LOW</sub>   |                                                               |     |     | 475 | mV    |

| NTC Monitor                    |            |                       |                                                               |     |     |     |       |

| HOT Threshold                  |            | V <sub>VTS</sub> _HOT | VTS falling, the ratio of VPTS, VIN > V <sub>IN(MIN)</sub>    |     | 30  | 31  | %VPTS |

| WARM Threshold                 |            | Vvts_warm             | VTS falling, the ratio of VPTS,<br>VIN > V <sub>IN(MIN)</sub> | 37  | 38  | 39  | %VPTS |

| COOL Threshold                 |            | Vvts_cool             | VTS rising, the ratio of VPTS,<br>VIN > V <sub>IN(MIN)</sub>  | 55  | 56  | 57  | %VPTS |

| COLD Threshold                 |            | V <sub>VTS_COLD</sub> | VTS rising, the ratio of VPTS, VIN > V <sub>IN(MIN)</sub>     | 59  | 60  | 61  | %VPTS |

| Low Temperature Hys            | steresis   | ΔVvτs                 |                                                               |     | 1   |     | %VPTS |

| Disable Threshold              |            | V <sub>VTS_OFF</sub>  | TS function disable                                           | 2   | 3   | 4   | %VPTS |

| Control I/O Pin                |            |                       |                                                               |     |     |     |       |

| Output Low Voltage for STAT    |            | VoL                   | I <sub>DS</sub> = 10mA                                        |     |     | 0.4 | V     |

| CE Input Threshold             | Logic-High | V <sub>IH</sub>       |                                                               | 1.3 |     |     |       |

| Voltage                        | Logic-Low  | VIL                   |                                                               |     |     | 0.4 | V     |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A$  = 25°C on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

# **Typical Application Circuit**

# **Typical Operating Characteristics**

Copyright@2016 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

### **Applications Information**

The RT9460 switching charger integrates a synchronous PWM controller with power MOSFETs to provide input voltage MIVR (Minimum Input Voltage Regulation), input current AICR (Active Input Current Regulation), high accuracy current and voltage regulation, and charge termination. The charger also features USB OTG (On-The-Go).

The RT9460 has three operation modes: charge mode, boost mode (USB OTG), and high impedance mode. In charge mode, the RT9460 supports a precision charging system for single cell. In boost mode, the RT9460 works as the boost converter and boosts the voltage from battery to VIN pin for sourcing the OTG devices. In high impedance mode, the RT9460 stops charging or boosting and operates in a mode with low current from VIN or battery to reduce the power consumption when the portable device is in standby mode.

Notice that the RT9460 integrate input power source (AC adapter or USB input) detection. Thus, the RT9460 can automatically set the charge current by option. The charge current needs to be set via I<sup>2</sup>C interface by the host. The RT9460 application mechanism and I<sup>2</sup>C compatible interface are introduced in later sections.

#### **Charge Mode Operation**

#### Minimum Input Voltage Regulation (MIVR)

The RT9460 features input voltage MIVR function to prevent input voltage drop due to insufficient current provided by the adaptor or USB input. If MIVR function is enabled, the input voltage decreases when the over current of the input power source occurs. VIN is regulated at a predetermined voltage level which can be set as 4V to 11V by I<sup>2</sup>C interface. At this time, the current drawn by the RT9460 equals to the maximum current value that the input power can provide at the predetermined voltage level, instead of the set value.

#### **Charge Profile**

The RT9460 provides a precision Li-ion or Li-polymer charging solution for single-cell applications. Input current limit, charge current, termination current, charge voltage and input voltage MIVR are all programmable via the I<sup>2</sup>C interface. In charge mode, the RT9460 has five control loops to regulate input current (AICR), charge current, charge voltage, input voltage (MIVR) and device junction temperature. During the charging process, all five loops (if MIVR is enabled) are enabled and the dominant one will take over the control.

For normal charging process, the Li-ion or Li-polymer battery is charged in three charging modes depending on the battery voltage. At the beginning of the charging process, the RT9460 is in pre-charge mode. When the battery voltage rises above pre-charge threshold voltage (V<sub>PREC</sub>), the RT9460 enters fast-charge mode. Once the battery voltage is close to the regulation voltage (V<sub>OREG</sub>), the RT9460 enters constant voltage mode.

#### **Pre-Charge Mode**

For life-cycle consideration, the battery can not be charged with large current under low battery condition. When the BATS pin voltage is below pre-charge threshold voltage (V<sub>PREC</sub>), the charger is in pre-charge mode with a weak charge current witch equals to the pre-charge current (I<sub>PREC</sub>). There are two control loops in Pre-charge mode. One is the ICC and the other is the MIN SYS. If the battery voltage is lower than the SYS voltage, the MOSFET won't fully turn-on to prevent the battery voltage to influence the SYS voltage. It features that the charger can also provide the current to the load from SYS even the battery voltage is too low. In pre-charge mode, the charger basically works as an LDO. The pre-charge current also acts as the current limit when the BATS pin is shorted. The Pre-Charge current levels are 100mA - 850mA programmed by I<sup>2</sup>C.

#### **Fast-Charge Mode and Settings**

As the BAT pin rises above VPREC, the charger enters fast-charge mode and starts charging. Notice that the MUIC integrates input power source (AC adapter or USB input) detection. Thus, the switching charger can set the charge current by option automatically. Unlike the linear charger (LDO), the switching charger (Buck converter) is a current amplifier. The current drawn by the switching charger is different from the current into the battery.

The user can set the Average Input Current Regulation (AICR) and output charge current (I<sub>CHRG</sub>) respectively.

#### **Cycle-by-Cycle Current Limit**

The charger of the RT9460 has an embedded cycle-bycycle current limit for inductor. Once the inductor current touches the threshold (4.5A typ.), the charger stops charging immediately to prevent over current from damaging the device. Notice that, the mechanism can not be disabled by any way.

#### **Average Input Current Regulation (AICR)**

The AICR setting is controlled by I<sup>2</sup>C. The AICR100 mode limits the input current to 100mA. The AICR500 mode limits the input current to 500mA. If the application does not need input current limit, it can be disabled also. The AICR levels programmed by I<sup>2</sup>C and suitable for USB port and several TA types.

#### Charge Current (I<sub>CHG</sub>)

The charge current into the battery is determined by the power path sensing RON and ICC setting by  $I^2C$ . The voltage between the SYS and BAT pins is regulated to the voltage control by ICC setting. ( $I_{CC} \times R_{ON}$ ,  $R_{ON}$ : power path  $R_{ON}$ )

At RT9460, the  $R_{ON}$  is  $35m\Omega$  and the Fast-Charge currents is set by the I²C interface from 1.25A to 3.125A per 125mA.

#### **Constant Voltage Mode and Settings**

The RT9460 enters constant voltage mode when the BATS voltage is close to the output-charge voltage ( $V_{OREG}$ ). In this mode, the charge current begins to decrease. For default settings (charge current termination is disabled),

the RT9460 does not turn off and always regulates the battery voltage at VOREG. However, once the charge current termination is enabled, the charger terminates if the charge current is below termination current ( $I_{EOC}$ ) in constant-voltage mode. The charge current termination function is controlled by the  $I^2C$  interface.

After termination, a new charge cycle restarts when one of the following conditions is detected:

- The BATS pin voltage falls below the V<sub>OREG</sub> V<sub>RECH</sub> threshold.

- VIN Power On Reset (POR).

- CHG\_EN bit toggle or RST bit is set (via I<sup>2</sup>C interface).

#### **Output Charge Voltage (Voreg)**

The output-charge voltage is set by the I<sup>2</sup>C interface from 3.5V to 4.62V per 25mV. The default value is 4V (011001).

#### **Termination Current (IEOC)**

If the charger current termination is enabled (TE bit = "1" of REG0x01[3]), the end-of-charge current is determined by both termination current sense voltage ( $V_{EOC}$ ) and power path sense resistor ( $R_{ON}$ ). General  $R_{ON}$  is 35m $\Omega$ , IEOC is set by the I<sup>2</sup>C interface from 100mA to 450mA per 50mA.

#### Input Voltage Protection in Charge Mode

During charge mode, there are two protection mechanisms against if input power source capability is less than the charging current setting. One is AICR and the other is minimum input voltage regulation. A suitable level of AICR can prevent VBUS drop by the insufficient capability. As the AICR setting is not suitable, MIVR will regulate the VBUS in the setting level and sink the maximum current of power source.

#### Sleep Mode $(V_{IN} - V_{BATS} < V_{SLP})$

The RT9460 enters sleep mode if the voltage drop between the VIN and BATS pins falls below  $V_{\text{SLP}}$ . In sleep mode, the reverse blocking switch and PWM are all turned off. This function prevents battery drain during poor or no input power source.

#### **Input Over Voltage Protection**

When VBUS rises above the input over voltage threshold, the switching charger stops charging and sets the fault status bits. The condition is released when VBUS falls below OVP threshold. The switching charger then resumes charging operation.

# **Boost Mode Operation (OTG) Trigger and Operation**

The RT9460 features USB OTG support. When OTG function is enabled, the synchronous boost control loop takes over the power MOSFETs and reverses the power flow from the battery to the VIN pin. In normal boost mode, the VIN pin is regulated to the level controlled by VOREG[5:0] from 4.425V to 5.825 per 25mV. The boost provides up to 1A current to support other OTG devices connected to the USB connector.

#### **Output Over Voltage Protection**

In boost mode, the output over voltage protection is triggered when the VIN voltage is above the output OVP threshold. When OVP occurs, the boost converter stops switching and turns off immediately.

#### **Output Overload Protection**

The RT9460 provides an overload protection to prevent the device and battery from damage when VIN is overload. Once overload condition is detected, the reverse blocking switch operates in linear region to limit the output current while the MID voltage remains in voltage regulation. If the overload condition lasts for more than 32ms, the RT9460 will recognize the overload fault condition and resets registers to the default settings.

#### **Battery Detection During Normal Charging**

The RT9460 provides a battery absent detection scheme to detect insertion or removal of the battery pack. The battery detection scheme is valid only when both TE = 1 and BATD\_EN = 1.

During normal charging process, once the charge done condition is satisfied ( $V_{BATS} > V_{OREG} - V_{RECH}$  and termination current is detected), the RT9460 turns off the PWM converter and initiates a discharge current (detection current) for a detection time period. After that,

the RT9460 checks the BATS voltage. If it is still above the recharge threshold, the battery is present and charge done is detected. If the BATS voltage is below the recharge threshold, the battery is absent. Thus, the RT9460 stops charging and the charge parameters are reset to the default values. The charge resumes after a period of tDET (2sec. typ.).

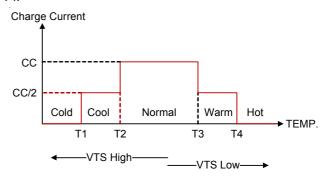

#### **JEITA Protection**

To enhance thermal protection of battery, JEITA function is implemented in RT9460. JEITA guideline was released in 2007. It includes Warm and cool protection (cool section is between T1 and T2; warm section is between T3 and T4, see the figure as below). When battery's temperature is in warm or cool section, RT9460 will reduce charging current (by a half of CC mode current). RT9460 stop charging if temperature is lower than T1 or is higher than T4.

Thermal of battery can be monitored by TS PIN. There are 4 sections should be implemented in JEITA function. Base on  $R_{hot}$  and  $R_{cold}$ , RT1 and RT2 can be determined by equation (1) and equation (2).

(R<sub>hot</sub> mean that system trigger battery OTP, R<sub>cold</sub> mean that system trigger battery low temperature protection.)

$$R_{T1} = VPTS \times [(1/V_{T1} - 1/V_{T4})/(1/R_{Cold} - 1/R_{Hot})]$$

(1)

$$R_{T2} = R_{T1} x [1/(VPTS/V_{T1} - R_{T1}/R_{Cold} - 1)]$$

(2)

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WL-CSP-25B 2.52x2.52 package, the thermal resistance,  $\theta_{JA}$ , is 32.1°C/W on a standard JEDEC 51-7 four-layer thermal test board. For WQFN-32L 4x4 package, the thermal resistance,  $\theta_{JA}$ , is 27.8°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A$ = 25°C can be calculated by the following formula :

$P_{D(MAX)}$  = (125°C - 25°C) / (32.1°C/W) = 3.11W for WL-CSP-25B 2.52x2.52 package

$P_{D(MAX)}$  = (125°C - 25°C) / (27.8°C/W) = 3.59W for WQFN-32L 4x4 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}.$  The derating curve in Figure 1 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 1. Derating Curve of Maximum Power Dissipation

#### **Layout Considerations**

- For AGND noise reduction, PGND and AGND should connect directly at top layer.

- ► For AGND noise reduction, PGND and AGND should be connected by ground plane at inner layer1. And this ground plane should be connected to system ground plane by via.

- VBUS and VMID (capacitor GND) should be connected to IC PGND directly at top layer.

- The output inductor and bootstrap capacitor should be placed close to the RT9460 and LX pins.

Figure 2. PCB Layout Guide

# **Control Register (Control)**

I<sup>2</sup>C Slave Address: 0100101

| Address | Name        | Bit7              | Bit6        | Bit5     | Bit4           | Bit3     | Bit2            | Bit1         | Bit0         |

|---------|-------------|-------------------|-------------|----------|----------------|----------|-----------------|--------------|--------------|

|         | Device ID   |                   | VENI        | DOR_ID   |                |          | CHI             | P_REV        |              |

| 0x03    | Reset Value | 0                 | 1           | 0        | 0              | 0        | 0               | 0            | 0            |

|         | Read/Write  | R                 | R           | R        | R              | R        | R               | R            | R            |

|         | Control1    | Sel_<br>SWFreq    | EN_<br>STAT | STA      | AT             | BOOST    | PWR_<br>Rdy     | OTG_<br>PinP | MIVR         |

| 0x00    | Reset Value | 0                 | 1           | 0        | 0              | 0        | 0               | 0            | 0            |

|         | Read/Write  | R/W               | R/W         | R        | R              | R        | R               | R            | R            |

|         | Control2    |                   | IEOC[2:0]   |          | Higher_<br>OCP | TE       | IIN_INT         | HZ           | OPA_<br>MODE |

| 0x01    | Reset Value | 0                 | 1           | 0        | 0              | 0        | 0               | 0            | 0            |

|         | Read/Write  | R/W               | R/W         | R/W      | R/W            | R/W      | R/W             | R/W          | R/W          |

|         | Control3    |                   |             | VORE     | G[5:0]         | <b>.</b> |                 | OTG_PL       | OTG_EN       |

| 0x02    | Reset Value | 0                 | 1           | 1        | 0              | 0        | 1               | 1            | 0            |

|         | Read/Write  | R/W               | R/W         | R/W      | R/W            | R/W      | R/W             | R/W          | R/W          |

|         | Control4    | RST               | Reserved    | Reserved | Reserved       | Reserved | Reserved        | Reserved     | Reserved     |

| 0x04    | Reset Value | 1                 | 0           | 0        | 0              | 0        | 0               | 0            | 0            |

|         | Read/Write  | R/W               | R/W         | R/W      | R/W            | R/W      | R/W             | R/W          | R/W          |

|         | Control5    | SYSUVP_<br>HW_SEL | OTG_OC      | SYS_M    | lin[1:0]       |          | IPRE            | EC[3:0]      |              |

| 0x05    | Reset Value | 1                 | 0           | 0        | 1              | 0        | 0               | 1            | 1            |

|         | Read/Write  | R/W               | R/W         | R/W      | R/W            | R/W      | R/W             | R/W          | R/W          |

|         | Control6    |                   | ICHI        | RG[3:0]  |                | EN_OSCSS |                 | VPREC[2      | :0]          |

| 0x06    | Reset Value | 0                 | 0           | 0        | 0              | 0        | 0               | 1            | 0            |

|         | Read/Write  | R/W               | R/W         | R/W      | R/W            | R/W      | R/W             | R/W          | R/W          |

|         | Control7    | CC_JEITA          | BATD_EN     | Chip_EN  | CHG_EN         | TS_HOT   | TS_<br>WARM     | TS_COOL      | TS_COLD      |

| 0x07    | Reset Value | 0                 | 0           | 1        | 1              | 0        | 0               | 0            | 0            |

|         | Read/Write  | R/W               | R/W         | R/W      | R/W            | R/W      | R/W             | R/W          | R/W          |

|         | Control8    | Reserved          | Reserved    | Reserved | Reserved       | Reserved | PI              | SenseNod     | e [2:0]      |

| 0x1C    | Reset Value | 1                 | 0           | 0        | 1              | 1        | 1               | 0            | 0            |

|         | Read/Write  | R/W               | R/W         | R/W      | R/W            | R/W      | R/W             | R/W          | R/W          |

|         | IRQ1        | TSDI              | VINOVPI     | WakeUpI  | WatchDogl      | Reserved | CHTERM_<br>TMRI | SYSUVP       | BATAB        |

| 0x08    | Reset Value | 0                 | 0           | 0        | 0              | 0        | 0               | 0            | 0            |

|         | Read/Write  | R                 | R           | R        | R              | R        | R               | R            | R            |

|         | IRQ2        | CHRVPI            | CHBADI      | CHBATOVI | CHTERMI        | CHRCHGI  | CHTMRI          | CHTREGI      | SYSWAKEUPI   |

| 0x09    | Reset Value | 0                 | 0           | 0        | 0              | 0        | 0               | 0            | 0            |

|         | Read/Write  | R                 | R           | R        | R              | R        | R               | R            | R            |

Copyright@2016 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Address | Name             | Bit7           | Bit6             | Bit5          | Bit4           | Bit3     | Bit2             | Bit1          | Bit0            |

|---------|------------------|----------------|------------------|---------------|----------------|----------|------------------|---------------|-----------------|

|         | IRQ3             | BSTVINOVI      | BSTOLI           | BSTLOWVI      | Reserved       | Reserved | Reserved         | Reserved      | Reserved        |

| 0x0A    | Reset Value      | 0              | 0                | 0             | 0              | 0        | 0                | 0             | 0               |

|         | Read/Write       | R              | R                | R             | R              | R        | R                | R             | R               |

|         | Mask 1           | TSDIM          | VINOVPIM         | WakeUpIM      | WatchDog<br>IM | Reserved | CHTERM_<br>TMRIM | SYSUVP<br>IM  | BATABM          |

| 0x0B    | Reset Value      | 0              | 0                | 0             | 0              | 0        | 0                | 0             | 0               |

|         | Read/Write       | R/W            | R/W              | R/W           | R/W            | R/W      | R/W              | R/W           | R/W             |

| 000     | Mask 2           | CHRVPIM        | CHBADIM          | CHBATOV<br>IM | CHTERMIM       | CHRCHGIM | CHTMRIM          | CHTREGI<br>M  | SYSWAKE<br>UPIM |

| 0x0C    | Reset Value      | 0              | 0                | 0             | 0              | 0        | 0                | 0             | 0               |

|         | Read/Write       | R/W            | R/W              | R/W           | R/W            | R/W      | R/W              | R/W           | R/W             |

| 0.00    | Mask 3           | BSTVINOV<br>IM | BSTOLIM          | BSTLOW<br>VIM | Reserved       | Reserved | Reserved         | Reserved      | Reserved        |

| 0x0D    | Reset Value      | 0              | 0                | 0             | 0              | 0        | 0                | 0             | 0               |

|         | Read/Write       | R/W            | R/W              | R/W           | R/W            | R/W      | R/W              | R/W           | R/W             |

|         | Control-DP<br>DM | (              | CHG_TYP[2:0      | ]             | IINLMT         | SEL[1:0] | CHG_<br>2DET     | CHG_<br>1DET  | CHGRUN          |

| 0x0E    | Reset Value      | 0              | 0                | 0             | 1              | 0        | 1                | 1             | 0               |

|         | Read/Write       | R              | R                | R             | R/W            | R/W      | R/W              | R/W           | R               |

|         | Control 9        | Reserved       | PPC_<br>CTRL_SEL | EN_<br>PPCTRL | MIVR_<br>ENB   |          | MIVR_L           |               |                 |

| 0x21    | Reset<br>Value   | 0              | 1                | 0             | 0              | 0        | 0                | 0             | 0               |

|         | Read/Write       | R/W            | R/W              | R/W           | R/W            | R/W      | R/W              | R/W           | R/W             |

|         | Control 10       | CLR_DP         | DP_STAT          |               | WT_FC[2:0]     |          | WT_PR            | RC[1:0]       | TMR_<br>Pause   |

| 0x22    | Reset<br>Value   | 0              | 0                | 0             | 0              | 0        | 0                | 0             | 0               |

|         | Read/Write       | R/W            | R                | R/W           | R/W            | R/W      | R/W              | R/W           | R/W             |

|         | Control 11       |                |                  | AICR[4:0]     | T              | I        | Dea              | dBAT_LVL      | [2:0]           |

| 0x23    | Reset<br>Value   | 0              | 0                | 1             | 0              | 1        | 1                | 1             | 1               |

|         | Read/Write       | R/W            | R/W              | R/W           | R/W            | R/W      | R/W              | R/W           | R/W             |

|         | Control 12       | EOC_Ti         | mer[1:0]         | Wa            | akeUp_Timer[   | 2:0]     | WK_<br>Timer_EN  | IRQ_<br>Pulse | IRQ_REZ         |

| 0x24    | Reset<br>Value   | 0              | 0                | 0             | 0              | 0        | 0                | 0             | 0               |

|         | Read/Write       | R/W            | R/W              | R/W           | R/W            | R/W      | R/W              | R/W           | R/W             |

|         | Control 13       | WDT_EN         | Reserved         | Reserved      | TWDTRST        | Reserved | Reserved         | TWI           | OT[1:0]         |

| 0x25    | Reset<br>Value   | 0              | 0                | 0             | 1              | 0        | 0                | 1             | 1               |

|         | Read/Write       | R/W            | R/W              | R/W           | R/W            | R/W      | R/W              | R/W           | R/W             |

| Address | Name             | Bit7    | Bit6     | Bit5         | Bit4         | Bit3          | Bit2   | Bit1     | Bit0     |

|---------|------------------|---------|----------|--------------|--------------|---------------|--------|----------|----------|

| 0x26    | STAT IRQ         | TSHOTI  | TSWARMI  | TSCOOLI      | TSCOLDI      | PWR_Rdyl      | MIVRI  | Reserved | Reserved |

|         | Reset<br>Value   | 0       | 0        | 0            | 0            | 0             | 0      | 0        | 0        |

|         | Read/Write       | R/W     | R/W      | R/W          | R/W          | R/W           | R/W    | R/W      | R/W      |

|         | STAT IRQ<br>Mask | TSHOTIM | TSWARMIM | TSCOOLI<br>M | TSCOLDI<br>M | PWR_<br>RdylM | MIVRIM | Reserved | Reserved |

| 0x27    | Reset<br>Value   | 0       | 0        | 0            | 0            | 0             | 0      | 0        | 0        |

|         | Read/Write       | R/W     | R/W      | R/W          | R/W          | R/W           | R/W    | R/W      | R/W      |

| Address                                                                                                       | Name           | Bit7                                                                                                                            | Bit6                                                                                                                                                   | Bit5        | Bit4           | Bit3    | Bit2        | Bit1         | Bit0         |  |  |

|---------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|---------|-------------|--------------|--------------|--|--|

|                                                                                                               | Control 1      | Sel_<br>SWFreq                                                                                                                  | EN_<br>STAT                                                                                                                                            | Sī          | TAT            | BOOST   | PWR_<br>Rdy | OTG_<br>Pinp | MIVR         |  |  |

| 0x00                                                                                                          | Reset<br>Value | 0                                                                                                                               | 1                                                                                                                                                      | 0           | 0              | 0       | 0           | 0            | 0            |  |  |

|                                                                                                               | Read/Write     | R/W R/W R R R R R                                                                                                               |                                                                                                                                                        |             |                |         |             |              |              |  |  |

| Sel_S                                                                                                         | SWFreq         | The switching frequency selection bit (Charger/OTG) 0 : The switching frequency is 1.5MHz 1 : The switching frequency is 750kHz |                                                                                                                                                        |             |                |         |             |              |              |  |  |

| EN_                                                                                                           | _STAT          | 0 : Disable S<br>1 : Enable S                                                                                                   |                                                                                                                                                        |             |                |         |             |              |              |  |  |

| S                                                                                                             | TAT            | Charger statu<br>00 : Ready<br>01 : Charge i<br>10 : Charge o<br>11 : Fault                                                     | n progress                                                                                                                                             |             |                |         |             |              |              |  |  |

| ВС                                                                                                            | OST            | 0 : Not in boo<br>1 : Boost mo                                                                                                  |                                                                                                                                                        |             |                |         |             |              |              |  |  |

| PWI                                                                                                           | R_Rdy          | 0 : Input pow                                                                                                                   | Power status bit ) : Input power is bad, VIN > VOVP or VIN < VUVLO or VIN < BATS + VSLP I : Input power is good, UVLO < VIN < VOVP & VIN > BATS + VSLP |             |                |         |             |              |              |  |  |

| ОТО                                                                                                           | S_PinP         | OTG pin pola<br>0 : OTG inpu<br>1 : OTG inpu                                                                                    | t pin is low                                                                                                                                           |             |                |         |             |              |              |  |  |

| M                                                                                                             | IVR            | MIVR status<br>0 : MIVR reg<br>1 : MIVR reg                                                                                     | ulation is ina                                                                                                                                         |             |                |         |             |              |              |  |  |

|                                                                                                               | Control 2      | ı                                                                                                                               | EOC[2:0]                                                                                                                                               |             | Higher_<br>OCP | TE      | IIN_INT     | HZ           | OPA_<br>MODE |  |  |

| 0x01                                                                                                          | Reset<br>Value | 0                                                                                                                               | 1                                                                                                                                                      | 0           | 0              | 0       | 0           | 0            | 0            |  |  |

|                                                                                                               | Read/Write     | R/W                                                                                                                             | R/W                                                                                                                                                    | R/W         | R/W            | R/W     | R/W         | R/W          | R/W          |  |  |

| EOC current level setting 000 : 100mA 001 : 150mA 010 : 200mA 011 : 250mA 100 : 300mA 101 : 350mA 111 : 450mA |                |                                                                                                                                 |                                                                                                                                                        |             |                |         |             |              |              |  |  |

| Highe                                                                                                         | er_OCP         | Charger/OTG OCP level selection  O: OCP = 4.5A  1: OCP = 6A                                                                     |                                                                                                                                                        |             |                |         |             |              |              |  |  |

|                                                                                                               | TE             | Charge curre<br>0 : Disable cl<br>1 : Enable ch                                                                                 | narge curren                                                                                                                                           | t terminati | on             | control |             |              |              |  |  |

| Address | Name           | Bit7                                                                                                                                                                                                                                              | Bit6                                                                                                                                                       | Bit5  | Bit4  | Bit3 | Bit2 | Bit1   | Bit0   |  |  |

|---------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|------|--------|--------|--|--|

| IIN     | _INT           | IAICR setting bit 0: Decided by external OTG pin, 500mA current limit when OTG pin is low and 1A current limit when OTG pin is high 1: Decided by I <sup>2</sup> C IAICR[4:0] and DPDM results, refer to REG0x0E                                  |                                                                                                                                                            |       |       |      |      |        |        |  |  |

| ŀ       | ΗZ             | 0 : Not high impedance mode 1 : High impedance mode                                                                                                                                                                                               |                                                                                                                                                            |       |       |      |      |        |        |  |  |

| OPA_    | MODE           | 0 : Charger n<br>1 : Boost mod                                                                                                                                                                                                                    |                                                                                                                                                            |       |       |      |      |        | _      |  |  |

|         | Control 3      |                                                                                                                                                                                                                                                   |                                                                                                                                                            | VOREG | [5:0] |      |      | OTG_PL | OTG_EN |  |  |

| 0x02    | Reset<br>Value | 0                                                                                                                                                                                                                                                 | 1                                                                                                                                                          | 1     | 0     | 0    | 1    | 1      | 0      |  |  |

|         | Read/Write     | R/W                                                                                                                                                                                                                                               | R/W                                                                                                                                                        | R/W   | R/W   | R/W  | R/W  | R/W    | R/W    |  |  |

| VORI    | EG[5:0]        | 00 0001 : 3.5<br>00 0010 : 3.5<br><br>01 1000 : 3.9<br>01 1001 : 4.0<br>01 1010 : 4.0<br><br>10 0111 : 4.2<br>10 1000 : 4.3<br>10 1001 : 4.3<br><br>10 1110 : 4.4<br>10 1111 : 4.4<br><br>11 0110 : 4.5<br>11 0111 : 4.6<br><br>11 1111 : 4.6<br> | 4V / 4.475V<br>8V / 5.025 V<br>0V / 5.05V<br>2 / 5.075V<br>8V / 5.4V<br>0V / 5.425V<br>2V / 5.575V<br>4V / 5.6V<br>8V / 5.775V<br>0V / 5.8V<br>2V / 5.825V |       |       |      |      |        |        |  |  |

| ОТ      | G_PL           |                                                                                                                                                                                                                                                   | : Active at low level<br>: Active at High level                                                                                                            |       |       |      |      |        |        |  |  |

| ОТО     | G_EN           | 0 : Disable O<br>1 : Enable O                                                                                                                                                                                                                     | _                                                                                                                                                          | _     | _     | _    |      |        | _      |  |  |

| Address    | Name           | Bit7                                                                                                                                                                                                           | Bit6                                                     | Bit5                      | Bit4         | Bit3        | Bit2        | Bit1     | Bit0     |  |  |

|------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------|--------------|-------------|-------------|----------|----------|--|--|

|            | Device ID      |                                                                                                                                                                                                                | VEND                                                     | OR_ID                     |              |             | CHIP        | _REV     |          |  |  |

| 0x03       | Reset<br>Value | 0                                                                                                                                                                                                              | 1                                                        | 0                         | 0            | 0           | 0           | 0        | 0        |  |  |

|            | Read/Write     | R                                                                                                                                                                                                              | R                                                        | R                         | R            | R           | R           | R        | R        |  |  |

| VENI       | DOR_ID         | Vendor Identification : Richtek : 0100b                                                                                                                                                                        |                                                          |                           |              |             |             |          |          |  |  |

| CHII       | P_REV          | Chip Revisi                                                                                                                                                                                                    | on                                                       |                           |              |             |             |          |          |  |  |

|            | Control 4      | RST                                                                                                                                                                                                            | Reserved                                                 | Reserved                  | Reserved     | Reserved    | Reserved    | Reserved | Reserved |  |  |

| 0x04       | Reset<br>Value | 0                                                                                                                                                                                                              | 0                                                        | 0                         | 0            | 0           | 0           | 0        | 0        |  |  |

|            | Read/Write     | R/W                                                                                                                                                                                                            | R/W                                                      | R/W                       | R/W          | R/W         | R/W         | R/W      | R/W      |  |  |

| F          | RST            | Write : 1-Ch                                                                                                                                                                                                   | narger in re                                             | set mode, 0               | )-No effect, | Read : alwa | ays get "0" |          |          |  |  |

|            | Control 5      | SYSUVP_<br>HW_SEL                                                                                                                                                                                              | OTG_OC                                                   | SYS_N                     | /lin[1:0]    |             | IPRE        | C[3:0]   |          |  |  |

| 0x05       | Reset<br>Value | 1                                                                                                                                                                                                              | 0                                                        | 0                         | 1            | 0           | 0           | 1        | 1        |  |  |

|            | Read/Write     | R/W                                                                                                                                                                                                            | R/W                                                      | R/W                       | R/W          | R/W         | R/W         | R/W      | R/W      |  |  |

| SYSUVF     | P_HW_SEL       | 1 : Switchin                                                                                                                                                                                                   | ig is not turi<br>ig is turned                           | ned off whe<br>off when S | n System U   | IVP         |             |          |          |  |  |

| ОТ         | G_OC           | Over current protection threshold<br>0 : 0.5A<br>1 : 1A                                                                                                                                                        |                                                          |                           |              |             |             |          |          |  |  |

| SYS_       | Min[1:0]       | System mir<br>00 : 3.5V<br>01 : 3.6V<br>10 : 3.7V<br>11 : 3.8V                                                                                                                                                 | nimum regu                                               | lation volta              | ge           |             |             |          |          |  |  |

| IPREC[3:0] |                | 0000 : 100r<br>0001 : 150r<br>0010 : 200r<br>0011 : 250r<br>0100 : 300r<br>0110 : 400r<br>0111 : 450r<br>1000 : 500r<br>1001 : 550r<br>1010 : 600r<br>1011 : 650r<br>1100 : 700r<br>1110 : 800r<br>1111 : 850r | mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA<br>mA |                           |              |             |             |          |          |  |  |

| Address                                                                                                         | Name           | Bit7                                                                | Bit6                                                                             | Bit5        | Bit4       | Bit3         | Bit2    | Bit1        | Bit0    |  |  |