# Dual Channel PWM Controller with I<sup>2</sup>C Interface Control for AMD SVI3 CPU/GPU Core Power Supply

# **General Description**

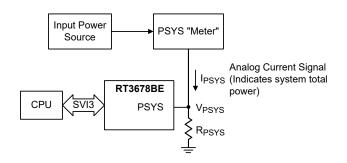

The RT3678BE is a synchronous buck controller which supports dual output rails and can fully meet AMD SVI3 requirements. The RT3678BE adopts G-NAVP<sup>TM</sup> (Green Native AVP), which is Richtek's proprietary topology derived from finite DC gain of EA amplifier with current mode control, making it easy to set the droop to meet all AMD CPU/GPU requirements of AVP (Adaptive Voltage Positioning). Based on the G-NAVP<sup>TM</sup> topology, the RT3678BE features a new generation of guick response mechanism (Adaptive Quick Response, AQR) to optimize AVP performance during load transient and reduce output capacitors. The RT3678BE integrates a high accuracy ADC for reporting and a non-volatile memory (NVM) to store custom configurations, such as output current scale, auto phase add/drop threshold, switching frequency, overcurrent threshold or AQR trigger level. It also features full fault protection functions, including overvoltage (OV), undervoltage (UV), overcurrent (OC) and undervoltage lockout (UVLO), over-temperature protection (OTP), VR-hot warning, CRC failure and communication failure. The RT3678BE provides independent enable, power good and temperature sensing for each output rail. It also supports several functions which can be set by the I<sup>2</sup>C interface.

# **Applications**

- AMD SVI3 VDDCR/VDDCR SOC Rails

- Desktop and Notebook Computer

- AVP Step-Down Converter

#### **Features**

- AMD SVI3 Rev 1.01 Compatible

- 8 Phase (Rail A) + 2 Phase (Rail B) PWM Controller

- G-NAVP<sup>TM</sup> (Green Native Adaptive Voltage Positioning) Topology

- 0.5% DAC Accuracy

- Differential Remote Voltage Sensing

- Built-in ADC for Reporting

- Accurate Current Balance

- Diode Emulation Mode (DEM) at Light Load

- Fast Transient Response: Adaptive Quick Response (AQR)

- OVP, OCP and UVP with Flag

- Switching Frequency Setting

- Auto Phase Add/Drop with DEM for Excellent Efficiency

- Voltage On-the-Fly (VOTF) Enhancement

- Acoustic Noise Suppression

- Zero Load-line

- Standard I<sup>2</sup>C Protocol Interface

- ► Internal Non-Volatile Memory (NVM) to Store Custom Configurations

- ► Current Balance Gain Adjustment for Thermal Balance

- **▶** Dynamic Load-line Setting

- ► Voltage Offset Setting

- ► Fixed VID Setting

- ▶ Protection Report and Protection Disable

- ► Output Voltage / Output Current / Temperature / Input Power Monitoring

- Soldering Good Detection

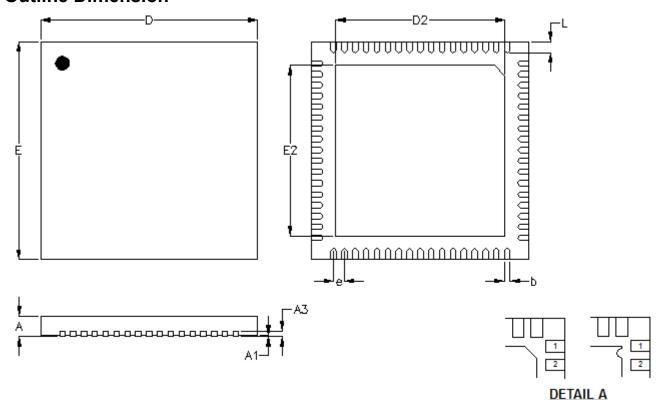

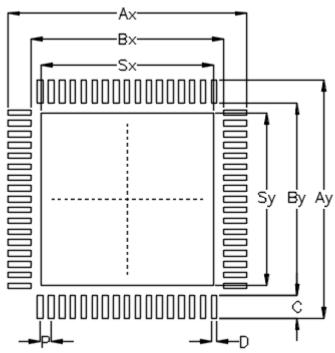

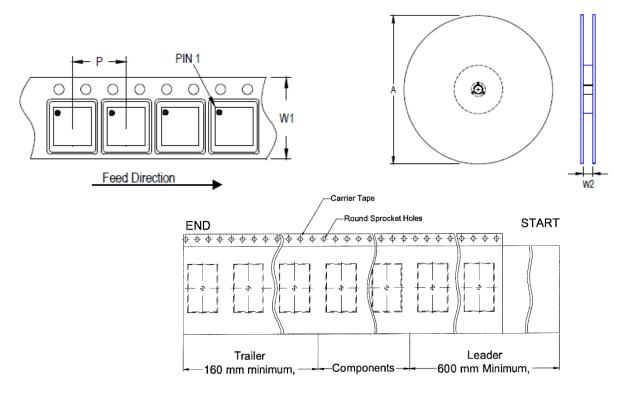

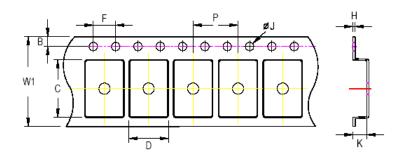

- Small 68-Lead WQFN Package

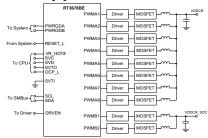

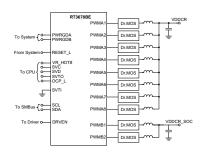

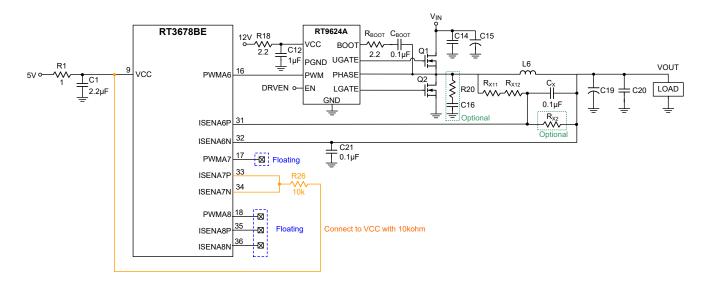

# **Simplified Application Circuit**

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

RICHTEK

is a registered trademark of Richtek Technology Corporation.

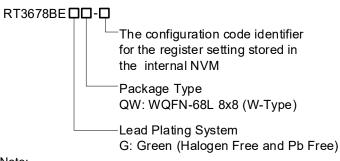

# **Ordering Information**

Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

# **Marking Information**

RT3678BE GQW YMDNN RT3678BEGQW: Product Code YMDNN: Date Code

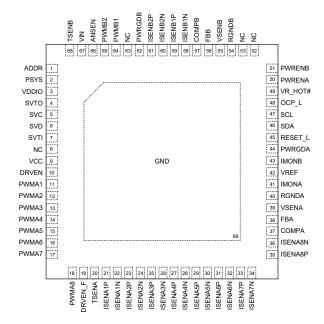

# **Pin Configuration**

(TOP VIEW)

WQFN-68L 8x8

# **Functional Pin Description**

| Pin No.          | Pin Name | Pin Function                                                                                                                                                                                                                                  |  |  |  |

|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                | ADDR     | A resistor tied to ground sets I <sup>2</sup> C address. For soldering check, connect the ADDR pin to 5V and pull the PWREN high. If the soldering is good, output voltage is 0.9V for rail A, 1V for rail B.                                 |  |  |  |

| 2                | PSYS     | System input power monitor. Place the PSYS resistor as close to the IC as possible.                                                                                                                                                           |  |  |  |

| 3                | VDDIO    | Supply voltage input of SVI3 interface. This pin serves as the reference for SVC, SVD, SVTI and SVTO.                                                                                                                                         |  |  |  |

| 4                | SVTO     | Serial VID Telemetry output. This pin is a push-pull output.                                                                                                                                                                                  |  |  |  |

| 5                | SVC      | Serial VID Clock input. This pin is a push-pull signal which acts as a clock for SVD, SVTI and SVTO.                                                                                                                                          |  |  |  |

| 6                | SVD      | Serial VID Data input. This pin is a push-pull signal which transmits commands from the controller to the targets.                                                                                                                            |  |  |  |

| 7                | SVTI     | Serial VID Telemetry input. This pin is driven by the next-furthest target on the telemetry daisy-chain.                                                                                                                                      |  |  |  |

| 8, 52,<br>53, 63 | NC       | No internal connection.                                                                                                                                                                                                                       |  |  |  |

| 9                | vcc      | Controller power supply. Connect this pin to 5V and place an RC filter, R = $1\Omega$ and C = $2.2\mu$ F. The decoupling capacitor should be placed as close to PWM controller as possible. The recommended size of R <sub>VCC</sub> is 0603. |  |  |  |

| 10               | DRVEN    | External driver mode control. As PSI6 command is received, this pin is in low state. The output high level is VCC.                                                                                                                            |  |  |  |

www.richtek.com

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                                                                 |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11      | PWMA1    | Phase #1 rail A PWM output. This signal is used to drive the PWM input of the FET diver IC. Unused PWM pins should be left unconnected. The PWM tri-state windows can be selected by NVM. One is 1.6V to 2.2V and the other is 1.4V to 2.1V. |

| 12      | PWMA2    | Phase #2 rail A PWM output. Refer to PWMA1 description.                                                                                                                                                                                      |

| 13      | PWMA3    | Phase #3 rail A PWM output. Refer to PWMA1 description.                                                                                                                                                                                      |

| 14      | PWMA4    | Phase #4 rail A PWM output. Refer to PWMA1 description.                                                                                                                                                                                      |

| 15      | PWMA5    | Phase #5 rail A PWM output. Refer to PWMA1 description.                                                                                                                                                                                      |

| 16      | PWMA6    | Phase #6 rail A PWM output. Refer to PWMA1 description.                                                                                                                                                                                      |

| 17      | PWMA7    | Phase #7 rail A PWM output. Refer to PWMA1 description.                                                                                                                                                                                      |

| 18      | PWMA8    | Phase #8 rail A PWM output. Refer to PWMA1 description.                                                                                                                                                                                      |

| 19      | DRVEN_F  | External driver mode control. As PSI6 command is received, this pin is in floating state. The output high level is VCC.                                                                                                                      |

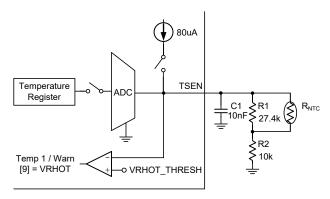

| 20      | TSENA    | External temperature sense input pin for rail A. Connect to NTC or integrated power stage temperature sensor.                                                                                                                                |

| 21      | ISENA1P  | Phase #1 current sense inputs of rail A. The ISENA1P and ISENA1N pins are                                                                                                                                                                    |

| 22      | ISENA1N  | used to differentially sense the corresponding channel current. Connecting ISENA1P to VCC if rail A is not used.                                                                                                                             |

| 23      | ISENA2P  | Phase #2 current sense inputs of rail A. The ISENA2P and ISENA2N pins are                                                                                                                                                                    |

| 24      | ISENA2N  | used to differentially sense the corresponding channel current. Connecting ISENA2P to VCC programs 1-phase operation.                                                                                                                        |

| 25      | ISNEA3P  | Phase #3 current sense inputs of rail A. The ISENA3P and ISENA3N pins are                                                                                                                                                                    |

| 26      | ISENA3N  | used to differentially sense the corresponding channel current. Connecting ISENA3P to VCC programs 2-phase operation.                                                                                                                        |

| 27      | ISENA4P  | Phase #4 current sense inputs of rail A. The ISENA4P and ISENA4N pins are                                                                                                                                                                    |

| 28      | ISENA4N  | used to differentially sense the corresponding channel current. Connecting ISENA4P to VCC programs 3-phase operation.                                                                                                                        |

| 29      | ISENA5P  | Phase #5 current sense inputs of rail A. The ISENA5P and ISENA5N pins are                                                                                                                                                                    |

| 30      | ISENA5N  | used to differentially sense the corresponding channel current. Connecting ISENA5P to VCC programs 4-phase operation.                                                                                                                        |

| 31      | ISENA6P  | Phase #6 current sense inputs of rail A. The ISENA6P and ISENA6N pins are                                                                                                                                                                    |

| 32      | ISENA6N  | used to differentially sense the corresponding channel current. Connecting ISENA6P to VCC programs 5-phase operation.                                                                                                                        |

| 33      | ISENA7P  | Phase #7 current sense inputs of rail A. The ISENA7P and ISENA7N pins are                                                                                                                                                                    |

| 34      | ISENA7N  | used to differentially sense the corresponding channel current. Connecting ISENA7P to VCC programs 6-phase operation.                                                                                                                        |

| 35      | ISENA8P  | Phase #8 current sense inputs of rail A. The ISENA8P and ISENA8N pins are                                                                                                                                                                    |

| 36      | ISENA8N  | used to differentially sense the corresponding channel current. Connecting ISENA8P to VCC programs 7-phase operation.                                                                                                                        |

| 37      | COMPA    | Error amplifier output of rail A.                                                                                                                                                                                                            |

| 38      | FBA      | Error amplifier voltage feedback of rail A.                                                                                                                                                                                                  |

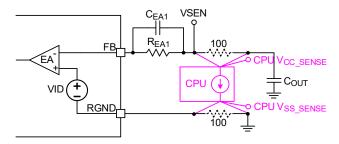

| 39      | VSENA    | Positive differential voltage sense input for rail A. Connect to positive remote sensing point and should be routed with RGNDA as a differential pair.                                                                                       |

| 40      | RGNDA    | Negative differential voltage sense input for rail A. Connect to negative remote sensing point.                                                                                                                                              |

| 41      | IMONA    | Rail A VR current monitor output. This pin outputs a current proportional to the output current.                                                                                                                                             |

| Pin No.             | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                    |

|---------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 42                  | VREF     | Fixed 0.6V output reference voltage. This voltage is used to offset the output voltage of all IMON pins. While controller shuts down or sets all rails in PSI6, voltage source shuts down. An external 0.47- $\mu$ F decoupling capacitor and a 3.9- $\Omega$ resistor must be placed between this pin and GND. |

| 43                  | IMONB    | Rail B VR current monitor output. This pin outputs a current proportional to the output current.                                                                                                                                                                                                                |

| 44                  | PWRGDA   | Power Good indicator for rail A. This open-drain output requires an external pull-up resistor. PWRGDA is pulled low when a shutdown fault occurs.                                                                                                                                                               |

| 45                  | RESET_L  | Input pin of SVI3 interface. Active low signal will reset all SVI3 state machines and SVI3 define registers to reset to default values.                                                                                                                                                                         |

| 46                  | SDA      | I <sup>2</sup> C data signal.                                                                                                                                                                                                                                                                                   |

| 47                  | SCL      | I <sup>2</sup> C clock signal.                                                                                                                                                                                                                                                                                  |

| 48                  | OCP_L    | Output pin of SVI3 interface. This open-drain output requires an external pull-up resistor. Asserted when output current is greater than OCP threshold or OCP warning threshold. The two rails of the controller share one OCP_L pin.                                                                           |

| 49                  | VR_HOT#  | Thermal warning flag. This open-drain output will be pulled low in an event of over-temperature warning without disabling the regulator.                                                                                                                                                                        |

| 50                  | PWRENA   | Active high output enable input pin for rail A. Faults are cleared when PWRENA is toggled but no effect on the sticky FAULT_STATUS bits.                                                                                                                                                                        |

| 51                  | PWRENB   | Active high output enable input pin for rail B. Faults are cleared when PWRENB is toggled but no effect on the sticky FAULT_STATUS bits.                                                                                                                                                                        |

| 54                  | RGNDB    | Negative differential voltage sense input for rail B. Connect to negative remote sensing point.                                                                                                                                                                                                                 |

| 55                  | VSENB    | Positive differential voltage sense input for rail B. Connect to positive remote sensing point and should be routed with RGNDB as a differential pair.                                                                                                                                                          |

| 56                  | FBB      | Error amplifier voltage feedback of rail B.                                                                                                                                                                                                                                                                     |

| 57                  | СОМРВ    | Error amplifier output of rail B.                                                                                                                                                                                                                                                                               |

| 58                  | ISENB1N  | Phase #1 current sense inputs of rail B. The ISENB1P and ISENB1N pins are                                                                                                                                                                                                                                       |

| 59                  | ISENB1P  | used to differentially sense the corresponding channel current. Connect ISENB1P to VCC if rail B is not used.                                                                                                                                                                                                   |

| 60                  | ISENB2N  | Phase #2 current sense inputs of rail B. The ISENB2P and ISENB1N pins are                                                                                                                                                                                                                                       |

| 61                  | ISENB2P  | used to differentially sense the corresponding channel current. Connect ISENB2P to VCC if rail B is not used.                                                                                                                                                                                                   |

| 62                  | PWRGDB   | Power Good indicator for rail B. This open-drain output requires an external pull-up resistor. PWRGDB is pulled low when a shutdown fault occurs.                                                                                                                                                               |

| 64                  | PWMB1    | Phase #1 rail B PWM output. This signal is used to drive the PWM input of the FET diver IC. Unused PWM pins should be left unconnected. The PWM tri-state windows can be selected by NVM. One is 1.6V to 2.2V and the other is 1.4V to 2.1V.                                                                    |

| 65                  | PWMB2    | Phase #2 rail B PWM output. Refer to PWMB1 description.                                                                                                                                                                                                                                                         |

| 66                  | ANSEN    | Acoustic Noise Suppression function setting. When the pin is pulled to VCC, this function can be enabled. This pin is not allowed to be floating.                                                                                                                                                               |

| 67                  | VIN      | VIN input pin. Connect a low pass filter to this pin to set on-time.                                                                                                                                                                                                                                            |

| 68                  | TSENB    | External temperature sense input pin for rail B. Connect to NTC or integrated power stage temperature sensor.                                                                                                                                                                                                   |

| 69<br>(Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND with enough via numbers for maximum power dissipation.                                                                                                                                                                             |

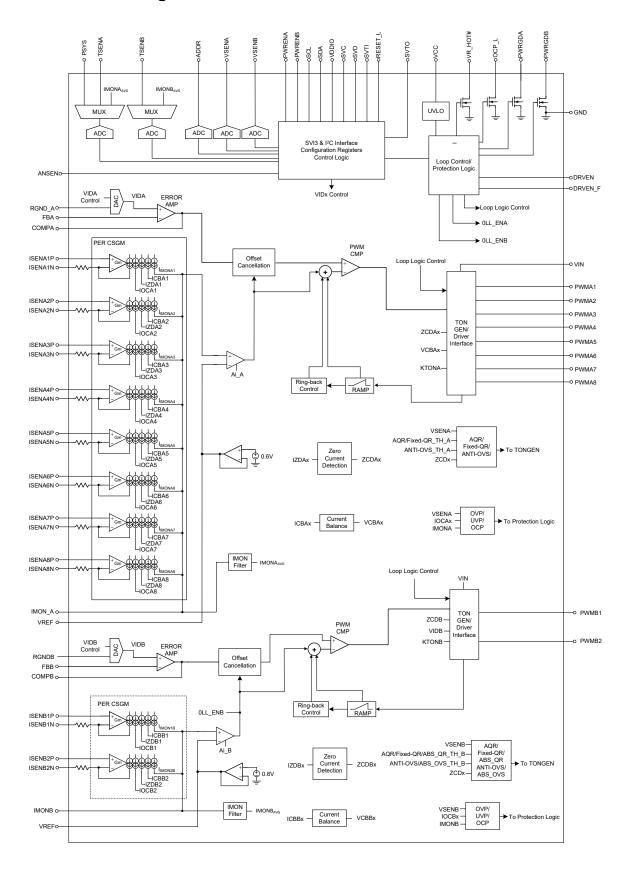

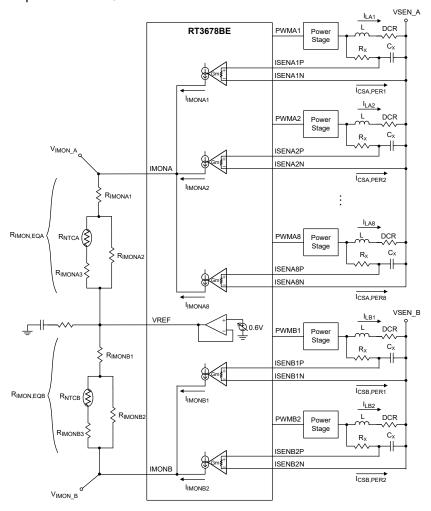

# **Functional Block Diagram**

March 2023

# **Operation**

# **G-NAVP<sup>TM</sup> Control Mode**

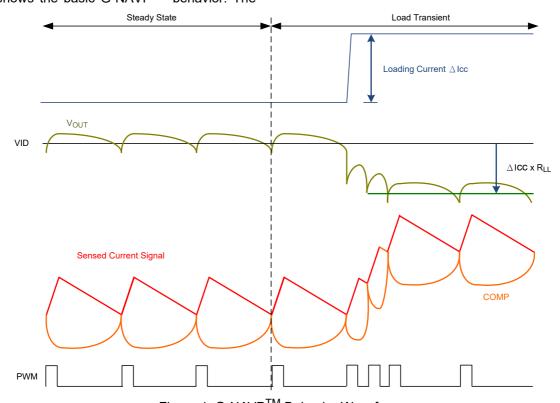

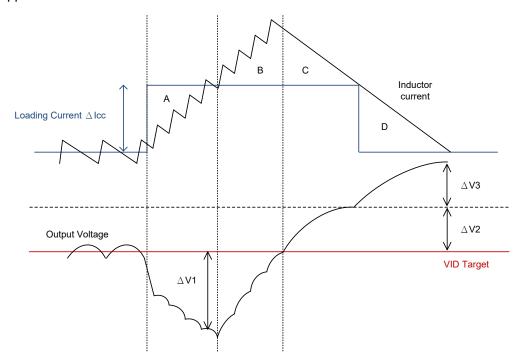

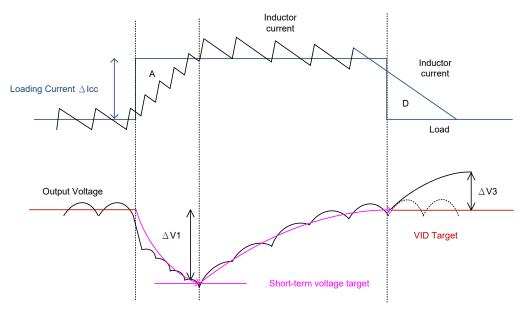

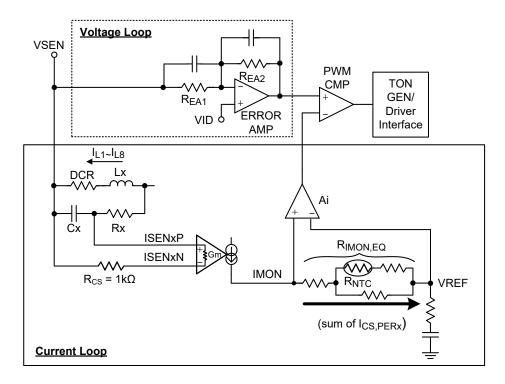

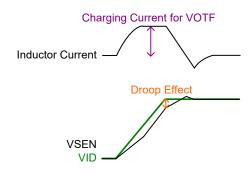

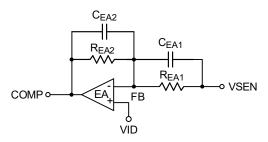

The RT3678BE adopts G-NAVPTM (Green Native AVP), which is Richtek's proprietary topology. It is derived from current mode constant on-time control with finite DC gain of error amplifier and DC offset cancellation. The topology can achieve easy load-line design and provide high DC accuracy and fast transient response. When the sensed current signal reaches the sensed voltage signal, the RT3678BE generates a PWM pulse to achieve loop modulation. Figure 1 shows the basic G-NAVP<sup>TM</sup> behavior. The

COMP signal is the inverted and amplified signal of the output voltage. The COMP rises due to output voltage droop and the rising COMP forces PWM to turn on earlier and more closely. While inductor current reaches loading current, COMP enters another steady state of higher voltage and the corresponding output voltage is in the steady state of lower voltage. The load-line, output voltage drooping proportional to loading current, is achieved.

Figure 1. G-NAVP<sup>TM</sup> Behavior Waveform

# SVI3, I<sup>2</sup>C Interface, Control Logic and Configuration Registers

SVI3 Interface receives or transmits SVI3 signal with CPU/GPU. The VR receives or transmits  $I^2C$  signals using the  $I^2C$  interface. Control Logic executes command (Read/Write/Reset registers, VID/Address packets, Change Power State and Telemetry Request) and sends related signals to control VR. Configuration Registers include function setting registers and SVI3 required registers.

#### **IMON Filter**

IMON Filter is used to average current signal by an analog low-pass filter. It outputs IMONA and IMONB to the MUX of ADC for current reporting.

# **MUX and ADC**

The MUX supports the inputs for TSENA, TSEN\_B, PSYS, IMON\_A and IMON\_B. The ADC converts these analog signals to digital codes for reporting or function settings.

#### **UVLO**

The UVLO detects the VCC voltage. As VCC exceeds the threshold, the controller issues POR = high and waits PWREN. After both POR PWREN are ready, the controller is enabled.

# **Loop Control/Protection Logic**

It controls power-on/off sequence, protections, power state transition and PWM sequence.

#### DAC

The DAC generates a reference VID voltage according to the VID code sent by Control Logic. According to VID packets command, Control Logic dynamically changes VID voltage to the target voltage with required slew rate.

#### **ERROR AMP**

The ERROR AMP inverts and amplifies the difference between output voltage and VID with externally set finite DC gain. The output signal is COMP for PWM trigger.

# **PER CSGM**

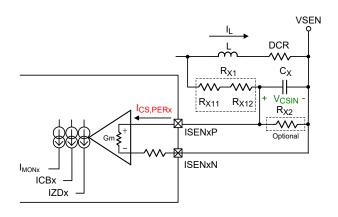

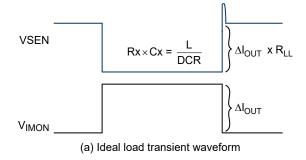

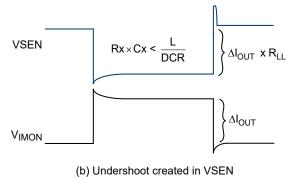

The PER CSGM senses per-phase inductor current. The outputs are used for loop response, current balance, zero current detection, current reporting and overcurrent protection.

#### **SUM CSGM**

The SUM CSGM senses total inductor current with RIMON gain adjustment. SUM CSGM output current ratio can also be set by NVM. It helps wide application range of DCR and load-line. SUM CSGM output is used for PWM trigger.

#### **RAMP**

The RAMP helps loop stability and transient response.

#### **PWM CMP**

The PWM comparator compares COMP signal with sum current signal based on RAMP to trigger PWM.

#### **Offset Cancellation**

The offset cancellation is based on VID, COMP voltage and current signal from SUM CSGM to control output voltage accurately.

#### **Current Balance**

Per-phase current sense signal is compared with sensed average current. The comparison result adjusts each phase PWM width to optimize current and thermal balance.

#### **Zero Current Detection**

Detects whether each phase current crosses zero current. The result is used for DEM power saving and overshoot reduction (anti-overshoot function).

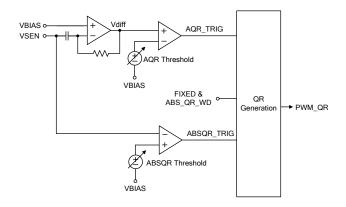

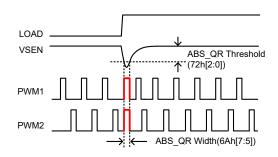

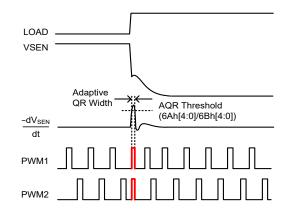

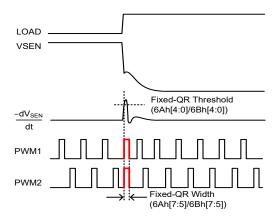

# AQR, Fixed-QR, ABS\_QR, ANTI-OVS, and ABS\_OVS

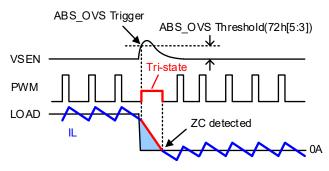

The AQR is a new generation of quick response mechanism (Adaptive Quick Response, AQR) which detects loading rising edge and allows all PWMs to turn on. The PWM pulse width triggered by AQR is adaptive to loading level. The AQR trigger level can be set by NVM. ANTI-OVS can help overshoot reduction which detects loading falling edge and forces all PWMs in tristate until the zero current is detected.

#### **TONGEN and Driver Interface**

The PWM comparator output signal triggers TONGEN to generate PWM pulse. The PWM sequence is controlled by Loop Control. The PWM pulse width is determined by frequency setting, current balance output and Adaptive Quick Response (AQR) settings. Once AQR is triggered, VR allows all PWM to turn on at the same time. Driver interface provides high/low/tri-state to

**RICHTEK**

drive external driver. In power saving mode, driver interface forces PWM in tri-state to turn off high-side and low-side power MOSFET according to zero current detection output. In addition, the PWM state is controlled by protection logic. Different protections force required PWM state.

# VCC\_UVLO, OVP, UVP, SSOCP, OCP, OTP, OCP Warning, VR-HOT Warning, CRC Failure, and Communication Failure

The RT3678BE includes the following protections: VCC undervoltage lockout, overvoltage protection, undervoltage protection, soft-start overcurrent protection, overcurrent protection, overcurrent warning, VR-Hot warning, CRC. failure, and Communication Failure.

# **Absolute Maximum Ratings** (Note 1)

| • VIN to GND                          | 0.3V to 28V      |

|---------------------------------------|------------------|

| • VCC to GND                          | -0.3V to 6.5V    |

| • RGND to GND                         | -0.3V to 0.3V    |

| • Other Pins                          | -0.3V to 6.8V    |

| Lead Temperature (Soldering, 10 sec.) | - 260°C          |

| • Junction Temperature                | - 150°C          |

| Storage Temperature Range             | - −65°C to 150°C |

|                                       |                  |

# **ESD Ratings** (Note 2)

• HBM (Human Body Model) ------ 2kV

# **Recommended Operating Conditions** (Note 3)

| • | VIN to GND                 | 4.5V to 24V    |

|---|----------------------------|----------------|

| • | Supply Input Voltage, VCC  | 4.5V to 5.5V   |

| • | Junction Temperature Range | –40°C to 125°C |

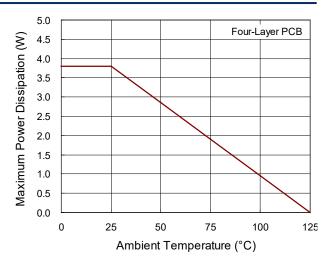

# **Thermal Information** (Note 4)

| • | WQFN-68L 8x8, $\theta$ JA | 26.3°C/W |

|---|---------------------------|----------|

| • | WQFN-68L 8x8, θJC(Top)    | 9.5°C/W  |

# **Electrical Characteristics**

(V<sub>CC</sub> = 5V, V<sub>VDDIO</sub> = 1.8V, typical values are referenced to T<sub>J</sub> = 25°C, Min. and Max. values are referenced to T<sub>J</sub> from -10°C to 105°C, unless otherwise specified)

| Parameter              | Symbol          | Test Conditions                           |           | Тур  | Max  | Unit |  |

|------------------------|-----------------|-------------------------------------------|-----------|------|------|------|--|

| Supply Input           |                 |                                           |           |      |      |      |  |

| Supply Voltage         | Vcc             |                                           | 4.5       |      | 5.5  | V    |  |

| Supply Current         | Ivec            | VCC = 5V, PWREN = H, no switching         |           |      | 40   | mA   |  |

| Supply Current at PSI6 | Ivcc_psi6       | VCC = 5V, PWREN = H, in<br>PSI6           |           |      | 180  | μΑ   |  |

| Shutdown Current ISHDN |                 | VCC = 5V, PWREN = L                       |           |      | 180  | μА   |  |

| VCC Power-ON Reset     | VCC_POR_R       | Rising edge                               | 4.2       | 4.32 | 4.45 | V    |  |

| (POR)                  | ΔVCC_POR_HYS    | Hysteresis                                |           | 170  |      | mV   |  |

| VCC Power-ON Reset     | VCC_POR_NVM_R   | Rising edge                               |           | 3.6  | 3.75 | V    |  |

| for NVM (POR_NVM)      | VCC_POR_NVM_F   | Falling edge                              | 3.32      | 3.47 |      |      |  |

| Reference and DAC      |                 |                                           |           |      |      |      |  |

| DAC Accuracy           | V <sub>FB</sub> | 0.250 to 0.995 T <sub>A</sub> = 0 to 85°C | <b>-5</b> |      | 5    | mV   |  |

| DAC Accuracy           | VFB             | 1.000 to 2.800 T <sub>A</sub> = 0 to 85°C |           | 0.5  | %    |      |  |

| Parameter                 |               | Symbol             | Test Conditions                                                        | Min    | Тур  | Max    | Unit  |

|---------------------------|---------------|--------------------|------------------------------------------------------------------------|--------|------|--------|-------|

| Slew Rate                 |               |                    |                                                                        |        |      |        |       |

| VOTF<br>Slew Rate         | Up            | UP_SR              | Measure VFB from 20% target VID to 80% target VID with ΔVOTF ≥ 100mV   | -10%   |      | 10%    | mV/μs |

|                           | Down          | DN_SR              | Default equals to UP_SR                                                | -10%   |      | 10%    |       |

| Current Se                | nsing Amplif  | ier                |                                                                        |        |      |        |       |

| CS Input Vo               | oltage Range  | Vcsin              | Differential voltage range of DCR sense.                               | -10    |      | 80     | mV    |

| Current Ser<br>Error      | nse Gain      | AMIRROR            | Internal current mirror gain of per phase current sense IIMON/ICS,PERx | 1.2125 | 1.25 | 1.2875 | A/A   |

| ton Setting               |               |                    | <del></del>                                                            |        |      |        |       |

| On-Time                   | Rail A        | ton                | VIN = 12V, VID = 1V,<br>KTON = 0.8V                                    |        | 208  |        | ns    |

| Setting                   | Rail B        |                    | VIN = 12V, VID = 1V,<br>KTON = 0.8V                                    |        | 208  |        | ns    |

| Minimum                   | Rail A        | ton Min            |                                                                        |        | 70   |        | ns    |

| On-Time                   | Rail B        | ton_min            |                                                                        |        | 70   |        | ns    |

| Protection                | s             | 1                  |                                                                        | •      |      | l      |       |

| Overvoltage<br>Threshold  | e Protection  | Vov                | Default threshold                                                      | 315    | 350  | 385    | mV    |

| De-bounce                 | Time of OVP   | tD_OVP             |                                                                        |        | 0.8  |        | μS    |

| Undervoltaç<br>Threshold  | ge Protection | Vuv                | Default threshold                                                      | 315    | 350  | 385    | mV    |

| De-bounce                 | Time of UVP   | t <sub>D_UVP</sub> |                                                                        |        | 3.3  |        | μS    |

| Overcurren<br>Threshold   | t Protection  | Vocp               |                                                                        | -3     |      | 3      | %     |

| Overcurren<br>Threshold   | t Warning     | Voc_warn           |                                                                        | -3     |      | 3      | %     |

| Over-Temp<br>Protection   |               | Тотр               |                                                                        |        | 125  |        | °C    |

| VRHOT Wa<br>Threshold     | arning        | TVRHOT             |                                                                        |        | 100  |        | °C    |

| PWREN an                  | d PWRGD       |                    |                                                                        |        | •    |        |       |

| PWREN                     | Logic-High    | VIH_PWREN          |                                                                        | 1.17   | -    |        | V     |

| TWKEN                     | Logic-Low     | VIL_PWREN          |                                                                        |        |      | 0.63   | v     |

| Leakage Current of PWREN  |               | ILEAK_PWREN        |                                                                        | -1     |      | 1      | μА    |

| PWRGD Pull Low<br>Voltage |               | Vpwrgd             | IPWRGD = 8mA                                                           |        |      | 0.2    | V     |

| VR_HOT#                   |               | ı                  | <b>'</b>                                                               |        |      |        |       |

| VR_HOT# I<br>Voltage      | Pull Low      | VVR_HOT#           | I <sub>VR_HOT#</sub> = 8mA                                             |        |      | 0.2    | V     |

| Para                                                       | ameter                         | Symbol      | Test Conditions  | Min             | Тур | Max             | Unit   |

|------------------------------------------------------------|--------------------------------|-------------|------------------|-----------------|-----|-----------------|--------|

| VREF                                                       |                                | <u> </u>    |                  | 1               |     | ı               |        |

| VREF Volta                                                 | age                            | VVREF       | Normal operation | 0.59            | 0.6 | 0.61            | V      |

| Acoustic N                                                 | loise Suppres                  | sion (ANS)  |                  | 1               |     |                 |        |

| ANS_EN                                                     | Logic-High                     | VIH_ANS_EN  |                  | Vcc -<br>0.7    |     |                 | V      |

| /                                                          | Logic-Low                      | VIL_ANS_EN  |                  |                 |     | 1               | V      |

| SVI3 Interf                                                | ace                            |             |                  |                 |     |                 |        |

| VDDIO Lev                                                  | el                             | VDDIO       |                  | 1.08            |     | 1.98            | V      |

| SVC,                                                       | Logic-High                     | ViH         |                  | 0.65 x<br>VDDIO |     |                 | V      |

| SVD, SVTI                                                  | Logic-Low                      | VIL         |                  |                 | -   | 0.35 x<br>VDDIO | V      |

| SVC, SVD,                                                  |                                | Vон         | I = -8mA         | VDDIO<br>- 0.45 |     |                 | V      |

| Output High                                                | n Voltage                      | VOIT        | I = -4mA         | VDDIO<br>- 0.22 |     |                 | V      |

| SVC, SVD,                                                  | VD. SVTO                       | 1/          | I = 8mA          |                 |     | 0.45            | V      |

| Output Low                                                 |                                | Vol         | I = 4mA          |                 |     | 0.22            | V      |

| DECET I                                                    | Logic-High                     | VIH_RESET_L |                  | 1.17            |     |                 | V      |

| RESET_L                                                    | Logic-Low                      | VIL_RESET_L |                  |                 |     | 0.63            | V      |

| Leakage Co<br>SVC, SVD,<br>SVTO                            |                                | ILEAK_SVI3  |                  | -10             |     | 10              | μΑ     |

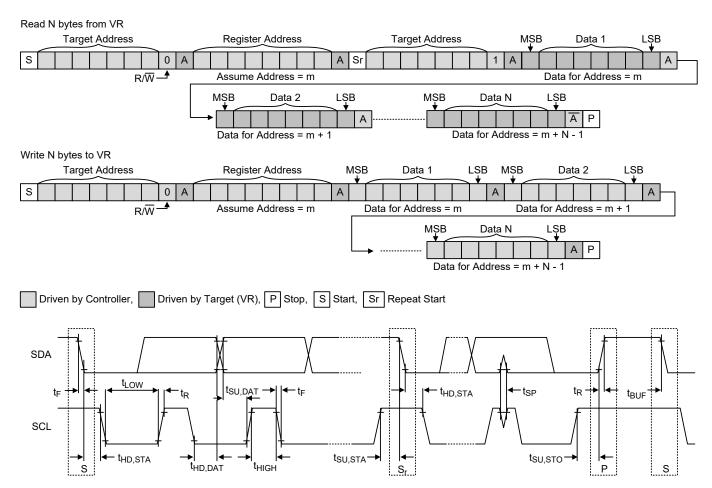

| I <sup>2</sup> C interfac                                  | ce                             |             |                  |                 |     |                 |        |

| CCL CDA                                                    | Logic-High                     | VIH_I2C     |                  | 1               |     |                 | V      |

| SCL, SDA                                                   | Logic-Low                      | VIL_I2C     |                  |                 |     | 0.6             | V      |

| Standard/F                                                 | ast Mode                       |             |                  | 1               |     |                 |        |

| 001.01.1                                                   | D. L.                          | fscL        | Standard mode    |                 |     | 100             | 1.1.1. |

| SCL Clock                                                  | Rate                           |             | Fast mode        |                 |     | 400             | kHz    |

| Hold Time (<br>Start Condi<br>this period,<br>pulse is ger | tion. After<br>the first clock | thd_sta     |                  | 0.6             |     |                 | μs     |

| Low Period of SCL<br>Clock                                 |                                | tLOW        |                  | 1.3             |     |                 | μS     |

| High Period of SCL<br>Clock                                |                                | thigh       |                  | 0.6             |     |                 | μS     |

| Set-Up Time for a<br>Repeated START<br>Condition           |                                | tsu_sta     |                  | 0.6             | -1  |                 | μS     |

| Data Hold                                                  |                                | tup pat     | Standard mode    | 0               | -   |                 |        |

| Dala ⊓Ulu                                                  | IIC                            | thd_dat     | Fast mode        | 0               |     | 0.9             | μS     |

| Data Set-U                                                 | n Time                         | tsu_dat     | Standard mode    | 250             |     |                 | ns     |

|                                                            | P 11110                        | 100_DA1     | Fast mode        | 100             |     |                 | 113    |

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

DS3678BE-00 March 2023 www.richtek.com

| Parameter                                                     | Symbol    | Test Conditions                           | Min           | Тур  | Max  | Unit    |  |

|---------------------------------------------------------------|-----------|-------------------------------------------|---------------|------|------|---------|--|

| Set-Up Time for STOP Condition                                | tsu_sto   |                                           | 0.6           |      |      | μs      |  |

| Bus Free Time Between<br>STOP and START<br>Condition          | tBUF      |                                           | 1.3           |      | 1    | μs      |  |

| Rising Time of Both SDA                                       | tR        | Standard mode                             |               |      | 300  | 20      |  |

| and CL Signals                                                | IR .      | Fast mode                                 | 20            |      | 300  | ns      |  |

| Falling Time of Both SDA                                      | <b>t-</b> | Standard mode                             |               |      | 300  |         |  |

| and SCL signals                                               | tF        | Fast mode                                 | 20            |      | 300  | ns      |  |

| SDA Output Low Sink<br>Current                                | loL       | SDA voltage = 0.4V                        | 2             |      |      | mA      |  |

| ADC                                                           |           |                                           |               |      |      |         |  |

| ADC Resolution                                                |           |                                           |               | 10   |      | bits    |  |

| ADC Reference Voltage                                         |           |                                           |               | 3.2  |      | V       |  |

| PWM Driving Capability                                        |           |                                           |               |      |      |         |  |

| PWM Source Resistance                                         | RPWM_SRC  |                                           |               | 30   |      | Ω       |  |

| PWM Sink Resistance RPWM_SNK                                  |           |                                           |               | 10   |      | Ω       |  |

| PWM Output                                                    |           |                                           |               |      |      |         |  |

| PWMx Output High<br>Level                                     |           | IOUT = 4mA                                | VCC<br>- 0.16 |      |      | \<br>\  |  |

| PWMx Output Low Level                                         |           | IOUT = 4mA                                |               |      | 0.08 |         |  |

| ITSEN                                                         |           |                                           | L             | I    |      |         |  |

| TSEN Source Current                                           | ITSEN     | VTSEN = 1.6V                              | 79.2          | 80   | 80.8 | μА      |  |

| PSYS and DIMON                                                |           |                                           |               | •    |      |         |  |

| Digital PSYS Reporting                                        | DPSYS     | VPSYS = 1.6V                              |               | 1023 |      | Decimal |  |

| Digital IMON of Rail A                                        | DVIMONA   | VIMONA - VVREF = 0.4V                     |               | 1023 |      | Decimal |  |

| Digital IMON of Rail B                                        | DVIMONB   | VIMONB - VVREF = 0.4V                     |               | 1023 |      | Decimal |  |

| Telemetry                                                     |           |                                           |               |      |      |         |  |

| Accuracy of Output<br>Voltage Telemetry                       | VOUTTEL   | 0.250 to 0.995 T <sub>A</sub> = 0 to 85°C | -7.5          |      | 7.5  | mV      |  |

| (10-bit Telemetry, 1LSB = 5mV)                                | VOUTIEL   | 1.000 to 2.800 T <sub>A</sub> = 0 to 85°C | -0.75         |      | 0.75 | %       |  |

| Temperature Reporting Accuracy (10-bit Telemetry, 1LSB = 1°C) | TEMPTEL   | Between 50°C to 125°C                     | -5            |      | 5    | °C      |  |

| Temperature Reporting Range                                   |           |                                           | -40           |      | 150  | °C      |  |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2. Devices are ESD sensitive. Handling precautions are recommended.

- Note 3. The device is not guaranteed to function outside its operating conditions.

- Note 4. For more information about thermal parameters, see the Application and Definition of Thermal Resistances report, AN061.

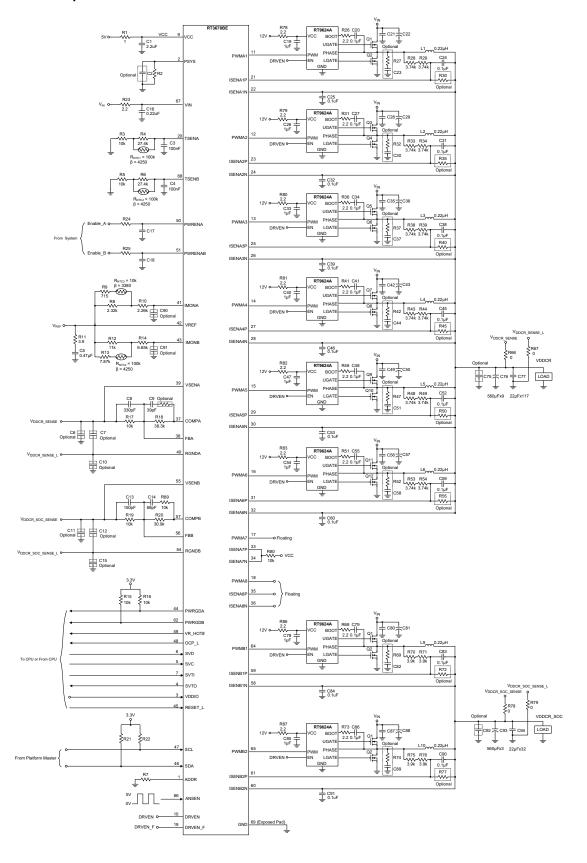

# **Typical Application Circuit**

Platform: AM5 Group A-170W

March 2023

DS3678BE-00

# **Typical Operating Characteristics**

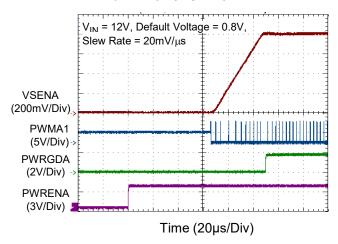

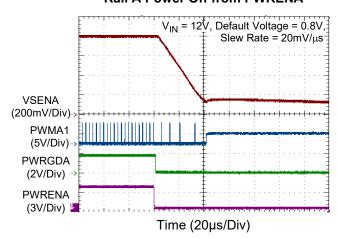

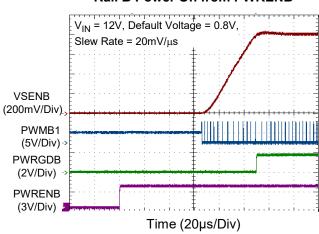

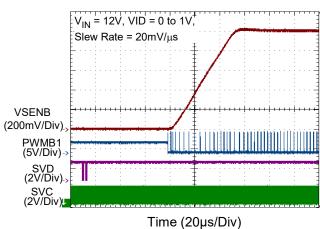

#### Rail A Power On from PWRENA

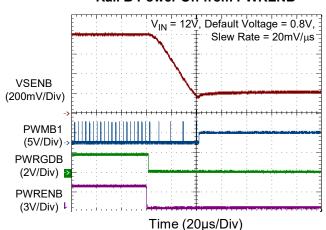

# Rail A Power Off from PWRENA

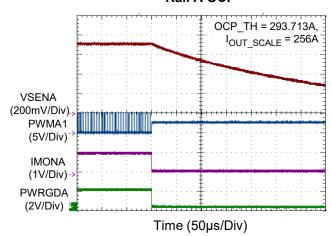

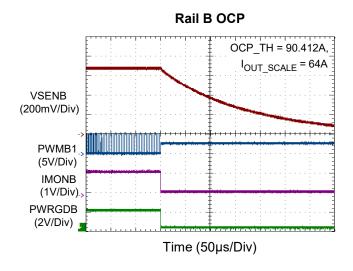

Rail A OCP

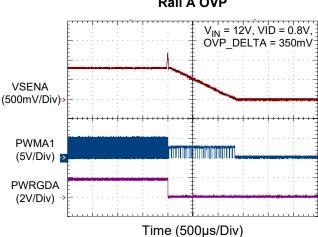

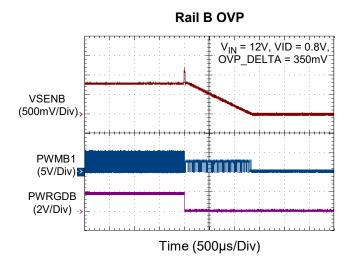

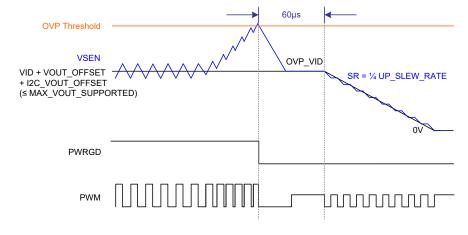

Rail A OVP

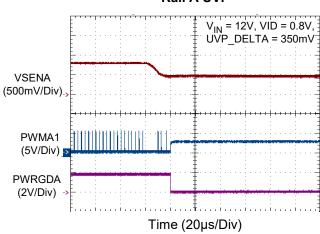

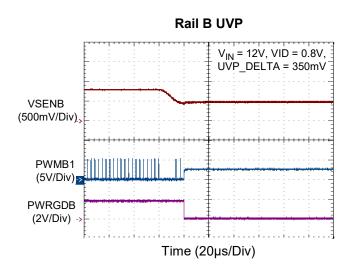

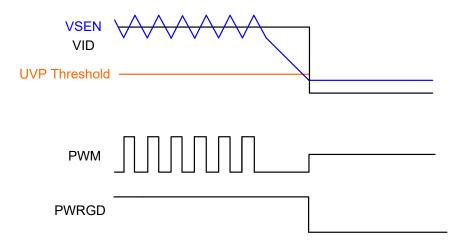

Rail A UVP

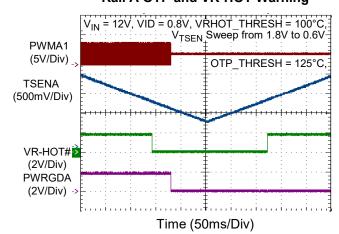

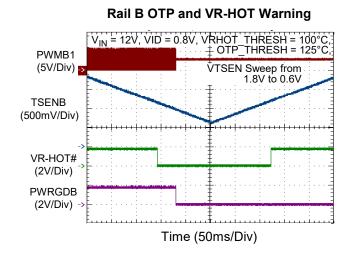

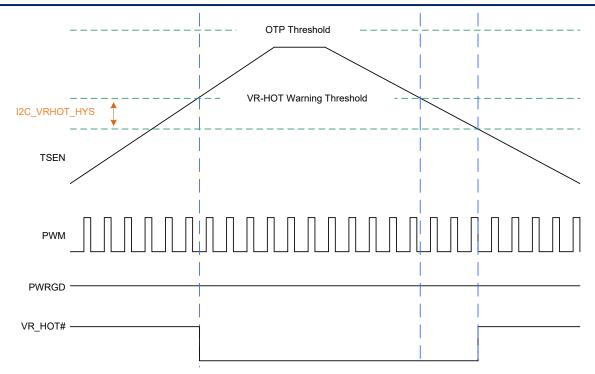

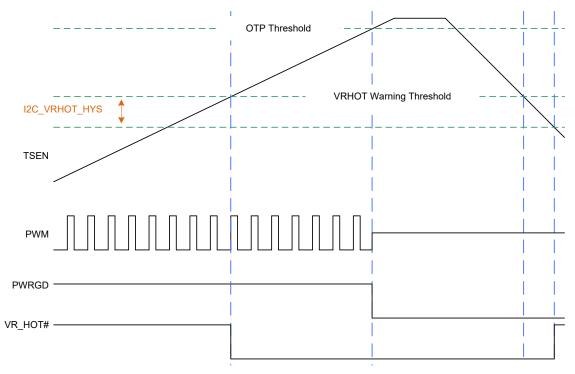

Rail A OTP and VR-HOT Warning

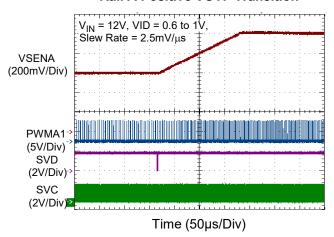

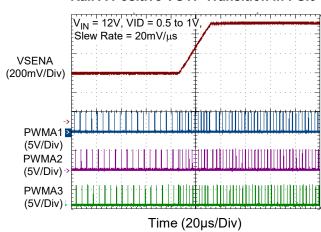

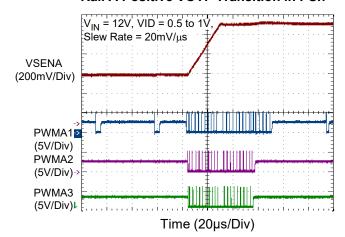

# **Rail A Positive VOTF Transition**

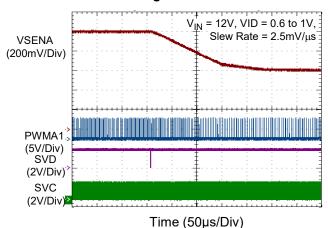

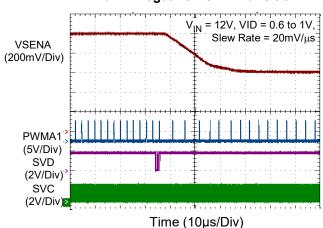

# Rail A Negative VOTF Transition

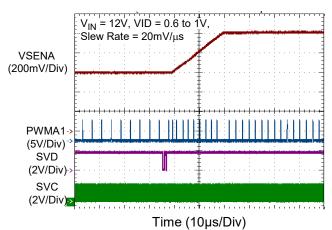

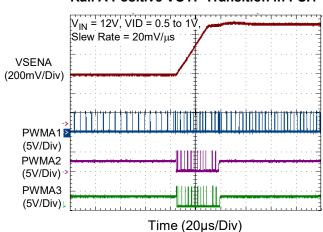

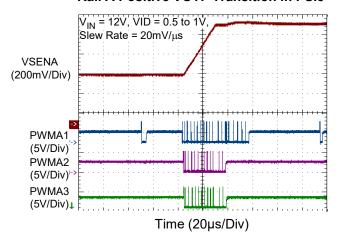

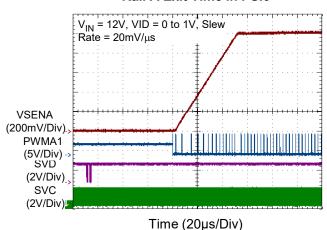

# **Rail A Positive VOTF Transition**

**Rail A Negative VOTF Transition**

# **Rail A Positive VOTF Transition in PSI0**

# **Rail A Positive VOTF Transition in PSI1**

RICHTEK is a

is a registered trademark of Richtek Technology Corporation.

#### Rail A Positive VOTF Transition in PSI3

#### Rail A Positive VOTF Transition in PSI7

Rail A Exit Time in PSI6

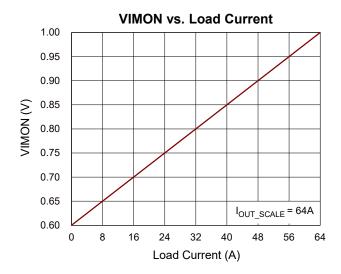

**VIMON vs. Load Current** 1.00 0.95 0.90 0.85 0.80 0.75 0.70 0.65 I<sub>OUT SCALE</sub> = 256A 0.60 32 64 128 160 192 224 Load Current (A)

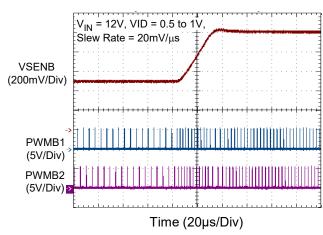

**Rail B Power On from PWRENB**

Rail B Power Off from PWRENB

RICHTEK

is a registered trademark of Richtek Technology Corporation.

March 2023

DS3678BE-00

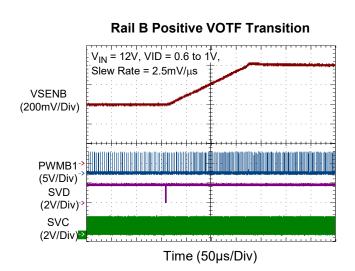

# **Rail B Positive VOTF Transition**

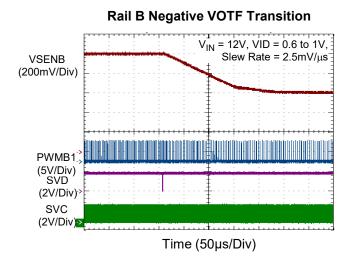

# **Rail B Negative VOTF Transition**

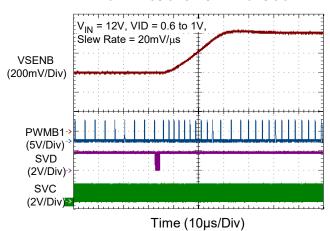

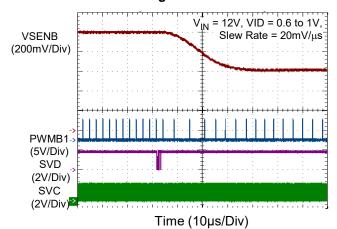

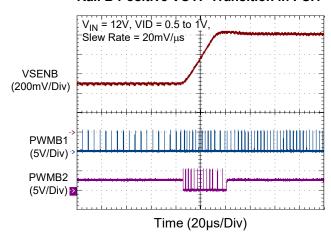

# **Rail B Positive VOTF Transition in PSI0**

# **Rail B Positive VOTF Transition in PSI1**

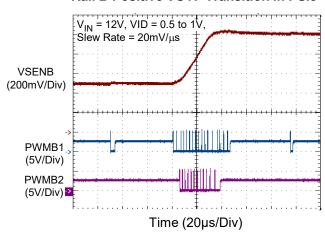

# **Rail B Positive VOTF Transition in PSI3**

# Rail B Positive VOTF Transition in PSI7

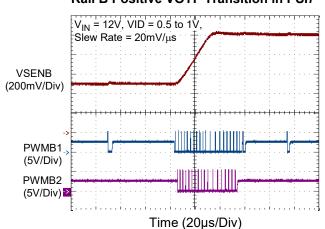

# Rail B Exit Time in PSI6

# **Application Information**

Richtek's component specification does not include the following information in the Application Information section. Thereby no warranty is given regarding its validity and accuracy. Customers should take responsibility to verify their own designs and to ensure the functional suitability of their components and systems.

The RT3678BE is a 8-phase + 2-phase synchronous buck controller that supports two voltage rails. The RT3678BE is designed to meet AMD SVI3 compatible CPUs specification. The controller provides built-in non-volatile memory (NVM) and I<sup>2</sup>C interface to store customized configuration. The RT3678BE is designed for notebook computers or desktop applications

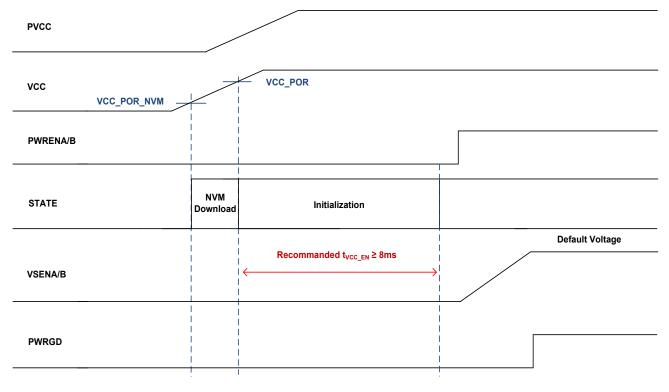

#### **Power-ON Sequence**

Supply a single +5.0V (VCC) to the RT3678BE to start power-on. Figure 2 shows the power-on timings. NVM loading of the RT3678BE begins after VCC crosses its rising VCC\_POR\_NVM threshold. When POR\_NVM conditions are met, RT3678BE will download NVM into the control registers. When VCC exceeds VCC\_POR, the RT3678BE starts initialization including internal circuit offset correction and function settings. During this

period, the PWM outputs are held in high impedance (Hi-Z) state. Set the correct default levels for static input signals with pull-down resistors (such as for the I2C address setting). The time from VCC exceeding VCC\_POR threshold to assertion of PWREN is tvcc\_EN. The minimum tvcc\_EN is 8ms. When initialization is done, the controller is in ultra-low power mode. It will ramp up to default voltage with default slew rate when PWREN is high. When the start-up process is completed, PWRGD is asserted within  $5\mu s$  after the output voltage exceeds minimum tolerance of output voltage. Users can set multi-functions through NVM by  $I^2C$  interface when initialization is done.

Driver power (PVCC) is strongly suggested to be ready after controller VCC. This can prevent current flowing back from driver PVCC to controller VCC through PWMx pins or DRVEN/DRVEN F pins.

Figure 2. Typical Timing of Controller Power-ON

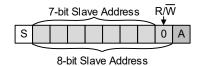

# I<sup>2</sup>C Address Setting

The RT3678BE provides multiple  $I^2C$  address to support multiple devices connected in one  $I^2C$  bus. To properly set the  $I^2C$  address (7-bit and 8-bit format), resistors with 1% tolerance must be connected from ADDR pin to ground. The required resistance is listed in Table 1. The controller sends the first target address

followed by write bit (0b). For example, the 8-bit target address combines 7-bit address and write bit (0b):

Table 1. I<sup>2</sup>C Address (HEX)

| Resistance (kΩ) | I <sup>2</sup> C Address | I <sup>2</sup> C Address |

|-----------------|--------------------------|--------------------------|

| Тур.            | 7bit (Hex)               | 8-bit (Hex)              |

| 0.309           | 40                       | 80                       |

| 0.931           | 41                       | 82                       |

| 1.54            | 42                       | 84                       |

| 2.15            | 43                       | 86                       |

| 3.09            | 50                       | A0                       |

| 4.64            | 51                       | A2                       |

| 4.99            | 52                       | A4                       |

| 5.9             | 53                       | A6                       |

| 6.81            | 60                       | C0                       |

| 8.06            | 61                       | C2                       |

| 9.31            | 62                       | C4                       |

| 10.7            | 63                       | C6                       |

| 11.8            | 70                       | E0                       |

| 13.7            | 71                       | E2                       |

| 15.8            | 72                       | E4                       |

| 17.4            | 73                       | E6                       |

# **Acoustic Noise Suppression**

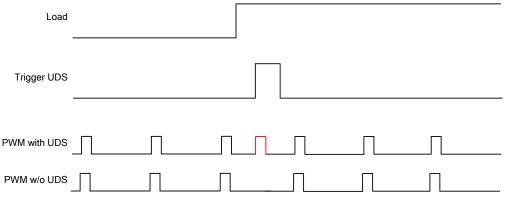

The RT3678BE supports acoustic noise suppression function for reducing acoustic noise induced by piezoelectric effect from MLCC. As output voltage transition occurs, especially in dynamic VID, the vibrating MLCC produces acoustic noise if the vibrating frequency falls into audible band; the noise level is related to the output voltage transition amplitude  $\Delta V$ . Therefore, the RT3678BE adopts acoustic noise suppression function enabled by pulling ANS\_EN pin to VCC to reduce  $\Delta V$  during negative VOTF (Voltage Onthe-Fly).

# **Maximum Active Phase Number Setting**

The number of active phases is determined by ISENxP voltage. The detection is only active and latched at initialization state. When ISENxP voltage > (VCC-0.5V), the maximum active phase number is (x-1). For example, pulling ISENA7P and ISENA7N to VCC programs 6-phase operation. It is suggested that the unused pins (such as ISENxN, PWMx pins) can be left floating. Figure 3 is a 6-phase operation example.

# Rail Disable

Pulling ISENA1P and ISENA1N to VCC disables the A rail. Pulling ISENB1P and ISENB1N to VCC disables the B rail. The unused pins (such as ISENXN, PWMX, VSEN, FB, COMP, IMON, TSEN, PWRGD and PWREN) can be left floating.

RICHTEK

Figure 3. 6-Phase Operation Setting

# **NVM Configuration Mechanism and SVI3 Registers**

The RT3678BE provides multiple parameters for platform setting and BOM optimization. These parameters can be set through NVM registers by the I<sup>2</sup>C interface. All setting functions are summarized in Table 2. Table 3 shows the functions that do not support online tuning. Table 4 shows the data and SVI3 registers for the SVI3 protocol. Table 5 shows the VID table of type 1 target.

22

# Table 2. Summary of Setting Functions (Page 02)

# **Setting Register Map (Page 02)**

|     | Register Address/Name                                       | Туре | Default<br>Value | Note                                                                                                                                                                | NVM |

|-----|-------------------------------------------------------------|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 00h | PWM_TRI_STATE_LEVEL & TARGET_SEQ                            | R/W  | 02h              | PWM tri-state window = 1.6V~2.2V,<br>SVI3 target sequence = A → B.                                                                                                  | Yes |

| 01h | P_SYS_MAX & P_SYS_EN & P_SYS_SCALE                          | R/W  | 0Ch              | P_SYS_MAX = 1.6V, System power telemetry enabled, P_SYS_SCALE = Scale 4: 256W                                                                                       | Yes |

| 10h | CODE_VERSION_L                                              | R/W  | 00h              | NVM code version low byte                                                                                                                                           | Yes |

| 11h | CODE_VERSION_H                                              | R/W  | 00h              | NVM code version high byte                                                                                                                                          | Yes |

| 20h | VID_DEFAULT_VOLTAGE_A                                       | R/W  | 48h              | VID_DEFAULT_VOLTAGE_A = 0.8V                                                                                                                                        | Yes |

| 21h | RESERVED                                                    | R/W  | 8Ch              | RESERVED                                                                                                                                                            | Yes |

| 22h | RESERVED                                                    | R/W  | 32h              | RESERVED                                                                                                                                                            | Yes |

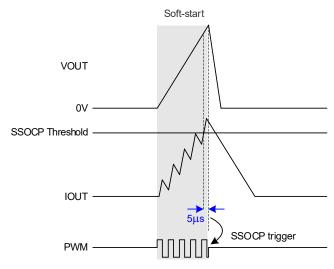

| 24h | SSOCP_EN_A & RATIO_A & I_OUT_SCALE_A                        | R/W  | A4h              | Soft-start OCP enabled for rail A,<br>SSOCP_RATIO_A = 2.1875,<br>I_OUT_SCALE_A = Scale 4: 255.75A.                                                                  | Yes |

| 25h | EN_0LL_A & AI_GAIN_A                                        | R/W  | 50h              | Zero load-line disable for A rail,<br>Al_GAIN_A = 0.25.                                                                                                             | Yes |

| 26h | ZCD_TH_A                                                    | R/W  | E4h              | ZCD_TH_A = -0.8332mV                                                                                                                                                | Yes |

| 27h | KTON_A                                                      | R/W  | 04h              | KTON_A = 0.7                                                                                                                                                        | Yes |

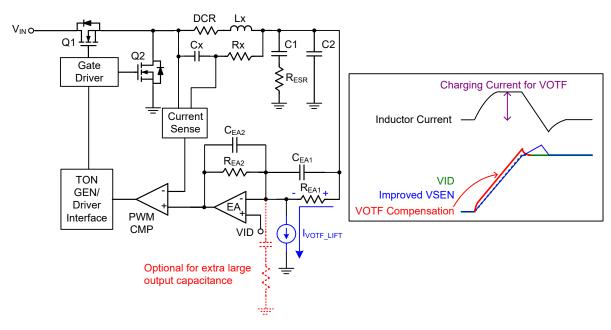

| 28h | ANTI-OVS_A & VOTF_LIFT_A                                    | R/W  | E3h              | Anti-overshoot disabled for rail A, VOTF_LIFT_A = $3\mu$ A.                                                                                                         | Yes |

| 29h | LPF_LIMIT_MUTI_PH_A & SINGLE_PH_A                           | R/W  | 63h              | LPF_LIMIT_MUTI_PH_A = 220mV for rail A, LPF_LIMIT_SINGLE_PH_A = 80mV for rail A.                                                                                    | Yes |

| 2Ah | FIXED_QR_WD_A & QR_TH_A                                     | R/W  | 7Fh              | PWM pulse = $1.25 \times t_{ON}$ , QR with multi-phase disabled for rail A.                                                                                         | Yes |

| 2Bh | FIXED_QR_WD_1PH_A & QR_TH_1PH_A                             | R/W  | 7Fh              | PWM pulse = $1.25 \times ton$ ,<br>QR with single phase disabled for rail A.                                                                                        | Yes |

| 2Ch | AR_TH_1PH_A & EN_EXTD_TON_A & EXTD_TON_TH_A & EXTD_WD_MAX_A | R/W  | 62h              | Adaptive ramp threshold for rail A = Disabled, $t_{ON}$ extend disabled for rail A, $t_{ON}$ extend threshold = 150mV, $t_{ON}$ max extend width = 1.375 × $t_{ON}$ | Yes |

| 2Dh | RESERVED                                                    | R/W  | 00h              | RESERVED                                                                                                                                                            | Yes |

| 2Eh | RESERVED                                                    | R/W  | 00h              | RESERVED                                                                                                                                                            | Yes |

| 2Fh | RESERVED                                                    | R/W  | 8Ch              | RESERVED                                                                                                                                                            | Yes |

| 30h | MIN_TOFF_A & QR_SEL_A & QR_SEL_1PH_A                        | R/W  | FAh              | MIN_TOFF_A = 50ns,<br>QR_SEL_A = AQR,<br>QR_SEL_1PH_A = AQR.                                                                                                        | Yes |

| 31h | EAGM_GAIN_A & SLL_RATIO_A & TSEN_SEL_A                      | R/W  | 00h              | EAGM_GAIN_A = 2/3,<br>SLL_RATIO_A = 100%,<br>TSEN_SEL_A = External NTC thermistor.                                                                                  | Yes |

| 32h | RESERVED                                                    | R/W  | 00h              | RESERVED                                                                                                                                                            | Yes |

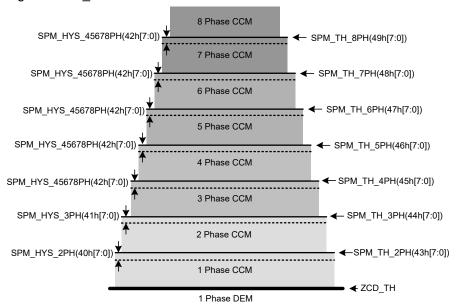

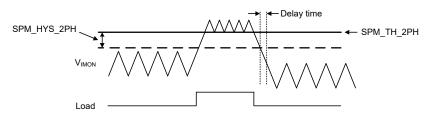

| 40h | SPM_HYS_2PH_A                                               | R/W  | 03h              | SPM_HYS_2PH_A = 4A                                                                                                                                                  | Yes |

| 41h | SPM_HYS_3PH_A                                               | R/W  | 02h              | SPM_HYS_2PH_A = 2.66A                                                                                                                                               | Yes |

| 42h | SPM_HYS_45678PH_A                                           | R/W  | 02h              | SPM_HYS_45678PH_A = 2.66A                                                                                                                                           | Yes |

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

is a registered trademark of Richtek Technology Corporation.

|      | Register Address/Name                                                                       | Туре      | Default<br>Value | Note                                                                    | NVM |

|------|---------------------------------------------------------------------------------------------|-----------|------------------|-------------------------------------------------------------------------|-----|

| 43h  | SPM_TH_2PH_A                                                                                | R/W       | 0Dh              | SPM_TH_2PH_A = 17.32A                                                   | Yes |

| 44h  | SPM_TH_3PH_A                                                                                | R/W       | 12h              | SPM_TH_3PH_A = 23.98A                                                   | Yes |

| 45h  | SPM_TH_4PH_A                                                                                | R/W       | 19h              | SPM_TH_4PH_A = 33.3A                                                    | Yes |

| 46h  | SPM_TH_5PH_A                                                                                | R/W       | 22h              | SPM_TH_5PH_A = 45.29A                                                   | Yes |

| 47h  | SPM_TH_6PH_A                                                                                | R/W       | 2Ah              | SPM_TH_6PH_A = 55.95A                                                   | Yes |

| 48h  | SPM_TH_7PH_A                                                                                | R/W       | 2Fh              | SPM_TH_7PH_A = 62.61A                                                   | Yes |

| 49h  | SPM_TH_8PH_A                                                                                | R/W       | 38h              | SPM_TH_8PH_A = 74.59A                                                   | Yes |

| 4Ah  | IOUT_CAL_OFFSET_A                                                                           | R/W       | 00h              | IOUT_CAL_OFFSET_A = 0 LSB                                               | Yes |

| 4Bh  | IOUT_CAL_GAIN_A                                                                             | R/W       | 80h              | IOUT_CAL_GAIN_A = 100%                                                  | Yes |

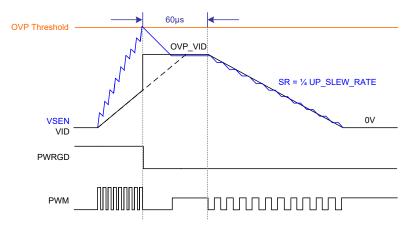

| 50h  | SVI3_20h_DECAY_CONDITION<br>S_A<br>SVI3_20h_DOWN_SLEW_RATE<br>_A<br>SVI3_20h_UP_SLEW_RATE_A | R/W       | 07h              | Please refer to SVI3 specification.<br>SVI3_20h_UP_SLEW_RATE_A= 20mV/μs | Yes |

| 51h  | SVI3_21h_LL_ADJUST_A                                                                        | R/W       | 0Ah              | Please refer to SVI3 specification.                                     | Yes |

| 52h  | SVI3_22h_VOUT_OFFSET_A                                                                      | R/W       | 00h              | No offset.                                                              | Yes |

| 53h  | SVI3_23h_VID_MAX_A                                                                          | R/W       | 00h              | Please refer to SVI3 specification.                                     | Yes |

| 54h  | SVI3_24h_VID_MIN_A                                                                          | R/W       | 00h              | Please refer to SVI3 specification.                                     | Yes |

| 55h  | SVI3_25h_TEN_BIT_TEL_EN_A                                                                   | R/W       | 00h              | Please refer to SVI3 specification.                                     | Yes |

| 56h  | SVI3_26h_SIXTEN_BIT_TEL_E<br>N_A                                                            | R/W       | 00h              | Please refer to SVI3 specification.                                     | Yes |

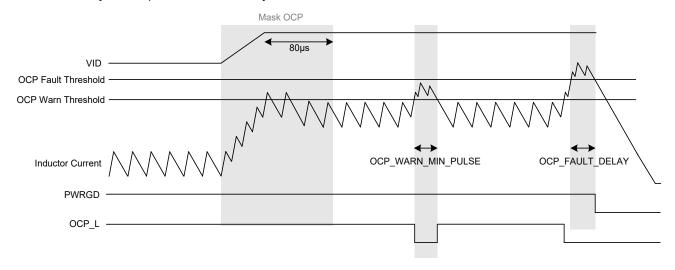

| 57h  | SVI3_27h_OCP_THRESH_A                                                                       | R/W       | 93h              | NVM configurable, based on platform                                     | Yes |

| 58h  | SVI3_28h_OCP_WARN_THRES<br>H_A                                                              | R/W       | 93h              | NVM configurable, based on platform                                     | Yes |

| 59h  | SVI3_29h_OCP_WARN_MIN_P<br>ULSE_A<br>SVI3_29h_OCP_FAULT_DELAY<br>_A                         | R/W       | 37h              | NVM configurable, based on platform                                     | Yes |

| 5Ah  | SVI3_2Ah_VRHOT_THRESH_A                                                                     | R/W       | 8Ch              | Please refer to SVI3 specification.                                     | Yes |

| 5Bh  | SVI3_2Bh_OTP_THRESH_A                                                                       | R/W       | A5h              | Please refer to SVI3 specification.                                     | Yes |

|      | SVI3_2Ch_OVP_REF_A                                                                          |           |                  |                                                                         |     |

| 5Ch  | SVI3_2Ch_OVP_DELTA_A                                                                        | R/W       | 66h              | Places refer to SVI2 appointment                                        | Voc |

| 3011 | SVI3_2Ch_UVP_REF_A                                                                          | EV VV     | 66h              | Please refer to SVI3 specification.                                     | Yes |

|      | SVI3_2Ch_UVP_DELTA_A                                                                        |           |                  |                                                                         |     |

| 5Dh  | SVI3_2Dh_PHASE_SHED_1_A                                                                     | R/W       | 11h              | Please refer to SVI3 specification.                                     | Yes |

| ווטט | SVI3_2Dh_PHASE_SHED_2_A                                                                     | 1 (7 ) (7 | 1 111            | Thease refer to OVIO specification.                                     | 163 |

|     | Register Address/Name                                       | Туре | Default<br>Value | Note                                                                                                                                                                   | NVM |

|-----|-------------------------------------------------------------|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 60h | VID_DEFAULT_VOLTAGE_B                                       | R/W  | 48h              | VID_DEFAULT_VOLTAGE_B = 0.8V                                                                                                                                           | Yes |

| 61h | RESERVED                                                    | R/W  | 8Ch              | RESERVED                                                                                                                                                               | Yes |

| 62h | RESERVED                                                    | R/W  | 32h              | RESERVED                                                                                                                                                               | Yes |

| 64h | SSOCP_EN_B & RATIO_B & I_OUT_SCALE_B                        | R/W  | B2h              | Soft-start OCP enabled for rail B,<br>SSOCP_RATIO_B = 2.5,<br>I_OUT_SCALE_B = Scale 2: 63.9375A.                                                                       | Yes |

| 65h | EN_OLL_B & AI_GAIN_B                                        | R/W  | E0h              | Zero load-line disable for B rail,<br>Al_GAIN_B = 0.25.                                                                                                                | Yes |

| 66h | ZCD_TH_B                                                    | R/W  | E2h              | ZCD_TH_B = -0.4166mV                                                                                                                                                   | Yes |

| 67h | KTON_B                                                      | R/W  | 44h              | KTON_B = 0.7                                                                                                                                                           | Yes |

| 68h | ANTI-OVS_B & VOTF_LIFT_B                                    | R/W  | 32h              | ANTI-OVS_B = 120mV<br>VOTF_LIFT_B = 3μA                                                                                                                                | Yes |

| 69h | LPF_LIMIT_MUTI_PH_B & SINGLE_PH_B                           | R/W  | 17h              | LPF_LIMIT_MUTI_PH_A = 80mV for rail B,<br>LPF_LIMIT_SINGLE_PH_A = 100mV for rail B.                                                                                    | Yes |

| 6Ah | FIXED&ABS_QR_WD_B & QR_TH_B                                 | R/W  | 7Fh              | PWM pulse = $1.25 \times \text{ton}$ , QR with multi-phase disabled for rail B.                                                                                        | Yes |

| 6Bh | FIXED_QR_WD_1PH_B & QR_TH_1PH_B                             | R/W  | 5Fh              | PWM pulse = $1 \times t_{ON}$ , QR with single phase disabled for rail B.                                                                                              | Yes |

| 6Ch | AR_TH_1PH_B & EN_EXTD_TON_B & EXTD_TON_TH_B & EXTD_WD_MAX_B | R/W  | 6Fh              | Adaptive ramp threshold for rail B = Disabled, ton extend disabled for rail B, ton extend threshold = $300\text{mV}$ , ton max extend width = $1.25 \times \text{ton}$ | Yes |

| 6Dh | RESERVED                                                    | R/W  | 0Ch              | RESERVED                                                                                                                                                               | Yes |

| 6Eh | RESERVED                                                    | R/W  | 00h              | RESERVED                                                                                                                                                               | Yes |

| 6Fh | RESERVED                                                    | R/W  | 8Ch              | RESERVED                                                                                                                                                               | Yes |

| 70h | MIN_TOFF_B & QR_SEL_B & QR_SEL_1PH_B                        | R/W  | FEh              | MIN_TOFF_B = 50ns,<br>QR_SEL_B = AQR,<br>QR_SEL_1PH_B = AQR.                                                                                                           | Yes |

| 71h | EAGM_GAIN_B & SLL_RATIO_B<br>& TSEN_SEL_B                   | R/W  | 80h              | EAGM_GAIN_B = 1,<br>SLL_RATIO_B = 100%,<br>TSEN_SEL_B = External NTC thermistor.                                                                                       | Yes |

| 72h | QR_TRIGGER_SEL &<br>ABSOVS_TH_B & ABS_QR_B                  | R/W  | 00h              | QR_TRIGGER_SE = Absolute (ABSQR),<br>Absolute-OVS disabled for rail B,<br>Absolute-QR disabled for rail B.                                                             | Yes |

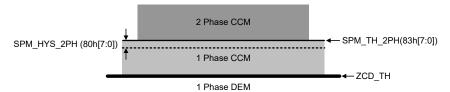

| 80h | SPM_HYS_2PH_B                                               | R/W  | 0Dh              | SPM_HYS_2PH = 4.33A                                                                                                                                                    | Yes |

| 83h | SPM_TH_2PH_B                                                | R/W  | 2Dh              | SPM_TH_2PH = 14.99A                                                                                                                                                    | Yes |

| 8Ah | IOUT_CAL_OFFSET_B                                           | R/W  | 00h              | IOUT_CAL_OFFSET_B = 0 LSB                                                                                                                                              | Yes |

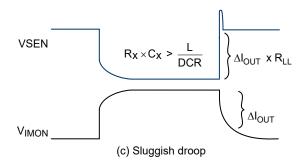

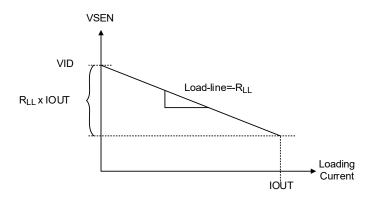

| 8Bh | IOUT_CAL_GAIN_B                                             | R/W  | 80h              | IOUT_CAL_GAIN_B = 100%                                                                                                                                                 | Yes |