## **RT5047BF**

## Single Output LNB Supply and Control Voltage Regulator

### **General Description**

The RT5047BF is a highly integrated voltage regulator and interface IC, specifically design for supplying power and control signals from advanced satellite set-top box (STB) modules to the LNB down-converter in the antenna dish or to the multi-switch box.

The device is consists of the independent current-mode boost controller and low dropout linear regulator along with the circuitry required for 22kHz tone shaping to support  $DiSEqC^{TM}1.x$  communications.

The RT5047BF has protection (over-current, over-temperature and under-voltage lockout).

The RT5047BF is available in a SOP-8 (Exposed Pad) package to achieve optimized solution for thermal dissipation.

### **Ordering Information**

RT5047BF 📮 📮

Package Type SP : SOP-8 (Exposed Pad-Option 2)

Lead Plating System

G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- ► RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

### Features

- Wide Input Supply Voltage Range : 8V to 16V

- Output Current Limit of 550mA with 6ms timer

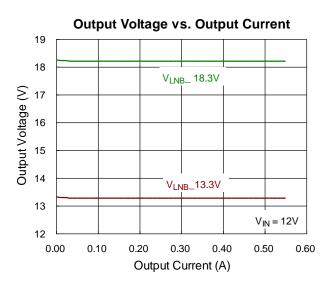

- Low Noise LNB Output Voltage (13.3V and 18.3V by SEL Pin)

- ±3% High Accuracy for 0mA to 500mA Current Output

- Push-Pull Output Stage Minimizes Output

Transition Time

- External 22kHz Tone Input

- Meet DiSEqC<sup>TM</sup>1.x Protocol

- Output Short Circuit Protection

- Over-Temperature Protection

### Applications

- LNB Power Supply and Control for Satellite Set-Top Box

- Analog and Digital Satellite Receivers/Satellite TV, Satellite PC cards

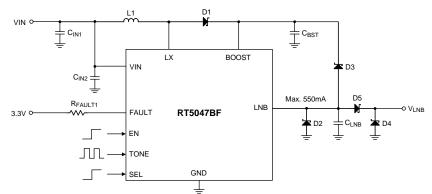

### **Simplified Application Circuit**

### **Marking Informaton**

RT5047BF GSPYMDNN RT5047BFGSP : Product Number YMDNN : Date Code

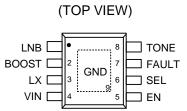

### **Pin Configuration**

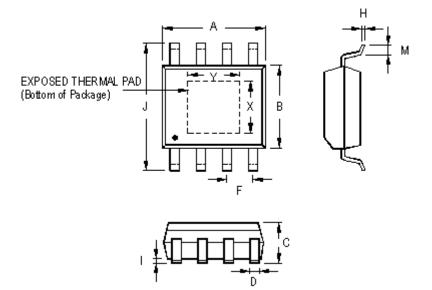

SOP-8 (Exposed Pad)

## **Functional Pin Description**

| Pin No.         | Pin Name | Pin Function                                                                                                |

|-----------------|----------|-------------------------------------------------------------------------------------------------------------|

| 1               | LNB      | Output voltage for LNB.                                                                                     |

| 2               | BOOST    | Boost output and tracking supply voltage to LNB.                                                            |

| 3               | LX       | Switching node of DC-DC boost converter.                                                                    |

| 4               | VIN      | Power supply input.                                                                                         |

| 5               | EN       | LNB output enable.                                                                                          |

| 6               | SEL      | LNB output voltage selection pin (Low is for 13.3V, high is for 18.3V).                                     |

| 7               | FAULT    | Fault detection pin. Pull to 3.3V by 4.7k $\Omega$ resistor.                                                |

| 8               | TONE     | 22kHz TONE input.                                                                                           |

| 9 (Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation. |

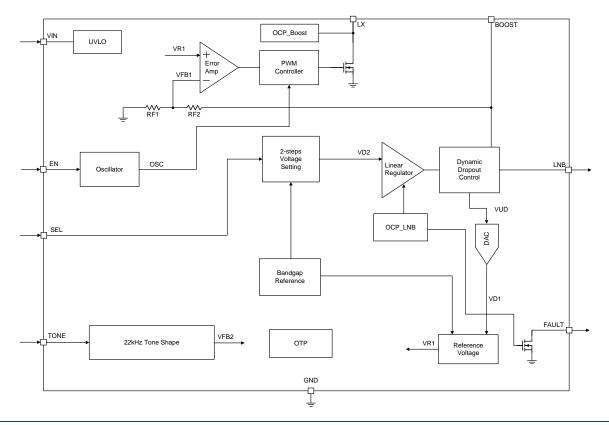

### **Functional Block Diagram**

Copyright © 2019 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

DS5047BF-01

May

2019

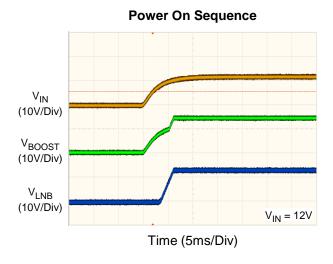

### Operation

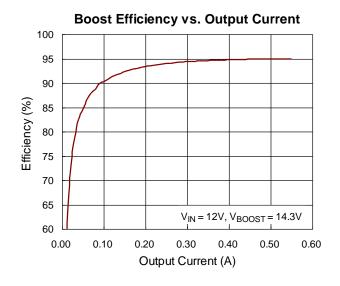

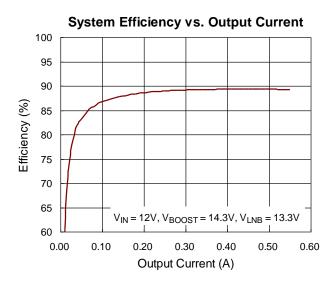

The RT5047BF integrates a current mode boost converter and linear regulator. Use the SEL pin to control the LNB voltage and the boost converter track is at least greater 850mV than LNB voltage. The boost converter is the high efficiency PWM architecture with 700kHz operation frequency. The linear regulator has the capability to source current up to 550mA during continuous operation. All the loop compensation, current sensing, and slope compensation functions are provided internally.

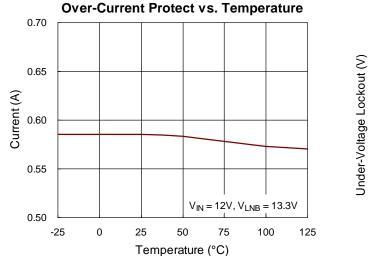

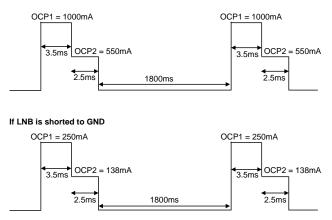

### OCP

Both the boost converter and the linear regulator have independent current limit.

(1) Boost

In the boost converter, this is achieved through cycle-by-cycle internal current limit.

(2) LNB

In the linear regulator, when the linear regulator exceeds OCP more than 6ms, the LNB output will be disabled and re-start after 1800ms.

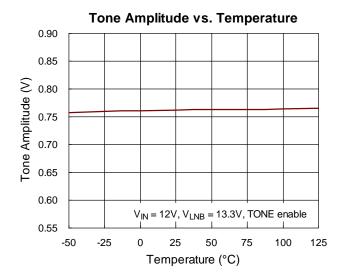

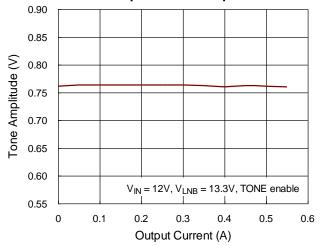

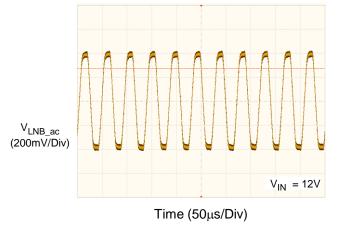

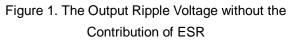

### **Tone Circuit**

This circuit is used for tone generation. Use the TONE pin to control output amplitude of LNB.

### ΟΤΡ

When the junction temperature reaches the critical temperature (typically 140°C), the boost converter and the linear regulator are immediately disabled.

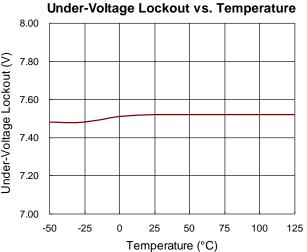

### UVLO

The UVLO circuit compares the VIN with the UVLO threshold (7.7V rising typically) to ensure that the input voltage is high enough for reliable operation. The 350mV (typ.) hysteresis prevents supply transients from causing a shutdown.

### **PWM Controller**

The loop compensation, current sensing, and slope compensation functions are provided internally.

### Absolute Maximum Ratings (Note 1)

| Supply Input Voltage, VIN                               | –0.3V to 28V   |

|---------------------------------------------------------|----------------|

| Output Voltage LNB, LX and BOOST Pins                   | –0.3V to 30V   |

| Others Pin to GND                                       | –0.3V to 6V    |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ (Note 5) |                |

| SOP-8 (Exposed pad)                                     | 3.44W          |

| Package Thermal Resistance (Note 2)                     |                |

| SOP-8 (Exposed pad), $\theta_{JA}$                      | 29°C/W         |

| SOP-8 (Exposed pad), $\theta_{JC}$                      | 2°C/W          |

| Lead Temperature (Soldering, 10 sec.)                   | 260°C          |

| Junction Temperature                                    | 150°C          |

| Storage Temperature Range                               | –65°C to 150°C |

| ESD Susceptibility (Note 3)                             |                |

| HBM (Human Body Model)                                  | 2kV            |

### Recommended Operating Conditions (Note 4)

| ٠ | Supply Input Voltage       | 8V to 16V      |

|---|----------------------------|----------------|

| • | Ambient Temperature Range  | –40°C to 85°C  |

| ٠ | Junction Temperature Range | –40°C to 125°C |

### **Electrical Characteristics**

| $(V_{IN (typ.)} = 12V, V_{IN})$ | = 8V to 16V, $T_A$ = | = 25°C, unless | otherwise specified) |

|---------------------------------|----------------------|----------------|----------------------|

|---------------------------------|----------------------|----------------|----------------------|

| Parameter                                        | Symbol              | Test Conditions                                                                           | Тур     | Мах  | Unit |     |

|--------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------|---------|------|------|-----|

| General                                          |                     |                                                                                           |         |      |      |     |

| LNB Output Accuracy,<br>Load and Line Regulation | E <sub>RR</sub>     | Relative to selected V <sub>LNB</sub> target level, $I_{LNB} = 0$ to 450mA                | -3      |      | 3    | %   |

|                                                  | I <sub>IN_OFF</sub> | EN = 0, LNB output disabled                                                               |         | 0.3  | 0.5  | mA  |

| Supply Current                                   | lin_on              | EN = 1, VLNB = 18.3V, Tone = 0V                                                           |         | 10   | 18   | mA  |

|                                                  | IIN_ON              | EN = 1, VLNB = 18.3V, 22kHz TONE<br>Input                                                 | Hz TONE |      | mA   |     |

| Boost Switch On<br>Resistance                    | RDS(ON)             | I <sub>LNB</sub> = 450mA                                                                  |         | 150  | 300  | mΩ  |

| Switching Frequency                              | fsw                 |                                                                                           | 600     | 700  | 800  | kHz |

| Switch Current Limit                             | ILIMSW              | V <sub>IN</sub> = 10V, V <sub>LNB</sub> = 18.3V                                           |         | 3    |      | А   |

| Linear Regulator Voltage<br>Drop                 | Vdrop               | $V_{BOOST}$ - $V_{LNB}$ , $I_{LNB}$ = 450mA                                               |         | 0.85 |      | V   |

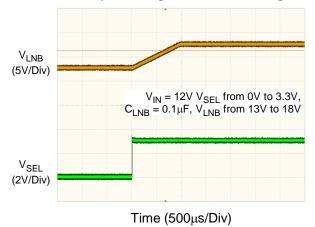

| Output Voltage Rise Time                         | t <sub>R_LNB</sub>  | For V <sub>LNB</sub> = 13.3V→18.3V,<br>C <sub>LNB</sub> = 100nF, I <sub>LNB</sub> = 450mA |         | 3 10 |      | ms  |

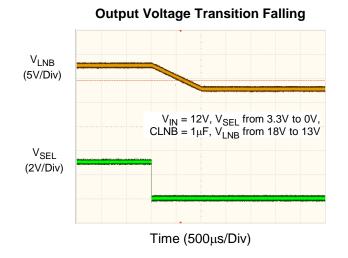

| Output Voltage Pull-Down<br>Time                 | tf_lnb              | For V <sub>LNB</sub> = 18.3V→13.3V,<br>C <sub>LNB</sub> = 100nF, I <sub>LNB</sub> = 0mA   |         | 3    | 10   | ms  |

## **RT5047BF**

| Parameter                               | Symbol              | Test Conditions                                              | Min | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Max | Unit             |  |

|-----------------------------------------|---------------------|--------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|--|

| Ripple and Noise on LNB Output          | V <sub>RIP_PP</sub> | 20MHz bandwidth limit (Note 6)                               |     | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | mV <sub>PP</sub> |  |

| Lood Degulation                         |                     | $V_{LNB} = 13.3V$ , $I_{LNB} = 50mA$ to 450mA                |     | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76  | m)/              |  |

| Load Regulation                         | Vout_load           | $V_{LNB} = 18.3V$ , $I_{LNB} = 50mA$ to 450mA                |     | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 90  | mV               |  |

| Line Degulation                         |                     | $V_{IN} = 9$ to 14V, $V_{LNB} = 13.3V$ ,<br>$I_{LNB} = 50mA$ | -10 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10  | m)/              |  |

| Line Regulation                         | VOUT_LINE           | $V_{IN} = 9$ to 14V, $V_{LNB} = 18.3V$ ,<br>$I_{LNB} = 50mA$ | -10 | 38       38         45       1          1         550       6         1800       1         7.35       1         7.35       1         7.35       1         7.35       1         700       9         50       1         10       1         50       1         700       9         50       1         10       1          0         5           0         5           0         5           0         5           0         5           0         5           0         5           0         5           0         5           0         5           0 | 10  | mV               |  |

| Protection                              |                     |                                                              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |                  |  |

| Output Over-Current Limit               | ILIM_LNB1           | V <sub>LNB</sub> = 13.3V/18.3V                               | 500 | 550                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 650 | mA               |  |

| Output Over-Current<br>Disable Time     | tDIS_ON             | V <sub>LNB</sub> short to GND                                |     | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | ms               |  |

| Output Over-Current<br>Disable Time     | tDIS_OFF            | V <sub>LNB</sub> short to GND (Note 6)                       |     | 1800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | ms               |  |

| VIN Under-Voltage Lockout<br>Threshold  | VUVLO               | V <sub>IN</sub> falling                                      |     | 7.35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | V                |  |

| VIN Turn On Threshold                   | VIN_TH              | V <sub>IN</sub> rising                                       | -   | 7.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8   | V                |  |

| VIN Under-Voltage Lockout<br>Hysteresis | VUVLOHYS            |                                                              |     | 350                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | mV               |  |

| OTP Threshold                           | T <sub>OTP</sub>    |                                                              |     | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | °C               |  |

| OTP Hysteresis                          | TOTPHYS             |                                                              |     | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | °C               |  |

| TONE                                    |                     | •                                                            |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |                  |  |

| TONE Frequency                          | <b>f</b> tone       |                                                              | 20  | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24  | kHz              |  |

| TONE Amplitude, Peak to Peak            | VTONE_PP            | $I_{LNB} = 50$ to 450mA, $C_{LNB} = 200$ nF                  | 550 | 700                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 900 | mVpp             |  |

| TONE Duty Cycle                         | DC <sub>TONE</sub>  | $I_{LNB} = 0$ to 450mA, $C_{LNB} = 570$ nF                   | 40  | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60  | %                |  |

| TONE Rise Time                          | <b>t</b> RTONE      | $I_{LNB} = 0$ to 450mA, $C_{LNB} = 570$ nF                   | 5   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15  | μS               |  |

| TONE Fall Time                          | <b>t</b> FTONE      | $I_{LNB} = 0$ to 450mA, $C_{LNB} = 570$ nF                   | 5   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15  | μS               |  |

| TONE Logic Input                        | V <sub>TONE_H</sub> |                                                              | 1.2 | $20$ $ $ $38$ $7$ $$ $45$ $9$ $-10$ $$ $1$ $-10$ $$ $1$ $-10$ $$ $1$ $-10$ $$ $1$ $-10$ $$ $1$ $-10$ $$ $1$ $-10$ $$ $1$ $-10$ $$ $1$ $-10$ $$ $1$ $-10$ $$ $1$ $-10$ $$ $6$ $$ $7.35$ $$ $$ $7.35$ $$ $$ $7.35$ $$ $$ $7.77$ $8$ $$ $140$ $$ $$ $140$ $$ $20$ $22$ $22$ $550$ $700$ $90$ $40$ $50$ $6$ $5$ $10$ $1$ $1.2$ $$ $-$ <tr td=""> <math> -</math></tr>                                                                                                                                                                                    |     | V                |  |

|                                         |                     |                                                              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |                  |  |

| TONE LOgic Input                        | V <sub>TONE_L</sub> |                                                              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.4 | V                |  |

| TONE Input Leakage                      | ITONELKG            |                                                              |     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10  | μΑ               |  |

| ENABLE, SEL FAULT Pins                  |                     |                                                              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |                  |  |

| EN Logic Input                          | V <sub>EN_H</sub>   |                                                              | 1.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | V                |  |

| EN LOGIC INPUL                          | V <sub>EN_L</sub>   |                                                              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.4 | V                |  |

| EN Input Leakage                        | I <sub>ENLKG</sub>  |                                                              |     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10  | μΑ               |  |

| SEL Logic Input                         | V <sub>SEL_H</sub>  |                                                              | 1.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | V                |  |

|                                         | VSEL_L              |                                                              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.4 | V                |  |

| SEL Input Leakage                       | ISELLKG             |                                                              |     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10  | μA               |  |

| FAULT Logic Low                         | VFAULT_L            |                                                              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.4 | V                |  |

| FAULT Input Leakage                     | VFAULTLKG           |                                                              |     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10  | μA               |  |

Copyright © 2019 Richtek Technology Corporation. All rights reserved.

- Note 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. Operation in  $V_{IN}$  > 14.5V can be limited by power loss in the linear regulator, and recommend voltage difference across the linear regulator between input (Boost) and output (LNB) terminal is smaller than 1.2V.

- Note 6. Guaranteed by design.

Copyright © 2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. www.richtek.com

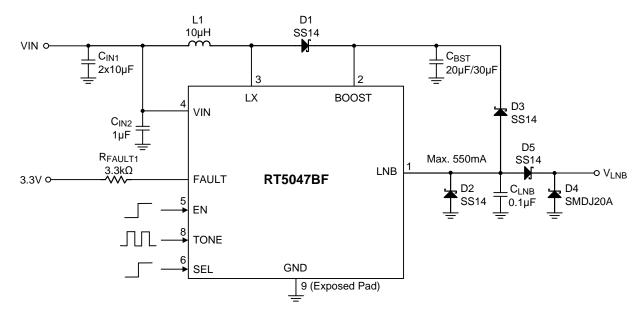

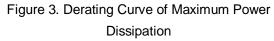

### **Typical Application Circuit**

Note :

- 1. D2, D3, D4, D5 are used for surge protection.

- 2. The capacitor  $C_{LNB}$  should be less than  $1\mu F$  for the power stability.

- 3. EN, TONE, and SEL are connected to microcontroller directly.

## **Typical Operating Characteristics**

Tone Amplitude vs. Output Current

**Output Voltage Transition Rising**

Copyright © 2019 Richtek Technology Corporation. All rights reserved.

### **Application Information**

### **Boost Converter/Linear Regulator**

The RT5047BF integrates a current-mode boost converter and linear regulator. Use the SEL pin to control the LNB voltage and the boost converter track is at least greater 800mV than the LNB voltage. The boost converter is high efficiency PWM architecture with 700kHz operation frequency. The linear regulator has the capability to source current up to 550mA during continuous operation. All the loop compensation, current sensing, and slope compensation functions are provided internally.

The RT5047BF has current limiting on the boost converter and the LNB output to protect the IC against short circuits. The internal MOSFET will turn off when the LX current is higher than 3A cycle-by-cycle. The LNB output will turn off when the output current higher than the 550mA and 6ms and turn-on after 1800ms automatically.

#### **Input Capacitor Selection**

The input capacitor reduces voltage spikes from the input supply and minimizes noise injection to the converter. A  $20\mu$ F capacitance is sufficient for most applications. Nevertheless, a higher or lower value may be used depending on the noise level from the input supply and the input current to the converter. Note that the voltage rating of the input capacitor must be greater than the maximum input voltage.

#### **Inductor Selection**

The inductance depends on the maximum input current. As a general rule, the inductor ripple current range is 20% to 40% of the maximum input current. If 40% is selected as an example, the inductor ripple current can be calculated according to the following equations :

$I_{\text{IN}(\text{MAX})} = \frac{V_{\text{OUT}} \times I_{\text{OUT}}(\text{MAX})}{\eta \times V_{\text{IN}}}$  $I_{\text{RIPPLE}} = 0.4 \times I_{\text{IN}(\text{MAX})}$

where  $\eta$  is the efficiency of the converter,  $I_{IN(MAX)}$  is the maximum input current, and IRIPPLE is the inductor ripple current. The input peak current can then be obtained by adding the maximum input current

with half of the inductor ripple current as shown in the following equation :

$I_{PEAK} = 1.2 \text{ x } I_{IN(MAX)}$

note that the saturated current of the inductor must be greater than  $I_{PEAK}$ . The inductance can eventually be determined according to the following equation :

$L = \frac{\eta \times (V_{IN})^2 \times (V_{OUT} - V_{IN})}{0.4 \times (V_{OUT})^2 \times I_{OUT(MAX)} \times f_{OSC}}$

where  $f_{OSC}$  is the switching frequency. For better system performance, a shielded inductor is preferred to avoid EMI problems.

#### **Boost Output Capacitor Selection**

The RT5047BF boost regulator is internally compensated and relies on the inductor and output capacitor value for overall loop stability. The output capacitor is in the  $20\mu$ F to  $30\mu$ F range with a low ESR, as strongly recommended. The voltage rating on this capacitor should be in the 25V to 35V range since it is connected to the boost V<sub>OUT</sub> rail.

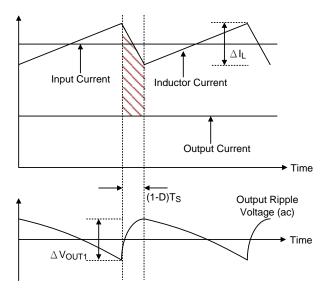

The output ripple voltage is an important index for estimating chip performance. This portion consists of two parts. One is the product of the inductor current with the ESR of the output capacitor, while the other part is formed by the charging and discharging process of the output capacitor. As shown in Figure 1,  $\Delta V_{OUT1}$  can be evaluated based on the ideal energy equalization. According to the definition of Q, the Q value can be calculated as the following equation :

$$Q = \frac{1}{2} \times \left[ \left( I_{IN} + \frac{1}{2} \Delta I_L - I_{OUT} \right) + \left( I_{IN} - \frac{1}{2} \Delta I_L - I_{OUT} \right) \right]$$

$$\times \frac{V_{IN}}{V_{OUT}} \times \frac{1}{f_{OSC}} = C_{OUT} \times \Delta V_{OUT1}$$

where  $f_{OSC}$  is the switching frequency and  $\Delta I_L$  is the inductor ripple current. Bring  $C_{OUT}$  to the left side to estimate the value of  $\Delta V_{OUT1}$  according to the following equation :

$$\Delta V_{OUT1} = \frac{D \times I_{OUT}}{\eta \times C_{OUT} \times f_{OSC}}$$

Copyright © 2019 Richtek Technology Corporation. All rights reserved.

where D is the duty cycle and  $\eta$  is the boost converter efficiency. Finally, take ESR into consideration, the overall output ripple voltage can be determined by the following equation :

$\Delta V_{OUT} = I_{IN} \times ESR + \frac{D \times I_{OUT}}{\eta \times C_{OUT} \times f_{OSC}}$

The output capacitor,  $C_{OUT}$ , should be selected accordingly.

### **Schottky Diode Selection**

diodes Schottky are chosen for their low forward-voltage drop and fast switching speed. However, when making a selection, important parameters such as power dissipation, reverse voltage rating, and pulsating peak current should all be taken into consideration. A suitable Schottky diode's reverse voltage rating must be greater than the maximum output voltage and its average current rating must exceed the average output current. The chosen diode should also have a sufficiently low leakage current level, since it increases with temperature.

### Under-Voltage Lockout (UVLO)

The UVLO circuit compares the input voltage at VIN with the UVLO threshold (7.7V rising typically) to ensure that the input voltage is high enough for reliable operation. The 350mV (typ.) hysteresis prevents supply transients from causing a shutdown. Once the input

voltage exceeds the UVLO rising threshold, start-up begins. When the input voltage falls below the UVLO falling threshold, all IC internal functions will be turned off by the controller.

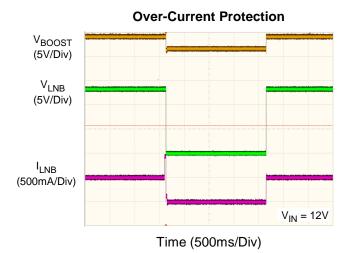

### **Over-Current Protection**

The RT5047BF features an over-current protection function to prevent chip damage from high peak currents. Both the boost converter and the linear regulator have independent current limit.

(1) Boost

In the boost converter, this is achieved through cycle-by-cycle internal current limit. During the ON-period, the chip senses the inductor current that is flowing into the LX pin. The internal NMOS will be turned off if the peak inductor current reaches the current-limit value of 3A (typ.).

(2) LNB

When the linear regulator exceeds 550mA (typ.) more than 6ms, the LNB output will be disabled. During this period of time, if the current limit condition disappears, the OCP will be cleared and the part restarts.

If the part is still in current limit after this time period, the linear regulator and boost converter will automatically disable to prevent the part from overheating.

### **Short Circuit Protection**

If the LNB output is shorted to ground, and more than 6ms, the RT5047BF will be disabled 1800ms then enable automatically.

### **Over-Temperature Protection**

When the junction temperature reaches the critical temperature (typically 140°C), the boost converter and the linear regulator are immediately disabled. When the junction temperature cools down to a lower temperature threshold specified, the RT5047BF will be allowed to restart by normal start operation.

### FAULT

FAULT is a open-drain input. If it is 0, it stands for fault occurred. The FAULT provide the information to show over-current and short circuit protection of the system.

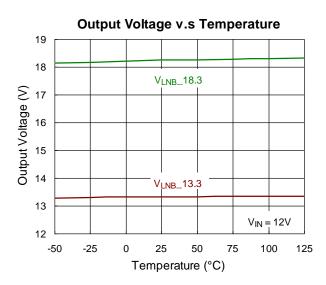

### LNB Output Voltage

The RT5047BF has voltage control function on the LNB output. This function provides 2 levels for the common

standards and compensation if the cable line has voltage drop. These voltage levels are defined in Table 1. The rise time and fall time of the VLNB is 3ms (typ.).

| Table 1        |                    |  |  |  |  |  |  |  |

|----------------|--------------------|--|--|--|--|--|--|--|

| SEL Pin Status | LNB Output Voltage |  |  |  |  |  |  |  |

| 0              | 13.3V              |  |  |  |  |  |  |  |

| 1              | 18.3V              |  |  |  |  |  |  |  |

#### **Tone Generation**

The RT5047BF provides the tone generation function, please refer to the Figure 2. Set the TONE pin with 22kHz logic signal, the LNB linear regulator output will

carry a 22kHz, 700mV peak to peak signal for DiSEqC 1.x communication. It can meet base-band timings of  $500\mu s$  (±100 $\mu s$ ) for a one-third bit PWK coded signal period on a nominal 22kHz (±20%)

#### **Pull-Down Rate Control**

The output linear stage provides approximately 40mA of pull-down capability. This ensures that the output volts are ramped in a reasonable amount of time.

#### **Over-Current Disable Time**

If the LNB output current exceeds 550mA, typical, for more than 6ms, then the LNB output will be disabled and device enters a  $t_{ON} = 6ms/t_{OFF} = 1800ms$  routine. It will be returned to normal operation after a successful soft-start process.

#### Inrush Current

At start-up or during a LNB reconfiguration event, a transient surge current above the normal DC operating level can be provided by the IC. This current increase can be as high as 550mA, typical, for as long as required, up to a maximum of 6ms.

#### **DC Current**

The RT5047BF can handle up to 500mA during continuous operation.

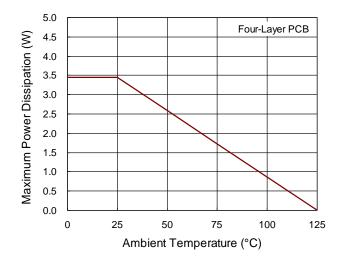

#### **Thermal Considerations**

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula :

#### $\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{J}\mathsf{A}}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a SOP-8 (Exposed Pad) package, the thermal resistance,  $\theta_{JA}$ , is 29°C/W on a standard JEDEC 51-7 hiah effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated as below :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (29^{\circ}C/W) = 3.44W$  for a SOP-8 (Exposed Pad) package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 3 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

RICHTEK

#### Layout Consideration

For high frequency switching power supplies, the PCB layout is important to get good regulation, high efficiency and stability. The following descriptions are the guidelines for better PCB layout.

- For good regulation, place the power components as close as possible. The traces should be wide and short enough especially for the high-current loop.

- Minimize the size of the LX node and keep it wide and shorter.

The exposed pad of the chip should be connected to a strong ground plane for maximum thermal consideration.

$D_3$  and  $D_4$  should be placed as closed as possible to  $V_{OUT}$  for surge protection. The CIN, CBST and CLNB should be placed as closed as possible to the RT5047BF for good filter.

The exposed pad of the chip should be connected to analog ground plane for thermal consideration.

The TONE, SEL, FAULT and EN pin should be connected to MCU or GND. Do not floating these pins.

The inductor should be placed as close as possible to the LX pin to minimize the noise coupling into other circuits.

LX node copper area should be minimized for reducing EMI

Place the power components as close as possible. The traces should be wide and short especially for the high-current loop.

Figure 4. PCB Layout Guide

## **Outline Dimension**

| Symp     |     | Dimensions | n Millimeters   | <b>Dimensions In Inches</b> |       |  |  |

|----------|-----|------------|-----------------|-----------------------------|-------|--|--|

| Symb     | 001 | Min        | Max             | Min                         | Max   |  |  |

| A        |     | 4.801      | 5.004           | 0.189                       | 0.197 |  |  |

| В        |     | 3.810      | 4.000           | 0.150                       | 0.157 |  |  |

| С        |     | 1.346      | 1.753           | 0.053                       | 0.069 |  |  |

| D        |     | 0.330      | 0.510           | 0.013                       | 0.020 |  |  |

| F        |     | 1.194      | 1.346           | 0.047                       | 0.053 |  |  |

| Н        |     | 0.170      | 0.254 0.007     |                             | 0.010 |  |  |

| I        |     | 0.000      | 000 0.152 0.000 |                             | 0.006 |  |  |

| J        |     | 5.791      | 1 6.200 0.228   |                             | 0.244 |  |  |

| М        |     | 0.406      | 1.270           | 0.016                       | 0.050 |  |  |

| Option 1 | Х   | 2.000      | 2.300           | 0.079                       | 0.091 |  |  |

| Option 1 | Y   | 2.000      | 2.300           | 0.079                       | 0.091 |  |  |

| Option 2 | Х   | 2.100      | 2.500           | 0.083                       | 0.098 |  |  |

| Option 2 | Y   | 3.000      | 3.500           | 0.118                       | 0.138 |  |  |

8-Lead SOP (Exposed Pad) Plastic Package

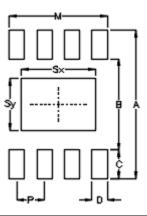

### **Footprint Information**

| Deel    |         | Number of Din | Footprint Dimension (mm) |      |      |         |      |      |      |      | Teleronee |

|---------|---------|---------------|--------------------------|------|------|---------|------|------|------|------|-----------|

| Package |         | Number of Pin | Р                        | А    | В    | С       | D    | Sx   | Sy   | М    | Tolerance |

| PSOP-8  | Option1 | 0             | 1.27                     | 6.80 | 4.20 | 20 1.30 | 0.70 | 2.30 | 2.30 | 4.51 | ±0.10     |

|         | Option2 | Ő             |                          |      |      |         |      | 3.40 | 2.40 |      |           |

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.