**RT5147**

## **Power Management Unit Total Power Solution for SSD**

## 1 General Description

The RT5147 provides a highly-integrated multichannel system power management solutions designed to fulfill the performance, efficiency, and feature requirements of SSD applications.

It features four buck regulators and two LDOs, delivering multiple output voltages to accommodate various applications with different Voltage Identification (VID) requirements. The power-on sequence is configurable, offering enhanced flexibility for system design.

Additionally, the RT5147 is equipped with eight configurable GPIO pins to meet diverse system hardware control requirements. These GPIOs can be programmed for a variety of functions, including PWRDIS, Sleep, and Deep Sleep settings for PMIC state machine control, Enable/Disable settings for Buck1 and Buck2, VID control settings for Buck3 and Buck4, nRESET pin functionality to monitor PMIC power-good status, and configuration as External Enable (External\_EN) and External Power-Good (External\_PG) signals. Furthermore, the GPIOs support three-state configuration through the I<sup>2</sup>C interface when operating in the normal mode. The RT5147 is designed to operate recommended junction temperature range of -40°C to 125°C, and an ambient temperature range of -40°C to 85°C.

## 2 Applications

SSDs

## 3 Marking Information

3T: Product Code XXYY: Wafer ID with Check Sum CCC-RRR: IC Coordinate (X, Y) YMDAN: Date Code

### 4 Features

- Input Supply Voltage Range: 2.7V to 3.7V

- Highly Efficient Programmable Regulators

- BUCK 1: 1.7V to 2.9V, 20mV per Step; 4A

- BUCK 2: 0.5V to 1.3V, 10mV per Step; 2A

- BUCK 3: 0.5V to 1.3V, 10mV per Step; 4A

- BUCK 4: 0.9V to 2.0V, 10mV per Step; 2A

- LDO 1: 1.0V to 2.7V, 50mV per Step; 400mA

- LDO 2: 1.0V to 2.7V, 50mV per Step; 400mA

- Configurable Outputs

- ±1.5% Feedback Voltage Accuracy for Full Temperature Range (-40°C to 125°C)

- DVS Change for All Bucks via I<sup>2</sup>C Interface

- Enable Time for All VRs

- Soft-Start Time for All VRs

- Selectable Switching Frequency for Every Buck Rail

- Input OV/UV Warning Indication and Fault Protection

- Output OV/UV/OC Fault Protection

- Over-Temperature Protection

- Diode Emulation Mode for Light-Load and High Efficiency Operation

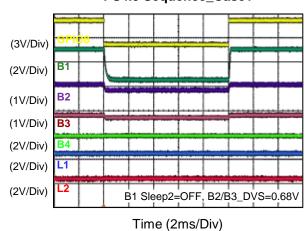

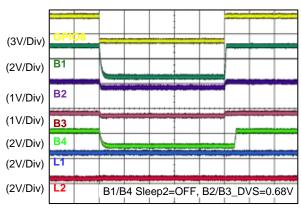

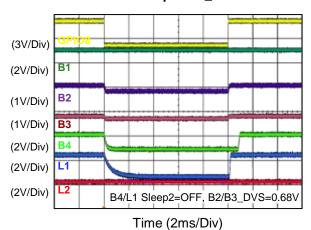

- Buck2 and Buck3 Support DVS without I<sup>2</sup>C

Command at Sleep Mode

- Non-Volatile Register Configurability

- I<sup>2</sup>C Interface 400kHz/1MHz/3.4MHz

- 8 Multi-Function GPIOs for Control and Command Unit

- nRESET\_N for ASIC

- IRQ N Interrupt Flag

- PWRDIS, SLEEP1, SLEEP2

- Enable/Disable Settings for Buck1 and Buck2

- 2 Sets of EXT\_EN\_I and EXT\_EN\_O

- SYSMON Can Only be Set by GPIO5

- Buck1/2/3/4 and LDO1/2 Selection by GPIOx

1

## **5 Ordering Information**

#### Note 1.

Richtek products are Richtek Green Policy compliant and marked with (1) indicates compatible with the current requirements of IPC/JEDEC J-STD-020.

#### **Part Number Version Table**

| Part Number  |                 |     |            |             | ,           | VOUT (V)    |            |           |           |

|--------------|-----------------|-----|------------|-------------|-------------|-------------|------------|-----------|-----------|

|              | GPIOx<br>Status |     | BUCK1      | BUCK2 (B2)  | BUCK3 (B3)  | B2/B3       | BUCK4      | LDO1      | LDO2      |

|              |                 |     | (B1)       | Normal      | Normal      | Sleep       | (B4)       | (L1)      | (L2)      |

|              | Н               | 3.3 | PLSW       | BUCK = 0.91 | BUCK = 0.78 | BUCK = 0.68 | BUCK = 1.1 | LDO = 1.8 | LDO = 1.8 |

| RT5147WSC-01 | Hi-Z            | 3.3 | BUCK = 2.5 | BUCK = 0.91 | BUCK = 0.78 | BUCK = 0.68 | BUCK = 1.2 | LDO = 1.8 | Х         |

|              | L               | 3.3 | BUCK = 2.5 | BUCK = 0.91 | BUCK = 1.2  | BUCK = 0.68 | BUCK = 1.2 | LDO = 2.5 | PLSW      |

#### Note 2.

- GPIO2 controls BUCK1 and BUCK2, GPIO3 controls BUCK3, GPIO4 controls BUCK4 and LDO1, and GPIO6 controls LDO2.

- PLSW = P-type Load Switch.

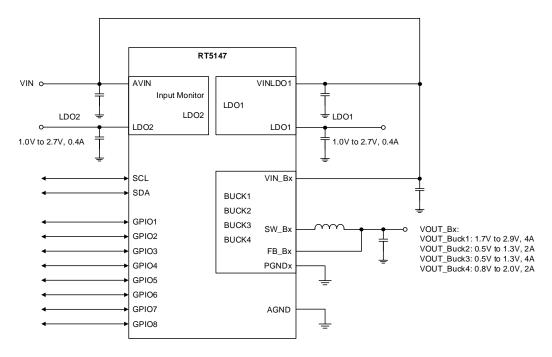

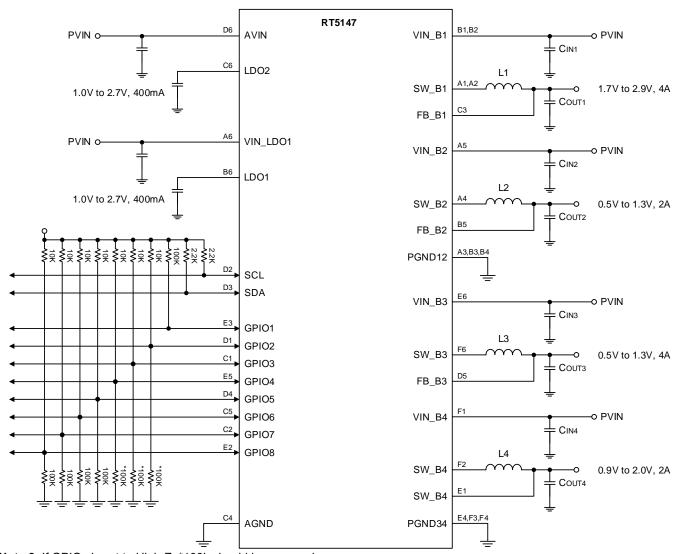

## 6 Simplified Application Circuit

www.richtek.com

## **Table of Contents**

| 1  |        | ral Description                                |    |    | 16.8     | AVIN Overvoltage Protection (AVIN OVP) | 36    |

|----|--------|------------------------------------------------|----|----|----------|----------------------------------------|-------|

| 2  |        | cations                                        |    |    | 16.9     | AVIN Undervoltage-Lockout (AVIN UVLO   | ) -37 |

| 3  |        | ng Information                                 |    |    | 16.10    | Over-Temperature Protection (OTP)      | 37    |

| 4  |        | res                                            |    |    | 16.11    | Protection Functions                   |       |

| 5  | Order  | ing Information                                | 2  |    | 16.12    | Rails Configuration                    |       |

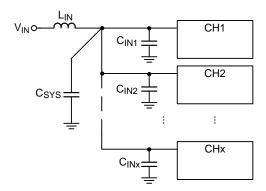

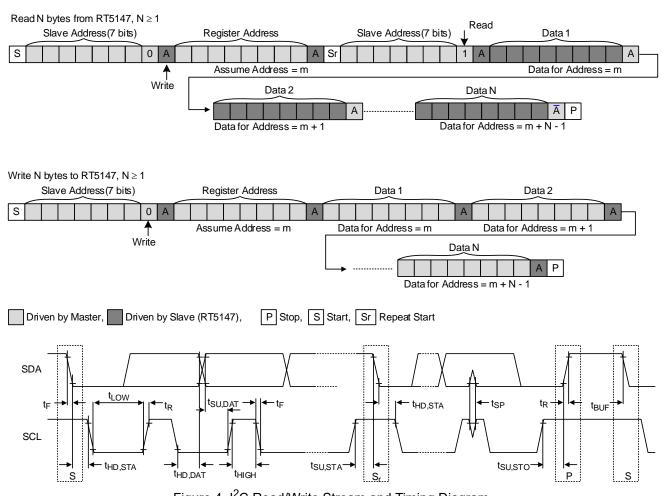

| 6  |        | ified Application Circuit                      |    |    | 16.13    | I <sup>2</sup> C Interface             |       |

| 7  |        | onfiguration                                   |    |    | 16.14    | State Machine                          |       |

| 8  | Funct  | ional Pin Description                          | 4  |    | 16.14.1  | •                                      |       |

| 9  | Funct  | ional Block Diagram                            | 7  |    |          | Standby State                          |       |

| 10 |        | ute Maximum Ratings                            |    |    |          | Normal State                           |       |

| 11 |        | mmended Operating Conditions                   |    |    |          | Sleep1/Sleep2 State                    |       |

| 12 |        | ical Characteristics                           |    |    |          | Thermal Recovery State                 |       |

| 13 |        | al Application Circuit                         |    |    | 16.14.6  | Recovery State                         |       |

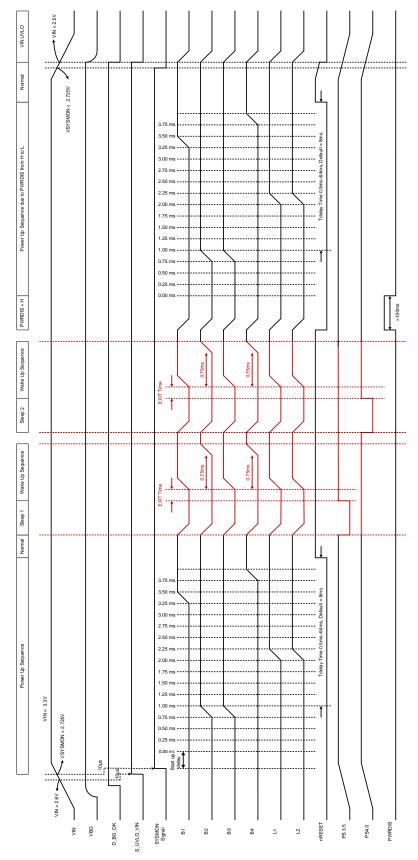

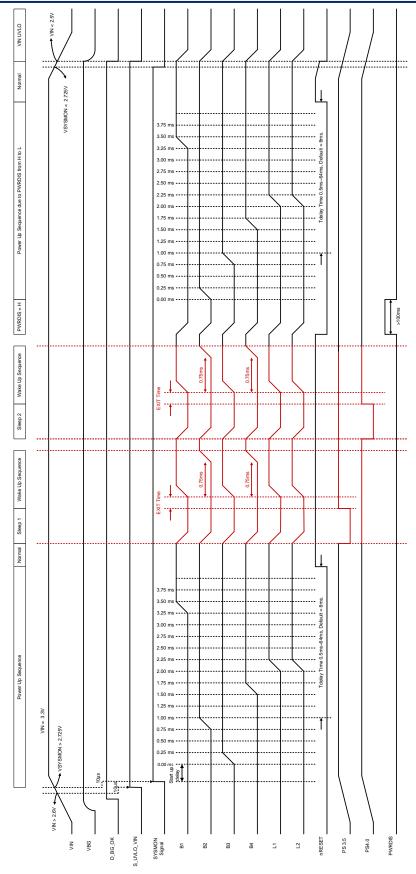

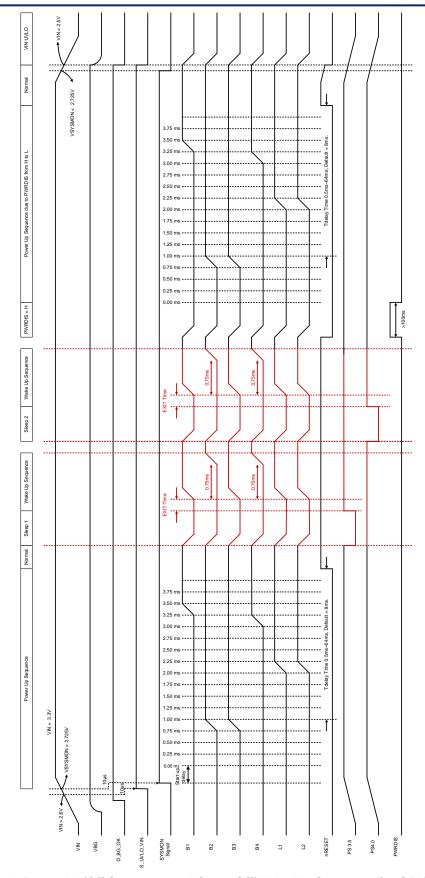

| 14 |        | al Operating Characteristics                   |    |    | 16.15    | Sequence Diagram                       | 41    |

| 15 | Opera  | ition                                          |    |    | 16.16    | TIME_SLOT, ON_DLY,                     |       |

|    | 15.1   | Buck Converter                                 |    |    |          | WAKE_UP_DLY, and OFF_DLY               |       |

|    | 15.2   | Buck Overcurrent Protection (OCP)              |    |    | 16.17    | B1/B2_EN                               |       |

|    | 15.3   | Buck Undervoltage Protection (UVP)             |    |    | 16.18    | VOUT_LOW                               |       |

|    | 15.4   | Buck Overvoltage Protection (OVP)              |    |    | 16.19    | EXT_ENx_O                              |       |

|    | 15.5   | Linear Dropout Regulator (LDO)                 |    |    | 16.20    | SYSMON, SYSWARN, and POK_OV            |       |

|    | 15.6   | Over-Temperature Protection (OTP)              |    |    | 16.21    | AVIN_OV and AVIN UVLO                  |       |

|    | 15.7   | GPI01                                          |    |    | 16.22    | Status and Flag                        |       |

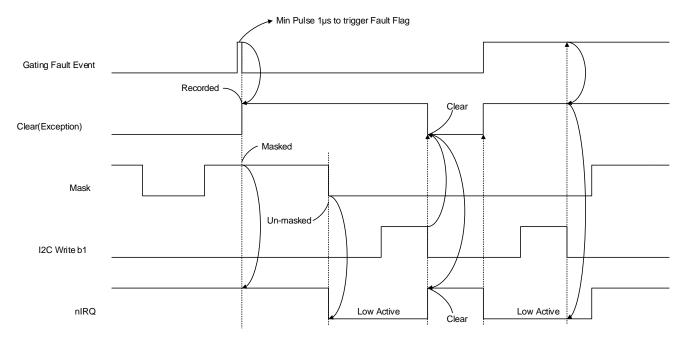

|    | 15.8   | GPI02                                          |    |    | 16.23    | nIRQ (Negative Interrupt Request)      | 47    |

|    | 15.9   | GPIO3                                          |    |    | 16.24    | Power Disable (PWRDIS)                 | 48    |

|    | 15.10  | GPI04                                          | -  |    | 16.25    | B2/B3_DVS_EN_SLEEPx                    |       |

|    | 15.11  | GPI06                                          |    |    | 16.26    | Thermal Considerations                 |       |

|    | 15.12  | GPIO5/7/8                                      |    |    | 16.27    | Layout Considerations                  |       |

| 16 | Applic | cation Information                             |    | 17 | Function | onal Register Description              | 51    |

|    | 16.1   | Bucker Converter                               |    |    | 17.1     | Registers Configuration                | 53    |

|    | 16.2   | Inductor Selection                             |    | 18 |          | e Dimension                            |       |

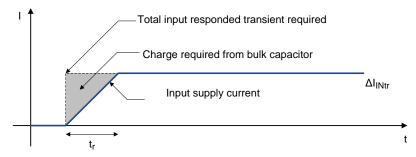

|    | 16.3   | C <sub>IN</sub> and C <sub>SYS</sub> Selection |    | 19 |          | int Information                        |       |

|    | 16.4   | Cout Selection                                 |    | 20 |          | g Information                          |       |

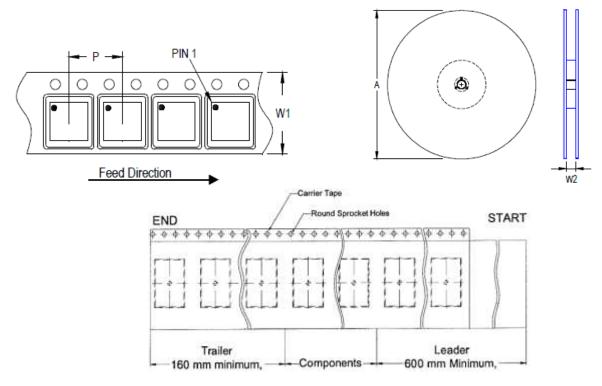

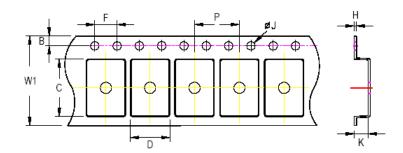

|    | 16.5   | Overcurrent Protection (OCP)                   |    |    | 20.1     | Tape and Reel Data                     |       |

|    | 16.6   | Undervoltage Protection (UVP)                  |    |    | 20.2     | Tape and Reel Packing                  |       |

|    | 16.7   | Overvoltage Protection (OVP)                   | 36 |    | 20.3     | Packing Material Anti-ESD Property     |       |

|    |        |                                                |    | 21 | Datash   | neet Revision History                  | - 109 |

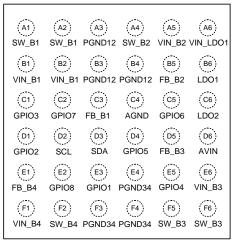

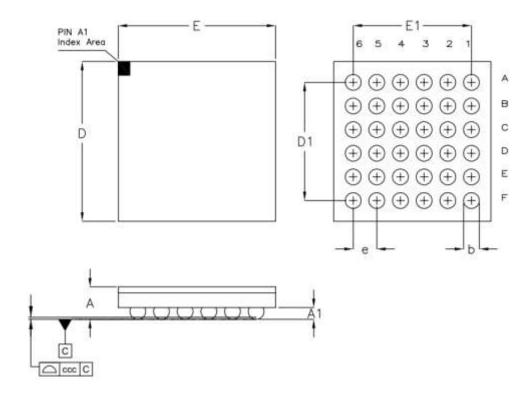

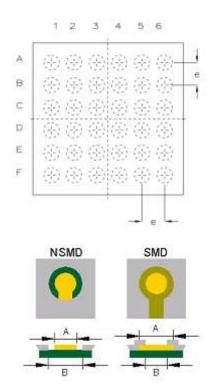

## 7 Pin Configuration

### (TOP VIEW)

WL-CSP-36B 2.66x2.70 (BSC)

## **8 Functional Pin Description**

| Pin No.    | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                    |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2     | SW_B1    | Switch node of Buck1. It is internally connected to the drain terminal of the high-side MOSFET and the drain terminal of the low-side MOSFET. Connect these pins to the output inductor and keep the sensitive trace and signals away.                                                                                                          |

| A3, B3, B4 | PGND12   | Power stage ground for Buck1 and Buck2. This is the ground return path for the low-side power MOSFETs and drivers of Buck1 and Buck2. To minimize the parasitic impedance and thermal resistance, it is essential to directly solder this ground to a large PCB Power Ground (PGND) plane and to incorporate thermal vias beneath the PGND pin. |

| A4         | SW_B2    | Switch node of Buck2. It is internally connected to the drain terminal of the high-side MOSFET and the drain terminal of the low-side MOSFET. Connect this pin to output inductor and keep the sensitive trace and signals away.                                                                                                                |

| A5         | VIN_B2   | Buck2 Input voltage pin. It is internally connected to the source terminal of Buck2 high-side MOSFET. It is necessary to connect a ceramic capacitor (C = $10\mu\text{F}/0603$ ) as close as possible from the VIN_B2 pin to the PGND12 pin.                                                                                                    |

| A6         | VIN_LDO1 | LDO1 input supply. It is necessary to connect a ceramic capacitor (C = $2.2\mu\text{F}/0402$ ) as close as possible from the VIN_LDO1 pin to the PGND pin.                                                                                                                                                                                      |

| B1, B2     | VIN_B1   | Buck1 input voltage pins are internally connected to the source terminal of Buck1 high-side MOSFET. It is necessary to connect a ceramic capacitor (C = $10\mu\text{F}/0603$ ) as close as possible from the VIN_B1 pin to the PGND12 pin.                                                                                                      |

| B5         | FB_B2    | Buck2 feedback sense for output regulation. It is used to detect output voltage status for OVP, UVP, and Power Good of Buck2. Connect it to the Buck2 output capacitor.                                                                                                                                                                         |

| В6         | LDO1     | LDO1 output. To ensure stability of the LDO, it is recommended to connect the pin to a ceramic capacitor (C = $2.2\mu F/0402$ ).                                                                                                                                                                                                                |

| C1         | GPIO3    | By default, GPIO3 is set as an EXT_EN1_O output pin with an Open Drain configuration, which requires the use of an external pull-up resistor. Once the AVIN voltage exceeds the UVLO threshold, the user can select GPIO3 to perform one of the other nine available functions.                                                                 |

| Pin No.    | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                          |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C2         | GPIO7    | By default, GPIO7 serves as a PWRDIS (Power Disable) input pin with an open drain configuration, which requires the use of an external pull-up resistor. Once the AVIN voltage exceeds the UVLO threshold, the user can select GPIO7 to perform one of the other nine available functions.                                                            |

| C3         | FB_B1    | Buck1 feedback sense for output regulation. It is used to detect output voltage status for OVP, UVP, and Power Good of Buck1. Connect it to the Buck1 output capacitor.                                                                                                                                                                               |

| C4         | AGND     | Ground of internal analog circuitry. AGND must be connected to the PGND plane through a single point.                                                                                                                                                                                                                                                 |

| C5         | GPIO6    | By default, GPIO6 is set as an EXT_EN1_O output pin with an open drain configuration, which requires the use of an external pull-up resistor. Once the AVIN voltage exceeds the UVLO threshold, the user can select GPIO6 to perform one of the other nine available functions.                                                                       |

| C6         | LDO2     | LDO2 output. To ensure stability of the LDO, it is recommended to connect it to a ceramic capacitor (C = $2.2\mu F/0402$ ).                                                                                                                                                                                                                           |

| D1         | GPIO2    | By default, GPIO2 is set as an EXT_EN1_O output pin with an open drain configuration, which requires the use of an external pull-up resistor. Once the AVIN voltage exceeds the UVLO threshold, the user can select GPIO2 to perform one of the other nine available functions.                                                                       |

| D2         | SCL      | I <sup>2</sup> C clock pin. This pin is the input of the serial bus clock signal.                                                                                                                                                                                                                                                                     |

| D3         | SDA      | I <sup>2</sup> C data pin. This pin is the input and output of the serial bus data signal.                                                                                                                                                                                                                                                            |

| D4         | GPIO5    | GPIO5 is pre-configured as an nIRQ (Negative Interrupt Request) output pin with an open drain configuration, which requires the use of an external pull-up resistor. Once the AVIN voltage exceeds the UVLO threshold, the user can select GPIO5 to perform one of the other nine available functions.                                                |

| D5         | FB_B3    | Buck3 feedback sense for output regulation. It is used to detect output voltage status for OVP, UVP, and Power Good of Buck3. Connect it to the Buck3 output capacitor.                                                                                                                                                                               |

| D6         | AVIN     | Input voltage pin of internal analog circuitry. Connecting the ceramic capacitor (C = $2.2\mu F/0402$ ) as close as possible from the AVIN pin to the AGND pin is necessary. It is also used to detect input voltage status for VIN OV and UV.                                                                                                        |

| E1         | FB_B4    | Buck4 feedback sense for output regulation. It is used to detect output voltage status for OVP, UVP, and Power Good of Buck4. Connect it to the Buck4 output capacitor.                                                                                                                                                                               |

| E2         | GPIO8    | By default, GPIO8 is configured as a Sleep Mode 2 input pin with an open drain configuration, which requires the use of an external pull-up resistor. Once the AVIN voltage exceeds the UVLO threshold, the user can select GPIO8 to perform one of the other nine available functions.                                                               |

| E3         | GPIO1    | GPIO1 is an output pin dedicated to the nRESET signal. Following the power-up sequence of Buck1, the state of nRESET provides an indication of the PMIC's status: nRESET = H indicates PMIC is in a Power-Good (PG) state, whereas nRESET = L indicates a Power Bad (PBAD) status.                                                                    |

| E4, F3, F4 | PGND34   | Power Stage Power Ground for Buck3 and Buck4. This is the ground return path for the low-side power MOSFETs and drivers of Buck3 and Buck4. To minimize the parasitic impedance and thermal resistance, it is essential to directly solder this ground to a large PCB Power Ground (PGND) plane and to incorporate thermal vias beneath the PGND pin. |

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                                                                                                  |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E5      | GPIO4    | GPIO4 is initially set as an EXT_EN1_O output pin with an open drain configuration, which requires the use of an external pull-up resistor. Once the AVIN voltage exceeds the UVLO threshold, the user can select GPIO4 to perform one of the other nine available functions. |

| E6      | VIN_B3   | Buck3 input voltage pin. It is internally connected to the source terminal of the Buck3 high-side MOSFET. It is necessary to connect a ceramic capacitor (C = $10\mu\text{F}/0603$ ) as close as possible from the VIN_B3 pin to the PGND34 pin.                              |

| F1      | VIN_B4   | Buck4 input voltage pin. It is internally connected to the source terminal of the Buck4 high-side MOSFET. It is necessary to connect a ceramic capacitor (C = $10\mu\text{F}/0603$ ) as close as possible from the VIN_B4 pin to the PGND34 pin.                              |

| F2      | SW_B4    | Switch node of Buck4. It is internally connected to the drain terminal of the high-side MOSFET and the drain terminal of the low-side MOSFET. Connect this pin to the output inductor and keep the sensitive trace and signals away.                                          |

| F5, F6  | SW_B3    | Switch node of Buck3. It is internally connected to the drain terminal of the high-side MOSFET and the drain terminal of the low-side MOSFET. Connect this pin to the output inductor and keep the sensitive trace and signals away.                                          |

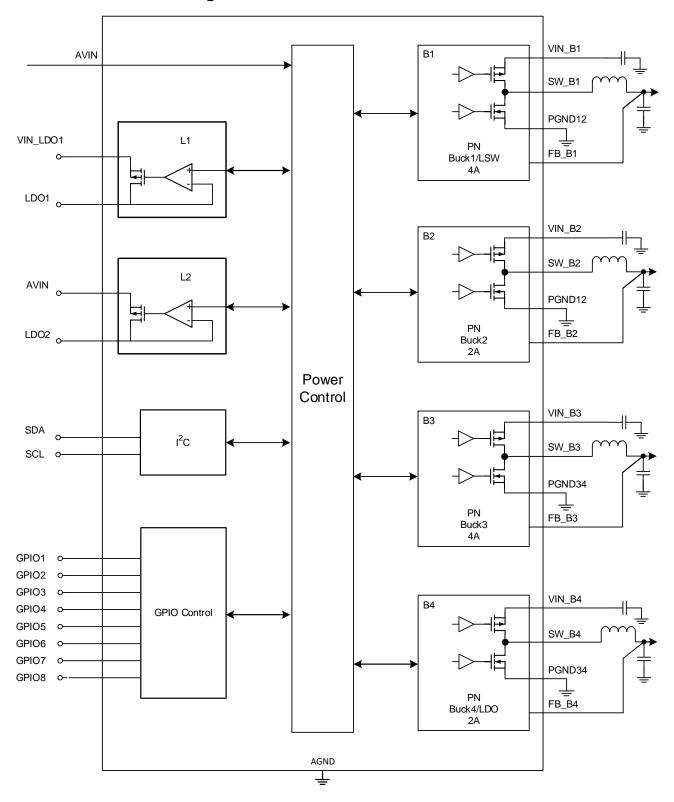

## 9 Functional Block Diagram

## 10 Absolute Maximum Ratings

### (Note 3)

| Supply Input Voltage, VIN                                   | -0.3V to $6V$   |

|-------------------------------------------------------------|-----------------|

| • VIN_B1, VIN_B2, VIN_B3, VIN_B4, AVIN, VIN_LDO1            | -0.3V to $6V$   |

| • SWx to PGNDx (DC)                                         | -0.3V to $6V$   |

| • SWx to PGNDx (<100ns)                                     | -0.3V to $6.5V$ |

| • SWx to PGNDx (<10ns)                                      | -2.5V to 9.0V   |

| • PGNDx to AGNDx                                            | 0.3V to 0.3V    |

| Other Pins to AGNDx                                         | -0.3V to 6V     |

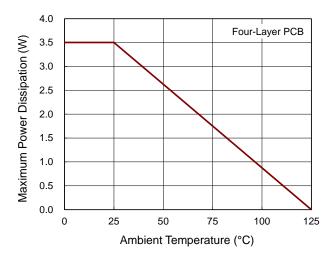

| • Power Dissipation, P <sub>D</sub> @ T <sub>A</sub> = 25°C |                 |

| WL-CSP-36B 2.66x2.70 (BSC)                                  | 3.5W            |

| Package Thermal Resistance (Note 4)                         |                 |

| WL-CSP-36B 2.66x2.70 (BSC), $\theta$ JA                     | 28.56°C/W       |

| • Lead Temperature (Soldering, 10 sec)                      | 260°C           |

| • Junction Temperature                                      | 150°C           |

| Storage Temperature Range                                   | –65°C to 150°C  |

| • ESD Susceptibility (Note 5)                               |                 |

| HBM (Human Body Model)                                      | ±2kV            |

| CDM (Charge Device Model)                                   | ±500V           |

|                                                             |                 |

- Note 3. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 4. θ<sub>JA</sub> is measured under natural convection (still air) at T<sub>A</sub> = 25°C with the component mounted on a high effectivethermal-conductivity four-layer test board on a JEDEC 51-9 thermal measurement standard.

- Note 5. Devices are ESD sensitive. Handling precautions are recommended.

## 11 Recommended Operating Conditions

#### (Note 6)

| • | Supply Input Voltage       | 2.7V to 3.7V |

|---|----------------------------|--------------|

| • | Other Pins                 | 0V to 5.5V   |

| • | Ambient Temperature Range  | 40°C to 85°C |

| • | Junction Temperature Range |              |

Note 6. The device is not guaranteed to function outside its operating conditions.

www.richtek.com

## 12 Electrical Characteristics

(VIN\_B1 = VIN\_B2 = VIN\_B3 = VIN\_B4 = AVIN = VIN\_LDO1 = 3.3V, T<sub>A</sub> = 25°C, unless otherwise specified.)

| Parameter                                                                                | Symbol          | Test Conditions                       | Min   | Тур | Max  | Unit |  |

|------------------------------------------------------------------------------------------|-----------------|---------------------------------------|-------|-----|------|------|--|

| Supply Input Volta                                                                       | ge Range        | ,                                     | 1     |     |      |      |  |

| VIN_B1 to<br>PGND12<br>VIN_B2 to<br>PGND12<br>VIN_B3 to<br>PGND34<br>VIN_B4 to<br>PGND34 | VVIN_Bx         | Input voltage range                   | 2.7   |     | 3.7  | V    |  |

|                                                                                          | VVIN_LDO1       | LDO mode                              | 1.62  |     | 5.5  |      |  |

| VIN_LDO1 to<br>AGND                                                                      | VVIN_LDO1_NLSW  | NLSW mode                             | 0.4   |     | 3.6  | V    |  |

|                                                                                          | VVIN_LDO1_PLSW  | PLSW mode                             | 1.62  | 1   | AVIN |      |  |

| A) //N/ 1 I) // O                                                                        | VAVIN_UV_F_TH   | Falling threshold                     | 2.4   | 2.5 | 2.6  | V    |  |

| AVIN UVLO                                                                                | Vavin_uvlo_hys  | Hysteresis                            |       | 100 |      | mV   |  |

| A) (IN L O) (                                                                            | Vavin_ov_r_th   | Rising threshold                      | 3.8   | 3.9 | 4    | V    |  |

| AVIN OV                                                                                  | VAVIN_OV_HYS    | Hysteresis                            |       | 300 |      | mV   |  |

|                                                                                          | Vavin_pok_r_th  | REG_0x10_bit 7 = 0b, rising threshold | 3.38  | 3.5 | 3.62 | V    |  |

| AVIN POK OV                                                                              | VAVIN_FOR_R_TH  | REG_0x10_bit 7 = 1b, rising threshold | 3.66  | 3.8 | 3.93 | V    |  |

|                                                                                          | Vavin_pok_hys   | Hysteresis                            | 100   | 200 | 300  | mV   |  |

|                                                                                          | tavin_pok_r_deg | Deglitch time                         |       | 10  |      | μS   |  |

| Operating Supply                                                                         | Current         |                                       |       |     |      |      |  |

| AVIN Supply<br>Current                                                                   | lavin_Q         | All rails are off                     |       | 30  |      | μΑ   |  |

| VIN_LDO1                                                                                 | IVIN_LDO1_Q     | Normal mode                           |       | 31  |      |      |  |

| VIIV_LDOT                                                                                | IVIN_LDO1_LPM_Q | Low power mode, LPM                   |       | 15  |      | μΑ   |  |

| VINI Dec                                                                                 | IVIN_Bx_Q       | Normal mode                           |       | 25  | 35   | ^    |  |

| VIN_Bx                                                                                   | IVIN_Bx_LPM_Q   | Low power mode, LPM                   |       | 15  | 25   | μΑ   |  |

| System Monitor/W                                                                         | arning          | ,                                     | 1     |     |      |      |  |

| SYSMON Rising<br>Threshold                                                               | VSYSMON_R_TH    | 25mV Step                             | 2.725 |     | 3.1  | V    |  |

| SYSMON<br>Accuracy                                                                       |                 |                                       | -3.5  |     | 3.5  | %    |  |

| SYSWARN Rising<br>Threshold                                                              | Vsyswarn_r_th   | 25mV Step                             | 2.755 |     | 3.15 | V    |  |

| SYSWARN<br>Accuracy                                                                      |                 |                                       | -3.5  |     | 3.5  | %    |  |

| Parameter                   | Symbol               | Test Conditions                   | Min | Тур  | Max | Unit |  |  |

|-----------------------------|----------------------|-----------------------------------|-----|------|-----|------|--|--|

| Input Deglitch Time         |                      |                                   |     |      |     |      |  |  |

| AVIN UV                     | tavin_uv_r_exit      |                                   |     | 20   |     | μS   |  |  |

| AVIN OV                     | tavin_ov_r_th        |                                   |     | 10   |     | μS   |  |  |

| Others                      |                      |                                   | 1   | I    |     |      |  |  |

|                             | TCritical_SD         | Temperature for critical shutdown |     | 150  |     |      |  |  |

| Over-Temperature Protection | TRecovery_HYS        | Hysteresis for thermal recovery   |     | 25   |     | °C   |  |  |

|                             | TInterrupt_TH        | Interrupt flag threshold          |     | 110  |     |      |  |  |

| OV/UV Retry Time            | tRecovery_Dwell_Time | VIN = 3.3V, power rails OV or UV  |     | 200  |     | ms   |  |  |

|                             |                      | Bx_ON_DLY_Bits = 000b             |     | 0    |     |      |  |  |

|                             |                      | Bx_ON_DLY_Bits = 001b             |     | 0.25 |     |      |  |  |

|                             |                      | Bx_ON_DLY_Bits = 010b             |     | 0.5  |     |      |  |  |

| Bx Startup Delay            |                      | Bx_ON_DLY_Bits = 011b             |     | 0.75 |     | me   |  |  |

| DX Startup Delay            |                      | Bx_ON_DLY_Bits = 100b             |     | 1    |     | ms   |  |  |

|                             |                      | Bx_ON_DLY_Bits = 101b             |     | 2    |     |      |  |  |

|                             |                      | Bx_ON_DLY_Bits = 110b             |     | 4    |     |      |  |  |

|                             |                      | Bx_ON_DLY_Bits = 111b             |     | 8    |     |      |  |  |

|                             |                      | Bx_OFF_DLY_Bits = 000b            |     | 0    |     |      |  |  |

|                             |                      | Bx_OFF_DLY_Bits = 001b            |     | 0.25 |     |      |  |  |

|                             |                      | Bx_OFF_DLY_Bits = 010b            |     | 0.5  |     |      |  |  |

| Dy Turn Off Doloy           |                      | Bx_OFF_DLY_Bits = 011b            |     | 0.75 |     | ma   |  |  |

| Bx Turn Off Delay           |                      | Bx_OFF_DLY_Bits = 100b            |     | 1    |     | ms   |  |  |

|                             |                      | Bx_OFF_DLY_Bits = 101b            |     | 2    |     |      |  |  |

|                             |                      | Bx_OFF_DLY_Bits = 110b            |     | 4    |     |      |  |  |

|                             |                      | Bx_OFF_DLY_Bits = 111b            |     | 8    |     |      |  |  |

|                             |                      | EXT_EN1_DLY_Bits = 0000b          |     | 0    |     |      |  |  |

|                             |                      | EXT_EN1_DLY_Bits = 0001b          |     | 0.25 |     |      |  |  |

|                             |                      | EXT_EN1_DLY_Bits = 0010b          |     | 0.5  |     |      |  |  |

|                             |                      | EXT_EN1_DLY_Bits = 0011b          |     | 0.75 |     |      |  |  |

| EXT_EN Delay                |                      | EXT_EN1_DLY_Bits = 0100b          |     | 1    |     | ms   |  |  |

|                             |                      | EXT_EN1_DLY_Bits = 0101b          |     | 1.25 |     |      |  |  |

|                             |                      | EXT_EN1_DLY_Bits = 0110b          |     | 1.5  |     |      |  |  |

|                             |                      | EXT_EN1_DLY_Bits = 0111b          |     | 1.75 |     |      |  |  |

|                             |                      | EXT_EN1_DLY_Bits = 1000b          |     | 2    |     |      |  |  |

| Parameter                    | Symbol        | Test Conditions                                                                                                              | Min          | Тур  | Max         | Unit |

|------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------------|------|

|                              |               | EXT_EN1_DLY_Bits = 1001b                                                                                                     |              | 2.25 |             |      |

|                              |               | EXT_EN1_DLY_Bits = 1010b                                                                                                     |              | 2.5  |             |      |

|                              |               | EXT_EN1_DLY_Bits = 1011b                                                                                                     |              | 2.75 |             |      |

|                              |               | EXT_EN1_DLY_Bits = 1100b                                                                                                     |              | 3    |             |      |

|                              |               | EXT_EN1_DLY_Bits = 1101b                                                                                                     |              | 3.25 |             |      |

|                              |               | EXT_EN1_DLY_Bits = 1110b                                                                                                     |              | 3.5  |             |      |

|                              |               | EXT_EN1_DLY_Bits = 1111b                                                                                                     |              | 3.75 |             |      |

|                              |               | POR_DLY_TIME_Bits = 000b                                                                                                     |              | 0.5  |             |      |

|                              |               | POR_DLY_TIME_Bits = 001b                                                                                                     |              | 1    |             |      |

|                              |               | POR_DLY_TIME_Bits = 010b                                                                                                     |              | 2    |             |      |

| , DEOET                      |               | POR_DLY_TIME_Bits = 011b                                                                                                     |              | 4    |             |      |

| nRESET                       |               | POR_DLY_TIME_Bits = 100b                                                                                                     |              | 8    |             | ms   |

|                              |               | POR_DLY_TIME_Bits = 101b                                                                                                     |              | 16   |             |      |

|                              |               | POR_DLY_TIME_Bits = 110b                                                                                                     |              | 32   |             |      |

|                              |               | POR_DLY_TIME_Bits = 111b                                                                                                     |              | 64   |             |      |

| Buck1 Converter              |               |                                                                                                                              |              |      |             |      |

| Output Voltage               | VB1_VOUT      | B1 (Buck1) VID Range                                                                                                         | 1.7          |      | 2.9         | V    |

| Range                        | VB1_Per_Step  | B1 programmable step                                                                                                         |              | 20   |             | mV   |

|                              | 1             | Enable, not switching                                                                                                        |              | 25   | 35          |      |

| Standby Current              | IStandby_B1   | Enable, not switching, LPM                                                                                                   |              | 15   | 25          | μΑ   |

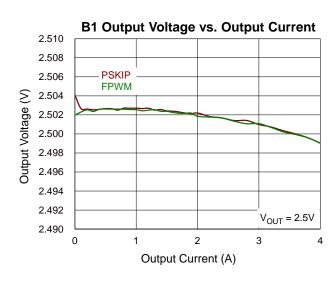

| Output Voltage<br>Accuracy   | VB1_Error     | GPIO2 = Hi-Z or Low                                                                                                          | 2.475        | 2.5  | 2.525       | V    |

| Line Regulation              |               | VIN = 2.7V to 3.7V                                                                                                           |              | 0.5  |             | %/V  |

| Load Regulation              |               | IOUT = 0 to Max Rating                                                                                                       |              | 0.5  |             | %/A  |

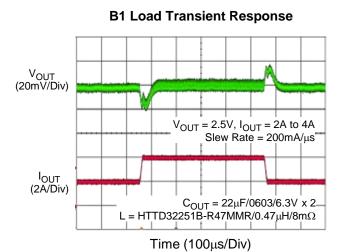

| Transient Load<br>Regulation | VB1_TLR_Error | VIN_B1 = 3.3V, FB1 = 2.5V,<br>L = 0.47μH, COUT = 22μF x 2.<br>1. Load = 1A to 2A @ 0.2A/μs<br>2. Load = 50mA to 1A @ 0.2A/μs | -75<br>(-3%) |      | 100<br>(4%) | mV   |

|                              | VB1_PGL_R_0b  | VOUT_B1 rises from 0V to PG rising (EFUSE_UVSEL = 0b, default)                                                               | 90           | 93   | 96          |      |

| PG Threshold (Low Level)     | VB1_PGL_R_1b  | VOUT_B1 rises from 0V to PG rising (EFUSE_UVSEL = 1b)                                                                        | 82           | 85   | 88          | %    |

|                              | VB1_PGL_HYS   | VOUT_B1 falls from VID to PG falling                                                                                         |              | 3    |             |      |

| Parameter                      | Symbol           | Test Conditions                                                                   | Min | Тур | Max | Unit |  |

|--------------------------------|------------------|-----------------------------------------------------------------------------------|-----|-----|-----|------|--|

| PG Threshold                   | VB1_PGH_F        | VOUT_B1 rises from VID to PG falling                                              | 107 | 110 | 113 | %    |  |

| (High Level)                   | VB1_PGH_HYS      | VOUT_B1 falls from VID to PG rising                                               |     | 3   |     | %    |  |

| Switching<br>Frequency         | fsw_B1           | REG_0x1B[3:1] = 101b                                                              | 1.8 | 2   | 2.2 | MHz  |  |

| Minimum Off-Time               | tB1_OFF_MIN      |                                                                                   |     | 120 | 160 | ns   |  |

|                                |                  | REG_0x19[7:6] = 00b. The time for VOUT to rise from 10% to 90% of 2.5V.           |     | 50  |     |      |  |

| Soft-Start Time                | to a second      | REG_0x19[7:6] = 01b (Default). The time for VOUT to rise from 10% to 90% of 2.5V. | 1   | 100 |     | 0    |  |

| Soit-Start Time                | tB1_Soft_Start   | REG_0x19[7:6] = 10b. The time for VOUT to rise from 10% to 90% of 2.5V.           | 1   | 200 |     | μѕ   |  |

|                                |                  | REG_0x19[7:6] = 11b. The time for VOUT to rise from 10% to 90% of 2.5V.           |     | 300 |     |      |  |

|                                | lB1_CL           | Valley Current, REG_0x1B[7:6] = 00b                                               | 3.5 | 4   |     | Α    |  |

| Commont Limit                  |                  | Valley Current, REG_0x1B[7:6] = 01b                                               | 4.5 | 5   |     |      |  |

| Current Limit                  |                  | Valley Current, REG_0x1B[7:6] = 10b                                               | 5.5 | 6   |     |      |  |

|                                |                  | Valley Current, REG_0x1B[7:6] = 11b                                               | 6.5 | 7   |     |      |  |

| PMOS On-<br>Resistance         | RDS(ON)_B1_P     | PVIN = 3.3V                                                                       |     | 60  |     | mΩ   |  |

| NMOS On-<br>Resistance         | RDS(ON)_B1_N     | PVIN = 3.3V                                                                       |     | 35  |     | mΩ   |  |

| Output Discharge<br>Resistance | RDISCH_B1        |                                                                                   |     | 4.4 |     | Ω    |  |

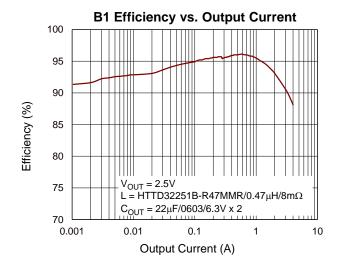

| Efficiency                     | no               | PVIN = 3.3V, FB_B1 = 2.5V,<br>IOUT = 10mA                                         | 85  |     |     | 0/   |  |

| Efficiency                     | ηв1              | PVIN = 3.3V, FB_B1 = 2.5V,<br>I <sub>OUT</sub> = 1A                               | 90  |     |     | %    |  |

| Buck1 Bypass Mo                | de               |                                                                                   |     |     |     |      |  |

| Input Voltage<br>Range         | VVIIN_B1_BYP     | GPIO2 = H                                                                         | 2.7 | 3.3 | 3.7 | V    |  |

| PMOS On-<br>Resistance         | RDS(ON)_B1_BYP_P | Isw = -1A, VIN_B1 = 3.3V                                                          |     | 60  |     | mΩ   |  |

| Parameter                                     | Symbol                | Test Conditions                                                                                                           | Min          | Тур  | Max        | Unit |  |

|-----------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------|--------------|------|------------|------|--|

| Internal PMOS<br>Shutdown Current             | lb1_byp_oc_off        | REG_0x1B[7:6] = any, all registers code (00~11) are the same as OC value                                                  | 4.5          | 5    |            | А    |  |

| Internal PMOS<br>Shutdown Current<br>Off-Time | tB1_BYP_OC_OFF        |                                                                                                                           |              | 14   |            | ms   |  |

| Internal PMOS<br>Soft-Start Time              | tB1_BYP_SStart        | PVIN = 3.3V                                                                                                               |              | 250  |            | μS   |  |

| OV Threshold                                  | VB1_BYP_OV_TH         |                                                                                                                           |              | 3.8  |            | V    |  |

| OV Deglitch Time                              | tB1_BYP_OV_DEG        |                                                                                                                           |              | 20   |            | μS   |  |

| Buck2 Converter                               |                       |                                                                                                                           |              |      |            |      |  |

| Output Voltage                                | V <sub>B2</sub> _vout | B2 (Buck2) VID range                                                                                                      | 0.5          |      | 1.3        | V    |  |

| Range                                         | VB2_Per_Step          | B2 programmable step                                                                                                      |              | 10   |            | mV   |  |

| Ota a dhaa Oasaa at                           | IStandby_B2           | Enable, not switching                                                                                                     |              | 25   | 35         |      |  |

| Standby Current                               |                       | Enable, not switching, LPM                                                                                                |              | 15   | 25         | μΑ   |  |

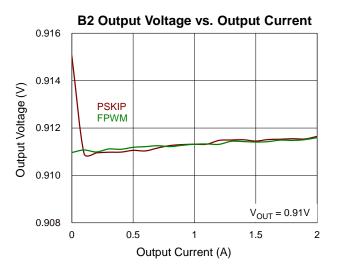

| Output Voltage<br>Accuracy                    | VB2_Error             | GPIO2 = any state                                                                                                         | 0.901        | 0.91 | 0.911      | V    |  |

| Line Regulation                               |                       | VIN = 2.7V to 3.7V                                                                                                        |              | 0.5  |            | %/V  |  |

| Load Regulation                               |                       | IOUT = 0 to max rating                                                                                                    |              | 0.5  |            | %/A  |  |

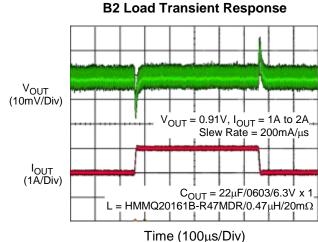

| Transient Load<br>Regulation                  | VB2_TLR_Error         | VIN_B2 = 3.3V, FB2 = 0.91V,<br>L = 0.47μH, COUT = 22μF.<br>1. Load = 1A to 2A @ 0.2A/μs<br>2. Load = 50mA to 1A @ 0.2A/μs | -27<br>(-3%) |      | 36<br>(4%) | mV   |  |

|                                               | VB2_PGL_R_0b          | VOUT_B2 rises from 0V to PG rising (EFUSE_UVSEL = 0b, Default)                                                            | 90           | 93   | 96         | %    |  |

| PG Threshold (Low Level)                      | VB2_PGL_R_1b          | VOUT_B2 rises from 0V to PG rising (EFUSE_UVSEL = 1b)                                                                     | 82           | 85   | 88         | %    |  |

|                                               | VB2_PGL_HYS           | VOUT_B2 falls from VID to PG falling                                                                                      |              | 3    |            | %    |  |

| PG Threshold                                  | VB2_PGH_F             | VOUT_B2 rises from VID to PG falling                                                                                      | 107          | 110  | 113        | %    |  |

| (High Level)                                  | VB2_PGH_HYS           | VOUT_B2 falls from VID to PG<br>Rising                                                                                    |              | 3    |            | %    |  |

| Switching<br>Frequency                        | fsw_B2                | REG_0x1D[3:1] = 101b                                                                                                      | 1.8          | 2    | 2.2        | MHz  |  |

| Parameter                      | Symbol         | Test Conditions                                                                    | Min    | Тур  | Max        | Unit |

|--------------------------------|----------------|------------------------------------------------------------------------------------|--------|------|------------|------|

|                                |                | REG_0x19[5:4] = 00b. The time for VOUT to rise from 10% to 90% of 0.91V.           |        | 40   |            | μS   |

| Soft-Start Time                | tB2_Soft_Start | REG_0x19[5:4] = 01b (default). The time for VOUT to rise from 10% to 90% of 0.91V. |        | 80   |            | μS   |

|                                |                | REG_0x19[5:4] = 10b. The time for VOUT to rise from 10% to 90% of 0.91V.           |        | 160  |            | μS   |

|                                |                | REG_0x19[5:4] = 11b. The time of 10% to 90% of VOUT = 0.91V.                       | -      | 240  | -          | us   |

|                                |                | Valley Current, REG_0x1D[7:6] = 00b                                                | 1.5    | 2    |            | Α    |

| Current Limit                  | lno o          | Valley Current, REG_0x1D[7:6] = 01b                                                | 2.5    | 3    |            | Α    |

| Current Limit                  | lB2_CL         | Valley Current, REG_0x1D[7:6] = 10b                                                | 3.5    | 4    |            | Α    |

|                                |                | Valley Current, REG_0x1D[7:6] = 11b                                                | 4.5    | 5    |            | А    |

| PMOS On-<br>Resistance         | RDS(ON)_B2_P   | PVIN = 3.3V                                                                        |        | 65   |            | mΩ   |

| NMOS On-<br>Resistance         | RDS(ON)_B2_N   | PVIN = 3.3V                                                                        |        | 30   |            | mΩ   |

| Output Discharge<br>Resistance | RDISCH_B2      |                                                                                    |        | 9.4  |            | Ω    |

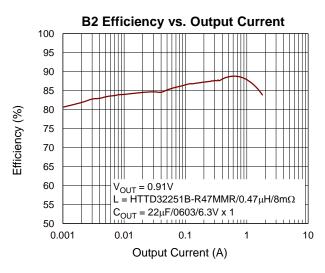

| F#:-:                          | n              | PVIN = 3.3V, FB_B1 = 0.91V,<br>IOUT = 10mA                                         | 85     |      |            | 0/   |

| Efficiency                     | ηв2            | PVIN = 3.3V, FB_B1 = 0.91V,<br>IOUT = 1A                                           | 85     |      |            | %    |

| Buck3 Converter                |                | •                                                                                  |        |      |            |      |

| Output Voltage                 | VB3_VOUT       | B3 (Buck3) VID range                                                               | 0.5    |      | 1.3        | V    |

| Range                          | VB3_Per_Step   | B3 programmable step                                                               |        | 10   |            | mV   |

| Standby Current                | Standby D2     | Enable, not switching                                                              |        | 25   | 35         | ,. ^ |

| Standby Current                | IStandby_B3    | Enable, not switching, LPM                                                         |        | 15   | 25         | μΑ   |

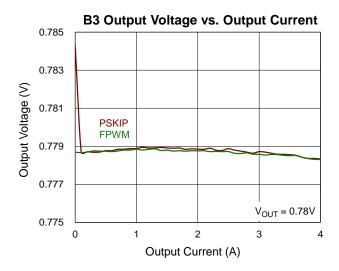

| Output Voltage<br>Accuracy     | VB3_Error      | GPIO3 = any state                                                                  | 0.7722 | 0.78 | 0.787<br>8 | V    |

| Line Regulation                |                | VIN = 2.7V to 3.7V                                                                 |        | 0.5  |            | %/V  |

| Load Regulation                |                | IOUT = 0 to max rating                                                             |        | 0.5  |            | %/A  |

| Parameter                    | Symbol         | Test Conditions                                                                                                                       | Min              | Тур | Max          | Unit |

|------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|--------------|------|

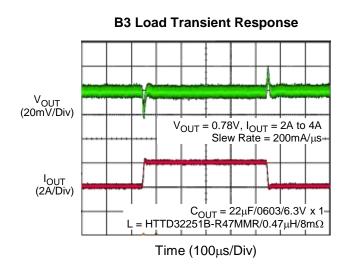

| Transient Load<br>Regulation | VB3_TLR_Error  | VIN_B3 = 3.3V, FB3 = 0.78V,<br>L = 0.47μH, C <sub>OUT</sub> = 22μF.<br>1. Load = 2A to 4A @ 0.2A/μs<br>2. Load = 50mA to 2A @ 0.2A/μs | -27.3<br>(-3.5%) |     | 31.2<br>(4%) | mV   |

|                              | VB3_PGL_R_0b   | VOUT_B3 rises from 0V to PG rising (EFUSE_UVSEL = 0b, Default)                                                                        | 90               | 93  | 96           |      |

| PG Threshold (Low Level)     | VB3_PGL_R_1b   | VOUT_B3 rises from 0V to PG rising (EFUSE_UVSEL = 1b)                                                                                 | 82               | 85  | 88           | %    |

|                              | VB3_PGL_HYS    | VOUT_B3 falls from VID to PG falling                                                                                                  |                  | 3   |              |      |

| PG Threshold                 | VB3_PGH_F      | VOUT_B3 rises from VID to PG falling                                                                                                  | 107              | 110 | 113          | 0/   |

| (High Level)                 | VB3_PGH_HYS    | VOUT_B3 falls from VID to PG rising                                                                                                   |                  | 3   |              | %    |

| Switching<br>Frequency       | fsw_B3         | REG_0x1F[3:1] = 101b                                                                                                                  | 1.8              | 2   | 2.2          | MHz  |

|                              |                | REG_0x19[3:2] = 00b. The time for VOUT to rise from 10% to 90% of 0.78V.                                                              |                  | 35  |              |      |

| 0.50.47                      | tB3_Soft_Start | REG_0x19[3:2] = 01b (default) . The time for VOUT to rise from 10% to 90% of 0.78V.                                                   |                  | 70  |              |      |

| Soft-Start Time              |                | REG_0x19[3:2] = 10b. The time for VOUT to rise from 10% to 90% of 0.78V.                                                              |                  | 140 |              | μS   |

|                              |                | REG_0x19[3:2] = 11b. The time for VOUT to rise from 10% to 90% of 0.78V.                                                              |                  | 210 |              |      |

|                              |                | Valley Current, REG_0x1F[7:6] = 00b                                                                                                   | 3.5              | 4   |              |      |

|                              |                | Valley Current, REG_0x1F[7:6] = 01b                                                                                                   | 4.5              | 5   |              | A    |

| Current Limit                | lB3_CL         | Valley Current, REG_0x1F[7:6] = 10b                                                                                                   | 5.5              | 6   |              |      |

|                              |                | Valley Current, REG_0x1F[7:6] = 11b                                                                                                   | 6.5              | 7   |              |      |

| PMOS On-<br>Resistance       | RDS(ON)_B3_P   | PVIN = 3.3V                                                                                                                           |                  | 55  |              | mΩ   |

| NMOS On-<br>Resistance       | RDS(ON)_B3_N   | PVIN = 3.3V                                                                                                                           |                  | 25  |              | mΩ   |

| Parameter                      | Symbol        | Test Conditions                                                                                                                      | Min          | Тур | Max        | Unit       |  |

|--------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------|-----|------------|------------|--|

|                                |               | REG_0x1F[5:4] = 00b                                                                                                                  |              | 20  |            |            |  |

| Dynamic Voltage                | \/            | REG_0x1F[5:4] = 01b                                                                                                                  |              | 15  |            | ma\ // . a |  |

| Scaling Rate                   | VDVID_UP_B3   | REG_0x1F[5:4] = 10b                                                                                                                  |              | 10  |            | mV/μs      |  |

|                                |               | REG_0x1F[5:4] = 11b                                                                                                                  |              | 5   |            |            |  |

| Output Discharge<br>Resistance | RDISCH_B3     |                                                                                                                                      |              | 9.4 |            | Ω          |  |

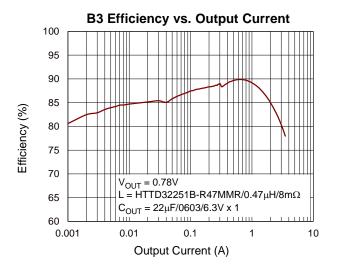

| <b>-</b>                       |               | PVIN = 3.3V, FB_B3 = 0.78V,<br>IOUT= 1mA, LPM                                                                                        | 80           |     |            | 0/         |  |

| Efficiency                     | ηв3           | PVIN = 3.3V, FB_B3 = 0.78V,<br>IOUT = 1A                                                                                             | 85           |     |            | %          |  |

| Buck4 Converter                |               |                                                                                                                                      |              |     | •          |            |  |

| Output Voltage                 | VB4_VOUT      | B4 (Buck4) VID range                                                                                                                 | 0.9          |     | 2.0        | V          |  |

| Range                          | VB4_Per_Step  | B4 programmable step                                                                                                                 |              | 10  |            | mV         |  |

| Charadha Carrant               | la            | Enable, not switching                                                                                                                |              | 25  | 35         |            |  |

| Standby Current                | Standbyt_B4   | Enable, not switching, LPM                                                                                                           |              | 15  | 25         | μА         |  |

| Output Voltage<br>Accuracy     | VB4_Error     | GPIO4 = High                                                                                                                         | 1.089        | 1.1 | 1.111      | V          |  |

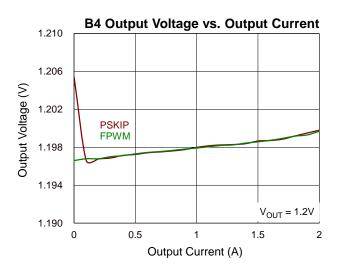

| Output Voltage<br>Accuracy     | VB4_Error     | GPIO4 = Hi-Z or Low                                                                                                                  | 1.188        | 1.2 | 1.212      | V          |  |

| Line Regulation                |               | VIN = 2.7V to 3.7V                                                                                                                   | 1            | 0.5 |            | %/V        |  |

| Load Regulation                |               | IOUT = 0 to max rating                                                                                                               |              | 0.5 |            | %/A        |  |

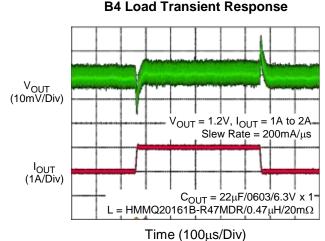

| Transient Load                 | Vo. T. D. F.  | VIN_B4 = 3.3V, FB4 = 1.1V,<br>L = 0.47μH, C <sub>OUT</sub> = 22μF.<br>1. Load = 1A to 2A @ 0.2A/μs<br>2. Load = 50mA to 1A @ 0.2A/μs | -33<br>(-3%) |     | 44<br>(4%) | mV         |  |

| Regulation                     | VB4_TLR_Error | VIN_B4 = 3.3V, FB4 = 1.2V,<br>L = 0.47μH, C <sub>OUT</sub> = 22μF.<br>1. Load = 1A to 2A @ 0.2A/μs<br>2. Load = 50mA to 1A @ 0.2A/μs | -36<br>(-3%) |     | 48<br>(4%) | IIIV       |  |

|                                | VB4_PGL_R_0b  | VOUT_B4 rises from 0V to PG rising (EFUSE_UVSEL = 0b, default)                                                                       | 90           | 93  | 96         |            |  |

| PG Threshold (Low<br>Level)    | VB4_PGL_R_1b  | VOUT_B4 rises from 0V to PG rising (EFUSE_UVSEL = 1b)                                                                                | 82           | 85  | 88         | %          |  |

|                                | VB4_PGL_HYS   | VOUT_B4 falls from VID to PG falling                                                                                                 |              | 3   |            |            |  |

| PG Threshold                   | VB4_PGH_F     | VOUT_B4 rises from VID to PG falling                                                                                                 | 107          | 110 | 113        | 0.4        |  |

| (High Level)                   | VB4_PGH_HYS   | VOUT_B4 falls from VID to PG rising                                                                                                  |              | 3   |            | %          |  |

| Parameter                      | Symbol           | Test Conditions                                                                  | Min              | Тур | Max | Unit |  |

|--------------------------------|------------------|----------------------------------------------------------------------------------|------------------|-----|-----|------|--|

| Switching<br>Frequency         | fsw_B4           | REG_0x22[3:1] = 101b                                                             | 1.8              | 2   | 2.2 | MHz  |  |

|                                |                  | REG_0x19[1:0] = 00b. The time for VOUT to rise from 10% to 90% of 1.1V           |                  | 45  |     |      |  |

| Soft-Start Time                | to a const       | REG_0x19[1:0] = 01b (default). The time for VOUT to rise from 10% to 90% of 1.1V |                  | 90  |     |      |  |

| Soit-Start Time                | tB4_Soft_Start   | REG_0x19[1:0] = 10b. The time for VOUT to rise from 10% to 90% of 1.1V           | I                | 180 |     | μS   |  |

|                                |                  | REG_0x19[1:0] = 11b. The time for VOUT to rise from 10% to 90% of 1.1V           |                  | 270 |     |      |  |

|                                |                  | Valley Current, REG_0x22[7:6] = 00b                                              | 1.5              | 2   |     |      |  |

| Current Limit                  | lb4_cl           | Valley Current, REG_0x22[7:6] = 01b                                              | 2.5              | 3   |     | Α    |  |

|                                |                  | Valley Current, REG_0x22[7:6] = 10b                                              | 3.5              | 4   |     |      |  |

|                                |                  | Valley Current, REG_0x22[7:6] = 11b                                              | 4.5              | 5   |     |      |  |

| PMOS On-<br>Resistance         | RDS(ON)_B4_P     | PVIN = 3.3V                                                                      |                  | 70  |     | mΩ   |  |

| NMOS On-<br>Resistance         | RDS(ON)_B4_N     | PVIN = 3.3V                                                                      |                  | 40  |     | mΩ   |  |

| Output Discharge<br>Resistance | RDISCH_B4        |                                                                                  |                  | 9.4 |     | Ω    |  |

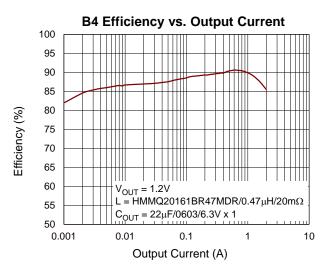

| Efficiency                     | η <sub>в4</sub>  | PVIN = 3.3V, FB_B4 = 1.2V,<br>IOUT = 10mA, LPM                                   | 85               |     |     | 0/   |  |

|                                |                  | PVIN = 3.3V, FB_B4 = 1.2V,<br>IOUT = 1A                                          | 85               |     |     | %    |  |

| B4_LDO Mode                    |                  |                                                                                  |                  | •   |     |      |  |

| Output Voltage<br>Range        | VB4_LDO_VOUT     | GPIO4 = Hi-Z for optional setting                                                | 0.9              | 1.8 | 2.0 | V    |  |

| Output Voltage<br>Range        | VB4_LDO_Per_Step | B4_LDO programmable step                                                         | -                | 10  |     | mV   |  |

| Standby Current                | IStandby_B4_LDO  | Enabled, no load,<br>low power mode                                              |                  | 15  |     | μА   |  |

|                                | IStandby_64_LDO  | Enabled, no load                                                                 | Enabled, no load | -   | 31  |      |  |

| Parameter                          | Symbol                | Test Conditions                                                                                                                          | Min  | Тур | Max  | Unit |  |

|------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|--|

| Output Voltage                     | Vp4 1 p0 5            | AVIN > B4_LDO + 0.4V @ Normal,<br>VNOM = 1.8V (25°C)                                                                                     | -1   |     | 1    | %    |  |

| Accuracy                           | VB4_LDO_Error         | AVIN > B4_LDO + 0.4V@ Normal,<br>VNOM = 1.8V (-40~125°C)                                                                                 | -1.5 |     | 1.5  | - %  |  |

| Line Regulation (GBD) (Note 7)     |                       | AVIN = 2.7V to 3.3V, B4_LDO Load 5mA @ Normal, VNOM = 1.8V                                                                               |      | 0.5 |      | %/V  |  |

| Load Regulation<br>(GBD)           |                       | AVIN > B4_LDO + 0.4V,<br>Load = 1mA to 390mA @ Normal<br>VNOM = 1.8V                                                                     |      | 0.5 |      | %/A  |  |

| Transient Load<br>Regulation (GBD) | VB4_LDO_TLR_Err       | AVIN > B4_LDO + 0.4V<br>VNOM = 1.8V, C <sub>OUT</sub> = 2.2μF<br>1. Load = 5mA to 50mA @ 0.2A/μs<br>2. Load = 50mA to 100mA @<br>0.2A/μs | -3.5 |     | +3.5 | %    |  |

|                                    | VB4_LDO_PGL_R_0b      | VOUT_B4_LDO rises from 0V to PG rising (EFUSE_UVSEL = 0b, default)                                                                       | 90   | 93  | 96   |      |  |

| PG Threshold (Low<br>Level)        | VB4_LDO_PGL_R_1b      | VOUT_B4_LDO rises from 0V to PG rising (EFUSE_UVSEL = 1b)                                                                                | 82   | 85  | 88   | %    |  |

|                                    | VB4_LDO_PGL_HYS       | VOUT_B4_LDO falls from VID to PG falling                                                                                                 |      | 3   |      |      |  |

| PG Threshold                       | VB4_LDO_PGH_F         | VOUT_B4_LDO rises from VID to PG falling                                                                                                 | 107  | 110 | 113  | 0/   |  |

| (High Level)                       | VB4_LDO_PGH_HYS       | VOUT_B4_LDO falls from VID to PG rising                                                                                                  |      | 3   |      | %    |  |

| Soft-Start Time                    | <b>t</b> aa. a. a. a  | B4_LDO = 10% to 90% of VNOM,<br>REG_0x19[0] = 0b                                                                                         |      | 140 |      | _    |  |

| Soit-Start Time                    | tB4_LDO_Soft_Start    | B4_LDO = 10% to 90% of VNOM,<br>REG_0x19[0] = 1b                                                                                         |      | 280 |      | μS   |  |

| D                                  | V                     | AVIN = 2.7V, B4_LDO = 2.6V,<br>Load = 200mA @ Normal                                                                                     |      |     | 200  | \/   |  |

| Dropout Voltage                    | VB4_LDO_DROP          | AVIN = 2.7V, B4_LDO = 2.5V,<br>Load = 400mA @ Normal                                                                                     |      |     | 400  | mV   |  |

| Discharge<br>Resistance            | RDISCH_B4_LDO         |                                                                                                                                          |      | 9.4 |      | Ω    |  |

| Overcurrent<br>Protection          | la os. s:             | AVIN > B4_LDO + 0.4V @ Normal,<br>REG_0x22[6] = 0b                                                                                       | 300  | 400 |      | A    |  |

|                                    | B4_LOD_CL             | AVIN > B4_LDO + 0.4V @ Normal,<br>REG_0x22[6] = 1b (default)                                                                             | 400  | 500 |      | mA   |  |

| PG/OV Deglitch<br>Time (GBD)       | tB4_LDO_PG/OV_<br>DEG |                                                                                                                                          |      | 20  |      | μS   |  |

| Parameter                              | Symbol            | Test Conditions                                                                                                                                  | Min  | Тур | Max | Unit |

|----------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| LDO1                                   |                   |                                                                                                                                                  |      |     |     |      |

| Output Voltage<br>Range                | VLDO1_VOUT        | LDO1 VID range                                                                                                                                   | 1    | 1.8 | 2.7 | V    |

| Output Voltage<br>Programmable<br>Step | VLDO1_Per_Step    | LDO1 programmable step                                                                                                                           |      | 50  |     | mV   |

| Standby Current                        | lStandby_LDO1     | Enabled, no load,<br>low power mode                                                                                                              |      | 15  |     | μА   |

| , -                                    |                   | Enabled, no load,                                                                                                                                |      | 31  |     | ·    |

| Output Voltage                         | W pour 5          | AVIN = VIN_LDO1 > LDO1 + 0.4V<br>@ Normal, VNOM = 2.5V (25°C)                                                                                    | -1   |     | 1   | %    |

| Accuracy                               | VLDO1_Error       | AVIN = VIN_LDO1 > LDO1 + 0.4V@<br>Normal, VNOM = 2.5V (-40~125°C)                                                                                | -1.5 |     | 1.5 |      |

| Line Regulation<br>(GBD)               |                   | AVIN = VIN_LDO1 = 2.7V to 3.3V,<br>LDO1 Load 5mA @ Normal,<br>VNOM = 2.5V.                                                                       | 1    | 0.5 |     | %/V  |

| Load Regulation<br>(GBD)               |                   | AVIN = VIN_LDO1 > LDO1 + 0.4V,<br>LDO1 Load = 1mA to 390mA @<br>Normal, VNOM = 2.5V.                                                             |      | 0.5 |     | %/A  |

| Transient Load<br>Regulation (GBD)     | VLDO1_TLR_Err     | AVIN = VIN_LDO1 > LDO1 + 0.4V,<br>VNOM = 2.5V, C <sub>OUT</sub> = 2.2μF<br>1. Load= 5mA to 50mA @ 0.2A/μs<br>2. Load= 50mA to 100mA @<br>0.2A/μs | -3.5 |     | 3.5 | %    |

| PG Threshold (Low                      | VLDO1_PGL_R       | V <sub>LDO1</sub> rises from 0V to PG rising                                                                                                     | 81   | 84  | 88  | %    |

| Level)                                 | VLDO1_PGL_HYS     | VLDO1 falls from VID to PG falling                                                                                                               |      | 4   |     | %    |

| PG Threshold                           | VLDO1_PGH_F       | VLDO1 rises from VID to PG falling                                                                                                               | 111  | 114 | 118 | %    |

| (High Level)                           | VLDO1_PGH_HYS     | VLDO1 falls from OV to PG rising                                                                                                                 |      | 8   |     | %    |

| Coft Ctart Time                        | t. D. 0. 0. 0. 1. | LDO1 = 10% to 90% of VNOM,<br>REG_0x1A[7] = 0b (Default)                                                                                         |      | 60  |     | 0    |

| Soft-Start Time                        | tLDO1_Soft_Start  | LDO1 = 10% to 90% of VNOM,<br>REG_0x1A[7] = 1b                                                                                                   |      | 120 |     | μS   |

| Dropout Voltage                        | V/ po4 5505       | AVIN = VIN_LDO1 = 2.7V,<br>LDO1 = 2.6V, Load = 200mA @<br>Normal                                                                                 |      |     | 200 | m\/  |

|                                        | VLDO1_DROP        | AVIN = VIN_LDO1 = 2.7V,<br>LDO1 = 2.5V, Load = 400mA @<br>Normal                                                                                 |      |     | 400 | mV   |

| Discharge<br>Resistance                | RDISCH_LDO1       | Discharged path enabled when LDO1 is disabled.                                                                                                   |      | 20  |     | Ω    |

| Parameter                              | Symbol              | Test Conditions                                                | Min  | Тур  | Max        | Unit |  |

|----------------------------------------|---------------------|----------------------------------------------------------------|------|------|------------|------|--|

| Overcurrent                            | li on co            | AVIN = VIN_LDO1 > LDO1 + 0.4V<br>@ Normal, EFUSE_LDO1_LIM = 0b | 300  | 400  |            | A    |  |

| Protection                             | ILOD1_CL            | AVIN = VIN_LDO1 > LDO1 + 0.4V<br>@ Normal, EFUSE_LDO1_LIM = 1b | 400  | 500  |            | mA   |  |

| LDO1_LSW Mode                          | (Load Switch)       |                                                                |      |      |            |      |  |

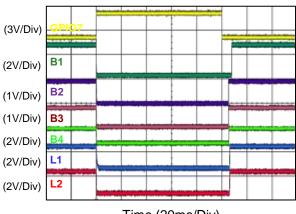

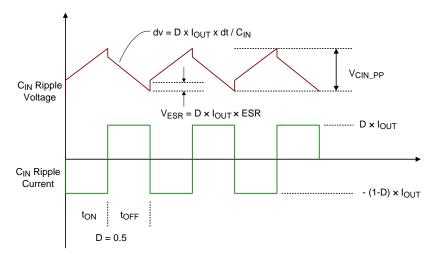

| Operating Voltage                      | Vi pod ciw vini     | NLSW mode, GPIO4 = Hi-z<br>EFUSE_LDO1_LSW_SEL = 0b             | 0.4  |      | AVIN<br>-1 | V    |  |