### **SSD Power Management Total Solution**

### **General Description**

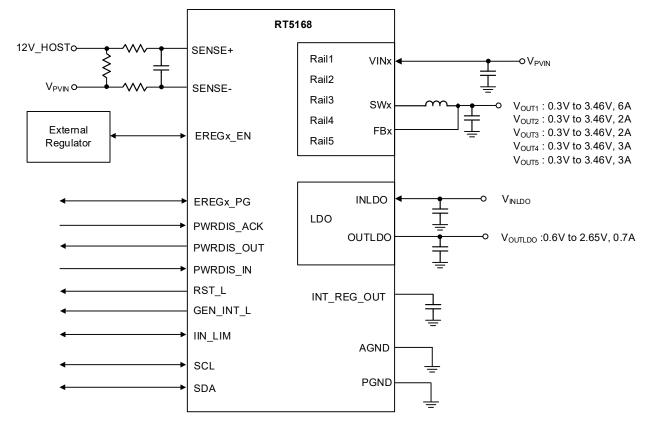

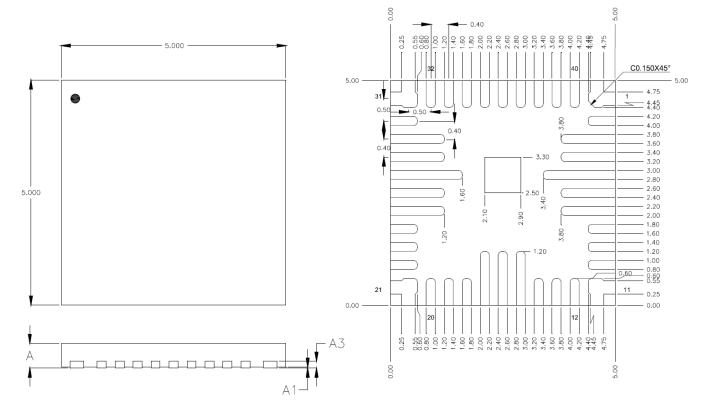

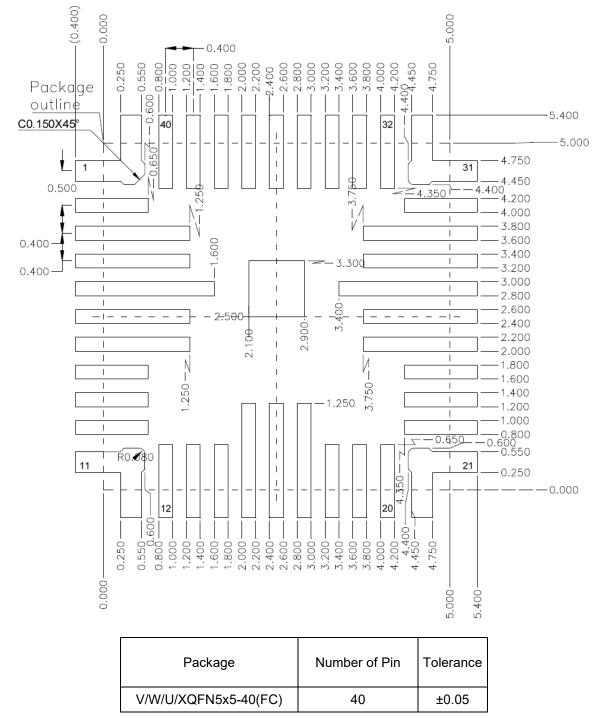

The RT5168 is an integrated solution for SSD power management IC. This device provides 5 single Buck voltage regulators (Rail1 to Rail5) and 1 LDO. Among the 5 voltage regulators, the Rail1, Rail2, Rail3 and Rail4 can operate either in single phase mode or dual phase mode. A complete protection mechanism is also embedded for safe power distribution and the corresponding fault events can be recorded by the registers. The RT5168 is available in a UQFN-40L.5x5-FC package. The recommended junction temperature is 0°C to 125°C, and the ambient temperature is 0°C to 85°C.

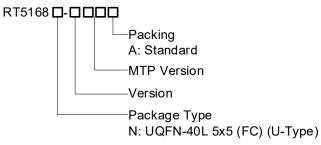

### **Ordering Information**

Note:

Richtek products are Richtek Green Policy compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

### **Marking Information**

RT5168 N100 YMDNN RT5168N100: Product Code YMDNN: Date Code

### Features

- Wide Input Supply Range: 4V to 16V

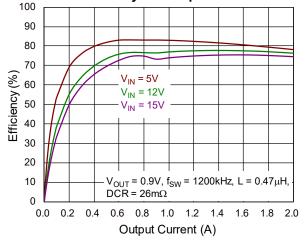

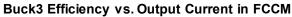

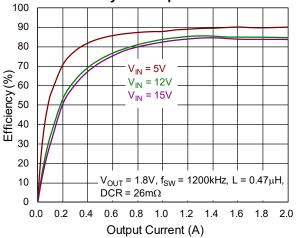

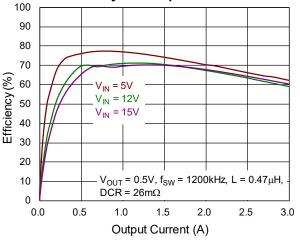

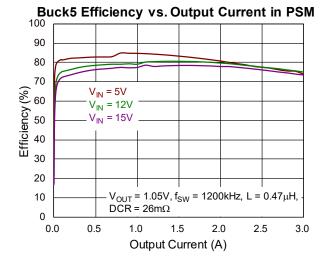

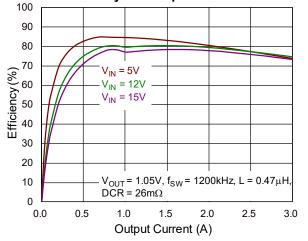

- High efficiency for each Buck Converter

- Configurable Outputs

- ▶ ±1% Feedback Voltage Accuracy

- DVID Change for all Bucks via I<sup>2</sup>C Interface

- Adjustable Enable Time and Soft-start Time for all VRs.

- Selectable Switching Frequency for Each Buck Rail

- Smart Protection Unit Provides Best Protection

Shutdown Sequence Control

- Dual-Phase DEM Operation Implements Good Light Load Efficiency and Good Transient Response

- 11 Bits ADC Reporting for VIN and IIN

- Non-Volatile Register Configurability

- I<sup>2</sup>C Interface 400kHz/1MHz

- Control and Command Unit

- Power Indication (RST\_L) and Interrupt Indication (GEN\_INT\_L)

- Power Disable Mode

- External Regulator Enable and Power Good Monitoring

- IIN\_LIM for OverCurrent Indicator

### Applications

• SSD

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

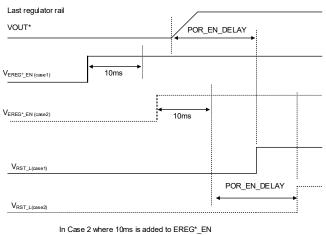

### **Simplified Application Circuit**

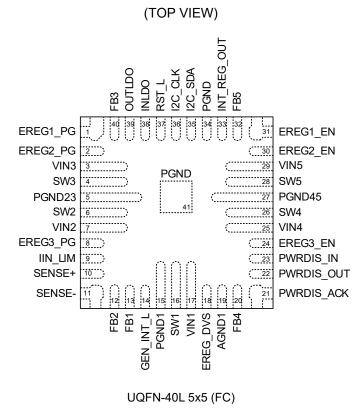

**Pin Configuration**

### **Functional Pin Description**

| Pin No.   | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1 11 110. |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 1         | EREG1_PG | External Regulator 1 power good input. This pin can also be configured<br>as an open-drain output pin by the setting of REG_0x6A[2], and the<br>output high or low are determined by REG_0x18[3]. In open-drain<br>output, the pull-up and pull-down resistors can be determined by<br>REG_0x75[4] to be provided externally or internally. If 0x75[4] = 0b<br>(resistors provided from internally), the output voltage, pull-up resistor,<br>and pull-down resistor parameters are determined by REG_0x6A[7:3]. |  |  |  |  |

| 2         | EREG2_PG | External Regulator 2 power good input. This pin can also be configured<br>as an open-drain output pin by the setting of REG_0x6B[2], and the<br>output high or low are determined by REG_0x18[2]. In open-drain<br>output, the pull-up and pull-down resistors can be determined by<br>REG_0x75[3] to be provided externally or internally. If 0x75[3] = 0b<br>(resistors provided from internally), the output voltage, pull-up resistor,<br>and pull-down resistor parameters are determined by REG_0x6B[7:3]. |  |  |  |  |

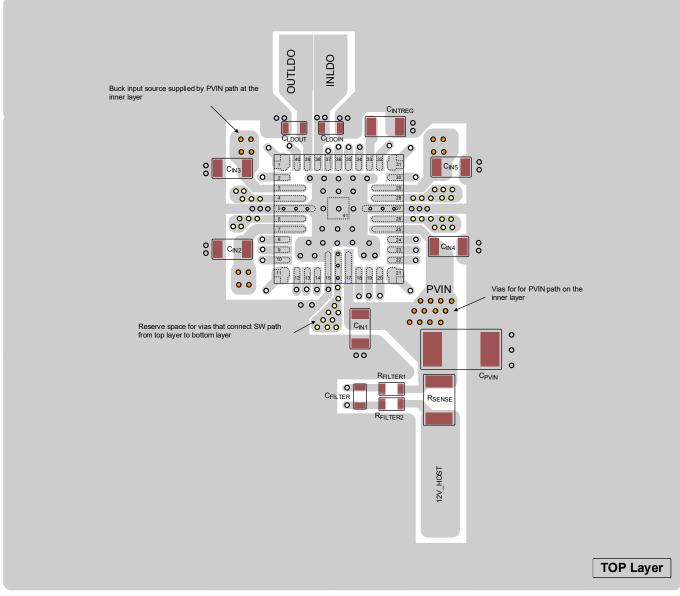

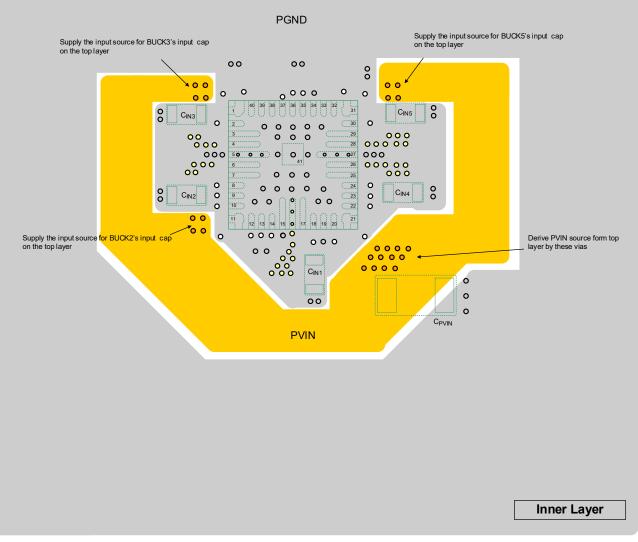

| 3         | VIN3     | Rail3 input supply. It is internally connected to the source terminal of the Rail3 high-side MOSFET. Use wide PCB traces and multiple vias to make the connection. Apply at least two layers for the input trace. Connecting the ceramic capacitor (C = $10\mu$ F/0805) as close as possible from VIN3 pin to PGND23 pin is necessary.                                                                                                                                                                           |  |  |  |  |

| 4         | SW3      | Switch node of the Rail3. It is internally connected to the drain terminal of the high-side MOSFET and the drain terminal of the low-side MOSFET. Connect this pin to output inductor and keep the sensitive trace and signals away.                                                                                                                                                                                                                                                                             |  |  |  |  |

| 5         | PGND23   | Ground return from low-side power MOSFET and driver of Rail2 and Rail3. Directly soldering to a large PCB PGND plane and connecting thermal vias under PGND pin are required to minimize the parasitic impedance and thermal resistance.                                                                                                                                                                                                                                                                         |  |  |  |  |

| 6         | SW2      | Switch node of the Rail2. It is internally connected to the drain terminal of the high-side MOSFET and the drain terminal of the low-side MOSFET. Connect this pin to output inductor and keep the sensitive trace and signals away.                                                                                                                                                                                                                                                                             |  |  |  |  |

| 7         | VIN2     | Rail2 input supply. It is internally connected to the source terminal of the Rail2 high-side MOSFET. Use wide PCB traces and multiple vias to make the connection. Apply at least two layers for the input trace. Connecting the ceramic capacitor (C = $10\mu$ F/0805) as close as possible from VIN2 pin to PGND23 pin is necessary.                                                                                                                                                                           |  |  |  |  |

| 8         | EREG3_PG | External Regulator 3 power good input. This pin can also be configured<br>as an open-drain output pin by the setting of REG_0x6C[2], and the<br>output high or low are determined by REG_0x18[1]. In open-drain<br>output, the pull-up and pull-down resistors can be determined by<br>REG_0x75[2] to be provided externally or internally. If 0x75[2] = 0b<br>(resistors provided from internally), the output voltage, pull-up resistor,<br>and pull-down resistor parameters are determined by REG_0x6C[7:3]. |  |  |  |  |

| 9         | IIN_LIM  | Fault indicator for input overcurrent. It is an open-drain output. The pull-<br>up and pull-down resistors can be determined by REG_0x6E[0] to be<br>provided externally or internally. If 0x6E[0] = 0b (resistors provided from<br>internally), the output voltage, pull-up resistor, and pull-down resistor<br>parameters are determined by REG_0x6E[7:3].                                                                                                                                                     |  |  |  |  |

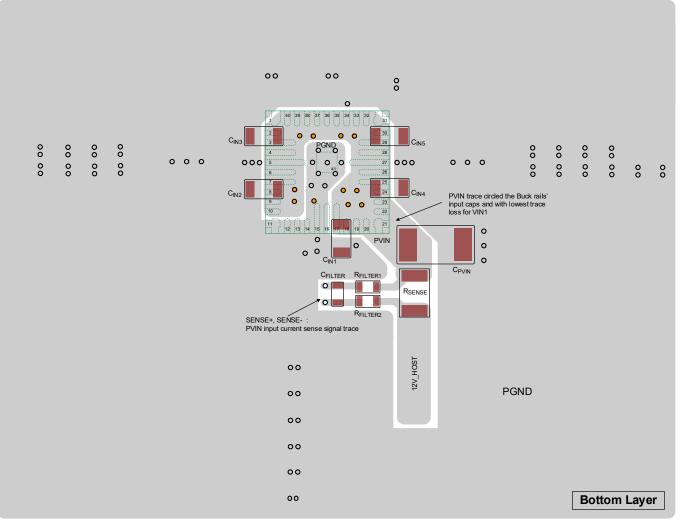

| 10        | SENSE+   | Input current sense positive node. It is recommended to add an RC filter externally, as shown in Figure 5. The recommended value for $R_{\text{filter}}$ is 4.7 $\Omega$ , and the recommended value for $C_{\text{Filter}}$ is 1 $\mu$ F.                                                                                                                                                                                                                                                                       |  |  |  |  |

| 11        | SENSE-   | Input current sense negative node.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

| Pin No. | Pin Name   | Pin Function                                                                                                                                                                                                                                                                                                                           |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

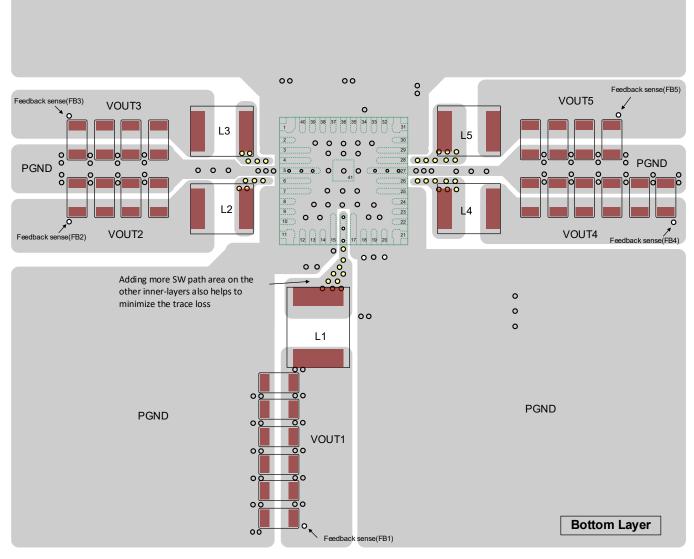

| 12      | FB2        | Rail2 feedback sense for output regulation. It is also used to detect output voltage status for OVP, UVP and Power good of Rail2.                                                                                                                                                                                                      |

| 13      | FB1        | Rail1 feedback sense for output regulation. It is also used to detect output voltage status for OVP, UVP and Power good of Rail1.                                                                                                                                                                                                      |

| 14      | GEN_INT_L  | General interrupt. It is an open-drain output. The pull-up and pull-down resistors can be determined by REG_0x66[0] to be provided externally or internally. If 0x66[0] =0b (resistors provided from internally), the output voltage, pull-up resistor, and pull-down resistor parameters are determined by REG_0x66 [7:3].            |

| 15      | PGND1      | Ground return from low-side power MOSFET and driver of Rail1.<br>Directly soldering to a large PCB PGND plane and connecting thermal<br>vias under PGND pin are required to minimize the parasitic impedance<br>and thermal resistance.                                                                                                |

| 16      | SW1        | Switch node of the Rail1. It is internally connected to the drain terminal of the high-side MOSFET and the drain terminal of the low-side MOSFET. Connect this pin to output inductor and keep the sensitive trace and signals away.                                                                                                   |

| 17      | VIN1       | Rail1 input supply. It is internally connected to the source terminal of the Rail1 high-side MOSFET. Use wide PCB traces and multiple vias to make the connection. Apply at least two layers for the input trace. Connecting the ceramic capacitor (C = $10\mu$ F/0805) as close as possible from VIN1 pin to PGND1 pin is necessary.  |

| 18      | EREG_DVS   | EREG_DVS is an open-drain output for external regulator's input<br>requirement. This pin is capable of outputting high, low, and Hi-Z three<br>states. Its Pull-up resistor, Pull-down resistor, output high-level voltage,<br>and output Hi-Z state are determined by REG_0x6D [7:2].                                                 |

| 19      | AGND1      | Ground of internal analog circuitry. AGND must be connected to the PGND plane through a single point.                                                                                                                                                                                                                                  |

| 20      | FB4        | Rail4 feedback sense for output regulation. It is also used to detect output voltage status for OVP, UVP and Power good of Rail4.                                                                                                                                                                                                      |

| 21      | PWRDIS_ACK | Power disable ack input. Regarding the functionality and description of this pin, please refer to the section "Power Disable Mode".                                                                                                                                                                                                    |

| 22      | PWRDIS_OUT | Power disable output. Regarding the functionality and description of this pin, please refer to the section "Power Disable Mode".                                                                                                                                                                                                       |

| 23      | PWRDIS_IN  | Power disable PMIC input. Regarding the functionality and description of this pin, please refer to the section "Power Disable Mode".                                                                                                                                                                                                   |

| 24      | EREG3_EN   | External Rail 2 enable drive. It is an open-drain output. The pull-up and pull-down resistors can be determined by REG_0x75[5] to be provided externally or internally. If 0x75[5] = 0b (resistors provided from internally), the output voltage, pull-up resistor, and pull-down resistor parameters are determined by REG_0x69[7:3]. |

| 25      | VIN4       | Rail4 input supply. It is internally connected to the source terminal of the Rail4 high-side MOSFET. Use wide PCB traces and multiple vias to make the connection. Apply at least two layers for the input trace. Connecting the ceramic capacitor (C = $10\mu$ F/0805) as close as possible from VIN4 pin to PGND45 pin is necessary. |

| 26      | SW4        | Switch node of the Rail4. It is internally connected to the drain terminal<br>of the high-side MOSFET and the drain terminal of the low-side<br>MOSFET. Connect this pin to output inductor and keep the sensitive<br>trace and signals away.                                                                                          |

| 27      | PGND45     | Ground return from low-side power MOSFET and driver of Rail4 and<br>Rail5. Directly soldering to a large PCB PGND plane and connecting<br>thermal vias under PGND45 pin are required to minimize the parasitic<br>impedance and thermal resistance.                                                                                    |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. www.richtek.com **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Pin No. | Pin Name    | Pin Function                                                                                                                                                                                                                                                                                                                                    |

|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28      | SW5         | Switch node of the Rail5. It is internally connected to the drain terminal of the high-side MOSFET and the drain terminal of the low-side MOSFET. Connect this pin to output inductor and keep the sensitive trace and signals away.                                                                                                            |

| 29      | VIN5        | Rail 5 input supply. It is internally connected to the source terminal of the Rail5 high-side MOSFET. Use wide PCB traces and multiple vias to make the connection. Apply at least two layers for the input trace. Connecting the ceramic capacitor (C = $10\mu$ F/0805) as close as possible from VIN pin to PGND45 pin is necessary.          |

| 30      | EREG2_EN    | External Rail 2 enable drive. It is an open-drain output. The pull-up and pull-down resistors can be determined by REG_0x75[6] to be provided externally or internally. If $0x75[6] = 0b$ (resistors provided from internally), the output voltage, pull-up resistor, and pull-down resistor parameters are determined by REG_0x68[7:3].        |

| 31      | EREG1_EN    | External Rail 1 enable drive. It is an open-drain output. The pull-up and pull-down resistors can be determined by REG_0x75[7] to be provided externally or internally. If $0x75[7] = 0b$ (resistors provided from internally), the output voltage, pull-up resistor, and pull-down resistor parameters are determined by REG_0x67[7:3].        |

| 32      | FB5         | Rail5 feedback sense for output regulation. It is also used to detect output voltage status for OVP, UVP and Power good of Rail5.                                                                                                                                                                                                               |

| 33      | INT_REG_OUT | Internal LDO output. Used as supply to internal control circuits. <b>DO NOT</b> connect to any external loads. Connect a high-quality capacitor (C = $10\mu$ F/0603) to ensure system stability.                                                                                                                                                |

| 34      | PGND        | Power dissipation pad. This pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                                                                                                                                                             |

| 35      | I2C_SDA     | I <sup>2</sup> C data pin. This pin is the input and output of serial bus data signal.                                                                                                                                                                                                                                                          |

| 36      | I2C_CLK     | I <sup>2</sup> C clock pin. This pin is the input of serial bus clock signal.                                                                                                                                                                                                                                                                   |

| 37      | RST_L       | Reset signal from PMIC. It is an open-drain output. The pull-up and pull-<br>down resistors can be determined by REG_0x65 [0] to be provided<br>externally or internally. If 0x65[0] = 0b (resistors provided from<br>internally), the output voltage, pull-up resistor, and pull-down resistor<br>parameters are determined by REG_0x65 [7:3]. |

| 38      | INLDO       | LDO input supply. Connecting the ceramic capacitor (C = $1\mu$ F/0402) as close as possible from INLDO pin to PGND pin is necessary.                                                                                                                                                                                                            |

| 39      | OUTLDO      | LDO output. To ensure stability of the LDO, it is recommended to Connecting the ceramic capacitor (C = $22\mu$ F/0402)                                                                                                                                                                                                                          |

| 40      | FB3         | Rail3 feedback sense for output regulation. It is also used to detect output voltage status for OVP, UVP and Power good of Rail3.                                                                                                                                                                                                               |

| 41      | PGND        | Power dissipation pad. This pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                                                                                                                                                             |

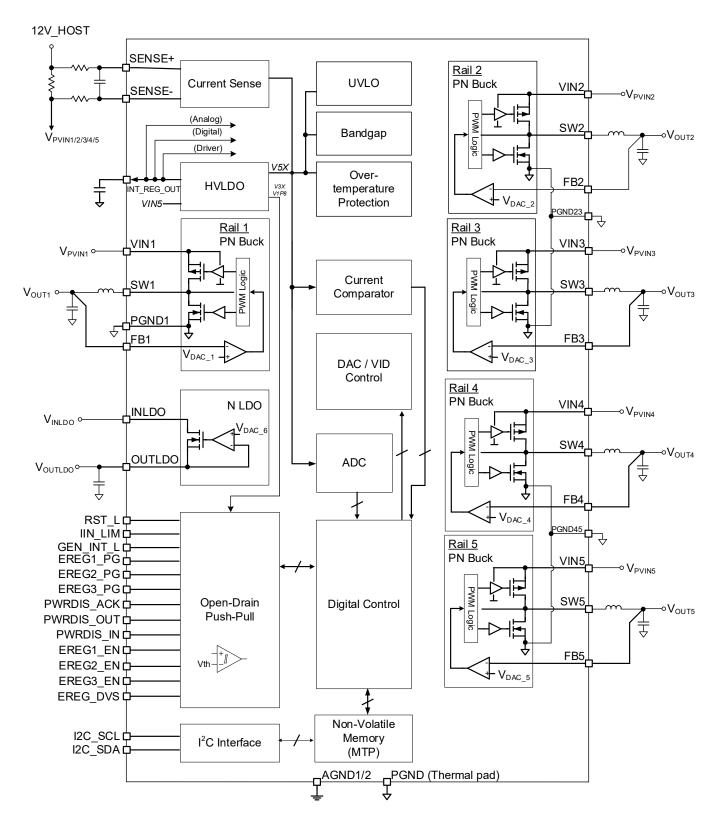

### **Functional Block Diagram**

### Operation

The RT5168 provides five high-efficiency synchronous buck regulators and one LDO for the power system of SSD.

### **Buck Converter**

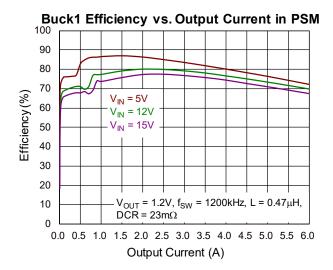

The RT5168 incorporates five high-efficiency COTbased mode synchronous buck converters integrated with high-side P-MOSFET and low-side N-MOSFET. It features low output voltage, quick transient response, and low quiescent current. These buck converters also possess all standard protections.

## Buck Undervoltage Protection (UVP), Overvoltage Protection (OVP)

The buck rail output voltages are continuous monitored for undervoltage and overvoltage protections.

If the output voltage falls below 80% or 85%(Typ.) of the reference voltage, UVP will be triggered, and both highside and low-side MOSFETs will be turned off and shut off the rail immediately. The UVP trigger level is defined by REG\_0x62.

While output voltage exceeds 115% or 120% (Typ.) of the reference voltage, it triggers OVP, both high-side and low-side MOSFETs turn off and shut off the rail immediately. The OVP trigger level is defined by REG\_0x61.

### **Buck Overcurrent Limiter (OCL)**

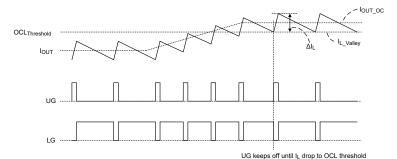

The current-limited architecture of all buck rails uses valley current detection. When low-side turns on, inductor current is sensed from RDS(ON) of low-side by the internal ZC/OC circuit. If the voltage on low-side RDS(ON) is over VOC (overcurrent voltage), OC circuit forces low-side at turn on status to reduce inductor current and the low-side will not turn off until the inductor current goes low to OC level. Once the inductor current is under OC level, the rail goes back to normal operation. If the controller continues to detect current limited sixteen times every internal clock, it shuts off the rail immediately. Please see the equations below to calculate the current limiting level defined as IOUT\_OC. Figure 1 illustrates cycle-by-cycle "valley" current-limiting control.

$$\Delta I_{L} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times L}$$

$$\mathsf{IOUT\_OC} = \mathsf{I}_{\mathsf{L\_Valley}} + \frac{\Delta \mathsf{I}_{\mathsf{L}}}{2} = \mathsf{I}_{\mathsf{L\_Valley}} + \frac{\mathsf{V}_{\mathsf{OUT}} \times \big(\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}}\big)}{\mathsf{V}_{\mathsf{IN}} \times \mathsf{f}_{\mathsf{SW}} \times \mathsf{L}}$$

Where,

$\Delta I_L$  = peak to peak inductor current.

$I_{OUT_OC}$  = average load current when current limitation occurs.  $I_{L_Valley}$  = the valley of inductor current when current limitation occurs as defined by REG\_0x5C,0x5D.

Figure 1. Cycle-by-Cycle "Valley" Current Limiting Control

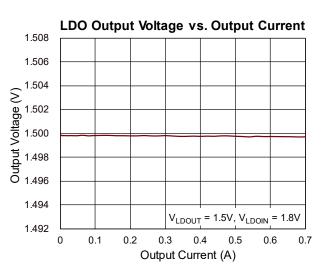

#### Linear Dropout Regulator (LDO)

The RT5168 includes one N-MOSFET type linear dropout regulator. The LDO contains independent current limit, overvoltage protection and undervoltage protection circuits to prevent unexpected situations.

When the load current is above the internal current-limit threshold, the current limit circuit adjusts the gate voltage of power stage to limit the output current; if the output load keeps draining current from LDO and the output voltage is lower than 80% or 85% (Typ.) of reference voltage, the UVP is triggered and shuts off LDO immediately.

If the LDO output terminal is abnormally charged and the voltage level is higher than 115% or 120% (Typ.) of the reference voltage, the OVP circuit is triggered and shuts off rails immediately.

#### **Over-Temperature Protection (OTP)**

If chip temperature is higher than 125°C, the OTP circuit will shut down all power rails. The PMIC will reboot with power- up sequence after chip temperature cools down and becomes lower than 105°C. The OTP trigger level is defined by REG\_0x42[7:6].

## External Regulator Enable and Power Good Monitoring

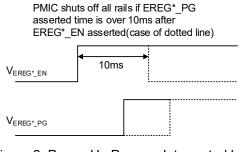

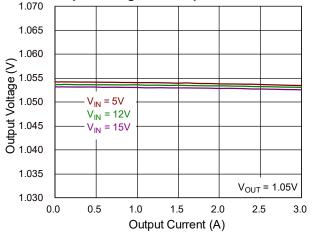

RT5168 supports 3 independent output signals (EREG1\_EN, EREG2\_EN, EREG3\_EN) for external regulator power-on sequence requirement, also with 3 input pins (EREG1\_PG, EREG2\_PG, EREG3\_PG) to monitor the coordinate regulator power status. The maximum waiting time between EREG\*\_EN and EREG\*\_PG is 10ms. If EREG\*\_EN is asserted and waits for over 10ms, and the EREG\*\_PG is still not asserted, the PMIC will stop the power-on process and shuts down as illustrated in Figure 2.

#### External Regulator DVS(EREG\_DVS)

EREG\_DVS as output pin can buffer out 1.8V/3.3V signal for external regulator's input requirement. Refer to REG\_0x6D for detailed setting descriptions.

#### **Power Disable Mode**

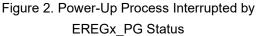

RT5168 supports power disable function for external input signal flag to shut down the PMIC immediately. It provides PWRDIS\_IN as input to accept the shutdown flag, and the PWRDIS\_OUT as a buffer output to follow the PWRDIS\_IN's flag and assert "High" when entering power disable mode.

Once the PWRDIS\_IN accepts the shutdown signal from SOC, the PMIC waits for the AUTO\_SHUTDOWN\_TIME time up and then shut down all rails immediately.

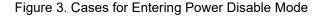

The PWRDIS\_ACK serves as an input to accept the acknowledge signal from SOC; if the ACK signal is asserted before AUTO\_SHUTDOWN\_TIME time up, the PMIC shuts down all rails immediately as illustrated in Figure 3.

# Power Indication (RST\_L) and Interrupt Indication (GEN\_INT\_L)

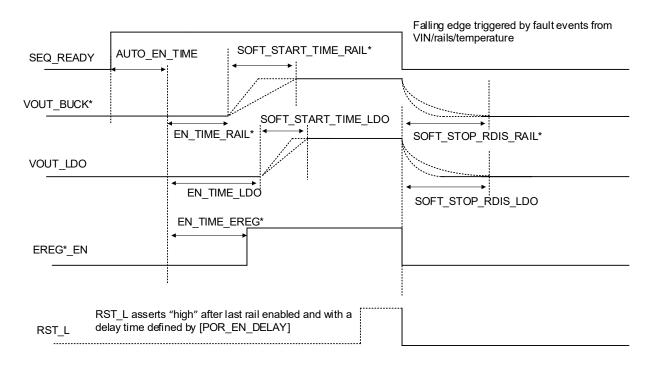

RST\_L is the indication output pin. When all regulator rails follow the settled sequence power-up successfully, the RST\_L asserts "high" after the last rail finishes the power-up procedure.

After power-up procedure completes, for any fault event (refer to REG\_0x72 for definition) that triggers protection mechanism, the PMIC shuts down

| Copyright © 2023 Richtek Technology Corporation. All rights reserved. | RICHTEK | is a registered trademark of Richtek Techno | logy Corporation |      |

|-----------------------------------------------------------------------|---------|---------------------------------------------|------------------|------|

| uuuu richtek eem                                                      |         | D05169.00                                   | Nevember         | 2021 |

immediately and RST\_L asserts "low".

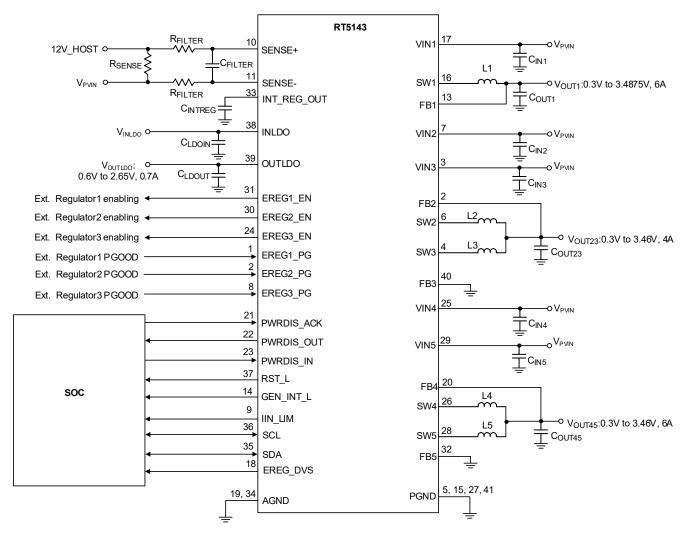

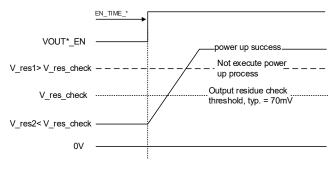

The delay time of RST\_L is defined by REG\_0x41[3:1]. The two cases are illustrated in Figure 4, where the external regulator power-good waiting time of 10ms is counted, and instead PMIC's regulator rail, it is used as the last regulator.

assertion, the external regulator requires start-up timing that is later than the PMIC's last regulator rail

Figure 4. Power-Up Process Completion and RST\_L Assertion

GEN\_INT\_L is output pin to indicate which interrupt event causes PMIC shutdown. It is flexible that the user can choose which event should be included by setting REG\_0x71. While interrupt event is detected and causes PMIC shutdown immediately, if this specific interrupt event is included by setting of REG\_0x71, GEN\_INT\_L asserts "low".

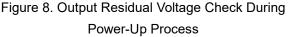

#### Input Current-Limit Indication (IIN\_LIM)

RT5168 integrates ADC function for input power monitoring purpose, the input current sensing voltage "VSENSE" which crosses on "SENSE+ " and "SENSE-" pins indicates the input current level.

The IIN\_LIM is used to alert the input overcurrent event. When VSENSE is over the defined input overcurrent range, IIN\_LIM asserts "high" and the PMIC keeps normal operation. If input current decreases to the level that VSENSE is lower than the overcurrent range, IIN\_LIM asserts "low". See **Input Power Monitoring** section for more detailed description of the pin application.

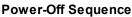

#### Protection Mode (Hiccup/Latch-Off)

The RT5168 supports two protection modes when fault events occur, it can be defined by the user with REG\_0x41[4].

For Hiccup Mode, when the protection function is triggered, the PMIC will shut down all rails for a period of time and then attempts to recover automatically. It retries a maximum of five times, and then latches the PMIC if the power-up procedure is not completed successfully. Hiccup mode allows the circuit to operate safely with low input current and power dissipation, and then resumes normal operation as soon as the overload or short circuit is removed.

For Latch-Off Mode, when the protection function is triggered, the PMIC shuts down all rails and goes into Latch-Off Mode. Only input re-power on over VIN UV rising threshold restarts the PMIC operation.

### Absolute Maximum Ratings (Note 1)

| • VINx, SENSE+, SENSE- to AGNDx                                                |

|--------------------------------------------------------------------------------|

| • SWx to PGNDx (DC)                                                            |

| • SWx to PGNDx (<100ns)                                                        |

| • PGNDx to AGNDx                                                               |

| <ul> <li>INT_REG_OUT, INLDO, OUTLDO to AGNDx</li></ul>                         |

| • FB_x to AGNDx                                                                |

| EREGx_EN, EREGx_PG, EREG_DVS to AGNDx                                          |

| <ul> <li>PWRDIS_IN, PWRDIS_OUT, PWRDIS_ACK to AGNDx</li></ul>                  |

| • IIN_LIM, RST_L, GEN_INT_L to AGNDx                                           |

| Junction Temperature                                                           |

| • Storage Temperature Range                                                    |

| <ul> <li>Lead Temperature 1.6mm (1/16 inch) from case for 10 seconds</li></ul> |

### ESD Ratings (Note 2)

| • | ESD Susceptibility                             |       |

|---|------------------------------------------------|-------|

|   | ESD rating, all pins Human Body Model (HBM)    | ±2kV  |

|   | ESD rating, all pins Charge Device Model (CDM) | ±500V |

### Recommended Operating Conditions (Note 3)

| ٠ | Supply Input Voltage       | 4V to 16V    |

|---|----------------------------|--------------|

| • | Ambient Temperature Range  | 0°C to 85°C  |

| • | Junction Temperature Range | 0°C to 125°C |

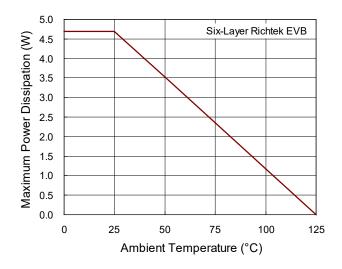

### Thermal Information (Note 4 and Note 5)

|          | Thermal Parameter                                       | UQFN-40L 5x5 (FC) | Unit |

|----------|---------------------------------------------------------|-------------------|------|

| θја      | Junction-to-ambient thermal resistance (JEDEC standard) | 25                | °C/W |

| θJC(Top) | Junction-to-case (top) thermal resistance               | 1                 | °C/W |

| θJA(EVB) | Junction-to-ambient thermal resistance (specific EVB)   | 21.3              | °C/W |

| ΨJC(Top) | Junction-to-top characterization parameter              | <1                | °C/W |

### **Electrical Characteristics**

(VIN1 = VIN2 = VIN3 = VIN4 = VIN5 = 12V,  $T_A$  = 25°C , unless otherwise specified)

| Parameter                           | Symbol          | Test Conditions                                                                                                  | Min  | Тур            | Мах  | Unit |

|-------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------|------|----------------|------|------|

| Input Power Supply                  | •               |                                                                                                                  |      |                |      |      |

| Supply Input Voltage                | VINx            | Input voltage range                                                                                              | 4    |                | 16   | V    |

| Cumply Input Cumpant                | IQ_VIN          | All VRs OFF, VIN > VINTREGOUT                                                                                    |      | 220            | 300  | μA   |

| Supply Input Current                | ISBY_VIN        | All VRs OFF, I <sup>2</sup> C active                                                                             |      | 1.4            | 1.8  | mA   |

| VIN Undervoltage                    | Vin_uv          | VIN_UV = 3.8V, Rising           Note: programmable range=         3.5           3.8V, 4.3V, 6V, 8V               |      | 3.8            | 4.1  | V    |

|                                     |                 | Falling                                                                                                          |      | Rising<br>–0.3 |      | V    |

| VIN Overvoltage                     | Vin ov          | VIN_OV =16V, Rising<br>Note: programmable range:<br>14V, 15V, 16V, 17V                                           | 15.5 | 16             | 16.5 | V    |

|                                     |                 | Hysteresis, Falling.                                                                                             |      | Rising<br>–0.5 |      | V    |

| Thermal Shutdown                    | Temp_ot         | Thermal Shutdown = 145°C, rising<br>threshold<br>Note: Rising, programmable range:<br>115°C, 125°C, 135°C, 145°C | 140  | 145            | 150  | °C   |

|                                     |                 | Hysteresis                                                                                                       |      | 20             |      |      |

| Current Sense                       |                 |                                                                                                                  |      |                |      |      |

| CS Accuracy                         | Vcs             | VSENSE+ - VSENSE- = 60mV                                                                                         | -2   |                | 2    | %    |

| Internal Regulator                  |                 |                                                                                                                  |      |                |      |      |

| INT_REG_OUT<br>Output Voltage       | VINTREGOUT      | VIN5 = 12V,<br>0 < IINTREGOUT < 150mA                                                                            | 4.5  | 5              | 5.5  | V    |

| INT_REG_OUT                         | VINTREGOUT_UV_R | Rising                                                                                                           | 3.2  | 3.5            | 3.8  | V    |

| UVLO                                | VINTREGOUT_UV_F | Falling                                                                                                          |      | 2.5            | 2.8  | V    |

| INT_REG_OUT<br>Output Current Limit | ILIM_INTREGOUT  | VIN5 = 12V, 0 < VINTREGOUT < 4V                                                                                  | 150  | 300            | 450  | mA   |

| Buck1 Converter (Ra                 | ail1)           |                                                                                                                  |      |                |      |      |

| Input Voltage Range                 | VIN_1           | Input voltage range                                                                                              | 4    | 12             | 16   | V    |

| Quiescent Current                   | lQ_1            | VFB1 > VID, no switching                                                                                         |      | 320            | 450  | μA   |

| Output Voltage<br>Range             | VOUT_1          | VFB1 setting range, 1.2V default                                                                                 | 0.3  |                | 3.46 | V    |

| VOUT AVS/DVS                        | VOUT_AVS1       | Output Voltage in AVS mode -15                                                                                   |      | 15             | %    |      |

| Regulation Voltage<br>Accuracy      | VFB_1           | Active Mode, output voltage<br>regulation. VOUT = 1.2V                                                           | -1   |                | 1    | %    |

| Parameter                          | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Test Co                                                                            | onditions            | Min  | Тур  | Max  | Unit  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------|------|------|------|-------|

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    | fSW = 0.6MHz         | 0.51 | 0.6  | 0.69 |       |

| Switching frequency                | for a second sec |                                                                                    | fSW = 0.8MHz         | 0.72 | 0.8  | 0.88 | MHz   |

|                                    | fsw_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PWM mode                                                                           | fSW = 1MHz           | 0.9  | 1    | 1.1  |       |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    | fSW = 1.2MHz         | 1.08 | 1.2  | 1.32 |       |

| Soft-Start Time                    | tss_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Soft-start time = 2<br>Note: Programma<br>0.5ms to 10ms                            |                      |      | 2    |      | ms    |

| Output Load<br>Transient           | ACLOAD_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $V_{IN} = 12V, V_{OUT1}$<br>L = 0.33µH, COUT<br>to 80% of IMAX in                  | 1 = 22µF x 7, 20%    | -4   |      | 4    | %     |

| High-Side Switch<br>On- Resistance | Rds(ON)_H_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | VIN1 - VSW1 = 0.1                                                                  | V                    |      | 60   | 110  | mΩ    |

| Low-Side Switch On-<br>Resistance  | RDS(ON)_L_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Vsw1 - Vpgnd1 =                                                                    | 0.1V                 |      | 12.5 | 20   | mΩ    |

| Selectable Bleed<br>Resistance     | RDIS_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Soft-stop discharg<br>Programmable rai<br>$10\Omega$ , $20\Omega$ , $50\Omega$ , H | nge:                 | 6    | 10   | 14   | Ω     |

| Bleed Monitor<br>Comparator        | VLOW_TH_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                    |                      |      | 0.07 | 0.1  | V     |

| Overvoltage<br>Protection          | Vov_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Vov_1 = 120%, Rising threshold<br>Note: Programmable range:<br>110%, 115%, 120%    |                      | 115  | 120  | 125  | %     |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Hysteresis                                                                         |                      |      | 2.5  |      |       |

| Undervoltage<br>Protection         | Vuv_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V∪v_1 = 85%, Fall<br>Programmable rai<br>90%, 85%, 80%                             |                      | 80   | 85   | 90   | %     |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Hysteresis                                                                         |                      |      | 2.5  |      |       |

| OV/UV Deglitch Time                | Tov/UV_DLY1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Programmable setting:<br>5μs (default), Disable deglitch (option)                  |                      |      | 5    |      | μs    |

|                                    | ILIM 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Valley current, 8A setting.                                                        |                      | 6.4  | 8    | 9.6  | A     |

| Overcurrent Limit                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Valley current, 9A setting.                                                        |                      | 7.2  | 9    | 10.8 |       |