# 3MHz 4A High Efficiency Step-Down Converter with I<sup>2</sup>C Interface

## **General Description**

The RT5701 is a Peak-Current Mode Pulse-Width-Modulated (PWM) step-down DC/DC converter with I<sup>2</sup>C control interface. Capable of delivering 4A continuing output current over a wide input voltage range from 2.5V to 5.5V, the RT5701 is ideally suited for Automotive Infotainment applications for low-voltage outputs to Micro controllers and ASICs in Navigation, Information Display, and Audio systems, Video systems and other battery operated systems requiring very low Shutdown current and Quiescent current consumption.

Internal synchronous rectifier with low  $R_{DS(ON)}$  dramatically reduces conduction loss at PWM mode. No external Schottky barrier diode is required in practical application. The RT5701 enters low-dropout mode when normal PWM cannot provide regulated output voltage by continuously turning on the upper P-MOSFET. The RT5701 enters shutdown mode and consumes less than  $5\mu A$  when the EN pin is pulled low. The switching ripple is easily smoothedout by small package filtering elements due to a fixed operation frequency of 3MHz. This along with small TSSOP-14 (Exposed Pad) package provides small PCB area applications.

The RT5701 also includes Dynamic Voltage Scaling (DVS) for system low power applications.

The I<sup>2</sup>C interface let the RT5701 controllable flexibly to select V<sub>OUT</sub> voltage level, peak current limit level, PWM

control mode, and so on. Other features include soft-start, auto discharge, lower internal reference voltage, over-temperature, and over-current protection.

## **Features**

- 2.5V to 5.5V Input Range

- Output Range from 0.3V to 5.5V

▶ Bank 0 : 0.3V to 0.7V

▶ Bank 1 : 0.6V to 1.4V

▶ Bank 2 : 1.2V to 2.8V

▶ Bank 3 : 2.4V to 5.5V

- ➤ The Default Value is 1.5V (VSEL = High) and 1V (VSEL = Low)

- 4A Continuing Output Current

- Support DVS in the Same Bank

- ▶ V<sub>OUT</sub> Adjusting Range (max, min) is Settable

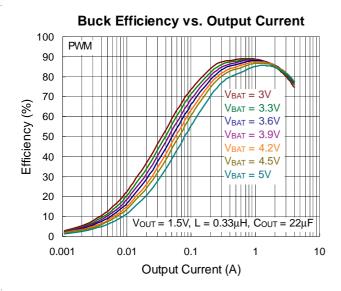

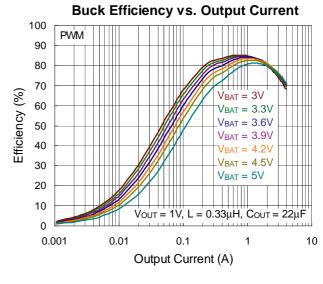

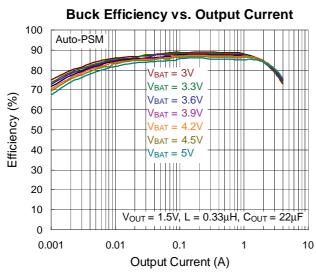

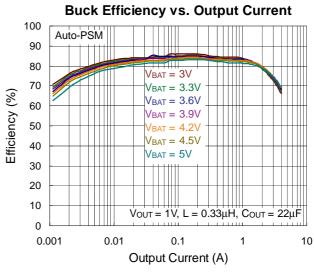

- High Efficiency

- ▶ 84% at 5V → 1.5V with 1.5A Load

- 3MHz Fixed-Frequency PWM Operation

- ▶ Auto-PSM/PWM or Force-PWM Selectable

- Support Remote Ground Sensing for Accurate Output Voltage

- Dedicated Hardware Pin to Immediately Switch Nominal Output Voltage Setting

- Output Discharging when Turning Off

- Over-Current Protection

- **▶ OC Level Settable**

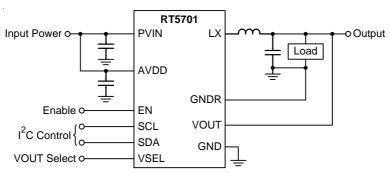

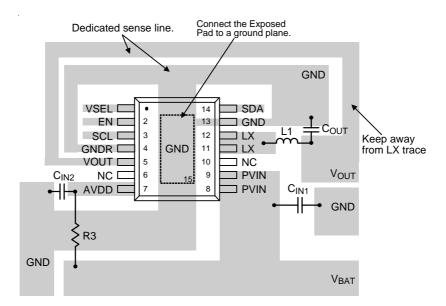

# **Simplified Application Circuit**

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

- Over-Temperature Protection

- Integrated Soft-Start Function

- Enabling Control by Enable Pin and I<sup>2</sup>C Register **Setting by Software**

- I<sup>2</sup>C Interface

- ▶ I<sup>2</sup>C Communication allowed Even in Off-State (EN = L)

- ▶ Support Fast Mode (400kbps)

- ▶ Registers Setting Retained in Off-State (EN = L)

- RoHS Compliant and Halogen Free

# **Applications**

- Automotive Infotainment Systems

- Microprocessor and DSP Core Supply

- Industrial-Grade Point-of-Load

- Cellular Telephones

- Personal Information Appliances

- · Wireless and DSL Modems

- MP3 Players

- Portable Instruments

# **Marking Information**

RT5701 **GCPYMDNN**  RT5701GCP: Product Number

YMDNN: Date Code

# **Ordering Information**

RT5701 🗖 📮 Package Type CP: TSSOP-14 (Exposed Pad) Lead Plating System G: Green (Halogen Free and Pb Free)

#### Note:

#### Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

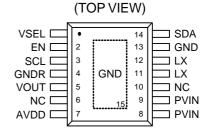

# **Pin Configurations**

TSSOP-14 (Exposed Pad)

www.richtek.com

# **Functional Pin Description**

| Pin No.                | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                      |

|------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

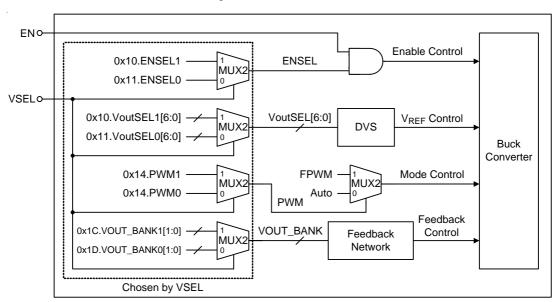

| 1                      | VSEL     | Nominal VOUT setting select input pin. VSEL = Low selects {0x11.ENSEL0, 0x11.VoutSEL0[6:0], 0x14.PWM0, 0x1D.VOUT_BANK0[1:0]}. VSEL = High selects {0x10.ENSEL1, 0x10.VoutSEL1[6:0], 0x14.PWM1, 0x1C.VOUT_BANK1[1:0]}. If 0x1C.VOUT_BANK1[1:0] $\neq$ 0x1D.VOUT_BANK0[1:0], do not toggle VSEL when EN = High.                                                                     |

| 2                      | EN       | Enable Control Input. The IC enable control pin turns on the step-down converter if the internal register ENSEL bit = 1. If ENSEL = 0, EN goes high still cannot enable step-down converter. The EN pin includes a internal pull-down current about $1\mu A.$ When IC protection occurs and is latched in shutdown state, toggling EN or re-power AVDD can reset the latch state. |

| 3                      | SCL      | I <sup>2</sup> C Interface Clock Input.                                                                                                                                                                                                                                                                                                                                           |

| 4                      | GNDR     | Remote Ground Sense Input.                                                                                                                                                                                                                                                                                                                                                        |

| 5                      | VOUT     | Step-Down Converter Output Voltage Sense Input.                                                                                                                                                                                                                                                                                                                                   |

| 6, 10                  | NC       | No Internal Connection.                                                                                                                                                                                                                                                                                                                                                           |

| 13,15<br>(Exposed Pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                                                                                                                                                                                                       |

| 7                      | AVDD     | Analog and I <sup>2</sup> C Interface Power Input.                                                                                                                                                                                                                                                                                                                                |

| 8, 9                   | PVIN     | Power Input. Input capacitor C <sub>IN</sub> must be placed as close to IC as possible.                                                                                                                                                                                                                                                                                           |

| 11,12                  | LX       | Switch Node.                                                                                                                                                                                                                                                                                                                                                                      |

| 14                     | SDA      | I <sup>2</sup> C Interface Data Input.                                                                                                                                                                                                                                                                                                                                            |

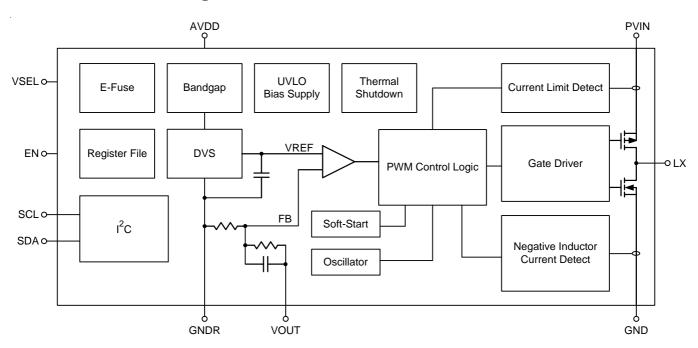

# **Functional Block Diagram**

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Operation**

The RT5701 is a low voltage synchronous step-down converter that can support the input voltage range from 2.5V to 5.5V and can deliver up to 4 A at an I<sup>2</sup>C selectable voltage ranging from 0.3 V to 5.5 V, distributed into 4 banks of output voltages. The converter can operate in Auto mode or forced PWM mode. Operating modes and output voltage can be selected via I2C.

By adapting current mode architecture, converter decides its switching duty by inductor current sense information. compensation ramp and error amplifier output. The converter turns on the high-side P-MOSFET whenever the raising edge of the switching clock. After the decided duty time, the high-side P-MOSFET would be turned off and the low-side N-MOSFET would be turned on until the next frequency clock raising in forced PWM mode or turn off by ZC (Zero Current Detection) in auto mode. The error amplifier may adjust its output, COMP, with selected voltage reference and output feed-back voltage information. Different selection of voltage reference and different loading at output node regulate the required COMP voltage, which regulating the output voltage.

#### **VSEL Function for Immediately Voltage Change**

To address different performance operating points and startup conditions, the device offers two output voltage / mode presets, which can be chosen via a dedicated VSEL pin; this allows simple and zero latency output voltage transition.

#### **Operating Mode Selection**

The converter can operate in Auto mode or forced PWM mode. It can be selected by programming register 0x14.PWM0 for VSEL = Low or 0x14.PWM1 for VSEL = High. If Auto mode is selected, the converter automatically switches the operation mode between PWM and PSM according to the load conditions. If forced PWM mode is selected, the converter works only in PWM mode.

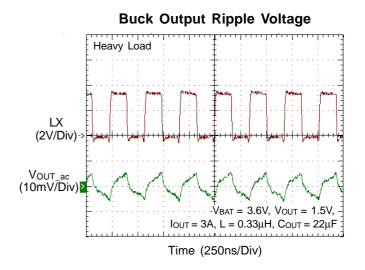

#### **PWM (Pulse Width Modulation) Operating Mode**

The converter operates in PWM (Pulse Width Modulation) mode from medium to heavy load. In PWM mode, the converter operates with its nominal switching frequency of 3MHz, and adapts its duty cycle to regulate the desired output voltage. In this mode, the inductor current is in CCM (Continuous Current Mode) and the voltage is regulated by PWM.

#### Forced PWM (FPWM) Operating Mode

If forced PWM mode is selected, the converter works only in PWM mode, and disables the transition from PWM to PSM as the load decreases. The advantage of forced PWM is that the switching frequency is fixed to be 3MHz, and thus it is easy for EMI immunity design. The disadvantage is that the efficiency at light load is poor due to the negative inductor current.

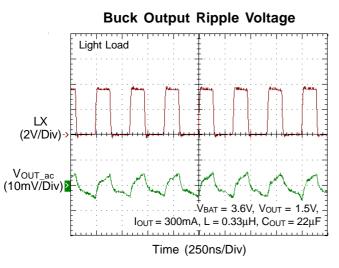

#### Pulse Skipping Modulation (PSM) Operating Mode

When in Forced PWM operating mode without output current loading, half of FPWM inductor current is negative to balance total average zero output current. If that negative inductor current could be saved, the efficiency will be improved strongly. PSM is one Buck operation mode with zero inductor current detection. Whenever zero current occur, the low-side N-MOSFET is turned off immediately and save the resident power into output capacitor (store energy in higher V<sub>OUT</sub>). Then, the converter skips internal synchronous clock and keeps sleep-state until output voltage is discharged to below its target value. Once skips occurs, the power MOSFETs of converter is turned off and lots of sub-block circuits is in sleep state to save quiescent consumption. If the output loading is increasing, the discharge time is shortened, i.e. the switching frequency depends on the output loading. The switch frequency is decayed from 3MHz; the lighter output loading, the lower switch frequency. As result, PSM V<sub>OUT</sub> ripple would be slightly larger than FPWM but PSM gains significant efficiency improvement.

#### **Auto-Zero Current Detector**

The Auto-Zero Current (AZC) detector circuit senses the LX waveform to adjust the inductor zero current threshold voltage automatically. In traditional trimmed zero current detectors, the zero current threshold changes due to V<sub>IN</sub> / V<sub>OUT</sub> variation. This would degrade efficiency due to

www.richtek.com

the extra power consumption by body diode or negative inductor current. Regard with this defect, AZC adjusts current threshold continuously when the RT5701 is operating. With AZC circuit, the RT5701 could avoid negative current in PSM mode and could achieve higher efficiency performance.

#### **Minimum Peak Current**

Minimum peak current is an evolution version from minimum on time. Rather than fixed minimum on time, Minimum peak current produce the "effective minimum on time" which could be adjusted according to  $V_{\text{IN}}/V_{\text{OUT}}$  condition.

$$T_{ON} = \frac{L}{V_{IN} - V_{OUT}} \times I_{MIN\_Peak}$$

It's an advantage to not provide too much energy at low duty; also, to not provide too less energy at high duty. When the converter is in PSM operation, every time pulse skip duration finishes, the converter will provide current energy for output loading by turning on P-MOSFET until inductor current achieve minimum peak current.

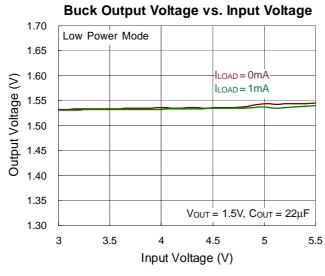

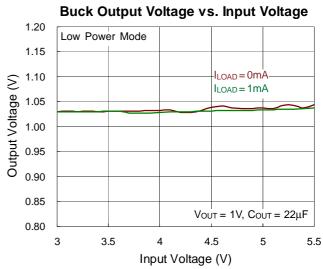

#### Low Power Mode (LPM)

The RT5701 provides Low Power Mode (LPM) to save more quiescent consumption. With maximum output current ability, 1mA, LPM enhances the efficiency at load below 100 $\mu$ A, more than the Pulse Skipping Mode (PSM) does. This extremely efficiency improvement may extend battery life, especially in stand-by mode of hand held products.

#### **Enabling**

The converter can be enabled or disabled by IC pin, EN. For more flexibility, users can turn on/off the converter by  $I^2C$  programming. There are ENSEL register bit located in register 0x10.ENSEL1 and 0x11.ENSEL0 to control internal enable signal for both VSEL selection high/low.

#### **Dynamic Voltage Scaling (DVS)**

Users can select required output voltage bank and preferred output voltage by I<sup>2</sup>C programming. When output voltage is changed, the RT5701 provides Dynamic Voltage Scaling (DVS) skill to prevent any undershoot or overshoot when output voltage transition. The DVS means to adjust one

reference voltage into another reference voltage in steps smoothly. The slew rate of the internal reference voltage is around 3mV / 10 $\mu$ s. Please note DVS function could only be available in the same output voltage bank.

#### **Remote Ground Sensing**

The RT5701 can deliver output current up to 4A. Inevitably, there is voltage drops due to the routing trace resistance between output node and chip location, especially when heavy loading. Also, voltage drops exist in ground trace. Remote ground sensing pin, GNDR, can tell the converter the lost drops to compensate to the correct and accuracy voltage level.

#### **Active Output Discharge**

To make sure that no residual voltage remains in the power supply rail, an active discharge path can ground the output voltage. The output gets discharged by the LX pin with a typical discharge resistor when the device shuts down. This feature can be easily disabled or enabled with register 0x12.Discharge. By default the discharge path is active. The default value of the feature is factory programmable.

#### **Power Good**

When the output voltage is higher than Power Good rising threshold, the Power Good flag, register 0x01.SEN\_PG is high.

#### **Under-Voltage Lockout (UVLO)**

The UVLO continuously monitors the PVIN voltage to make sure the device works properly. When the PVIN is high enough to reach the UVLO high raising threshold voltage, 2.4V, the converter softly starts. When the PVIN decreases to its UVLO low threshold voltage, 2.3V, the device will shut down. The event is recorded in register 0x18.PVIN\_UVLO. The record can be reset with I<sup>2</sup>C interface or automatically reset by re-power-on AVDD.

#### **Output Under-Voltage Protection (UVP)**

When the output voltage is lower than UVP threshold (~50% of nominal target) after soft-start, the UVP is triggered. The converter will be latched and the output voltage will no longer be regulated during UVP latched state. Re-power-on input voltage or EN pin can unlatch

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

the protection state. Using I<sup>2</sup>C to shutdown the system and then re-enable it will also unlatch UVP function. The event is recorded in register 0x18.SCP. The record can be reset with I2C interface or automatically reset by repower-on AVDD.

#### **Over-Current Protection (OCP)**

The converter senses the current signal when the highside P-MOSFET turns on. As a result, The OCP is cycleby-cycle current limitation. If the OCP occurs, the converter holds off the next on pulse until inductor current drops below the OCP limit. The event is recorded in register 0x18.OCP. The record can be reset with I<sup>2</sup>C interface or automatically reset by re-power-on AVDD. The OCP level can be set with 0x16.IPEAK[1:0].

#### **Over-Temperature Protection (OTP)**

The converter has an over-temperature protection. When the junction temperature is higher than the thermal shutdown rising threshold, the system will be latched and the output voltage will no longer be regulated until the junction temperature drops under the falling threshold.

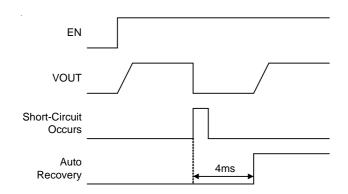

#### **Output Under-Voltage Protection (UVP)**

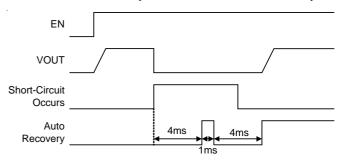

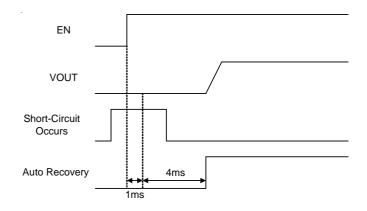

For short-circuit time < 4ms, the IC will automatically recovers in 4ms after the short-circuit occurs.

For short-circuit time > 5ms, the RT5701 will try to recover in 4ms after the short-circuit occurs. If it still fails to recover in 1ms later, it will try to recover in another 4ms cycle.

If short-circuit occurs before enable, and the IC fails to turn on in 1ms, it will recover in 4ms later.

# **Absolute Maximum Ratings** (Note 1)

| Supply Input Voltage, PVIN and AVDD                                         |               |

|-----------------------------------------------------------------------------|---------------|

| Switch Node DC Rating, LX                                                   | 6V            |

| • EN, VOUT, SCL, SDA Voltage                                                | 0.3V to 6V    |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |               |

| TSSOP-14 (Exposed Pad)                                                      | 3.32W         |

| Package Thermal Resistance (Note 2)                                         |               |

| TSSOP-14 (Exposed Pad), $\theta_{JA}$                                       | 30.1°C/W      |

| TSSOP-14 (Exposed Pad), $\theta_{JC}$                                       | 7.5°C/W       |

| • Junction Temperature                                                      |               |

| • Lead Temperature (Soldering, 10 sec.)                                     |               |

| Storage Temperature Range                                                   | 65°C to 150°C |

| ESD Susceptibility (Note 3)                                                 |               |

| HBM (Human Body Model)                                                      |               |

| MM (Machine Model)                                                          | 200V          |

| Recommended Operating Conditions (Note 4)                                   |               |

| Supply Input Voltage, AVDD and PVIN                                         |               |

| • Junction Temperature Range                                                |               |

| Ambient Temperature Range                                                   | 40°C to 105°C |

## **Electrical Characteristics**

$(V_{IN}=3.6V,\ V_{OUT}=2.5V,\ L=0.33\mu H,\ C_{IN}=10\mu F,\ C_{OUT}=22\mu F,\ T_A=-40^{\circ}C$  to  $105^{\circ}C$ , unless otherwise specification)

• Input Capacitance ------ 10μF

| Parameter                                             | Symbol                | Test Conditions                                                | Min       | Тур | Max | Unit |

|-------------------------------------------------------|-----------------------|----------------------------------------------------------------|-----------|-----|-----|------|

| Input Voltage Start-up                                | V <sub>IN</sub>       | AVDD and PVIN                                                  | 2.45      |     | 5.5 | V    |

| Input Voltage Range                                   | V <sub>IN</sub>       | I <sub>OUT</sub> = 2A                                          | 2.5       | 1   | 5.5 | V    |

| GNDR Current                                          | I <sub>GNDR</sub>     | I <sub>OUT</sub> = 0mA, No Switching                           | 1         | 1   | 10  | μΑ   |

| Shutdown Current                                      | ISHDN                 | EN = GND                                                       | 1         | 1   | 5   | μΑ   |

| Adjustable Output Range for Internal Feedback Network | V <sub>OUT</sub>      | SDA = SCL = High at AVDD Power On, 0x1D.VOUT_BANK[1:0] = 2'b10 | 1.2       |     | 2.8 | V    |

| Output Voltage Accuracy in Normal Mode                | V <sub>OUT</sub>      | V <sub>IN</sub> = 2.5V to 5.5V, 0A < I <sub>OUT</sub> < 2.7A   | -2        |     | 2   | %    |

| Output Voltage Accuracy in Low Power Mode             | V <sub>OUT</sub>      | V <sub>IN</sub> = 2.5V to 5.5V, 0A < I <sub>OUT</sub> < 1mA    | <b>-5</b> | 1   | 5   | %    |

| P-Channel On-Resistance                               | R <sub>DS(ON)</sub> P | I <sub>OUT</sub> = 200mA                                       | 1         | 40  | 1   | mΩ   |

| N-Channel On-Resistance                               | R <sub>DS(ON)_N</sub> | I <sub>OUT</sub> = 200mA                                       |           | 20  |     | mΩ   |

Copyright © 2015 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Param                                        | eter        | Symbol             | Test Conditions                                                  | Min  | Тур  | Max  | Unit |

|----------------------------------------------|-------------|--------------------|------------------------------------------------------------------|------|------|------|------|

| P-Channel Curr                               | rent Limit  | I <sub>LIM_P</sub> | 0x16.IPEAK[1:0] = 2'b11                                          | 5.2  | 6.2  | 7.2  | Α    |

| Under-Voltage Lockout<br>Threshold (Falling) |             | UVLO_F             | PVIN Falling                                                     | 2.15 | 2.3  | 2.45 | V    |

| UVLO Hysteres                                | sis gap     | UVLO_Hys           |                                                                  |      | 0.1  |      | V    |

| Oscillator Frequ                             | uency       | fosc               |                                                                  | 2.7  | 3    | 3.3  | MHz  |

| Maximum Duty                                 | Cycle       |                    |                                                                  | 100  |      |      | %    |

| Start-Up Time                                |             | tsT                | V <sub>OUT</sub> = 1V, From EN going high to 90% of nominal VOUT |      | 420  |      | μS   |

| VOUT Power Good<br>Threshold (Rising)        |             |                    | Nominal VOUT Ratio                                               |      | 90   |      | %    |

| Power Conversion                             |             |                    | 5V to 1.5V and Load = 1.5A                                       |      | 84   |      | %    |

| Efficiency                                   |             |                    | 5V to 1V and Load = 1.5A                                         |      | 78   |      |      |

| Line Regulation                              |             |                    |                                                                  |      | 0.25 |      | %/V  |

| Load Regulation                              | n           |                    |                                                                  |      | 0.25 |      | %/A  |

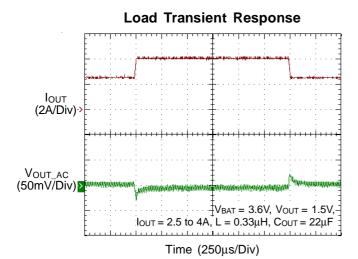

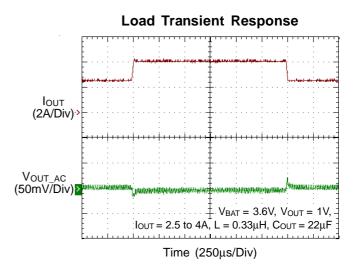

| Load Transient                               | Drop        |                    | 5V to 2.5V and Load Current step<br>1.5A in 10μs Rising Time     |      | 50   |      | mV   |

| Output Dischar                               | ge Resistor | Rod                | EN = GND                                                         |      | 40   |      | Ω    |

| Thermal Shutdo<br>Threshold                  | own         | T <sub>SD</sub>    |                                                                  | 130  | 150  |      | °C   |

| Thermal Shutdown<br>Hysteresis               |             | $\Delta T_{SD}$    |                                                                  |      | 20   |      | °C   |

| EN, VSEL Pull Low Current                    |             |                    |                                                                  |      | 1    |      | μΑ   |

| EN, VSEL                                     | Logic-High  |                    |                                                                  | 1.05 |      |      | V    |

| - · · · · · · · · · · · · · · · · · · ·      | Logic-Low   |                    |                                                                  |      |      | 0.4  | V    |

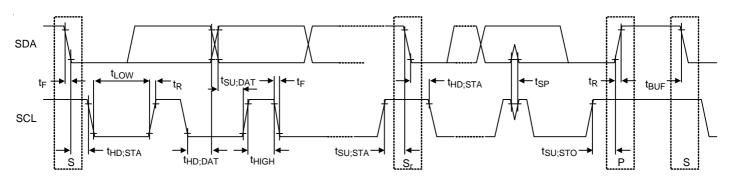

## I<sup>2</sup>C for Fast Mode

(AVDD = 3.6V,  $T_A = -40^{\circ}C$  to  $105^{\circ}C$ , unless otherwise specification)

| Param                                                                                                | eter       | Symbol              | Test Conditions | Min  | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------------|------------|---------------------|-----------------|------|-----|-----|------|

| SDA, SCL Input                                                                                       | High-Level |                     |                 | 1.05 |     |     | V    |

| Voltage                                                                                              | Low-Level  |                     |                 |      |     | 0.4 | V    |

| Fast Mode                                                                                            |            |                     |                 |      |     |     |      |

| SCL Clock Rate                                                                                       |            | f <sub>SCL</sub>    |                 |      |     | 400 | kHz  |

| Hold Time (Repeated) START<br>Condition.<br>After this Period, the First Clock<br>Pulse is Generated |            | t <sub>HD;STA</sub> |                 | 0.6  |     |     | μS   |

| LOW Period of the SCL Clock                                                                          |            | t <sub>LOW</sub>    |                 | 1.3  |     |     | μS   |

| HIGH Period of the SCL Clock                                                                         |            | tHIGH               |                 | 0.6  |     |     | μS   |

| Parameter                                        | Symbol              | Test Conditions           | Min | Тур | Max | Unit |

|--------------------------------------------------|---------------------|---------------------------|-----|-----|-----|------|

| Set-Up Time for a Repeated START Condition       | tsu;sta             |                           | 0.6 |     |     | μS   |

| Data Hold Time                                   | t <sub>HD;DAT</sub> |                           | 0   |     | 0.9 | μS   |

| Data Set-Up Time                                 | t <sub>SU;DAT</sub> |                           | 100 |     | -   | ns   |

| Set-Up Time for STOP<br>Condition                | tsu;sto             |                           | 0.6 |     | 1   | μS   |

| Bus Free Time between a STOP and START Condition | t <sub>BUF</sub>    |                           | 1.3 |     | -   | μS   |

| Rising Time of both SDA and SCL Signals          | t <sub>r</sub>      |                           | 20  |     | 300 | ns   |

| Falling Time of both SDA and SCL Signals         | t <sub>f</sub>      |                           | 20  |     | 300 | ns   |

| SDA and SCL Output Low Sink Current              | I <sub>OL</sub>     | SDA or SCL Voltage = 0.4V | 2   |     |     | mA   |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

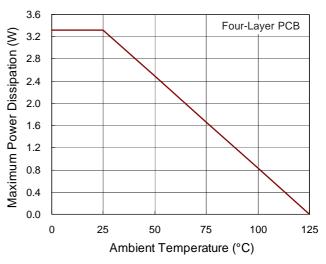

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

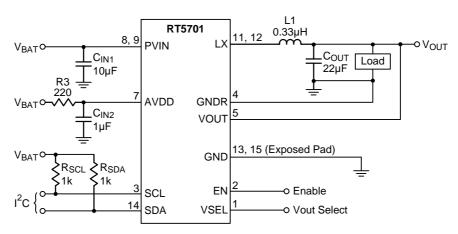

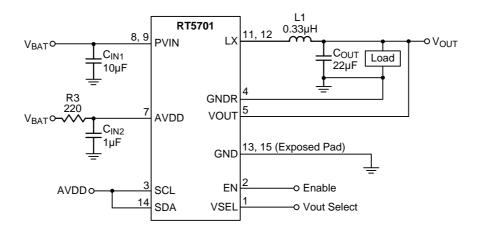

# **Typical Application Circuit**

Figure 1. Typical Application Circuit for I<sup>2</sup>C Control

Figure 2. Typical Application Circuit for Internal Resistor Control without I<sup>2</sup>C

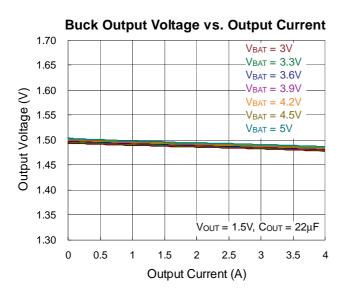

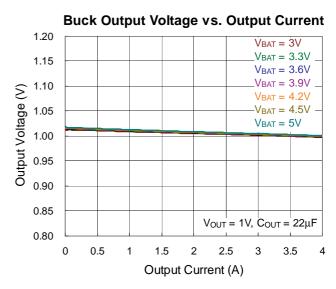

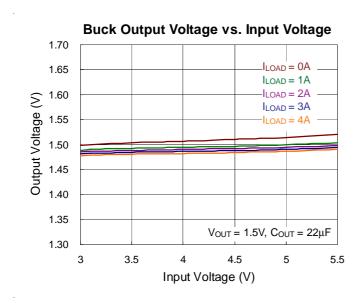

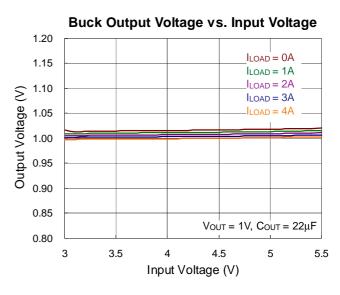

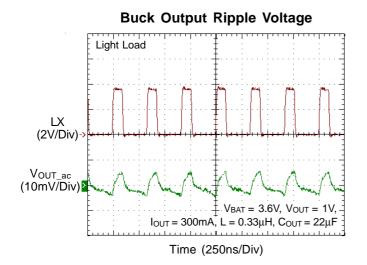

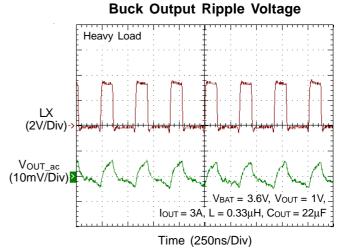

# **Typical Operating Characteristics**

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# Application Information

The basic RT5701 application circuit is shown in Typical Application Circuit. External component selection is determined by the maximum load current and begins with the selection of the inductor value and operating frequency followed by C<sub>IN</sub> and C<sub>OUT</sub>.

#### **Inductor Selection**

The inductor value and operating frequency determine the current ripple according to a specific input and output voltage. The ripple current,  $\Delta I_L$ , increases with higher  $V_{IN}$ and decreases with higher inductance, as shown in equation below:

$$\Delta I_{L} = \frac{1}{f} \times \frac{V_{OUT}}{V_{IN}} \times \frac{V_{IN} - V_{OUT}}{L}$$

where f is the switch frequency and L is the inductance.

Having a lower ripple current reduces not only the ESR losses in the output capacitors, but also the output voltage ripple. Higher operating frequency combined with smaller ripple current is necessary to achieve high efficiency. The largest ripple current occurs at the highest V<sub>IN</sub>. To guarantee that the ripple current stays below the specified  $\Delta I_{L(MAX)}$ , the inductor value should be chosen according to the following equation:

$$L = \frac{1}{f} \times \frac{V_{OUT}}{V_{IN(MAX)}} \times \frac{V_{IN(MAX)} - V_{OUT}}{\Delta I_{L(MAX)}}$$

The inductor's current rating (defined by a temperature rise from 25°C ambient to 40°C) should be greater than the maximum load current and its saturation current should be greater than the short-circuit peak current limit. Refer to Table 1 for the suggested inductor selection.

Table 1. Suggested Inductors for Typical Application Circuit

| Inductor Value | Component Supplier / Part Number | Dimensions<br>(LxWxH mm) | I <sub>SAT</sub> (L-30%) / DCR       |

|----------------|----------------------------------|--------------------------|--------------------------------------|

| 0.33μΗ         | Coilcraft / XFL4015-331          | 4.0x4.0x1.5              | 7A / 6.8mΩ                           |

| 0.47μΗ         | Coilcraft / XFL4015-471          | 4.0x4.0x1.5              | 5.4A / 7.6mΩ                         |

| 0.47μΗ         | SUMIDA / CDMCDS-R47MC            | 2.5x2.0x1.2              | 4.8A / 15.0 mΩ                       |

| 0.47μΗ         | TDK / TFM252010G                 | 2.5x2.0x1.0              | $4.5\text{A}$ / $24.0\text{m}\Omega$ |

#### Input and Output Capacitor Selection

An input capacitor, CIN, is needed to filter out the trapezoidal current at the source of the high-side MOSFET. To prevent large ripple current, a low ESR input capacitor sized for the maximum RMS current should be used. The RMS current is given by:

$$I_{RMS} = I_{OUT(MAX)} \times \frac{V_{OUT}}{V_{IN}} \times \sqrt{\frac{V_{IN}}{V_{OUT}}} - 1$$

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT(MAX)} / 2$ . This simple worst-case condition is commonly used for design. Choose a capacitor rated at a higher temperature than required. Several capacitors may also be paralleled to meet the size or height requirements of the design. Ceramic capacitors have high ripple current, high voltage rating and low ESR, which makes them ideal for switching regulator applications. However, they can also have a high voltage coefficient and audible piezoelectric effects. The high Q of ceramic capacitors with trace inductance can lead to significant ringing. When a ceramic capacitor is used at the input and the power is supplied by a wall adapter through long wires, a load step at the output can induce ringing at the input, VIN. At best, this ringing can couple to the output and be mistaken as loop instability. At worst, a sudden inrush of current through the long wires can potentially cause a voltage spike at V<sub>IN</sub> large enough to damage the part. Thus, care must be taken to select a suitable input capacitor.

The selection of Cout is determined by the required ESR to minimize output voltage ripple. Moreover, the amount of bulk capacitance is also a key for C<sub>OUT</sub> selection to ensure that the control loop is stable. Loop stability can be checked by viewing the load transient response. The output voltage ripple, V<sub>OUT</sub>, is determined by :

$$\Delta V_{OUT} \le \Delta I_{L} \left[ ESR + \frac{1}{8 \times f_{OSC} \times C_{OUT}} \right]$$

where  $f_{\text{OSC}}$  is the switching frequency and  $I_{\text{L}}$  is the inductor ripple current.

The output voltage ripple will be the highest at the maximum input voltage since  $I_L$  increases with input voltage. Multiple capacitors placed in parallel may be needed to meet the ESR and RMS current handling requirement. Ceramic capacitors have excellent low ESR characteristics, but can have a high voltage coefficient and audible piezoelectric effects. The high Q of ceramic capacitors with trace inductance can also lead to significant

ringing. Nevertheless, high value, low cost ceramic capacitors are now becoming available in smaller case sizes. Their high ripple current, high voltage rating and low ESR make them ideal for switching regulator applications.

#### **VSEL Function Selection**

Figure 3 shows the detailed logic of VSEL function. There are several parameters can be set its initial condition, such as output voltage, operation mode (Auto PSM/PWM or Forced-PWM) and output voltage bank. Users can set separately into VSEL high state and VSEL low state to design the required performance.

Figure 3. VSEL Logic

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

### Setting the Output Voltage with Internal Feedback Network

Besides defined initial output voltages in VSEL high and VSEL low, the RT5701 can manually change voltage reference from 0.3V to 0.7V by I<sup>2</sup>C programming. The difference among bank0 to bank3 is internal feedback configuration. Then the output voltage can be designed as following equation:

$V_{OUT} = V_{REF} \times 2^{(BANK)}$

where V<sub>REF</sub> stand for reference voltage; BANK is 0 to 3, for bank0 to bank3 separately.

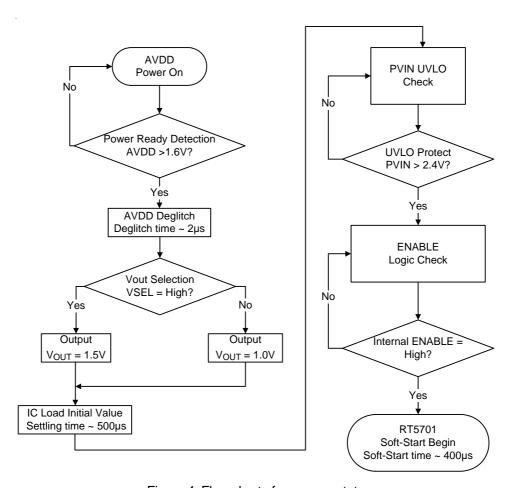

#### The Flow Chart from Power-ON to Soft-Start

To summarize the above functions and judgments such as VSEL function, internal feedback network selection at power-on state, following chart shows the actions and protections to clarify the time sequence and priority.

Figure 4. Flow chart of power-on state

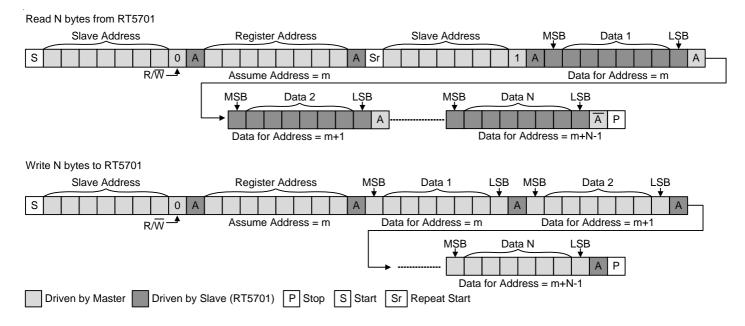

#### I<sup>2</sup>C Interface

The RT5701 default  $I^2C$  slave address = 7'b0011100.  $I^2C$  interface support fast mode (bit rate up to 400kb/s). The write or read bit stream (N  $\geq$  1) is shown below :

Figure 5. Definition of Timing for Hs-mode Devices on the I<sup>2</sup>C-bus

# I<sup>2</sup>C Register Map

| Register<br>Address | Register<br>Address | b[7]<br>(MSB)                                             | b[6]                                       | b[5]        | b[4]     | b[3]     | b[2]     | b[1]     | b[0]<br>(LSB) |  |

|---------------------|---------------------|-----------------------------------------------------------|--------------------------------------------|-------------|----------|----------|----------|----------|---------------|--|

| 0x01                | Meaning             | SEN_TSD                                                   | Reserved                                   | Reserved    | Reserved | Reserved | Reserved | Reserved | SEN_PG        |  |

|                     | Default             | 0                                                         | Х                                          | Х           | Х        | Х        | Х        | х        | 0             |  |

|                     | Read/Write          | R                                                         |                                            |             |          |          |          |          | R             |  |

|                     |                     | Report junction temperature > thermal shutdown threshold. |                                            |             |          |          |          |          |               |  |

| SEN                 | N_TSD               | 0 : T <sub>J</sub> < 150°C                                |                                            |             |          |          |          |          |               |  |

|                     |                     | 1 : T <sub>J</sub> > 150°C                                |                                            |             |          |          |          |          |               |  |

|                     |                     |                                                           | Report V <sub>OUT</sub> Power GOOD or not. |             |          |          |          |          |               |  |

| SEN_PG              |                     | 0 : V <sub>OUT</sub> < 90% of target.                     |                                            |             |          |          |          |          |               |  |

|                     |                     | 1: Vout is                                                | within nom                                 | inal range. |          |          |          |          |               |  |

| Register<br>Address                                                                                                                                         | Register<br>Address | b[7]<br>(MSB)                                                                                                                                                                                                                                                                                   | b[6] | b[5] | b[4] | b[3]       | b[2]    | b[1] | b[0]<br>(LSB) |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------------|---------|------|---------------|--|--|

|                                                                                                                                                             | Meaning             | ENSEL1                                                                                                                                                                                                                                                                                          |      | •    | V    | outSEL1[6: | 0]      | •    |               |  |  |

| 0x10                                                                                                                                                        | Default             | 1                                                                                                                                                                                                                                                                                               | 0    | 0    | 1    | 0          | 1       | 1    | 1             |  |  |

|                                                                                                                                                             | Read/Write          | RW                                                                                                                                                                                                                                                                                              | R/W  | R/W  | R/W  | R/W        | R/W     | R/W  | RW            |  |  |

| ENSEL1                                                                                                                                                      |                     | When VSEL = High, it is used to gate the EN pin of the step-down converter. This makes the step-down converter can enable/disable by I <sup>2</sup> C and Software.  When EN pin = High and this bit = 1, step-down converter can be enabled. Otherwise, step-down converter would be disabled. |      |      |      |            |         |      |               |  |  |

|                                                                                                                                                             |                     | 0 : Disable (even if EN=High, step-down converter still cannot be enabled.)                                                                                                                                                                                                                     |      |      |      |            |         |      |               |  |  |

|                                                                                                                                                             |                     | 1 : Enable                                                                                                                                                                                                                                                                                      |      |      |      |            |         |      |               |  |  |

| When VSEL = High, it is used to set Vout voltage level.  VoutSEL1[6:0] Vout voltage level = (303.125mV + 3.125mV x VoutSEL1[6:0]) x 2 ^ (0x1C.VOUT_B [1:0]) |                     |                                                                                                                                                                                                                                                                                                 |      |      |      |            | T_BANK1 |      |               |  |  |

| Register<br>Address                                                                                                                                      | Register<br>Address | b[7]<br>(MSB)                                                                                                                                                                                                                                                                                                                                                              | b[6] | b[5] | b[4] | b[3]       | b[2] | b[1] | b[0]<br>(LSB) |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------------|------|------|---------------|--|--|

|                                                                                                                                                          | Meaning             | ENSEL0                                                                                                                                                                                                                                                                                                                                                                     |      |      | V    | outSEL0[6: | 0]   |      |               |  |  |

| 0x11                                                                                                                                                     | Default             | 1                                                                                                                                                                                                                                                                                                                                                                          | 0    | 1    | 1    | 1          | 1    | 1    | 1             |  |  |

|                                                                                                                                                          | Read/Write          | RW                                                                                                                                                                                                                                                                                                                                                                         | R/W  | R/W  | R/W  | R/W        | R/W  | R/W  | RW            |  |  |

| EN                                                                                                                                                       | SEL0                | When VSEL = Low, it is used to gate the EN pin of the step-down converter. This makes the step-down converter can enable/disable by I <sup>2</sup> C and Software.  When EN pin = High and this bit = 1, step-down converter can be enabled. Otherwise, step-down converter would be disabled.  0: Disable (even if EN=High, step-down converter still cannot be enabled.) |      |      |      |            |      |      |               |  |  |

|                                                                                                                                                          |                     | 1 : Enable                                                                                                                                                                                                                                                                                                                                                                 |      |      |      |            |      |      |               |  |  |

| When VSEL = Low, it is used to set Vout voltage level.  VoutSEL0[6:0] Vout voltage level = (303.125mV + 3.125mV x VoutSEL0[6:0]) x 2 ^ (0x1D.VOUT [1:0]) |                     |                                                                                                                                                                                                                                                                                                                                                                            |      |      |      | Γ_BANK0    |      |      |               |  |  |

| Register<br>Address | Register<br>Address | b[7]<br>(MSB)                                                                         | b[6]          | b[5]       | b[4]        | b[3]           | b[2]         | b[1]          | b[0]<br>(LSB) |  |  |

|---------------------|---------------------|---------------------------------------------------------------------------------------|---------------|------------|-------------|----------------|--------------|---------------|---------------|--|--|

|                     | Meaning             | Reserved                                                                              | Reserved      | Reserved   | Discharge   | Reserved       | Reserved     | Reserved      | Reserved      |  |  |

| 0x12                | Default             | х                                                                                     | Х             | Х          | 1           | Х              | х            | Х             | х             |  |  |

|                     | Read/Write          |                                                                                       |               |            | R/W         |                |              |               |               |  |  |

|                     |                     | Control the enabling of the LX discharge path when step-down converter is turned off. |               |            |             |                |              |               |               |  |  |

| D'                  | 1                   | 0 : Disable discharge path.                                                           |               |            |             |                |              |               |               |  |  |

| Discharge           |                     | 1 : Enable discharge path.                                                            |               |            |             |                |              |               |               |  |  |

|                     |                     | Note. If the                                                                          | ere is a star | ndby power | at VOUT pir | n, it is sugge | st to disabl | e this functi | on.           |  |  |

| Register<br>Address | Register<br>Address | b[7]<br>(MSB)                                                                                               | b[6]        | b[5]         | b[4]           | b[3]     | b[2]     | b[1]     | b[0]<br>(LSB) |  |  |

|---------------------|---------------------|-------------------------------------------------------------------------------------------------------------|-------------|--------------|----------------|----------|----------|----------|---------------|--|--|

|                     | Meaning             | PWM0                                                                                                        | PWM1        | Reserved     | Reserved       | Reserved | Reserved | Reserved | Reserved      |  |  |

| 0x14                | Default             | 1                                                                                                           | 1           | Х            | Х              | Х        | Х        | Х        | Х             |  |  |

|                     | Read/Write          | R/W                                                                                                         | R/W         |              |                |          |          |          |               |  |  |

|                     |                     | When VSEL = Low, it is used to control PWM operation mode of step-down converter                            |             |              |                |          |          |          |               |  |  |

| P\                  | VM0                 | 0 : step-down converter would automatically switch the operation mode among CCM (forced PWM), DCM, and PSM. |             |              |                |          |          |          |               |  |  |

|                     |                     | 1 : step-down converter works only at the forced PWM.                                                       |             |              |                |          |          |          |               |  |  |

|                     |                     | When VSEL = High, it is used to control PWM operation mode of step-down converter                           |             |              |                |          |          |          |               |  |  |

| PWM1                |                     | 0 : step-down converter would automatically switch the operation mode among CCM (forced PWM), DCM, and PSM. |             |              |                |          |          |          |               |  |  |

|                     |                     | 1 : step-do                                                                                                 | wn converte | er works onl | y at the force | ed PWM.  |          |          |               |  |  |

| Register<br>Address | Register<br>Address | b[7]<br>(MSB)                    | b[6] | b[5]     | b[4]     | b[3]     | b[2]     | b[1]     | b[0]<br>(LSB) |  |

|---------------------|---------------------|----------------------------------|------|----------|----------|----------|----------|----------|---------------|--|

|                     | Meaning             | IPEAK[1:0]                       |      | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved      |  |

| 0x16                | Default             | 1                                | 1    | Х        | Х        | Х        | Х        | Х        | Х             |  |

|                     | Read/Write          | R/W                              | R/W  |          |          |          |          |          |               |  |

| IPEAK[1:0]          |                     | Set inductor peak current limit. |      |          |          |          |          |          |               |  |

|                     |                     | 00 : 4.7A                        |      |          |          |          |          |          |               |  |

|                     |                     | 01 : 5.2A                        |      |          |          |          |          |          |               |  |

|                     |                     | 10 : 5.7A                        |      |          |          |          |          |          |               |  |

|                     |                     | 11 : 6.2A                        |      |          |          |          |          |          |               |  |

www.richtek.com

Copyright ©2015 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation. DS5701-01 July 2015

| Register<br>Address | Register<br>Address | b[7]<br>(MSB)                                       | b[6]       | b[5]           | b[4]     | b[3]     | b[2]     | b[1]          | b[0]<br>(LSB) |  |  |

|---------------------|---------------------|-----------------------------------------------------|------------|----------------|----------|----------|----------|---------------|---------------|--|--|

| 0.40                | Meaning             | ОСР                                                 | Reserved   | Reserved       | SCP      | Reserved | Reserved | PVIN_<br>UVLO | Reserved      |  |  |

| 0x18                | Default             | 0                                                   | Х          | Х              | 0        | Х        | Х        | 0             | Х             |  |  |

|                     | Read/Write          | R/W                                                 |            |                | R/W      |          |          | R/W           |               |  |  |

|                     |                     | Record the                                          | Over-curre | ent protectio  | n event. |          |          |               |               |  |  |

| 0                   | CP                  | 0 : Over-current protection is not triggered        |            |                |          |          |          |               |               |  |  |

|                     |                     | 1 : Over-current protection is triggered            |            |                |          |          |          |               |               |  |  |

|                     |                     | Record the Vout short-circuit protection event.     |            |                |          |          |          |               |               |  |  |

| S                   | CP                  | 0 : Vout short-circuit protection is not triggered  |            |                |          |          |          |               |               |  |  |

|                     |                     | 1 : Vout short-circuit protection is triggered      |            |                |          |          |          |               |               |  |  |

|                     |                     | Record the PVIN under voltage event after enabling. |            |                |          |          |          |               |               |  |  |

| PVIN                | _UVLO               | 0 : PVIN U                                          | VLO occurs | s is not trigg | ered     |          |          |               |               |  |  |

|                     |                     | 1 : PVIN UVLO occurs is triggered                   |            |                |          |          |          |               |               |  |  |

| Register<br>Address | Register<br>Address | b[7]<br>(MSB)                                                                                                   | b[6]                   | b[5]         | b[4]     | b[3]     | b[2]     | b[1]    | b[0]<br>(LSB) |  |  |

|---------------------|---------------------|-----------------------------------------------------------------------------------------------------------------|------------------------|--------------|----------|----------|----------|---------|---------------|--|--|

| 0x1C                | Meaning             | Reserved                                                                                                        | Reserve<br>d           | Reserve<br>d | Reserved | Reserved | Reserved | VOUT_BA | NK1[1:0]      |  |  |

|                     | Default             | Х                                                                                                               | Х                      | х            | Х        | Х        | Х        | 1       | 0             |  |  |

|                     | Read/Write          |                                                                                                                 |                        |              |          |          |          | R/W     | R/W           |  |  |

|                     |                     | When VSEL = High. It is used to select the Vout list. It should be set before enabling the step-down converter. |                        |              |          |          |          |         |               |  |  |

|                     |                     |                                                                                                                 | 00 : 0.303125V to 0.7V |              |          |          |          |         |               |  |  |

| VOUT_BANK1[1:0]     |                     | 01 : 0.60625V to 1.4V                                                                                           |                        |              |          |          |          |         |               |  |  |

|                     |                     | 10 : 1.2125V to 2.8V                                                                                            |                        |              |          |          |          |         |               |  |  |

|                     |                     | 11 : 2.425V to 5.6V                                                                                             |                        |              |          |          |          |         |               |  |  |

| Register<br>Address | Register<br>Address | b[7]<br>(MSB)                                                                                                                         | b[6]     | b[5]     | b[4]     | b[3]     | b[2]     | b[1]   | b[0]<br>(LSB) |  |

|---------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|--------|---------------|--|

|                     | Meaning             | Reserved                                                                                                                              | Reserved | Reserved | Reserved | Reserved | Reserved | VOUT_B | 4NK0[1:0]     |  |

| 0x1D                | Default             | Х                                                                                                                                     | Х        | Х        | Х        | Х        | Х        | 0      | 1             |  |

|                     | Read/Write          |                                                                                                                                       |          |          |          |          |          | R/W    | R/W           |  |

| VOUT_BANK0[1:0]     |                     | When VSEL = Low. It is used to select the Vout list. It should be set before enabling the step-down converter.  00: 0.303125V to 0.7V |          |          |          |          |          |        |               |  |

|                     |                     | 01 : 0.60625V to 1.4V                                                                                                                 |          |          |          |          |          |        |               |  |

|                     |                     | 10 : 1.2125V to 2.8V                                                                                                                  |          |          |          |          |          |        |               |  |

|                     |                     | 11 : 2.425V to 5.6V                                                                                                                   |          |          |          |          |          |        |               |  |

20

| Register<br>Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Register<br>Address | b[7]<br>(MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | b[6]      | b[5]  | b[4] | b[3]                                                  | b[2]                                                                 | b[1]                                      | b[0]<br>(LSB) |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|------|-------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------|---------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Meaning             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Vout_High | [3:0] |      |                                                       | Vout_L                                                               | .ow(3:0]                                  |               |

| 0x1E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Default             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1         | 1     | 1    | 0                                                     | 0                                                                    | 0                                         | 0             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Read/Write          | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W       | R/W   | R/W  | R/W                                                   | R/W                                                                  | R/W                                       | R/W           |

| Vout_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | High[3:0]           | To avoid DVS change Vout out of reliable range, set the field to limit the effective upple bound of Vout voltage level.  When VSEL = Low, if Register 0x11.VoutSEL0[6:0] > {Vout_High[3:0], 3'b111}, effective Vout would be limited to be the voltage corresponding to the code {Vout_High[3:3'b111}. Else effective Vout would follow Register 0x11.VoutSEL0[6:0] setting. Who VSEL = High, if Register 0x10.VoutSEL1[6:0] > {Vout_High[3:0], 3'b111}, effective Vout would be limited to be the voltage corresponding to the code {Vout_High[3:0], 3'b111}. Else effective Vout would follow Register 0x10.VoutSEL1[6:0] setting. |           |       |      |                                                       |                                                                      |                                           |               |

| Vout_Low[3:0]  To avoid DVS change Vout out of reliable range, set the field to bound of Vout voltage level.  When VSEL = Low, if Register 0x11.VoutSEL0[6:0] < {Vout_Low Vout would be limited to be the voltage corresponding to the 3'b000}. Else effective Vout would follow Register 0x11.VoutSEL0[When VSEL = High, if Register 0x10.VoutSEL1[6:0] < {Vout_Low Vout would be limited to be the voltage corresponding to the 3'b000}. Else effective Vout would follow Register 0x10.VoutSEL1[6:0] < {Vout_Low Vout would be limited to be the voltage corresponding to the 3'b000}. |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |       |      | out_Low[3: g to the coutSEL0[6: out_Low[3: g to the c | 0], 3'b000]<br>ode {Vout<br>0] setting.<br>:0], 3'b000]<br>ode {Vout | , effective<br>_Low[3:0],<br>}, effective |               |

Copyright ©2015 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For TSSOP-14 (Exposed Pad) package, the thermal resistance, θ<sub>JA</sub>, is 30.1°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25$ °C can be calculated by the following formula:

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (30.1^{\circ}C/W) = 3.32W \text{ for}$ TSSOP-14 (Exposed Pad) package

The maximum power dissipation depends on the operating ambient temperature for fixed T<sub>J(MAX)</sub> and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 6 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 6. Derating Curve of Maximum Power Dissipation

#### **Layout Consideration**

For the best performance of the RT5701, the following PCB layout guidelines must be strictly followed.

- Place the input and output capacitors as close as possible to the input and output pins respectively for good filtering.

- Keep the main power traces as wide and short as possible.

- > The switching node area connected to LX and inductor should be minimized for lower EMI.

- Place the feedback components as close as possible to the VOUT pin and keep these components away from the noisy devices.

Figure 7. PCB Layout Guide

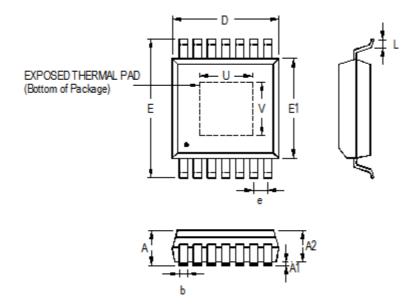

## **Outline Dimension**

| O. makal | Dimensions | In Millimeters | Dimensions In Inches |       |  |  |

|----------|------------|----------------|----------------------|-------|--|--|

| Symbol   | Min Max    |                | Min                  | Max   |  |  |

| А        | 1.000      | 1.200          | 0.039                | 0.047 |  |  |

| A1       | 0.000      | 0.150          | 0.000                | 0.006 |  |  |

| A2       | 0.800      | 1.050          | 0.031                | 0.041 |  |  |

| b        | 0.190      | 0.300          | 0.007                | 0.012 |  |  |

| D        | 4.900      | 5.100          | 0.193                | 0.201 |  |  |

| е        | e 0.650    |                | 0.0                  | )26   |  |  |

| E        | 6.300      | 6.500          | 0.248                | 0.256 |  |  |

| E1       | 4.300      | 4.500          | 0.169                | 0.177 |  |  |

| L        | 0.450      | 0.750          | 0.018                | 0.030 |  |  |