**RT5801**

# 3V to 5.5V, 4-Phase, Step-Down Converter with I<sup>2</sup>C Interface

### 1 General Description

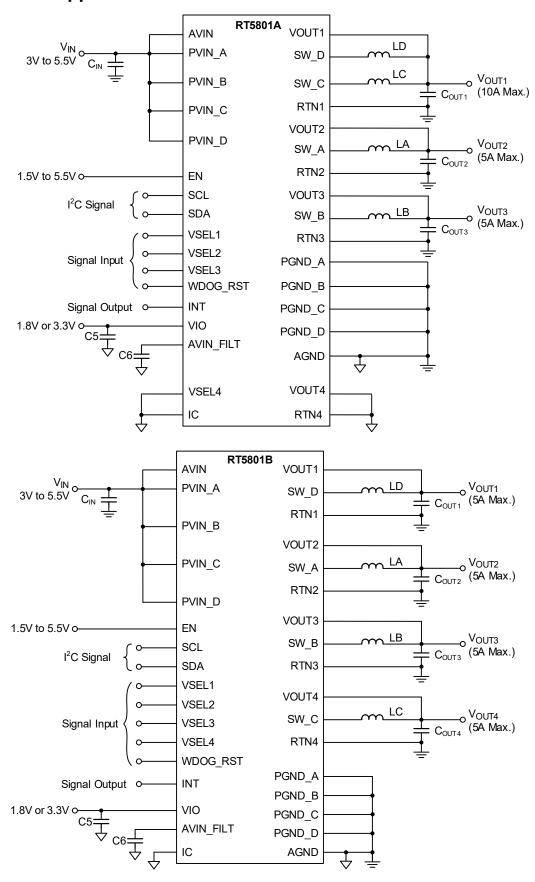

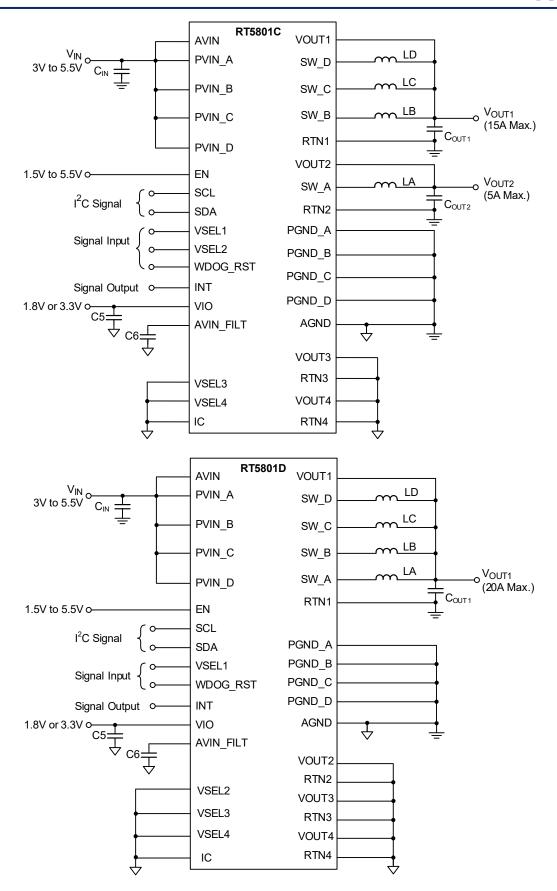

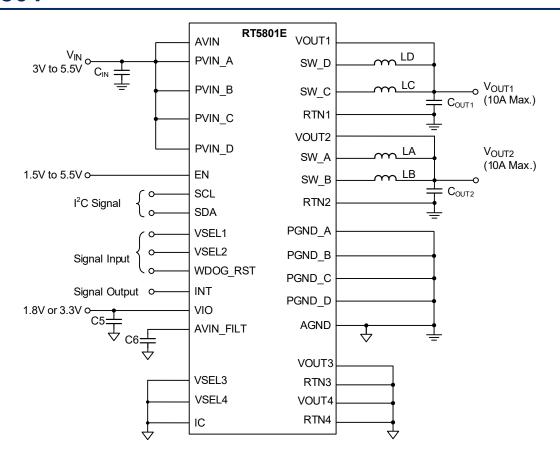

The RT5801 series products are synchronous stepdown converters with 4-phase capability, allowing for both multiphase and single-phase operations. These products offer a wide range of configuration options. The RT5801A provides triple outputs with 2+1+1 phase, while the RT5801B offers quad outputs with 1+1+1+1 phase. The RT5801C provides dual outputs with 3+1 phase, and the RT5801D offers a single output with 4phase. Lastly, the RT5801E provides dual outputs with 2+2 phase. This flexibility and high integration make the RT5801 series suitable for various applications that require high current and compact power management solutions, such as low-power processors, I/O power, the core power of FPGA, DSP, and other ASICs. With an input voltage range of 3V to 5.5V, these converters are compatible with a wide variety of low voltage systems. They can deliver up to 20A peak current and support output voltages ranging from 0.4V to 1.55V.

The RT5801 series products also offer programmable functions, including voltage level, voltage change slew rate, and soft-start slew rate, which can be controlled through an I<sup>2</sup>C interface operating at up to 3.4MHz. Additionally, these products support remote-sense function to ensure accurate output voltage under heavy loads. They are equipped with interrupt and fault-detection functions to report any error status. The RT5801 series products are available in a WL-CSP-54B 2.69x3.92 (BSC) package.

The recommended junction temperature range is  $-40^{\circ}$ C to 125°C.

See Ordering Information for the key features of each part number.

### 2 Features

- 4-Phase Buck Converter with Integrated MOSFETs

- Input Supply Voltage Range: 3V to 5.5V

- Typical Switching Frequency:

- 2MHz and 2.2MHz

- I<sup>2</sup>C Programmable Output Voltage Range:

- 0.4V to 2.05V

- (0.4 to 1.55V for 3-phase and 4-phase outputs)

Support 5A Output Current Capability Per Phase

- Differential Remote Sense for Each Output with High Accuracy

- Fast Transient Response

- Power Saving Mode Enables Higher Light Load Efficiency

- Output Dynamic Voltage Scaling (DVS) with Programmable Ramp Up/Down Slew Rate

- Programmable Soft-Start Function

- Programmable Startup/Shutdown Sequence

- Interrupt Function and Fault Detection

- Watchdog Reset Function Prevents System Hang

- Input Undervoltage-Lockout (UVLO)

- Cycle-by-Cycle Current Limit for Each Phase

- Output Overvoltage/Undervoltage Protection

- Over-Temperature Protection

- WL-CSP-54B 2.69x3.92 (BSC) Package

## 3 Applications

- Home Gateway and Access Point Networks

- Optical Modules

- Set-Top Boxes and OTT Devices

- Storage Systems

- Surveillance Systems

RICHTEK

June

RT5801 DS-03

www.richtek.com

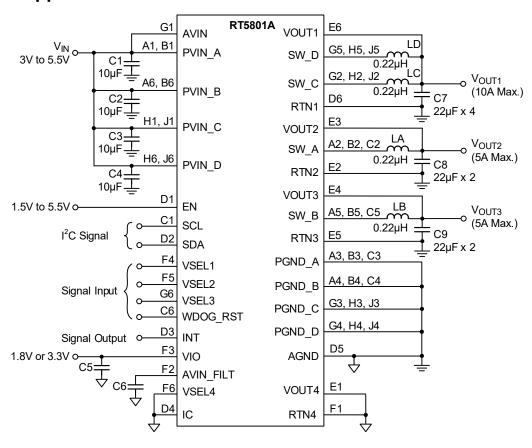

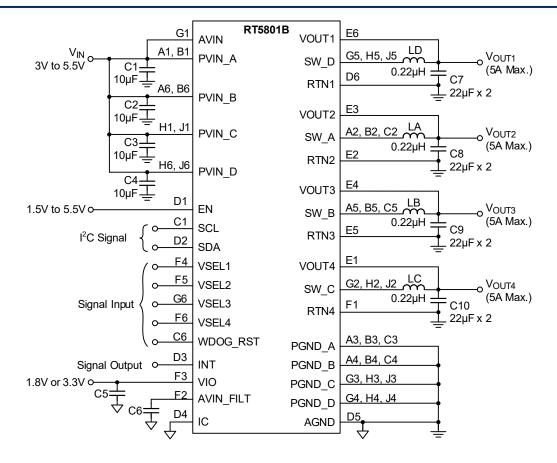

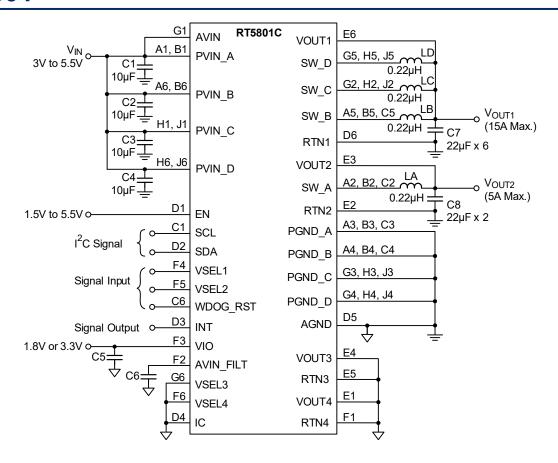

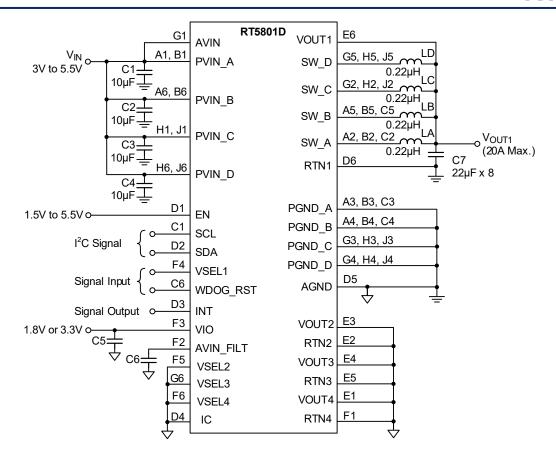

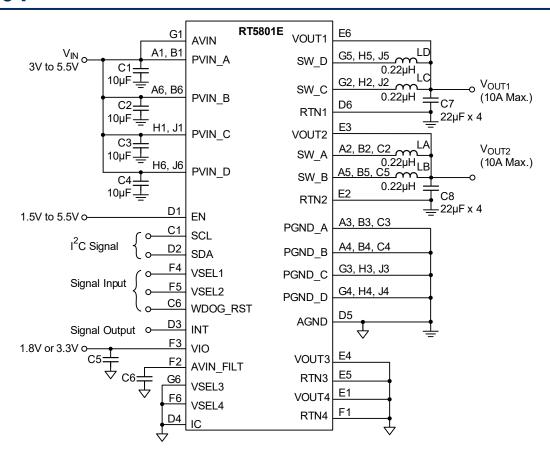

### 4 Simplified Application Circuit

### 5 Ordering Information

| Product<br>Number <sup>(1)</sup> | Output<br>Channel | Configuration | Typical<br>Switching<br>Frequency | I <sup>2</sup> C<br>Programmable<br>Output Voltage | Package Type <sup>(2)</sup> |

|----------------------------------|-------------------|---------------|-----------------------------------|----------------------------------------------------|-----------------------------|

| RT5801AWSC-YY                    | Vout1~3           | 2+1+1 phase   |                                   |                                                    |                             |

| RT5801BWSC-YY                    | Vout1~4           | 1+1+1+1 phase | 2MHz                              | 0.4V to 2.05V                                      |                             |

| RT5801EWSC-YY                    | Vout1~2           | 2+2 phase     |                                   |                                                    | WL-CSP-54B                  |

| RT5801CWSC-YY                    | Vout1             | 2+1 phase     |                                   | 0.4V to 1.55V                                      | 2.69x3.92 (BSC)             |

| K15001CWSC-11                    | Vout2             | 3+1 phase     | 2.2MHz                            | 0.4V to 2.05V                                      |                             |

| RT5801DWSC-YY                    | Vout1             | 4+0 phase     |                                   | 0.4V to 1.55V                                      |                             |

#### Note 1.

- Marked with <sup>(1)</sup> indicated: The last two bits "YY" represent the trim version. See Product Status for all available devices. For additional trim options, contact our sales representative directly or through a Richtek distributor located in your area.

- Marked with (2) indicated: Compatible with the current requirements of IPC/JEDEC J-STD-020.

## 6 Marking Information

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

### **Table of Contents**

| 1  | Gene  | eral Description                     | 1  |    | 17.6 Watchdog Function                  | 31 |

|----|-------|--------------------------------------|----|----|-----------------------------------------|----|

| 2  | Featu | ures                                 | 1  |    | 17.7 Fault Detection and Interrupt Pin  | 32 |

| 3  | Appli | ications                             | 1  |    | 17.8 Current-Limit Protection           | 33 |

| 4  | Simp  | lified Application Circuit           | 2  |    | 17.9 Output Undervoltage Protection     | 33 |

| 5  | Orde  | ring Information                     | 5  |    | 17.10 Output Overvoltage Protection     | 34 |

| 6  | Mark  | ing Information                      | 5  |    | 17.11 Over-Temperature Protection       | 34 |

| 7  | Pin C | Configuration                        | 7  |    | 17.12 Negative Overcurrent Protection   |    |

| 8  | Func  | tional Pin Description               | 7  |    | (FCCM Only)                             | 34 |

| 9  | Func  | tional Block Diagram                 | 10 | 18 | Application Information                 | 35 |

| 10 | Abso  | olute Maximum Ratings                | 11 |    | 18.1 Inductor Selection                 | 35 |

| 11 | ESD   | Ratings                              | 11 |    | 18.2 Input Capacitor Selection          | 35 |

| 12 | Reco  | mmended Operating Conditions         | 11 |    | 18.3 Output Capacitor Selection         | 35 |

| 13 | Ther  | mal Information                      | 11 |    | 18.4 Thermal Considerations             | 36 |

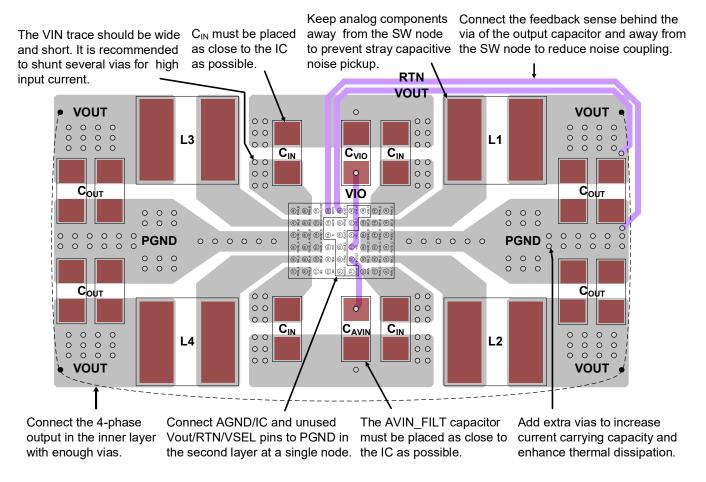

| 14 | Elect | rical Characteristics                | 12 |    | 18.5 Layout Guidelines                  | 37 |

|    | 14.1  | System Characteristics               | 13 |    | 18.6 I <sup>2</sup> C Interface         | 40 |

| 15 | Typic | cal Application Circuit              | 16 | 19 | Functional Register Description         | 42 |

| 16 | Typic | cal Operating Characteristics        | 21 | 20 | Outline Dimension                       | 75 |

| 17 | Oper  | ation                                | 26 | 21 | Footprint Information                   | 76 |

|    | 17.1  | UVLO, Enable Control, and Soft-Start |    | 22 | Packing Information                     | 77 |

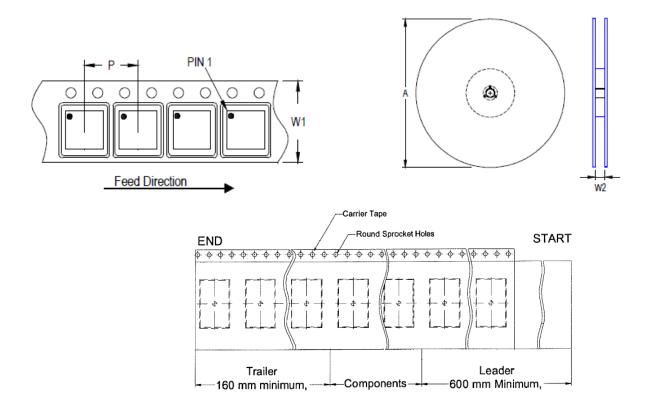

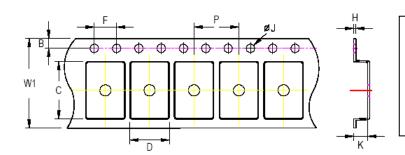

|    |       | Function                             | 27 |    | 22.1 Tape and Reel Data                 | 77 |

|    | 17.2  | Dynamic Voltage Scaling (DVS)        | 29 |    | 22.2 Tape and Reel Packing              | 78 |

|    | 17.3  | MODE Selection                       |    |    | 22.3 Packing Material Anti-ESD Property | 79 |

|    | 17.4  | Automatically Phase Adding/Shedding  | 31 | 23 | Product Status                          | 80 |

|    | 17.5  | Power-Good Indication                | 31 |    |                                         |    |

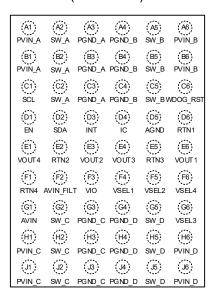

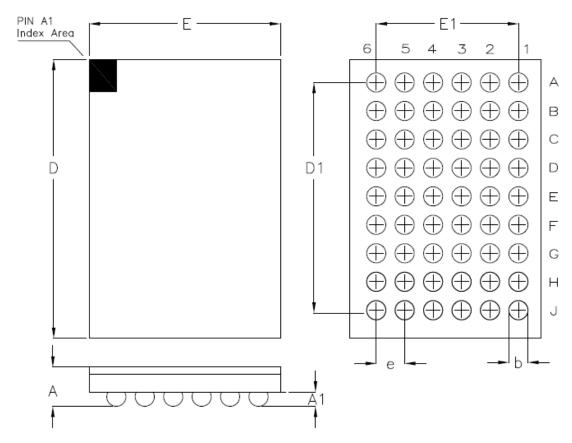

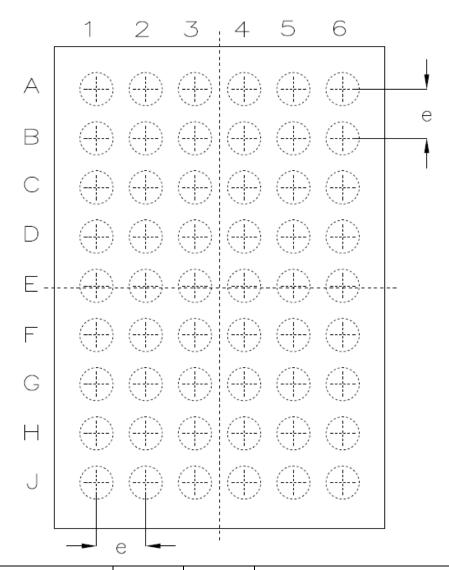

### Pin Configuration

(TOP VIEW)

WL-CSP-54B 2.69x3.92 (BSC)

### **Functional Pin Description**

| Pin No.    | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                     |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, B1     | PVIN_A   | Power input for power stage A. It is recommended to use a $10\mu\text{F},~\text{X7R}$ capacitor.                                                                                                                                                                                                                                                 |

| A2, B2, C2 | SW_A     | Switch node for power stage A. Connect to the power inductor.                                                                                                                                                                                                                                                                                    |

| A3, B3, C3 | PGND_A   | Power ground for power stage A.                                                                                                                                                                                                                                                                                                                  |

| A4, B4, C4 | PGND_B   | Power ground for power stage B.                                                                                                                                                                                                                                                                                                                  |

| A5, B5, C5 | SW_B     | Switch node for power stage B. Connect to the power inductor.                                                                                                                                                                                                                                                                                    |

| A6, B6     | PVIN_B   | Power input for power stage B. It is recommended to use a $10\mu\text{F},~\text{X7R}$ capacitor.                                                                                                                                                                                                                                                 |

| C1         | SCL      | Clock input for the I <sup>2</sup> C interface. The pull-up voltage supply must be the same as the VIO voltage for correct operation. Connect this pin to AGND if the I <sup>2</sup> C interface is not used. "Do Not" leave this pin floating.                                                                                                  |

| C6         | WDOG_RST | Control input for output voltage reset. Reset each buck output voltage, DVSx, and ENDVSx registers to the factory default setting value when this pin is pulled low. Connect this pin to be higher than 70% of the VIO pin voltage if this pin is not used. "Do Not" leave this pin floating. The minimum watchdog debounce time is $100\mu s$ . |

| D1         | EN       | Master chip enable. A logic-high enables the converter; a logic-low forces the device into shutdown mode. "Do Not" leave this pin floating.                                                                                                                                                                                                      |

| D2         | SDA      | Data line for the I <sup>2</sup> C interface. The pull-up voltage supply must be the same as the VIO voltage for correct operation. Connect this pin to AGND if the I <sup>2</sup> C interface is not used. "Do Not" leave this pin floating.                                                                                                    |

| D3         | INT      | Interrupt indicator.                                                                                                                                                                                                                                                                                                                             |

| D4         | IC       | Internal connection. Connect this pin to AGND.                                                                                                                                                                                                                                                                                                   |

| D5         | AGND     | Ground for internal analog and digital circuitry.                                                                                                                                                                                                                                                                                                |

Copyright © 2025 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

| Pin No.    | Pin Name  | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D6         | RTN1      | Remote ground sense for Buck1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| E1         | VOUT4     | Output voltage sense for Buck4. Short to AGND for RT5801A/C/D/E.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| E2         | RTN2      | Remote ground sense for Buck2. Short to AGND for RT5801D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| E3         | VOUT2     | Output voltage sense for Buck2. Short to AGND for RT5801D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| E4         | VOUT3     | Output voltage sense for Buck3. Short to AGND for RT5801C/D/E.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| E5         | RTN3      | Remote ground sense for Buck3. Short to AGND for RT5801C/D/E.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| E6         | VOUT1     | Output voltage sense for Buck1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| F1         | RTN4      | Remote ground sense for Buck4. Short to AGND for RT5801A/C/D/E.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| F2         | AVIN_FILT | Filtered analog supply voltage. It is recommended to connect a $1\mu\text{F},~\text{X7R}$ capacitor from this pin to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| F3         | VIO       | I/O supply voltage for digital communications. Connect this pin to 1.8V or 3.3V. "Do Not" leave this pin floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| F4         | VSEL1     | Buck1 DVS register selection control input. $0x52[1:0]$ determines the DVS register control input of Buck1. When $0x52[1:0]$ is set to "10", Buck1 DVS up or down operation is controlled by the external VSEL1 pin. Then $0x52[2]$ determines the polarity of the VSEL1 pin: DVS0 is selected if the VSEL1 pin is pulled up to $V_{VIO}$ , but DVS1 is selected if the VSEL1 pin is pulled down to AGND. The factory default setting value of $0x52[1:0]$ is 00 (DVS0 is selected and ignores the VSEL1 pin). "Do Not" leave this pin floating.                                |

| F5         | VSEL2     | Buck2 DVS register selection control input. 0x6C[1:0] determines the DVS register control input of Buck2. When 0x6C[1:0] is set to "10", Buck2 DVS up or down operation is controlled by the external VSEL2 pin. Then 0x6C[2] determines the polarity of the VSEL2 pin: DVS0 is selected if the VSEL2 pin is pulled up to VVIO, but DVS1 is selected if the VSEL2 pin is pulled down to AGND. The factory default setting value of 0x6C[1:0] is 00 (DVS0 is selected and ignores the VSEL2 pin). "Do Not" leave this pin floating. Short to AGND for RT5801D.                   |

| G6         | VSEL3     | Buck3 DVS register selection control input. $0x86[1:0]$ determines the DVS register control input of Buck3. When $0x86[1:0]$ is set to "10", Buck3 DVS up or down operation is controlled by the external VSEL3 pin. Then $0x86[2]$ determines the polarity of the VSEL3 pin: DVS0 is selected if the VSEL3 pin is pulled up to $V_{VIO}$ , but DVS1 is selected if the VSEL3 pin is pulled down to AGND. The factory default setting value of $0x86[1:0]$ is 00 (DVS0 is selected and ignores the VSEL3 pin). "Do Not" leave this pin floating. Short to AGND for RT5801C/D/E. |

| G1         | AVIN      | Analog supply voltage input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| G2, H2, J2 | SW_C      | Switch node for power stage C. Connect to the power inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| G3, H3, J3 | PGND_C    | Power ground for power stage C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| G4, H4, J4 | PGND_D    | Power ground for power stage D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| G5, H5, J5 | SW_D      | Switch node for power stage D. Connect to the power inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F6      | VSEL4    | Buck4 DVS register selection control input. 0xA0[1:0] determines the DVS register control input of Buck4. When 0xA0[1:0] is set to "10", Buck4 DVS up or down operation is controlled by the external VSEL4 pin. Then 0xA0[2] determines the polarity of the VSEL4 pin: DVS0 is selected if the VSEL4 pin is pulled up to VVIO, but DVS1 is selected if the VSEL4 pin is pulled down to AGND. The factory default setting value of 0xA0[1:0] is 00 (DVS0 is selected and ignores the VSEL4 pin). "Do Not" leave this pin floating. Short to AGND for RT5801A/C/D/E. |

| H1, J1  | PVIN_C   | Power input for power stage C. It is recommended to use a $10\mu\text{F},~\text{X7R}$ capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| H6, J6  | PVIN_D   | Power input for power stage D. It is recommended to use a $10\mu\text{F},~\text{X7R}$ capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

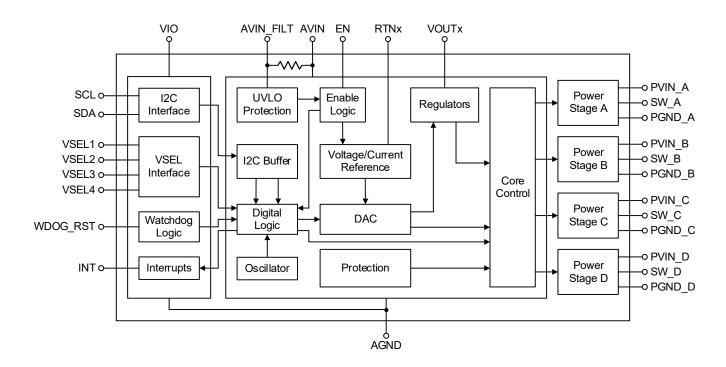

## 9 Functional Block Diagram

www.richtek.com

### 10 Absolute Maximum Ratings

#### (Note 2)

- **Note 2.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

### 11 ESD Ratings

#### (Note 3)

ESD Susceptibility

HBM (Human Body Model) ----- 2kV

Note 3. Devices are ESD sensitive. Handling precautions are recommended.

### 12 Recommended Operating Conditions

### (Note 4)

| Supply Input Voltage                                 | - 3V to 5.5V    |

|------------------------------------------------------|-----------------|

| Output Voltage Range for 1 and 2 Phase Configuration | - 0.4V to 2.05V |

| Output Voltage Range for 3 and 4 Phase Configuration | - 0.4V to 1.55V |

| Junction Temperature Range                           | 40°C to 125°C   |

|                                                      |                 |

**Note 4.** The device is not guaranteed to function outside its operating conditions.

#### 13 Thermal Information

#### (Note 5 and Note 6)

|                     | Thermal Parameter                                       | WL-CSP-54B<br>2.69x3.92 (BSC) | Unit |

|---------------------|---------------------------------------------------------|-------------------------------|------|

| $\theta$ JA         | Junction-to-ambient thermal resistance (JEDEC standard) | 37.9                          | °C/W |

| $\theta$ JC(Top)    | Junction-to-case (top) thermal resistance               | 0.8                           | °C/W |

| $\theta$ JC(Bottom) | Junction-to-case (bottom) thermal resistance            | 2.3                           | °C/W |

| θJA(EVB)            | Junction-to-ambient thermal resistance (specific EVB)   | 35.2                          | °C/W |

| ΨJC(Top)            | Junction-to-top characterization parameter              | 2.4                           | °C/W |

| ΨЈВ                 | Junction-to-board characterization parameter            | 19.6                          | °C/W |

Note 5. For more information about thermal parameter, see the Application and Definition of Thermal Resistances report, AN061.

Note 6. θ<sub>JA(EVB)</sub> and Ψ<sub>JC(TOP)</sub> are measured on a high effective-thermal-conductivity four-layer test board which is in size of 110mm x 100mm; furthermore, all layers with 1 oz. Cu. Thermal resistance/parameter values may vary depending on the PCB material, layout, and test environmental conditions.

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

### 14 Electrical Characteristics

(Note 7)

( $V_{IN}$  = 3.7V,  $V_{VIO}$  = 1.8V or 3.3V,  $T_J$  = -40°C to 125°C, unless otherwise specified.)

| Parameter                                                | Symbol    | Test Conditions                                          | Min          | Тур | Max          | Unit    |  |

|----------------------------------------------------------|-----------|----------------------------------------------------------|--------------|-----|--------------|---------|--|

| Analog Input Voltage                                     | VAVIN     |                                                          | 3            |     | 5.5          | V       |  |

| Power Input Voltage                                      | VPVIN     |                                                          | 3            |     | 5.5          | V       |  |

| Shutdown Current                                         | ISHDN     | EN = 0V, Digital circuit does not work                   |              | 0.1 |              | μΑ      |  |

| Buck Off Current                                         | ISDBO     | EN = VIO = 1.8V, disable all Buck converters by software |              | 30  |              | μА      |  |

| 1Phase No Switching<br>Current                           | ISLP_1ph  | Vout = 1.2 x Vout_setting                                |              | 100 |              | μΑ      |  |

| 2Phase No Switching<br>Current                           | ISLP_2ph  | Vout = 1.2 x Vout_setting                                |              | 130 |              | μА      |  |

| 3Phase No Switching<br>Current                           | ISLP_3ph  | Vout = 1.2 x Vout_setting                                |              | 160 |              | μΑ      |  |

| 4Phase No Switching<br>Current                           | ISLP_4ph  | Vout = 1.2 x Vout_setting                                |              | 190 |              | μΑ      |  |

| Undervoltage-Lockout<br>Threshold                        | Vuvlo     | V <sub>IN</sub> rising                                   | 2.45         | 2.7 | 2.95         | V       |  |

| Undervoltage-Lockout<br>Hysteresis                       | ΔVUVLO    |                                                          |              | 300 |              | mV      |  |

| Switching Frequency                                      | fsw       | RT5801A/B/E, Vout = 1V (FCCM)                            | 1.7          | 2   | 2.3          | MHz     |  |

|                                                          |           | RT5801C/D, Vout = 1V (FCCM)                              | 1.9          | 2.2 | 2.4          | IVII IZ |  |

| On-Resistance of High-<br>side MOSFET                    | RDSON_H   | VIN = 5V                                                 |              | 17  |              | mΩ      |  |

| On-Resistance of Low-<br>side MOSFET                     | RDSON_L   | V <sub>IN</sub> = 5V                                     |              | 5   |              | mΩ      |  |

| HSFET Current-Limit per Channel                          | Ішм_н     |                                                          | 6.5          | 8   | 9            | Α       |  |

| LSFET Current-Limit per<br>Channel                       | ILIM_L    |                                                          | 5            | 7   | 8.5          | Α       |  |

| LSFET Negative Current-<br>Limit per Channel             | ILIM_NL   |                                                          |              | 3.5 |              | Α       |  |

| SDA, SCL, WDOG_RST,<br>VSEL Input Voltage Logic-<br>High | VIH       | $3V \leq V_{IN} \leq 5.5V$                               | 0.7 x<br>VIO |     |              | V       |  |

| SDA, SCL, WDOG_RST,<br>VSEL Input Voltage Logic-<br>Low  | VIL       | $3V \le V_{IN} \le 5.5V$                                 |              |     | 0.3 x<br>VIO | V       |  |

| EN Input Voltage Rising<br>Threshold                     | VEN_R     |                                                          | 1.2          |     |              | V       |  |

| EN Input Voltage Falling<br>Threshold                    | VEN_F     |                                                          |              |     | 0.4          | v       |  |

| Vout DC Accuracy                                         | VOUT_FPWM | Forced PWM, 0.6V ≤ V <sub>OUT</sub> ≤ 2.05V              | -1.5         |     | 1.5          | %       |  |

| Output Undervoltage<br>Protection Rising<br>Threshold    | VUVP_R    | Trigger level                                            | 40           | 50  | 60           | %       |  |

| Parameter                                              | Symbol   | Test Conditions                                                      | Min | Тур | Max | Unit |

|--------------------------------------------------------|----------|----------------------------------------------------------------------|-----|-----|-----|------|

| Output Undervoltage<br>Protection Falling<br>Threshold | Vuvp_f   | Recovery level                                                       | 47  | 57  | 67  | %    |

| Output Overvoltage<br>Protection Rising<br>Threshold   | Vovp_r   | Trigger level                                                        | 120 | 133 | 145 | %    |

| Output Overvoltage<br>Protection Falling<br>Threshold  | Vovp_f   | Recovery level                                                       | 110 | 125 | 140 | %    |

| Minimum On-Time                                        | ton_min  |                                                                      | -   | 40  |     | ns   |

| Minimum Off-Time                                       | toff_min |                                                                      |     | 90  |     | ns   |

| Discharge Resistor                                     | Rdischg  |                                                                      |     | 10  |     | Ω    |

| O                                                      |          | RT5801A/E, Load = 10A,  IAvg – ISW_N;<br>N = A to D , TA = 0 to 85°C |     |     | 0.5 | Α    |

| Current Balance                                        | IBALANCE | Load = 10A,  IAvg - ISW_N; N = A to D                                |     |     | 1.2 | Α    |

| INT Output Voltage Logic-<br>High                      | Vон      | Push-pull, ISINK = 2mA                                               | 1.6 |     | VIO | V    |

| INT Output Voltage Logic-<br>Low                       | VoL      | Output low level, ISOURCE = 2mA                                      |     |     | 0.4 | V    |

**Note 7.** The measured switching frequency may not always fall within the declared range due to variations in operation modes and operating points. In auto mode, the switching frequency (fsw) is reduced to enable power-saving functionality during light load conditions. Additionally, in multiphase operation, the fsw varies based on the active phase count in auto mode, meaning that the switching frequency adjusts according to the number of active phases.

### 14.1 System Characteristics

The following specifications are guaranteed by design and are not performed in production testing. ( $V_{IN} = 3.7V$ ,  $V_{VIO} = 1.8V$  or 3.3V,  $T_{J} = -40^{\circ}$ C to 125°C, unless otherwise specified.)

| Parameter                  | Symbol     | Test Conditions                                                                                                                                              | Min  | Тур   | Max | Unit |  |  |  |

|----------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----|------|--|--|--|

| System                     | System     |                                                                                                                                                              |      |       |     |      |  |  |  |

| Vout DC Accuracy           | Vout_auto  | Auto Mode, Vout = 1V                                                                                                                                         | -2.5 |       | 2.5 | %    |  |  |  |

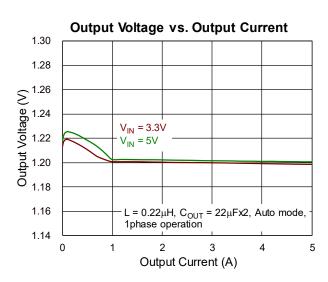

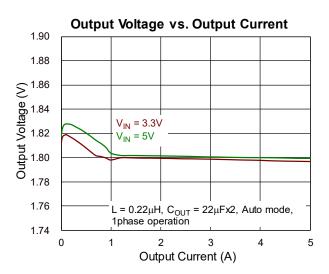

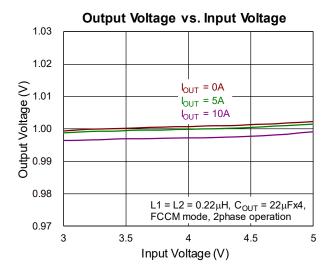

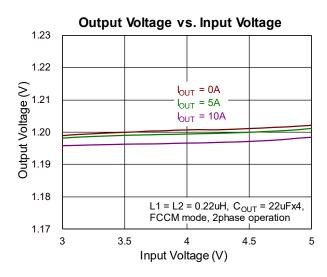

| Load Regulation            | VLOAD_REG  | IOUT(DC) = 0A to 10A (FCCM)                                                                                                                                  |      | -0.08 |     | %/A  |  |  |  |

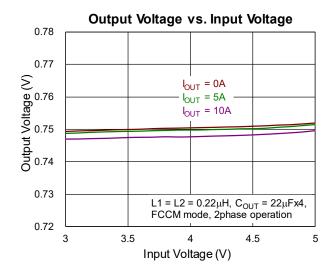

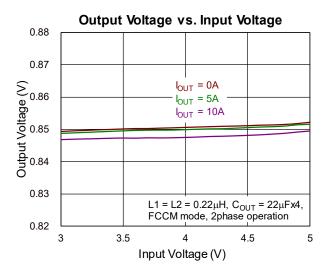

| Line Regulation            | VLINE_REG  | $3V \le V_{IN} \le 5V$ , $I_{OUT(DC)} = 0A$ (FCCM)                                                                                                           |      | 0.2   |     | %/V  |  |  |  |

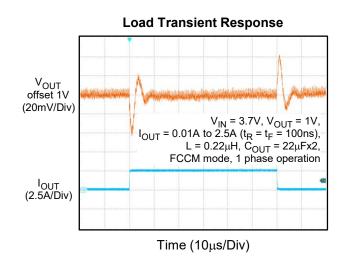

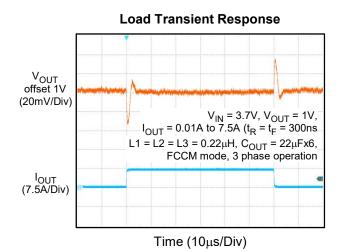

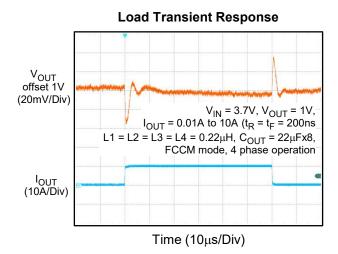

| Load Transient<br>Response | VLOAD_TRAN | 1-phase configuration, 0.01A to 2.5A, tR = tF = 100ns, L= 0.22 $\mu$ H, VOUT = 1V, COUT = 22 $\mu$ F x 2/phase, TA = 25°C (FCCM)                             |      | ±50   |     | mV   |  |  |  |

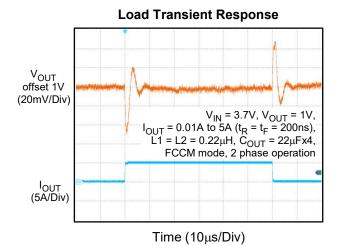

|                            |            | 2-phase configuration, 0.01A to 5A, $t_R = t_F = 200 ns$ , $L = 0.22 \mu H$ , $V_{OUT} = 1 V$ , $C_{OUT} = 22 \mu F$ x 2/phase, $T_A = 25 ^{\circ} C$ (FCCM) |      | ±50   |     | mV   |  |  |  |

|                            |            | 3-phase configuration, 0.01A to 7.5A, tR = tF = 300ns, L= 0.22 $\mu$ H, VOUT = 1V, COUT = 22 $\mu$ F x 2/phase, TA = 25°C (FCCM)                             |      | ±50   |     | mV   |  |  |  |

|                            |            | 4-phase configuration, 0.01A to 10A, tR = tF = 200ns, L= 0.22 $\mu$ H, VOUT = 1V, COUT = 22 $\mu$ F x 2/phase, TA = 25°C (FCCM)                              |      | ±50   |     | mV   |  |  |  |

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

| Parameter                                       | Symbol      | Test Conditions                                                   | Min  | Тур | Max | Unit    |  |

|-------------------------------------------------|-------------|-------------------------------------------------------------------|------|-----|-----|---------|--|

|                                                 |             | From 1-phase to 2-phase, Vout = 1V                                |      | 3.6 |     | Α       |  |

| Phase Adding Level                              | IPHASE_ADD  | From 2-phase to 3-phase, V <sub>OUT</sub> = 1V                    |      | 5.4 |     | Α       |  |

|                                                 |             | From 3-phase to 4-phase, V <sub>OUT</sub> = 1V                    |      | 8.2 |     | Α       |  |

|                                                 |             | From 2-phase to 1-phase, Vout = 1V                                |      | 2   |     |         |  |

| Phase Shedding<br>Level                         | IPHASE_SHED | From 3-phase to 2-phase, Vout = 1V                                |      | 4.5 |     | Α       |  |

| 20001                                           |             | From 4-phase to 3-phase, Vout = 1V                                |      | 6.4 |     |         |  |

| Soft-Start Time                                 | tss         | Slew Rate = 10mV/μs                                               | -20  |     | +20 | %       |  |

| Dynamic Voltage<br>Scaling Rising Slew<br>Rate  | tDVS_SR_R   | VIN = 3.7V, VOUT = 0.6V to 1.2V, Slew<br>Rate = 16mV/μs (default) | -20  |     | +20 | %       |  |

| Dynamic Voltage<br>Scaling Falling Slew<br>Rate | tDVS_SR_F   | VIN = 3.7V, VOUT = 1.2V to 0.6V, Slew<br>Rate = 4mV/μs (default)  | -20  |     | +20 | %       |  |

| Over-Temperature Protection Threshold           | Тотр        |                                                                   |      | 160 |     | °C      |  |

| Over-Temperature Protection Hysteresis          | TOTP_HYS    |                                                                   |      | 40  |     | °C      |  |

| HOT Die Warning                                 | THD         |                                                                   |      | 110 |     | °C      |  |

| HOT Die Warning<br>Hysteresis                   | THD_HYS     |                                                                   |      | 15  |     | °C      |  |

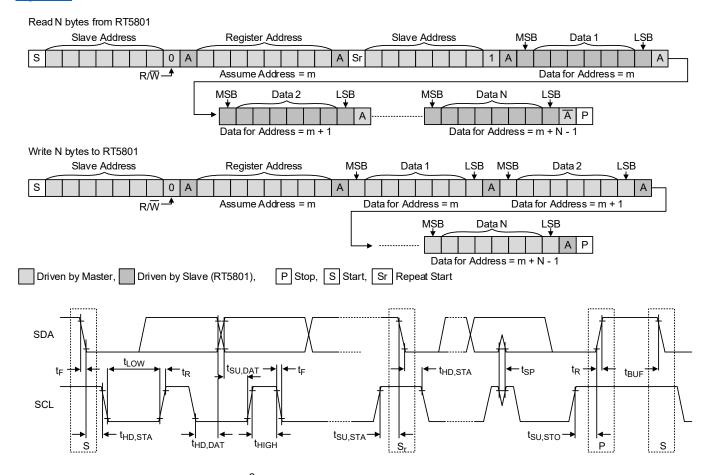

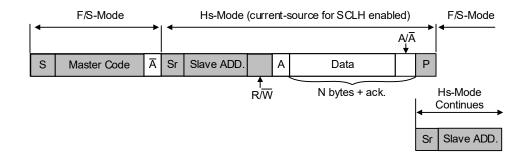

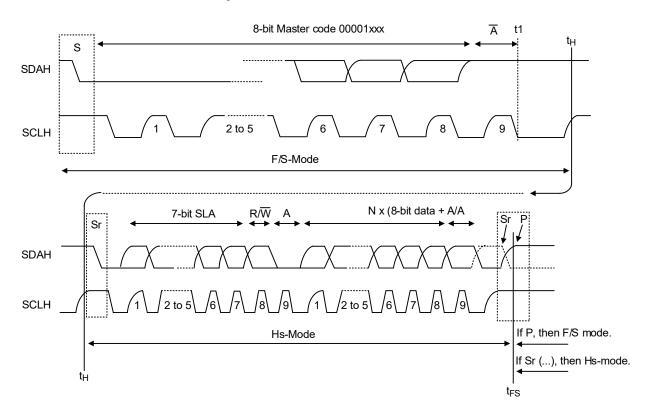

| I <sup>2</sup> C Interface                      |             |                                                                   |      |     |     |         |  |

|                                                 | fscL        | Standard mode                                                     |      |     | 100 | kHz     |  |

| SCL Clock Rate                                  |             | Fast mode                                                         |      |     | 400 | kHz     |  |

| SOL CIOCK Nate                                  |             | Fast mode plus                                                    |      |     | 1   | MHz     |  |

|                                                 |             | High speed mode, load 100pF max                                   |      |     | 3.4 | MHz     |  |

|                                                 |             | Standard mode                                                     | 4    |     |     | -<br>μs |  |

| (Repeated) Start Hold                           | thd;sta     | Fast mode                                                         | 0.6  |     |     |         |  |

| Time                                            | IND,STA     | Fast mode plus                                                    | 0.26 |     |     |         |  |

|                                                 |             | High speed mode                                                   | 0.16 |     |     |         |  |

|                                                 |             | Standard mode                                                     | 4.7  |     |     |         |  |

| SCL Clock Low                                   | t. 014      | Fast mode                                                         | 1.3  |     |     |         |  |

| Period                                          | tLOW        | Fast mode plus                                                    | 0.5  |     |     | μS      |  |

|                                                 |             | High speed mode                                                   | 0.16 |     |     |         |  |

|                                                 |             | Standard mode                                                     | 4    |     |     |         |  |

| SCL Clock High                                  | tu no u     | Fast mode                                                         | 0.6  |     |     |         |  |

| Period                                          | thigh       | Fast mode plus                                                    | 0.26 |     |     | μS      |  |

|                                                 |             | High speed mode                                                   | 0.09 |     |     |         |  |

|                                                 |             | Standard mode                                                     | 4.7  |     |     |         |  |

| (Repeated) Start                                | toures      | Fast mode                                                         | 0.6  |     |     |         |  |

| Setup Time                                      | tsu;sta     | Fast mode plus                                                    | 0.26 |     |     | μS      |  |

|                                                 |             | High speed mode                                                   | 0.16 |     |     | -       |  |

| Parameter                        | Symbol  | Test Conditions                         | Min                    | Тур | Max  | Unit |

|----------------------------------|---------|-----------------------------------------|------------------------|-----|------|------|

|                                  | 4       | Standard mode                           | 5                      |     |      |      |

| SDA Data Hold Time               |         | Fast mode                               | 0                      |     |      |      |

| SDA Data Hold Time               | thd;dat | Fast mode plus                          | 0                      |     |      | μS   |

|                                  |         | High speed mode                         | 0                      |     |      |      |

|                                  |         | Standard mode                           | 250                    |     |      |      |

| CDA Catur Time                   | tournat | Fast mode                               | 100                    |     |      | no   |

| SDA Setup Time                   | tsu;dat | Fast mode plus                          | 50                     |     |      | ns   |

|                                  |         | High speed mode                         | 10                     |     |      |      |

|                                  |         | Standard mode                           | 4                      |     |      |      |

| STOP Condition                   | touro   | Fast mode                               | 0.6                    |     |      |      |

| Setup Time                       | tsu;sto | Fast mode plus                          | 0.26                   |     |      | μS   |

|                                  |         | High speed mode                         | 0.16                   |     |      |      |

| Bus Free Time                    |         | Standard mode                           | 4.7                    |     |      | μs   |

| between Stop and                 | tBUF    | Fast mode                               | 1.3                    |     |      |      |

| Start                            |         | Fast mode plus                          | 0.5                    |     |      |      |

|                                  |         | Standard mode                           |                        |     | 1000 | ns   |

|                                  |         | Fast mode                               | 20                     |     | 300  | ns   |

| Rise Time of SDA                 |         | Fast mode plus                          |                        |     | 120  | ns   |

| and SCL Signals                  | tR      | High speed mode (SDA)<br>load 100pF max | 10                     |     | 80   | ns   |

|                                  |         | High speed mode (SCL)<br>load 100pF max | 10                     |     | 40   | ns   |

|                                  |         | Standard mode                           |                        |     | 300  |      |

|                                  |         | Fast mode                               | 20 x<br>(VDD/<br>5.5V) |     | 300  | ns   |

| Fall Time of SDA and SCL Signals | tF      | Fast mode plus                          | 20 x<br>(VDD/<br>5.5V) |     | 120  | ns   |

|                                  |         | High speed mode (SDA)<br>load 100pF max | 10                     | 1   | 80   | ns   |

|                                  |         | High speed mode (SCL)<br>load 100pF max | 10                     | -   | 40   | ns   |

| SDA Output Low Sink<br>Current   | lol_i2C | SDA voltage = 0.4V                      | 2                      |     |      | mA   |

### 15 Typical Application Circuit

Table 1. Recommended BOM

| Table 1. Necommended Bow |     |                      |                    |                               |             |

|--------------------------|-----|----------------------|--------------------|-------------------------------|-------------|

| Reference                | Qty | Part Number          | Description        | Package                       | Manufacture |

| U1                       | 1   | RT5801A              | DC-DC<br>Converter | WL-CSP-54B<br>2.69x3.92 (BSC) | Richtek     |

| 04 00 00 04              |     | GRM188D70J106MA73    | 40 F               | 0.0000                        | Murata      |

| C1, C2, C3, C4           | 4   | GRM188C81A106MA73    | 10μF               | C-0603                        |             |

| 05.00                    | 2   | GCM188R71C105KA64    | 1                  | C-0603                        | Murata      |

| C5, C6                   |     | GRM155C71C105KE11    | 1μF                | C-0402                        |             |

| 07.00.00                 |     | GRM188C80G226ME15    | 22. 5              | C-0603                        | Murata      |

| C7, C8, C9               | 8   | GRM188D70J226ME01    | 22μF               |                               |             |

| LA, LB, LC, LD           | 4   | DFE201610E-R24M      | 0.24μΗ             | 2016 -                        | Murata      |

|                          |     | TFM201610ALM-R24MTAA |                    |                               | TDK         |

| L (, LD, LO, LD          |     | HMMQ25201B-R22MSR-57 | 0.22μΗ             | 2520                          | Cyntec      |

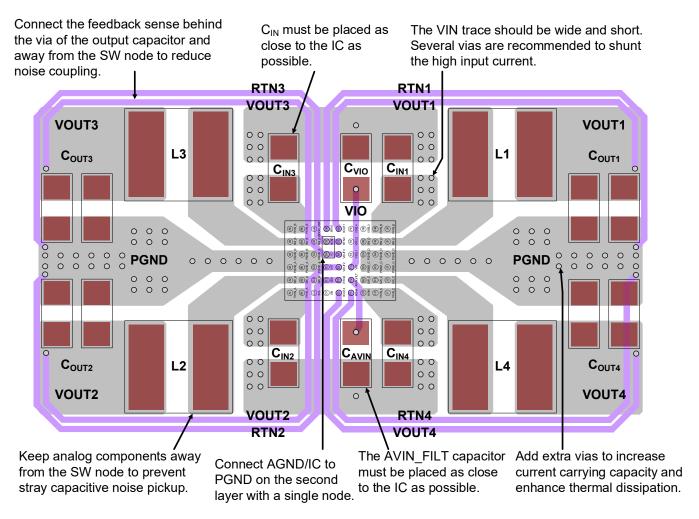

Note 8. All the input and output capacitors are the suggested values, referring to the effective capacitances, subject to any derating effect, like a DC bias. The effective values of capacitors C1 to C4 must be larger than 4μF, and capacitors C7 to C9 must be larger than 14μF.

Table 2. Recommended BOM

| Reference       | Qty | Part Number          | Description        | Package                       | Manufacture |

|-----------------|-----|----------------------|--------------------|-------------------------------|-------------|

| U1              | 1   | RT5801B              | DC-DC<br>Converter | WL-CSP-54B<br>2.69x3.92 (BSC) | Richtek     |

| C1 C2 C3 C4     | 4   | GRM188D70J106MA73    | 10. F              | C-0603                        | Murata      |

| C1, C2, C3, C4  | 4   | GRM188C81A106MA73    | 10μF               | C-0003                        |             |

| C5, C6          | 2   | GCM188R71C105KA64    | 1⊏                 | C-0603                        | Murata      |

| C5, C6          | 2   | GRM155C71C105KE11    | 1μF                | C-0402                        |             |

| C7 C9 C0 C10    | 0   | GRM188C80G226ME15    | 22⊏                | C-0603                        | Murata      |

| C7, C8, C9, C10 | 8   | GRM188D70J226ME01    | 22μF               |                               |             |

| LA, LB, LC, LD  | 4   | DFE201610E-R24M      | 0.24μΗ             | 2016                          | Murata      |

|                 |     | TFM201610ALM-R24MTAA |                    |                               | TDK         |

|                 |     | HMMQ25201B-R22MSR-57 | 0.22μΗ             | 2520                          | Cyntec      |

Note 9. All the input and output capacitors are the suggested values, referring to the effective capacitances, subject to any derating effect, like a DC bias. The effective values of capacitors C1 to C4 must be larger than  $4\mu F$ , and capacitors C7 to C9 must be larger than  $14\mu F$ .

Table 3. Recommended BOM

| Reference      | Qty | Part Number          | Description        | Package                       | Manufacture |

|----------------|-----|----------------------|--------------------|-------------------------------|-------------|

| U1             | 1   | RT5801C              | DC-DC<br>Converter | WL-CSP-54B<br>2.69x3.92 (BSC) | Richtek     |

| C1 C2 C2 C4    | 4   | GRM188D70J106MA73    | 10. F              | C-0603                        | Murata      |

| C1, C2, C3, C4 | 4   | GRM188C81A106MA73    | 10μF               |                               |             |

| C5, C6         | 2   | GCM188R71C105KA64    | 1⊏                 | C-0603                        | Murata      |

| C5, C6         | 2   | GRM155C71C105KE11    | 1μF                | C-0402                        |             |

| C7 C9          | 0   | GRM188C80G226ME15    | 22. 5              | C-0603                        | Murata      |

| C7, C8         | 8   | GRM188D70J226ME01    | 22μF               | C-0603                        |             |

|                | 4   | DFE201610E-R24M      | 0.24μΗ             | 2016                          | Murata      |

| LA, LB, LC, LD |     | TFM201610ALM-R24MTAA |                    |                               | TDK         |

|                |     | HMMQ25201B-R22MSR-57 | 0.22μH             | 2520                          | Cyntec      |

Note 10. All the input and output capacitors are the suggested values, referring to the effective capacitances, subject to any derating effect, like a DC bias. The effective values of capacitors C1 to C4 must be larger than  $4\mu F$ , and capacitors C7 to C9 must be larger than  $14\mu F$ .

eserved. RICHTEK

Table 4. Recommended BOM

| Reference      | Qty | Part Number          | Description        | Package                       | Manufacture |

|----------------|-----|----------------------|--------------------|-------------------------------|-------------|

| U1             | 1   | RT5801D              | DC-DC<br>Converter | WL-CSP-54B<br>2.69x3.92 (BSC) | Richtek     |

| C1 C2 C2 C4    | 4   | GRM188D70J106MA73    | 10. F              | 0.0000                        | Murata      |

| C1, C2, C3, C4 | 4   | GRM188C81A106MA73    | 10μF               | C-0603                        |             |

| C5, C6         | 2   | GCM188R71C105KA64    | 1⊏                 | C-0603                        | Murata      |

| C5, C6         | 2   | GRM155C71C105KE11    | 1μF                | C-0402                        |             |

| C7             | 0   | GRM188C80G226ME15    | 22. 5              | C-0603                        | Murata      |

| C7             | 8   | GRM188D70J226ME01    | 22μF               | C-0603                        |             |

| LA, LB, LC, LD | 4   | DFE201610E-R24M      | 0.24μΗ             | 2016 -                        | Murata      |

|                |     | TFM201610ALM-R24MTAA |                    |                               | TDK         |

|                |     | HMMQ25201B-R22MSR-57 | 0.22μΗ             | 2520                          | Cyntec      |

Note 11. All the input and output capacitors are the suggested values, referring to the effective capacitances, subject to any derating effect, like a DC bias. The effective values of capacitors C1 to C4 must be larger than  $4\mu F$ , and capacitors C7 to C9 must be larger than  $14\mu F$ .

Table 5. Recommended BOM

| Reference      | Qty | Part Number          | Description        | Package                       | Manufacture |

|----------------|-----|----------------------|--------------------|-------------------------------|-------------|

| U1             | 1   | RT5801E              | DC-DC<br>Converter | WL-CSP-54B<br>2.69x3.92 (BSC) | Richtek     |

| C1 C2 C2 C4    | 4   | GRM188D70J106MA73    | 10. F              | C-0603                        | Murata      |

| C1, C2, C3, C4 | 4   | GRM188C81A106MA73    | 10μF               |                               |             |

| C5, C6         | 2   | GCM188R71C105KA64    | 1μF                | C-0603                        | Murata      |

| C3, C0         | 2   | GRM155C71C105KE11    | ιμε                | C-0402                        |             |

| C7, C8         | 0   | GRM188C80G226ME15    | 22⊏                | C-0603                        | Murata      |

| C7, C8         | 8   | GRM188D70J226ME01    | 22μF               | C-0003                        |             |

|                | 4   | DFE201610E-R24M      | 0.24μΗ             | 2016                          | Murata      |

| LA, LB, LC, LD |     | TFM201610ALM-R24MTAA |                    |                               | TDK         |

|                |     | HMMQ25201B-R22MSR-57 | 0.22μH             | 2520                          | Cyntec      |

Note 12. All the input and output capacitors are the suggested values, referring to the effective capacitances, subject to any derating effect, like a DC bias. The effective values of capacitors C1 to C4 must be larger than  $4\mu F$ , and capacitors C7 to C9 must be larger than  $14\mu F$ .

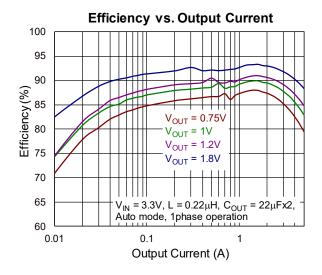

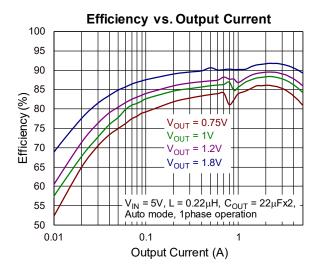

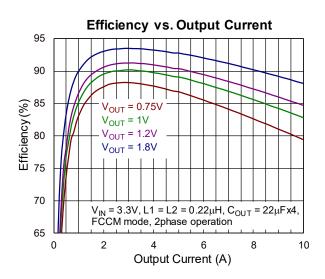

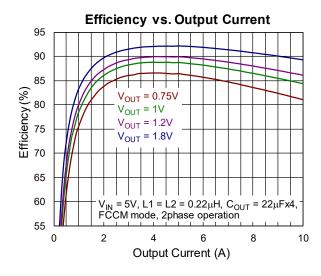

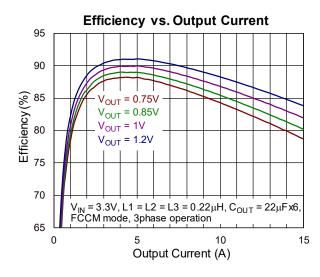

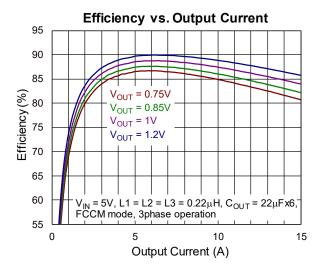

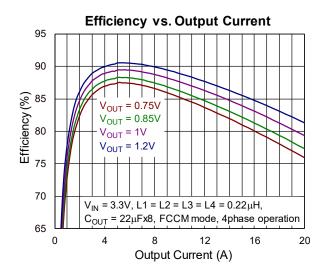

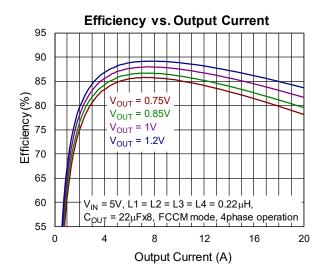

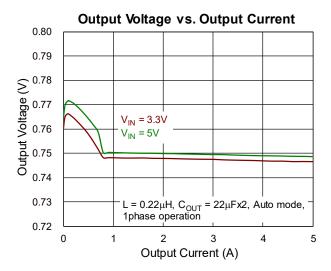

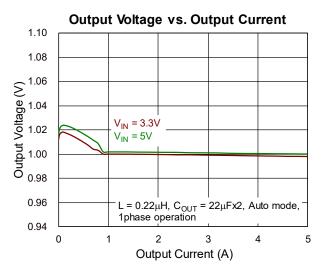

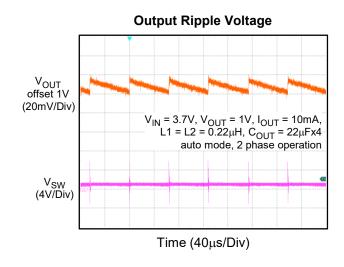

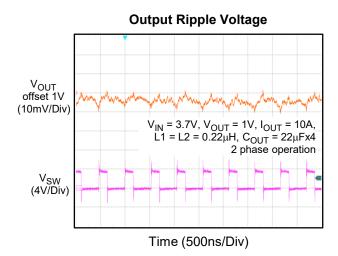

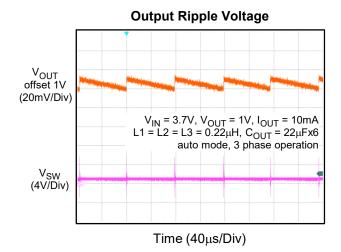

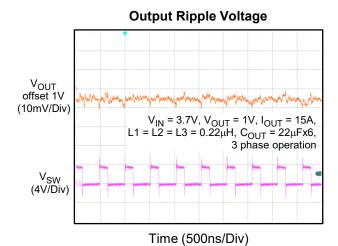

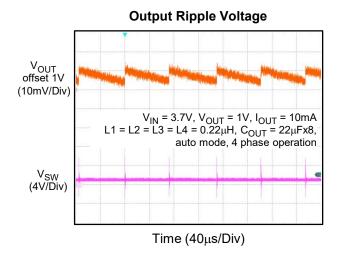

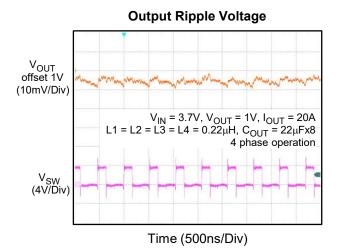

### 16 Typical Operating Characteristics

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

**RICHTEK** is a registered trademark of Richtek Technology Corporation.

RT5801\_DS-03 June 2025 www.richtek.com

www.richtek.com

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

**RICHTEK**

is a registered trademark of Richtek Technology Corporation.

### 17 Operation

The RT5801 series comprises power management ICs that integrate four high-efficiency buck converters. These series are factory configured as five different part options: RT5801A (2+1+1 phase), RT5801B (1+1+ 1+1 phase), RT5801C (3+1 phase), RT5801D (4-phase) and RT5801E (2+2 phase) converters. The converter is capable of providing up to 20A peak current with an output voltage range from 0.4V to 1.55V.

The RT5801 series utilizes the proprietary Advanced Constant On-Time (ACOT®) control architecture. The ultrafast ACOT® control enables the use of small ceramic capacitors (MLCC) to save the PCB size.

During normal operation, the internal high-side power switch (HSFET) is activated for a predetermined duration determined by a one-shot timer at the start of each clock cycle. When the HSFET is deactivated, the internal lowside power switch (LSFET) is activated. The output voltage is remotely sensed at the VOUT pin and the RTN pin to ensure high accuracy and is compared to an internal reference voltage. As a result, an error signal is obtained and internally compensated. The compensated error signal is then compared to an internal ramp signal. Once the minimum off-time one-shot has elapsed and the inductor current is below the current-limit threshold, the one-shot is triggered again if the internal ramp signal falls below the compensated error signal. The ACOT® control architecture is characterized by its ultrafast transient response. When there is a sudden increase in load, the output voltage rapidly drops, triggering a new on-time to increase the inductor current once again.

In multiphase operation, phase interleaving control is employed to minimize input and output ripple. This technique activates different phases in a cyclical fashion by applying a sequence of control pulses to the phase transistors. By doing so, the ripple in the input and output currents is reduced, resulting in improved performance and efficiency. Additionally, current balance control is utilized to ensure an equal distribution of stress on each phase. This control mechanism helps maintain balanced current flow among the different phases, preventing any phase from being overloaded or underutilized. The use of both phase interleaving control and current balance control enhances the overall performance and reliability of the multiphase system. The phase spacing of each switching stage in various multiphase configurations is as follows:

- In a 2-phase operation, the phases are spaced 180° apart.

- In a 3-phase operation, the phases are spaced 120° apart.

- In a 4-phase operation, the phases are spaced 90° apart.

The RT5801 series features a four-phase buck converter, which is divided into four groups as outlined below:

- Group 1:

- Power stage: PVIN\_D, SW\_D, PGND\_D;

- 2. Feedback and Control Pins: VOUT1, RTN1, and VSEL1;

- 3. I<sup>2</sup>C registers named Buck1: 0x14, 0x25[4], 0x33, 0x37, 0x3E~0x57.

- Group 2:

- 1. Power stage: PVIN A, SW A, PGND A;

- 2. Feedback and Control Pins: VOUT2, RTN2, and VSEL2;

- 3. I<sup>2</sup>C registers named Buck2: 0x15, 0x25[5], 0x34, 0x38, 0x5B~0x71.

- Group 3:

- 1. Power stage: PVIN\_B, SW\_B, PGND\_B;

- 2. Feedback and Control Pins: VOUT3, RTN3, and VSEL3;

- 3. I<sup>2</sup>C registers named Buck3: 0x16, 0x25[6], 0x35, 0x39, 0x75~0x8B.

- Group 4:

RT5801 DS-03

- Power stage: PVIN\_C, SW\_C, PGND\_C;

- 2. Feedback and Control Pins: VOUT4, RTN4, and VSEL4;

- 3. I<sup>2</sup>C registers named Buck4: 0x17, 0x25[7], 0x36, 0x3A, 0x8F~0xA5.

To ensure the proper operation of the converter, the circuit diagram is defined, and the control register is assigned based on the output configuration. When the RT5801 is configured for multiphase output, master and slave control is implemented. In the case where the selected group functions as a slave, the feedback pins (VOUTx and RTNx), VSELx pin, and the corresponding I<sup>2</sup>C control registers (Buckx) are not utilized and should be connected to GND.

For example, the RT5801C consists of two output channels. For Vout1, the output voltage is sensed from the output capacitor through VOUT1 and RTN1 pins, with the phase nodes employed being SW\_D (master), SW\_C, and SW\_B in the specified multiphase control order. The active control registers for this setup are Buck1. Similarly, for Vout2, the output voltage is sensed from the output capacitor through VOUT2 and RTN2 pins, with the employed phase node being SW\_A, and the active control registers being Buck2.

The output configuration setups based on the RT5801 part options are detailed in Table 6.

| Part No. | Output<br>Channel | Phase Sequence Assignment          | Output Voltage<br>Sense Pin | VSEL Pin<br>Control | Active Control<br>Registers |

|----------|-------------------|------------------------------------|-----------------------------|---------------------|-----------------------------|

|          | Vout1             | SW_D (master), SW_C                | VOUT1, RTN1                 | VSEL1               | Buck1                       |

| RT5801A  | Vout2             | SW_A                               | VOUT2, RTN2                 | VSEL2               | Buck2                       |

|          | Vоит3             | SW_B                               | VOUT3, RTN3                 | VSEL3               | Buck3                       |

|          | Vout1             | SW_D                               | VOUT1, RTN1                 | VSEL1               | Buck1                       |

| RT5801B  | Vout2             | SW_A                               | VOUT2, RTN2                 | VSEL2               | Buck2                       |

| KISOUID  | Vout3             | SW_B                               | VOUT3, RTN3                 | VSEL3               | Buck3                       |

|          | Vout4             | SW_C                               | VOUT4, RTN4                 | VSEL4               | Buck4                       |

| DT50040  | Vout1             | SW_D (master), SW_C, SW_B          | VOUT1, RTN1                 | VSEL1               | Buck1                       |

| RT5801C  | Vout2             | SW_A                               | VOUT2, RTN2                 | VSEL2               | Buck2                       |

| RT5801D  | Vout1             | SW_D (master), SW_C, SW_B,<br>SW_A | VOUT1, RTN1                 | VSEL1               | Buck1                       |

| DT5001E  | Vout1             | SW_D (master), SW_C                | VOUT1, RTN1                 | VSEL1               | Buck1                       |

| RT5801E  | Vout2             | SW_A (master), SW_B                | VOUT2, RTN2                 | VSEL2               | Buck2                       |

**Table 6. Output Configuration Setup**

### 17.1 UVLO, Enable Control, and Soft-Start Function

The RT5801 series implements undervoltage-lockout protection (UVLO) to prevent operation without fully turning on the internal HSFET and LSFET. The UVLO monitors the voltage of AVIN. When the AVIN voltage is lower than the UVLO threshold, the IC stops switching and resets all digital functions.

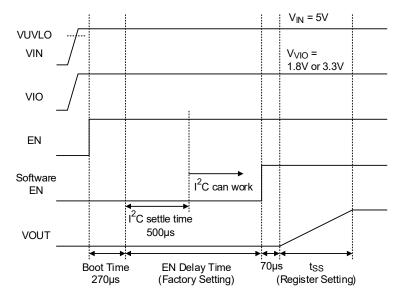

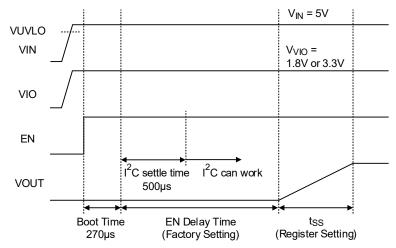

The RT5801 series provides an EN pin, as an external chip enable control, to enable or disable the device. If VEN is held below a logic-low threshold voltage (VENL) of the enable input (EN), the converter will enter shutdown mode and reset all digital functions ( $I^2C$ ). Then the converter is disabled even if the VIN voltage is above the VIN undervoltage-lockout threshold (VUVLO). During shutdown mode, the supply current can be reduced to ISHDN ( $I_0\mu$ A or below). If the EN voltage rises above the logic-high threshold voltage (VENH), the device starts switching. When appropriate voltages are present on the VIN, AVIN, VIO, and EN pins, the RT5801 series will begin digital functions, switching, and initiate a soft-start ramp of the output voltage. The boot time for the device to implement soft-start approximately  $270\mu$ s (typical) when both the input voltage and EN voltage are above UVLO and EN rising threshold. After the device completes the boot process, it takes  $500\mu$ s (typical) for the I²C interface circuit to settle. It is advisable to enable the device only after the VIO voltage has stabilized, as the VIO voltage serves as the power supply for digital functions. The RT5801 series supports enable/shutdown delay time setting (factory setting, default = 0ms) and soft-start slew

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

27

rate setting. The soft-start function is used to prevent large inrush current while the converter is powered up. The soft-start time of each buck is programmable through registers 0x55[5:4], 0x6F[5:4], 0x89[5:4], and 0xA3[5:4].

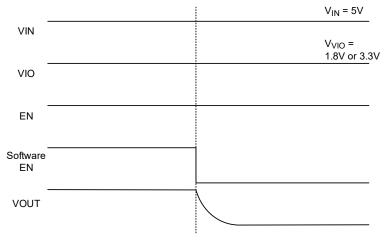

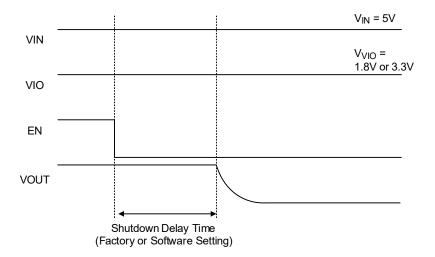

Figure 1 and Figure 2 show the start-up and power-off sequences with enable control by software EN. The output voltage is disabled or enabled by setting the following registers: 0x49[0] and 0x4B[0] (Buck1), 0x63[0] and 0x65[0] (Buck2), 0x7D[0] and 0x7F[0] (Buck3), 0x97[0] and 0x99[0] (Buck4). The RT5801 series also implements enable control by the external EN pin with enable and shutdown delay time. Note that the enable delay time is a factory setting only, and the default value of Buck1 to Buck4 can be read from the following registers: 0x56[5:0], 0x70[5:0], 0x8A[5:0], and 0xA4[5:0]. The shutdown delay time can be either factory programmed or set by software, and the default value of Buck1 to Buck4 can be read from the following registers: 0x57[5:0], 0x71[5:0], 0x8B[5:0], and 0xA5[5:0]. The start-up and power-off sequences by the external EN pin are shown in Figure 3 and Figure 4.

Figure 1. Start-Up Sequence by Software EN

Figure 2. Power-Off Sequence by Software EN

28

Figure 3. Start-Up Sequence by External EN Pin

Figure 4. Power-Off Sequence by External EN Pin

#### 17.2 Dynamic Voltage Scaling (DVS)

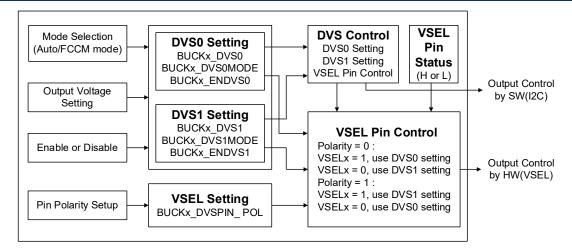

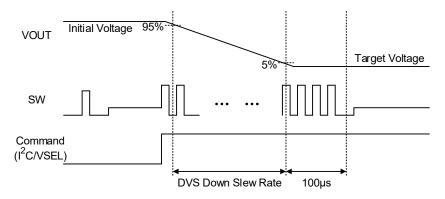

The RT5801 series offers a wide output voltage range with 8-bit resolution, and each buck converter features two independently programmable voltage settings known as DVS0 and DVS1. Taking Buck1 as an example, register 0x48[7:0] is utilized to set the voltage of DVS0, while 0x4A[7:0] is used to set the voltage of DVS1. There are two methods for selecting the DVS. In the first method, the selection can be changed via software using register 0x52[1:0]. DVS0 can be controlled by setting 0x52[1:0] = 00, and DVS1 can be controlled by setting 0x52[1:0] = 01. In the second method, the selection of the DVS can be controlled by an external hardware pin when setting 0x52[1:0] = 10. The VSEL pin plays this role, and its polarity is defined by 0x52[2]. When setting 0x52[2] = 0, pulling VSEL high uses DVS0, and pulling VSEL low uses DVS1. Conversely, when setting 0x52[2] = 1, pulling VSEL high uses DVS1, and pulling VSEL low uses DVS0. The output setting diagram is shown in Figure 5.

Figure 5. Output Setting Diagram

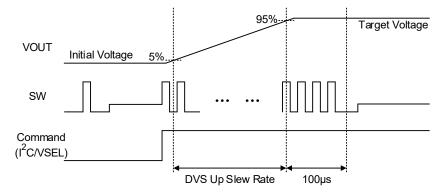

The RT5801 series also supports DVS speed configuration, regardless of the slew rate of voltage changes within the same DVSx or between DVS0 and DVS1. For example, in Buck1, when the output voltage is set from low to high or high to low, register 0x54[6:4] defines the slew rate of DVS up, while 0x54[2:0] is used to define the slew rate of DVS down. To achieve better performance during voltage changes operations, the master/slave enters PWM operation and maintains it for 100µs after the voltage achieves the target, even if the IC is set to Auto mode. Besides, set the output voltage down to the target voltage within 123% of the internal reference voltage to avoid OVP triggered when DVS down with decay mode. Figure 6 and Figure 7 show the DVS up and down operations.

Figure 6. DVS Up Operation

Figure 7. DVS Down Operation

#### 17.3 MODE Selection

The operation modes, whether DVS0 or DVS1, encompass two distinct configurations: forced continuous conduction mode (FCCM) and automatic power-saving mode (Auto mode). These modes are configured using specific registers as follows: 0x49[5] and 0x4B[5] for Buck1, 0x63[5] and 0x65[5] for Buck2, 0x7D[5] and 0x7F[5] for Buck3, and 0x97[5] and 0x99[5] for Buck4. For example, to set Buck1 to FCCM, a value of '1' should be written at 0x49[5].

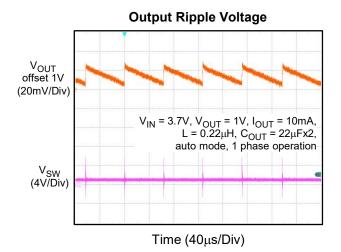

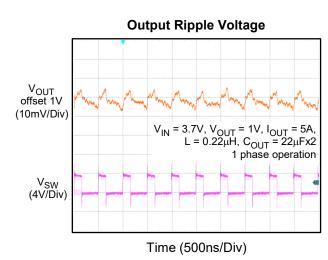

When Auto mode operation is selected, the RT5801 series automatically adjusts the switching frequency at light-load conditions to maintain high efficiency. This is achieved by enabling the internal zero current detection circuitry to sense the inductor current using the LSFET RDS(ON). As the inductor current decreases to zero and becomes negative, both HSFET and LSFET are turned off, and the output capacitor supplies the load current until the feedback voltage falls below the internal reference voltage. Moreover, the switching frequency increases to 2MHz/2.2MHz as the inductor current reaches the continuous conduction condition.

By setting the MODE to FCCM operation, the internal zero current detection circuitry is disabled, and full phase switching is enforced. This ensures that the switching frequency remains relatively constant to meet stringent voltage regulation accuracy requirements.

### 17.4 Automatically Phase Adding/Shedding

In a multiphase converter, the phase adding/shedding function is designed to optimize power efficiency based on the output current. The RT5801 series, which features a multiphase configuration, automatically increases the number of operating phases as the output current rises by setting the MODE to Auto mode operation. The phase interleaving function is automatically fine-tuned to correspond with the active phase count, scaling with the output current. For example, in the RT5801C (3-phase), an additional phase is seamlessly integrated and interleaved at 180-degree intervals when the load current exceeds the phase adding level from 1-phase to 2-phase. Conversely, when the load current drops below the phase shedding level from 2-phase to 1-phase, the device autonomously reduces the number of operating phases.

#### 17.5 Power-Good Indication

The RT5801 series provides a power-good indication to show the output voltage status. When the output voltage is between 110% and 90% of the set voltage, the PG indication bit changes to '1'. The relative registers are 0x14[7], 0x15[7], 0x16[7], and 0x17[7].

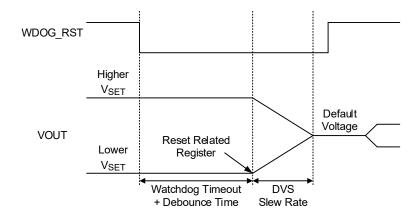

#### 17.6 Watchdog Function

The RT5801 series implements a watchdog function that resets the output voltage, DVSx, and ENDVSx registers to the factory default setting value. Register 0x25 can enable or disable watchdog function and provide watchdog timeout for selection. The minimum watchdog debounce time is 100µs when 0x25[2:0] is set to 000. The operation of the watchdog reset is shown in <u>Figure 8</u>. <u>Table 7</u> shows the registers that will be reset when the WDOG\_RST pin is pulled low. The I<sup>2</sup>C command needs to be given after the WDOG\_RST pin is pulled high.

Figure 8. Watchdog Reset Operation

Table 7. Watchdog Reset Register

| BUCK1_WDT | BUCK2_WDT | BUCK3_WDT | BUCK4_WDT |

|-----------|-----------|-----------|-----------|

| 0x48      | 0x62      | 0x7C      | 0x96      |

| 0x49[0]   | 0x63[0]   | 0x7D[0]   | 0x97[0]   |

| 0x4A      | 0x64      | 0x7E      | 0x98      |

| 0x4B[0]   | 0x65[0]   | 0x7F[0]   | 0x99[0]   |

| 0x52      | 0x6C      | 0x86      | 0xA0      |

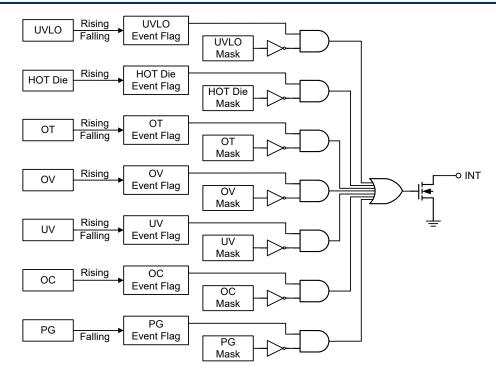

#### 17.7 Fault Detection and Interrupt Pin

The RT5801 series implements an interrupt function to alert the host when warning or fault events have occurred. The warning events are VIN UVLO and Hot Die, and the fault events are conditions such as overvoltage, undervoltage, overcurrent, and over-temperature. Registers 0x13, 0x14, 0x15, 0x16, and 0x17 can help the host to determine if a fault or warning event has occurred. These registers will be cleared when read. Moreover, the device provides an INT pin with open-drain output capability (default factory setting) to show these events using an active-low signal. The pull-high voltage of the INT pin will be the same as the VIO voltage. The RT5801 series also supports a mask function to either mask or pass the internal event flag output to the external INT pin using 0x32, 0x33, 0x34, 0x35, and 0x36 registers. The overall detection function is shown in Figure 9.

Figure 9. Overall Detection Function

#### 17.8 Current-Limit Protection

The RT5801 series features cycle-by-cycle current-limit protection on both the HSFET and LSFET to prevent the device from catastrophic damage in the event of an output short-circuit, overcurrent, or inductor saturation conditions.

The HSFET current-limit protection is achieved by an internal current comparator that monitors the inductor current during each on-time. The inductor current is compared with the HSFET current limit (I<sub>LIM\_H</sub>) after a certain amount of delay time when the HSFET is turned on in each cycle. If the peak inductor current rises above the HSFET current limit (I<sub>LIM\_H</sub>), the converter will immediately turn off the HSFET and turn on the LSFET to prevent the inductor current from exceeding the HSFET current limit.

The LSFET current-limit protection is achieved by measuring the inductor current during LSFET on-time. Once inductor current rises above the LSFET current limit (ILIM\_L), the on-time one-shot will be inhibited, and the next on-time will only be triggered when the inductor current falls below the LSFET current limit (ILIM\_L). If the output load current exceeds the available inductor current (clamped by the LSFET current limit), the output capacitor will need to supply the extra current, so that the output voltage will begin to drop. If it drops below the output undervoltage protection trip threshold, the IC will stop switching to avoid excessive heating.

### 17.9 Output Undervoltage Protection