# 36V Buck Controller with I<sup>2</sup>C Interface for USB-PD

# **General Description**

The RT6191A is a Buck controller designed for USB power delivery (USB PD). It operates with wide input voltage range from 4.5V to 36V, and the output voltage is programmable from 3V to 36V. The RT6191A implements peak current mode control mechanism with the programmable constant voltage (CV) and constant current (CC) output to support USB-PD 3.0 SPR mode and 28V of USB-PD 3.1 EPR mode. It also has built-in charge pumps for driving external low-cost N-MOSFETs to control the power path. With an I<sup>2</sup>C compatible interface, the RT6191A supports many programmable functions including CV/CC output, switching frequency, and cable voltage drop compensation. Moreover, the RT6191A integrates full protections including input UVLO, over/under-voltage protection, cycle-by-cycle current limit, short protection, and over-temperature protection. The RT6191A is available in a WQFN-40L 5x5 package.

# **Applications**

- Monitor

- USB Power Delivery

- Power Bank

## **Features**

- Support USB-PD 3.0 SPR Mode and 28V of USB-PD 3.1 EPR Mode

- Integrated Buck Controller:

- ▶ Wide Input Voltage Range: 4.5V to 36V

- ▶ Wide Output Voltage Range: 3V to 36V

- ► Peak Current Mode Control

- Programmable Switching Frequency (250kHz to 1MHz)

- ► Power Saving Mode Enables Higher Light Load Efficiency

- AnyPower<sup>TM</sup> for Constant Voltage (12.5mV/step, Typ.) and Constant Current (in 9-Bit Resolution) Output Settings

- Embedded 2nd OCP Function

- Bypass Mode

- I<sup>2</sup>C Compatible Interface

- Adjustable Soft-Start Time

- Programmable Cable Voltage Drop Compensation

- Built-in Bleeders for Quick VBUS Discharge

- Power Good Indicator

- Full Protection with UVLO, OVP, UVP, OCP, Cycleby-Cycle Current Limit and OTP

- WQFN-40L 5x5 Package

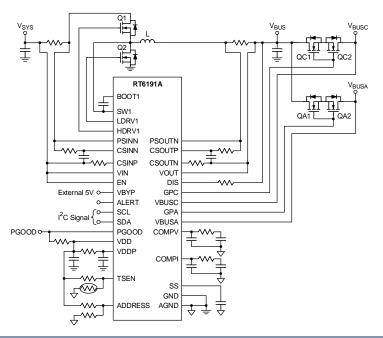

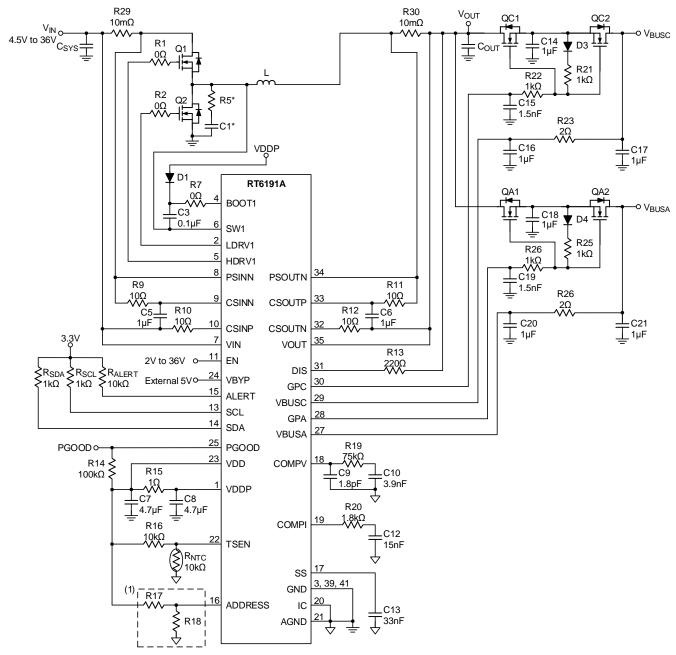

# **Simplified Application Circuit**

Copyright © 2022 Richtek Technology Corporation. All rights reserved.

RICHTEK

is a registered trademark of Richtek Technology Corporation.

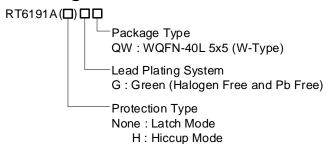

# **Ordering Information**

#### Note:

### Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

# **Marking Information**

RT6191AGQW: Product Code YMDNN: Date Code

#### RT6191AHGQW

RT6191AHGQW: Product Code YMDNN: Date Code

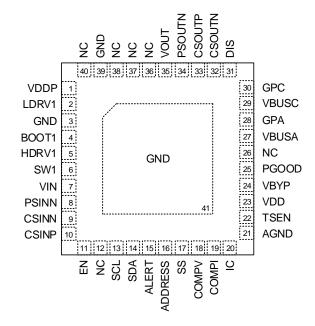

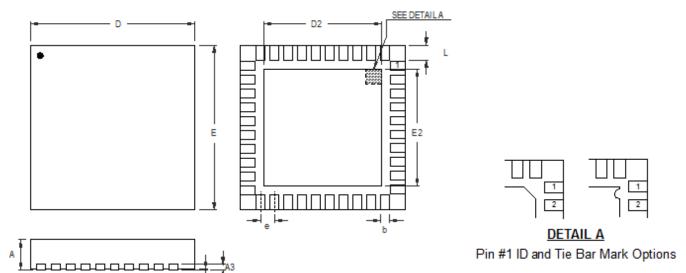

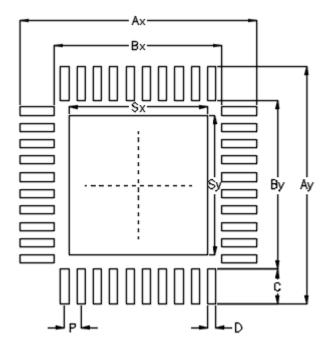

# **Pin Configuration**

(TOP VIEW)

WQFN-40L 5x5

DS6191A-00 December 2022

# **Functional Pin Description**

| Pin No.                    | Pin Name | Pin Function                                                                                                                                                                                                    |

|----------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                          | VDDP     | Bias voltage input pin for internal gate drivers. It is recommended to connect an external 4.7 $\mu\text{F}$ capacitor from this pin to GND.                                                                    |

| 2                          | LDRV1    | Buck mode low-side gate driver output for Q2. Connect to gate of low-side N-MOSFET Q2.                                                                                                                          |

| 3, 39,<br>41 (Exposed Pad) | GND      | Ground. Exposed pad. The exposed pad must be soldered to a large PCB copper area for maximum power dissipation.                                                                                                 |

| 4                          | BOOT1    | Buck mode bootstrap supply for high-side N-MOSFET Q1. It is recommended to connect a $0.1\mu F$ capacitor from this pin to SW1 pin. The bootstrap diode is integrated internally between VDDP pin and this pin. |

| 5                          | HDRV1    | Buck mode high-side gate driver output for Q1. Connect to gate of high-side N-MOSFET Q1.                                                                                                                        |

| 6                          | SW1      | Buck mode switch node. Connect to power inductor.                                                                                                                                                               |

| 7                          | VIN      | Supply voltage input. Input peak current sense positive input. Connect to the current sense resistor R29 for input peak current sense.                                                                          |

| 8                          | PSINN    | Input peak current sense negative input. Connect to the current sense resistor R29 for input peak current sense.                                                                                                |

| 9                          | CSINN    | Current sense negative input for input constant current control. Connect to the current sense resistor R29 directly. It is recommended to use $10m\Omega$ for the current sense resistor R29.                   |

| 10                         | CSINP    | Current sense positive input for input constant current control. Connect to the current sense resistor R29 directly. It is recommended to use $10m\Omega$ for the current sense resistor R29.                   |

| 11                         | EN       | Enable control input. A logic-high enables the converter; a logic-low forces the device into shutdown mode. "Do Not" leave this pin floating.                                                                   |

| 12, 26, 36, 37,<br>38, 40  | NC       | No internal connection. Please keep these pins floating.                                                                                                                                                        |

| 13                         | SCL      | Clock input for $I^2C$ interface. Connect this pin to AGND if $I^2C$ interface is not used. "Do Not" leave this pin floating.                                                                                   |

| 14                         | SDA      | Data line for $I^2C$ interface. Connect this pin to AGND if $I^2C$ interface is not used. "Do Not" leave this pin floating.                                                                                     |

| 15                         | ALERT    | Active low open-drain output. Connect this pin to 1.8V or 3.3V for normal operation. It will be pulled low if this chip is under the conditions of protection, EN shutdown, or after the end of soft-start.     |

| 16                         | ADDRESS  | I <sup>2</sup> C slave address selection pin. Connect this pin to VDD to select 0x2D, and connect this pin to AGND to select 0x2C.                                                                              |

| 17                         | ss       | Soft-start time control pin. Connect a capacitor between this pin and AGND to set the soft-start time.                                                                                                          |

| 18                         | COMPV    | Constant voltage (CV) loop compensation. Connect an external RC network from this pin to AGND for CV loop compensation. "Do Not" leave this pin floating.                                                       |

| 19                         | СОМРІ    | Constant current (CC) loop compensation. Connect an external RC network from this pin to AGND for CC loop compensation. "Do Not" leave this pin floating.                                                       |

Copyright © 2022 Richtek Technology Corporation. All rights reserved.

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                                                           |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20      | IC       | Internal connection. Connect this pin to AGND.                                                                                                                                                                                         |

| 21      | AGND     | Analog ground.                                                                                                                                                                                                                         |

| 22      | TSEN     | Thermal sense input. This pin is used for external over-temperature protection via an external NTC network circuit. Connect this pin to VDD if thermal sense function is not used. "Do Not" leave this pin floating.                   |

| 23      | VDD      | Internal LDO output. It is recommended to connect an external $4.7\mu F$ capacitor from this pin to GND. This pin is also used for internal analog circuit.                                                                            |

| 24      | VBYP     | Optional supply input from external 5V. Connect to external 5V voltage for VDD to increase converter efficiency.                                                                                                                       |

| 25      | PGOOD    | Power good indicator open-drain output. This pin is pulled high when the output voltage is within the target range. It will be pulled to ground if this chip is under the conditions of protection, EN shutdown, or during soft-start. |

| 27      | VBUSA    | Voltage sense input for monitoring VBUSA OVP and UVP.                                                                                                                                                                                  |

| 28      | GPA      | Charge-pump gate driver output for VBUSA. This pin drives external power N-MOSFETs to turn on or off the power path between Vout and VVBUSA.                                                                                           |

| 29      | VBUSC    | Voltage sense input for monitoring VBUSC OVP and UVP.                                                                                                                                                                                  |

| 30      | GPC      | Charge-pump gate driver output for VBUSC. This pin drives external power N-MOSFETs to turn on or off the power path between Vout and Vvbusc.                                                                                           |

| 31      | DIS      | Input pin for output discharge. Connect an external resistor between this pin and converter output to discharge energy of output capacitors through internal pull-low N-MOSFET.                                                        |

| 32      | CSOUTN   | Current sense negative input for output constant current control. Connect to the current sense resistor R30 directly. It is recommended to use $10m\Omega$ for the current sense resistor R30.                                         |

| 33      | CSOUTP   | Current sense positive input for output constant current control. Connect to the current sense resistor R30 directly. It is recommended to use $10m\Omega$ for the current sense resistor R30.                                         |

| 34      | PSOUTN   | Voltage sense input for internal constant current control loop.                                                                                                                                                                        |

| 35      | VOUT     | Voltage sense input for monitoring VOUT OVP and UVP.                                                                                                                                                                                   |

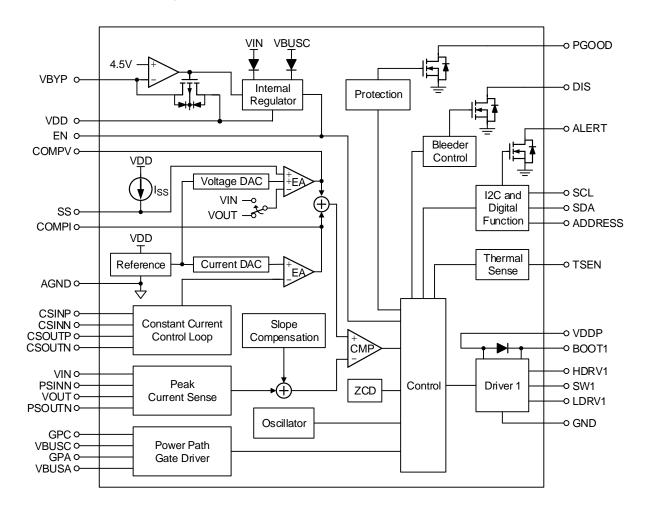

# **Functional Block Diagram**

# **Operation**

The RT6191A is a Buck controller to support USB-PD 3.0 SPR mode and 28V of USB-PD 3.1 EPR mode. The input voltage range is from 4.5V to 36V, and the output range is from 3V to 36V. The RT6191A utilizes peak current mode control to obtain fixed switching frequency from 250kHz to 1MHz. This control topology is also used for constant voltage (AnyVolt<sup>TM</sup>) regulation and constant current (AnyCurrent<sup>TM</sup>) regulation. The RT6191A also provides DVS function to set the output voltage dynamically with different rising and falling slew rates. By status change detecting function, the host can quickly and easily understand what types of warning or fault events occur from the external ALERT pin of RT6191A.

The RT6191A integrates an internal gate driver to control external power path MOSFETs for USB-C and USB-A (1C1A) VBUS terminals when Vout = 5V. The RT6191A also provides the flexibility for using N-MOSFETs or P-MOSFETs as external power path MOSFETs. With the cable voltage drop compensation function, the output voltage can be adjusted in heavy load condition for different equivalent series resistance (ESR) of USB cables.

The RT6191A implements full protections including input under-voltage lockout (UVLO), input and output over/under-voltage protection (OVP/UVP), output overcurrent protection (OCP), input cycle-by-cycle peak/average current limit and OTP. It is recommended to use  $10m\Omega/1206$  with 1W power dissipation as current sense resister for over-current condition.

#### **UVLO, Enable Control and Soft-Start**

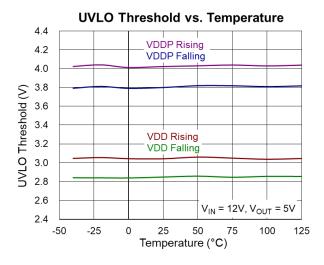

The RT6191A implements under-voltage lockout (UVLO) protection to prevent insufficient input voltage by monitoring VIN, VDD and VDDP pins. When the input voltage of these pins are lower than UVLO threshold, the IC stops switching and resets all digital functions.

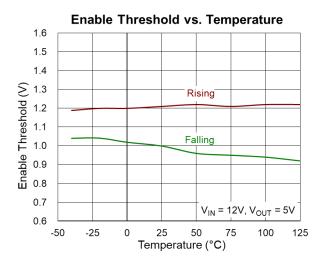

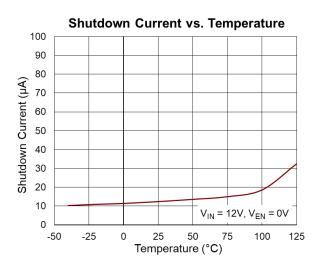

The RT6191A provides an EN pin to enable or disable the device externally. When EN pin voltage falls below a logic-low threshold voltage (VENL), the RT6191A will enter to shutdown mode and reset all digital functions even if the input voltage of relative pins are above each

UVLO threshold (VuyLo). In shutdown mode, the supply current can be reduced to ISHDN (typically 15µA). Once the EN pin voltage rises above a logic-high threshold voltage (VENH) and VIN is higher than its UVLO threshold, the VDD pin voltage will be regulated at 5V for internal digital circuits and VDDP for internal MOSFET gate drivers. After VDD and VDDP are higher than UVLO threshold voltage, the VOUT starts to ramp up with 50µs (typ.) delay time. In addition, EN pin can be connected to VIN pin directly to save power rail of system for normal operation.

The RT6191A provides adjustable soft-start function by connecting a capacitor from SS pin to AGND to prevent large inrush current during start-up. The soft-start time can be calculated by the equation below:

$$t_{SS}(ms) = \frac{C_{SS}(nF) \times 0.9V}{I_{SS}(\mu A)}$$

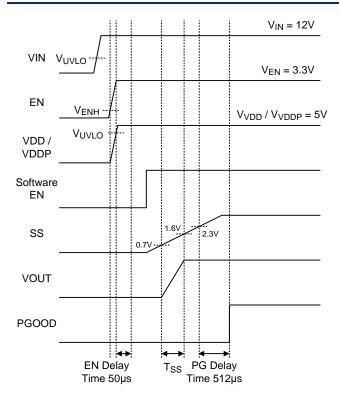

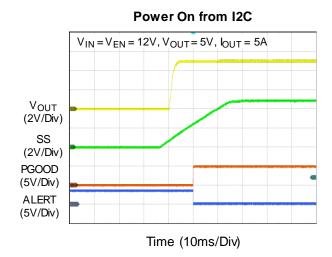

Figure 1 shows the start-up sequence with enable control by software. When VIN is above UVLO threshold voltage and EN is higher than a logic-high threshold voltage, the internal digital circuit will be enabled after VDD and VDDP rise above each UVLO threshold. If software EN (0x0E[7]) changes to "1", the VOUT starts to ramp up when SS voltage is higher than 0.7V. After SS voltage reaches to 2.3V, PGOOD will change to high level with 512µs (typ.) delay time.

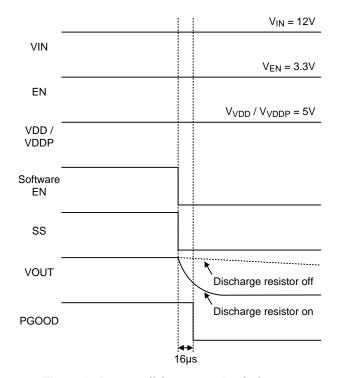

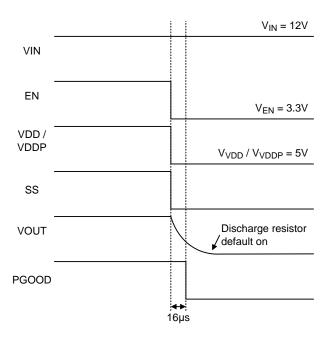

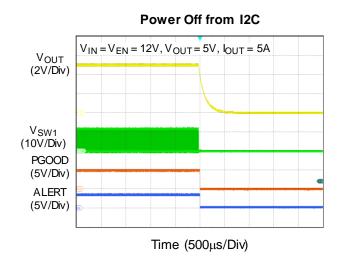

For power-off condition, RT6191A can be disabled by internal software EN (0x0E[7]) and external EN pin. When RT6191A is disabled by software, the discharge resistor can be controlled to be on or off by register 0x0E[4]. Once the RT6191A is disabled by external EN pin, the output voltage will ramp down with default discharge resistor on. In both software and hardware disabled operation, PGOOD will go low after 16µs (typ.) delay time after SS pin voltage is pulled low by the internal discharging current. The power-off sequence is shown in Figure 2 and Figure 3.

Figure 1. Start-up Sequence by Software

Figure 2. Power-off Sequence by Software

Figure 3. Power-off Sequence by External EN Pin

### **Dynamic Voltage Scaling (DVS)**

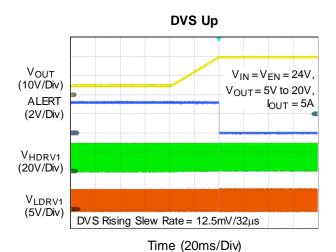

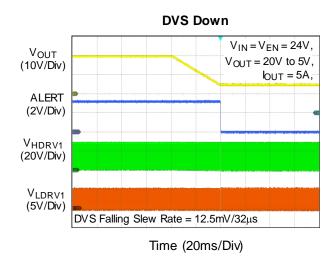

The RT6191A provides DVS function with wide voltage range for setting output voltage dynamically. Based on the voltage ratio setting of register 0x11[5], the output voltage can be set with different resolution by using register 0x01 and 0x02. The RT6191A also supports DVS rising and falling slew rate selection by using register 0x0D[6:3], the default factory setting of 0x0D[6:3] is "1111" for DVS rising and falling slew rate =  $\Delta$ VOUT / 32 $\mu$ s.

The ALERT\_PG bit, 0x1F[6], will change to "1" when the output voltage reaches to the target voltage, and then the external ALERT pin will go low immediately. The RT6191A also supports Mask function by register 0x21[6] to make the external ALERT pin not go low after DVS operation end. In addition, register 0x37[2] and 0x38[2] shows 275ms timeout indication if output voltage do not reach to target level within 275ms, and this mechanism also has Mask function by register 0x39[2].

# AnyVolt<sup>TM</sup> Constant Voltage (CV) Regulation

The RT6191A utilizes peak current mode control topology as main control loop for output constant voltage (CV) regulation. The output voltage is used to compare with the internal reference voltage to obtain an error signal by sensing VOUT pin voltage. This error

Copyright © 2022 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

signal is externally compensated on COMPV pin to compare with the inductor current sensed on the output current sense resistor. As the signal relative inductor current falls below the compensated error signal, the HDRV1 will be turned on with a time interval to make inductor current ramp up. As the inductor current reaches to peak current threshold (0x09[5:0]), the HDRV1 is turned off and LDRV1 will be turned on until an internal oscillator initializes next switching cycle.

# AnyCurrent<sup>TM</sup> Constant Current (CC) Regulation

The RT6191A also implements average current control loop by sensing the voltage across output current sense resistor R30 for output constant current (CC) regulation. The voltage across output current sense resistor is used to compare with the output CC level as register 0x03/0x04 to obtain an error signal, and then this error signal is externally compensated on COMPI pin. When the voltage across output current sense resistor is higher than output CC level, the COMPI pin voltage will fall below COMPV pin voltage to limit and keep the output current as output CC level. As the output current becomes higher than output CC level, RT6191A will limit the output current, and then the output voltage will be lower than regulation point until UVP happens. In addition, it is recommended to use  $10m\Omega/1206$  with 1W power dissipation as current sense resister for correct operation.

#### **Bypass Mode**

RT6191A implements a Bypass mode operation to enhance system efficiency when the output voltage becomes very close to the input voltage. After setting the output voltage to be at least 0.3V higher than the input voltage, the RT6191A will enter the Bypass mode immediately, then external N-MOSFET Q1 is fully turned on and Q2 is fully turned off. In Bypass mode, the external ALERT pin can also be asserted if any status is changed or protection is triggered. When the output voltage is lower than the input voltage, the RT6191A will return to Buck mode automatically to maintain normal output voltage regulation. Therefore, the RT6191A is more flexible for system firmware design by operation mode transition between Buck and Bypass modes without setting any register through I<sup>2</sup>C

#### **Mode Selection**

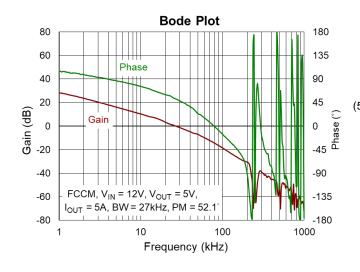

The RT6191A provides operation mode selection for light load Power Saving Mode (PSM) and Forced-CCM Mode (FCCM) by using register 0x0D[7]. The default factory setting of operation mode is light load PSM.

## **Power Saving Mode**

When 0x0D[7] = 0, RT6191A operates in PSM and automatically reduces switching frequency at light-load conditions to maintain high efficiency. The internal zero current detection (ZCD) circuitry will be enabled to sense the inductor current by utilizing RDS(ON) of the Q2 N-MOSFET in typical application circuit. As the inductor current drops to zero and becomes negative, both HDRV1 and LDRV1 are turned off with the output capacitor supplying the load current until the output voltage falls below the internal reference voltage. In reverse, when the output current increases from light load to heavy load, the switching frequency will increase to 250kHz (default factory setting) as the inductor current reaches the continuous conduction condition.

#### **FCCM Mode**

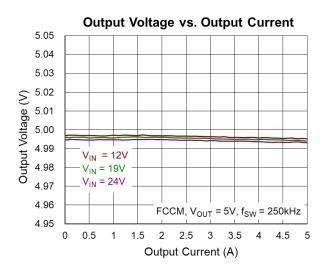

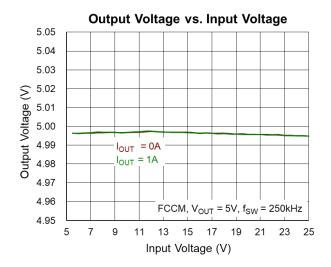

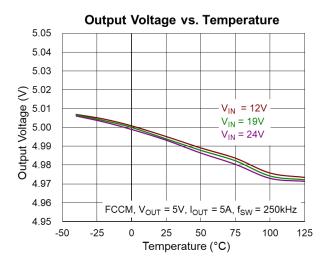

When 0x0D[7] = 1, the internal ZCD circuitry is disabled and the RT6191A operates in FCCM with typically 250kHz (default factory setting) at any load condition. This mode trades off reduced light load efficiency for low output voltage ripple, tight output voltage regulation, and constant switching frequency.

#### **ADC Reporting**

The RT6191A provides ADC function to report input/output voltage and current, VBUSC voltage and TSEN pin voltage by utilizing register 0x12 to 0x1B and 0x33 to 0x34 with 11-bit resolution. Register 0x10[1] and 0x32[1] are the enable control bits for ADC function, and 0x10[7:6] is the average times of ADC function. The default factory setting of 0x10 is 82h and 0x32 is 00h for ADC function default enable with average 8 times except VBUSC voltage reporting. Please see the I2C register map for detailed description of register 0x12 to 0x1B.

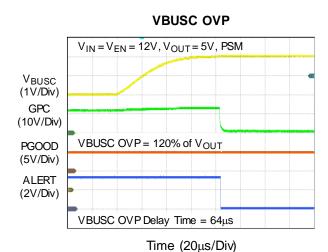

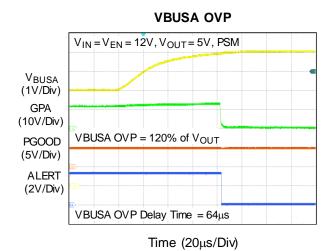

#### **Power Path Control**

The RT6191A integrates an internal gate driver to control external power path MOSFETs for USB-C and USB-A (1C1A) VBUS terminals when VBUS = 5V. The GPC/VBUSC pins are used for USB-C terminal, and GPA/VBUSA pins are used for USB-A terminal. Register 0x29[3:2] selects the external MOSFETs type of N-MOSFETs and P-MOSFETs for USB-C and USB-A terminals, and register 0x29[1:0] are the enable control bit for each power path MOSFETs. All power path MOSFETs will be turned off when protection happens with the default factory setting of register 0x29[7:4], and it can be set after internal digital circuit enabled for different applications. In addition, the default factory setting of register 0x29[1:0] is 00 for power path function not used.

### **Cable Voltage Drop Compensation**

The RT6191A implements cable voltage drop compensation to adjust the output voltage in heavy load condition for different equivalent series resistance (ESR) of USB cables. Register 0x0E[2:0] can set different compensation, and the default factory setting of 0x0E[2:0] is 000 for cable voltage drop compensation function default disabled. Besides, this function is inactive when RT6191A operates in Bypass mode.

## **Power Good Indication**

The RT6191A provides a power good indication with open-drain output capability to show the output voltage status. When output voltage is between 90% and 120% (typically OVP trip threshold of default factory setting) of reference voltage, the external PGOOD pin keeps as high level and internal PGOOD bit changes to "1" in register 0x1D[6] and 0x1F[6]. Register 0x1F[6] also shows the output voltage status for DVS operation, 0x1F[6] will change to "1" if the output voltage reaches to the target voltage whether in DVS up or down operation.

#### **External Thermal Sense**

The RT6191A provides an external thermal sense function to sense the temperature of external components such as inductor or MOSFETs by connecting a negative temperature coefficient (NTC)

thermistor from TSEN pin to AGND and a resistor from VDD to TSEN pin. Register 0x1A/0x1B can report the TSEN pin voltage from 0V to 2V with 1mV resolution while ADC function is enabled (0x10[1] = 1).

#### **Spread-Spectrum Operation**

Due to periodicity of the switching signals, the energy concentrates in one particular frequency and in its harmonics. These levels of energy will be radiated to induce potential EMI issues. The RT6191A provides spread-spectrum function by register 0x11[7] for simplifying in compliance with the CISPR and EMI requirements.

After the soft-start ends, the spread-spectrum can be enabled with a pseudo random sequence and used +8% spread of the switching frequency. This function is default disabled.

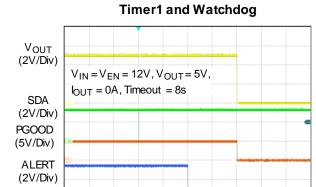

#### **Timer1 and Watchdog Function**

The RT6191A implements a Timer1 function to detect Host status if system hang occurs without any protection detected. Register 0x30[6:4] selects different Timer1 timeout, and the default factory setting value of 0x30[6:4] is 000 for Timer1 disabled. Timer1 will begin to count if 0x30[6:4] ≠ 000, and ALERT pin keeps high level if Timer1 is still counting. After Timer1 timeout completes, external ALERT pin will go to low level.

The RT6191A also implements a watchdog function to reset IC to factory default setting after watchdog timeout completes if ALERT pin keeps at low level. Register 0x30[2:0] selects different watchdog timeout, and the default factory setting value of 0x30[2:0] is 000 for watchdog disabled.

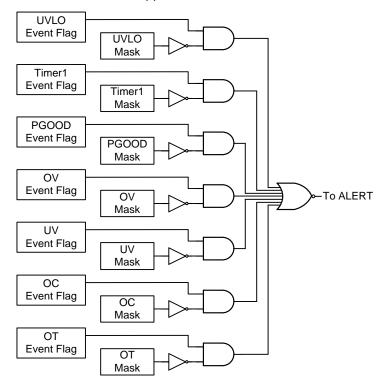

## Status Change Detection and ALERT Pin

The RT6191A implements a status change detection to alert the host when a warning or fault event occurs by using the external ALERT pin with push-pull output capability for active low behavior. The warning events are input UVLO, Timer1 and PGOOD, and the fault events are the conditions of over-voltage, under-voltage, over-current and over-temperature. In addition, PGOOD event indicates output voltage status for normal and DVS operation.

Register 0x1C, 0x1D, 0x1E and 0x1F can help the host

to know what type of warning of fault events happens. 0x1C and 0x1D will be cleared to default setting "0" if the event is removed, but 0x1E and 0x1F will be cleared to default setting "0" by writing this bit to "1" after the events is removed only. The RT6191A also supports

mask function to mask or pass the internal event flag output to external ALERT pin by using 0x20, and 0x21 registers. The overall detection function is shown in Figure 4.

Figure 4. Overall Detection Function Block Diagram

## **Protection**

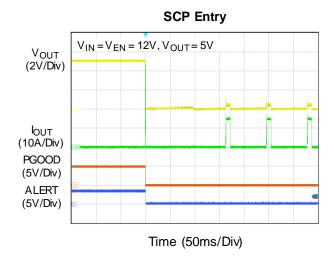

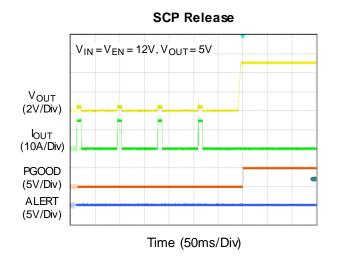

The RT6191A implements full protective mechanism including over/under-voltage protection (OVP/UVP) for each VOUT/VBUSC/VBUSA pin, output over-current protection (OCP), input cycle-by-cycle peak/average current limit, over-temperature protection (OTP) and input OVP/UVP. The protection type of RT6191A is latched-off operation, and RT6191AH is hiccup operation.

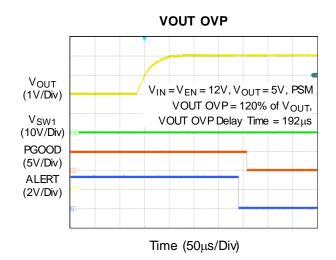

## **Output Over-Voltage Protection (OVP)**

The RT6191A provides output over-voltage protection (OVP) by constantly monitoring output voltage for VOUT/VBUSC/VBUSA pins. If VOUT is larger than the OVP trip threshold (typically 120%) with relative OVP delay time, HDRV1 will stop switching and LDRV1 will fully turn on to discharge energy of the inductor immediately until ZCD is triggered. When VBUSC/VBUSA OVP is triggered, GPC/GPA will turn off but HDRV1/LDRV1 will keep in original state. In

addition, the default factory setting of VBUSC/VBUSA OVP is disabled for correct operation if power path is not used. Register 0x0B[5:0] can select different OVP trip thresholds and OVP delay time, and OVP trip threshold can also be adjustable by register 0x2B[4] and 0x36.

In latched-off operation, RT6191A will return to normal operating unless resetting IC by 0x0E[7] after OVP happens. For hiccup behavior, RT6191AH will return to the last state before OVP happens and the output voltage will go back to regulation point after OVP is released.

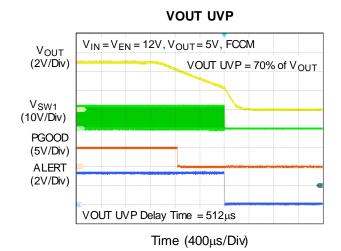

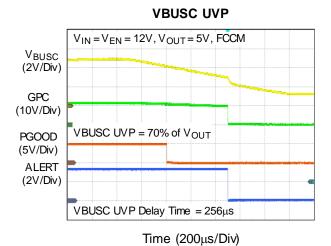

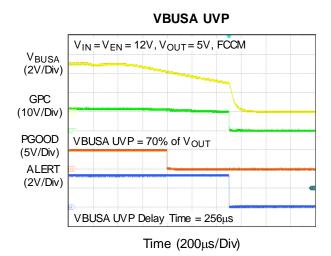

## Output Under-Voltage Protection (UVP)

The RT6191A provides output under-voltage protection (UVP) against over-load or short-circuit condition by constantly monitorina output voltage VOUT/VBUSC/VBUSA pins. If VOUT drops below the UVP trip threshold (typically 70%) with relative UVP delay time, HDRV1 will stop switching and LDRV1 will

Copyright © 2022 Richtek Technology Corporation. All rights reserved. RICHTEK

fully turn on to discharge energy of the inductor immediately until ZCD is triggered. When VBUSC/VBUSA UVP is triggered, GPC/GPA will turn off but HDRV1/LDRV1 will keep in original state. In addition, the default factory setting of VBUSC/VBUSA UVP is disabled for correct operation if power path is not used. Register 0x0C[5:0] can select different UVP trip thresholds and UVP delay time, and UVP trip threshold can also be adjustable by register 0x2B[5] and 0x35.

In latched-off operation, RT6191A will return to normal operating unless resetting the IC by 0x0E[7] after UVP happens. For hiccup behavior, both HDRV1 and LDRV1 of RT6191AH will keep in low state in 65ms and then the IC starts to switch. If the output voltage is not greater than UVP trip threshold after internal soft-start end signal is triggered, both HDRV1 and LDRV1 will still keep in low state again for next cycle.

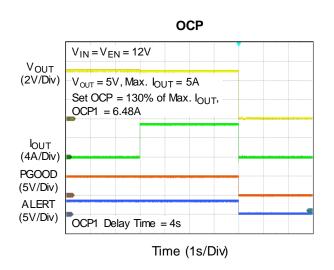

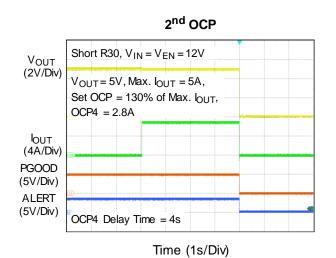

## Output Over-Current Protection (OCP) and Input **Peak/Average Current Limit**

The RT6191A provides over-current protection (OCP) and cycle-by-cycle current limit to prevent the IC from the catastrophic damage in output short-circuit, overcurrent or inductor saturation conditions. For OCP function, RT6191A monitors the voltage across output current sense resistor R30 for OCP1/OCP2/OCP3 detection, and R30/R29 for OCP4 detection. If OCPx is triggered with relative OCP delay time, HDRV1 will stop switching and LDRV1 will fully turn on to discharge energy of the inductor immediately until ZCD is triggered. Register 0x22 to 0x27 and 0x28[3:0] can select the OCP trip threshold and delay time, and 0x28[7:4] are the control bits for OCPx enable. It is recommended to use the same current sense gain of input and output for correct OCP4 function.

In latched-off operation, RT6191A will return to normal operating unless resetting the IC by 0x0E[7] after OCPx happens. For hiccup behavior, RT6191AH will return to the last state before OCPx happens and the output voltage will go back to the regulation point after OCPx is released.

The RT6191A also monitors the voltage across input current sense resistor R29 for cycle-by-cycle peak and average current-limit function. When peak or average current limit is triggered, RT6191A will limit the output current and then the output voltage will be lower than

regulation point until UVP happens. Register 0x0A can set the input peak current-limit threshold, and register 0x06/0x07 can set the input average current-limit threshold.

#### Input Over/Under-Voltage Protection (OVP/UVP)

The RT6191A also provides OVP and UVP by constantly monitoring input voltage for VIN pin. Register 0x0C[7] is used to enable or disable input OVP, and the default factory setting of input OVP is disabled. If input voltage is larger than the OVP trip threshold (default factory setting is 27V), HDRV1 will stop switching and LDRV1 will fully turn on to discharge energy of the inductor immediately until ZCD is triggered.

In addition, register 0x05 can be used to set the minimum input voltage level in FCCM operation. When the input voltage is lower than minimum input voltage level, COMPV will be pulled low to make output voltage lower than the regulation point until output UVP is triggered.

#### **Output Over-Temperature Protection (OTP)**

The RT6191A includes an over-temperature protection (OTP) circuitry to prevent overheating condition. When the junction temperature exceeds a thermal shutdown threshold TSD with latched-off operation, the RT6191A will stop switching and resume normal operation unless resetting the IC by 0x0E[7] after the junction temperature is lower than thermal shutdown hysteresis  $(\Delta T_{SD})$ . For hiccup operation, the RT6191AH will return to the last state and resume normal operation immediately once the junction temperature cools down by  $\Delta T_{SD}$ .

| Absolute Maximum Ratings (Note 1)                                |                |

|------------------------------------------------------------------|----------------|

| • VIN, PSINN, CSINP, CSINN, VOUT, PSOUTN, CSOUTP, CSOUTN to GND  | -0.3V to $40V$ |

| • VIN to PSINN, CSINP to CSINN, VOUT to PSOUTN, CSOUTP to CSOUTN | -5V to 5V      |

| • EN, DIS, VBUSC, VBUSA to GND                                   | -0.3V to $40V$ |

| • GPC, GPA to GND                                                | -0.3V to 50V   |

| • BOOT1 to SW1                                                   | -0.3V to 6V    |

| DC                                                               | -0.3V to 6V    |

| < 100ns                                                          | -5V to 7.5V    |

| HDRV1 to SW1                                                     |                |

| DC                                                               | -0.3V to 6V    |

| < 100ns                                                          | -5V to 7.5V    |

| SW1 to GND                                                       |                |

| DC                                                               | -0.3V to 40V   |

| < 100ns                                                          | -5V to 45V     |

| LDRV1 to GND                                                     |                |

| DC                                                               | -0.3V to 6V    |

| < 100ns                                                          | -2.5V to 7.5V  |

| • Other Pins                                                     | -0.3V to 6V    |

| Lead Temperature (Soldering, 10 sec.)                            | 260°C          |

| • Junction Temperature                                           | 150°C          |

| Storage Temperature Range                                        | −65°C to 150°C |

| ESD Ratings • ESD Susceptibility (Note 2)                        |                |

| HBM (Human Body Model)                                           | 2kV            |

| Recommended Operating Conditions (Note 3)                        |                |

| Supply Input Voltage                                             |                |

| Output Voltage                                                   |                |

| VDDP Supply Voltage                                              |                |

| VBYP Supply Voltage                                              | 4.5V to 5.5V   |

| Junction Temperature Range                                       | –40°C to 125°C |

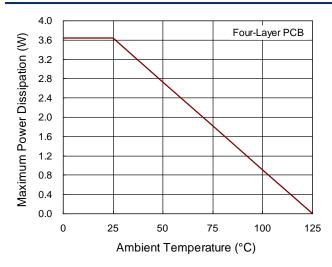

| Thermal Information (Note 4)                                     |                |

| • WQFN-40L 5x5, θJA                                              |                |

| • WQFN-40L 5x5, θJC(Top)                                         | 6°C/W          |

# **Electrical Characteristics**

( $V_{VIN}$  = 12V,  $V_{VDD}$  =  $V_{VDDP}$  = 5V,  $T_A$  = 25°C, unless otherwise specified)

| Parameter                                             | Symbol            | Test Conditions                                         | Min  | Тур | Max  | Unit |

|-------------------------------------------------------|-------------------|---------------------------------------------------------|------|-----|------|------|

| Input and Output                                      | Voltage Range     |                                                         | •    |     |      |      |

| Input Voltage<br>Range                                | VINPUT            | VVIN                                                    | 4.5  |     | 36   | V    |

| Output Voltage<br>Range                               | Vоитрит           | Vvbusc                                                  | 3    |     | 36   | V    |

| Input UVLO<br>Threshold                               |                   |                                                         | 2.7  | 3   | 3.4  | V    |

| Input UVLO<br>Hysteresis                              | ΔVυνιο            | VVIN                                                    |      | 200 |      | mV   |

| VDD Supply Volta                                      | ge and Enable     |                                                         |      |     |      |      |

| VDD Output<br>Voltage                                 | VVDD              | I <sub>VDD</sub> = 0 to 60mA,<br>V <sub>VIN</sub> = 12V | 4.8  | 5   | 5.2  | V    |

| VDD Short-Circuit<br>Current                          | rcuit IVDD_SC 120 |                                                         |      | mA  |      |      |

| VDD UVLO Threshold  VVDD_UVLO                         |                   | V <sub>VDD</sub> rising                                 | 2.7  | 3   | 3.4  | V    |

| VDD UVLO<br>Hysteresis                                | ΔVVDD_ UVLO       |                                                         |      | 200 |      | mV   |

| VDDP UVLO<br>Threshold                                | VVDDP_UVLO        | V <sub>VDDP</sub> rising                                | 3.7  | 4   | 4.3  | V    |

| VDDP UVLO<br>Hysteresis                               | ΔVVDDP_<br>UVLO   |                                                         |      | 200 |      | mV   |

| EN Threshold                                          | VENH              | EN rising                                               | 1.35 |     | 36   | V    |

| ENTITIESTICIO                                         | VENL              | EN falling                                              |      |     | 0.85 | V    |

| VBYP Switchover                                       |                   | VBYP rising                                             |      | 4.5 |      | V    |

| Threshold                                             |                   | VBYP falling                                            |      | 230 |      | mV   |

| VBYP Switchover On-Resistance                         |                   |                                                         |      | 3   |      | Ω    |

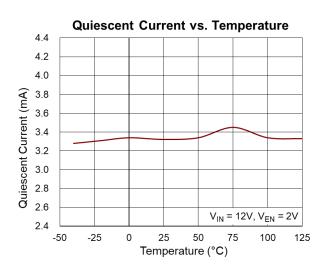

| VIN Operating Cu                                      | rrent             |                                                         |      |     |      |      |

| Input Current in Normal Mode IQ EN = High. In PSM wit |                   | EN = High. In PSM without switching                     |      | 3   | 5    | mA   |

| Input Current in Standby Mode                         | ISHDN             | EN = Low                                                |      | 15  | 30   | μΑ   |

| Parameter                                          | Symbol                                                                     | Test Conditions                                                                                                                                | Min  | Тур | Max  | Unit     |

|----------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|----------|

| Switching Freque                                   | ncy                                                                        |                                                                                                                                                |      |     |      |          |

|                                                    |                                                                            |                                                                                                                                                | 200  | 250 | 300  |          |

|                                                    |                                                                            |                                                                                                                                                | 260  | 325 | 390  |          |

|                                                    |                                                                            |                                                                                                                                                | 320  | 400 | 480  |          |

| Switching                                          | fsw                                                                        | Programmable by 0x0D[2:0]                                                                                                                      | 400  | 500 | 600  | kHz      |

| Frequency                                          | ISVV                                                                       | Trogrammable by 0x0b[2.0]                                                                                                                      | 492  | 615 | 738  | KIIZ     |

|                                                    |                                                                            |                                                                                                                                                | 584  | 730 | 876  |          |

|                                                    |                                                                            |                                                                                                                                                | 676  | 845 | 1014 |          |

|                                                    |                                                                            |                                                                                                                                                | 768  | 960 | 1152 |          |

| Soft-Start                                         |                                                                            |                                                                                                                                                |      |     |      | T        |

| Soft-Start Charge<br>Current                       | Iss                                                                        |                                                                                                                                                | 5    | 6   | 7    | μА       |

| Constant-Voltage                                   | (CV) and Cons                                                              | tant-Current (CC) Output Levels                                                                                                                | 1    |     | 1    | <u>'</u> |

| CSOUTP and<br>CSOUTN<br>Operating Voltage<br>Range | SOUTN perating Voltage                                                     |                                                                                                                                                | 3    |     | 36   | V        |

| CV Regulated                                       | Voca valit                                                                 | 11-bit DAC, VOUT Ratio = 0.08V/V, 12.5mV/step                                                                                                  | 3    |     | 25.6 | V        |

| Voltage Range at VOUT Pin                          | VREG_VOUT                                                                  | 11-bit DAC, VOUT Ratio = 0.05V/V, 20mV/step 3                                                                                                  | 3    |     | 36   | v        |

| CV Regulated<br>Voltage Accuracy<br>at VOUT Pin    |                                                                            | VREG_VOUT = 5V/9V/12V/15V/20V                                                                                                                  | -1.5 |     | 1.5  | %        |

| CSOUTP to<br>CSOUTN Built-in<br>Offset Voltage     |                                                                            |                                                                                                                                                |      | 1.5 |      | mV       |

| CSINP to CSINN<br>Built-in Offset<br>Voltage       |                                                                            |                                                                                                                                                |      | 4.5 |      | mV       |

| Output CC<br>Regulated<br>Voltage Range            | VCSOUTP and VCSOUTN > 3V, with GAIN_OCS = 10x, AVREF_CC_OUT = 0.24mV/step, |                                                                                                                                                | 3    |     | 58   | mV       |

| Output CC<br>Regulated<br>Voltage Accuracy         |                                                                            | VCSOUTP and VCSOUTN > 3V,<br>VREF_CC_OUT = 10mV/30mV/50mV,<br>GAIN_OCS = 10x, R30 = 10mΩ                                                       |      |     | 1    | mV       |

| Input CC<br>Regulated<br>Voltage Range             | VREF_CC_IN                                                                 | VCSINP and VCSINN > 3V, with GAIN_ICS = $10x$ , $\Delta V$ REF_CC_IN = $0.24$ mV/step, and R29 = $10$ m $\Omega$ for IREF_CC_IN = $24$ mA/step | 3    |     | 58   | mV       |

| Parameter                                            | Symbol                                                           | Test Conditions                                                                                                                 | Min  | Тур | Max   | Unit          |  |

|------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|---------------|--|

| Input CC<br>Regulated<br>Voltage Accuracy            |                                                                  | VCSINP and VCSINN > 3V, VREF_CC_IN = $10\text{mV}/30\text{mV}/50\text{mV}$ , GAIN_ICS = $10\text{x}$ , R29 = $10\text{m}\Omega$ | -3   |     | 3     | mV            |  |

| Minimum<br>Regulated                                 | Vpco viiv                                                        | 6-bit DAC, VIN Ratio = 0.08V/V, 350mV/step                                                                                      | 4.55 |     | 22.05 | V             |  |

| Voltage Range at VIN Pin                             | VREG_VIN                                                         | 6-bit DAC, VIN Ratio = 0.05V/V, 560mV/step                                                                                      | 7.28 |     | 35.28 | V             |  |

| Constant-Voltage                                     | Constant-Voltage (CV) and Constant-Current (CC) Error Amplifiers |                                                                                                                                 |      |     |       |               |  |

| Trans-<br>conductance of<br>COMPV Error<br>Amplifier | Gmv                                                              | $I_{COMPV} = \pm 20 \mu A$                                                                                                      | 382  | 550 | 718   | μA/V          |  |

| Maximum Sink/Source Current of COMPV Error Amplifier |                                                                  |                                                                                                                                 |      | 54  |       | μА            |  |

| Trans-<br>conductance of<br>COMPI Error<br>Amplifier | Gmi                                                              | ICOMPI = ±20μA                                                                                                                  | 382  | 550 | 718   | μ <b>A</b> /V |  |

| Maximum Sink/Source Current of COMPI Error Amplifier |                                                                  |                                                                                                                                 |      | 54  |       | μΑ            |  |

| On-Time Timer Co                                     | ontrol and ZCD                                                   |                                                                                                                                 |      |     |       |               |  |

| Minimum On-<br>Time                                  | ton_min                                                          |                                                                                                                                 |      | 200 | 230   | ns            |  |

| Minimum Off-<br>Time                                 | toff_min                                                         |                                                                                                                                 |      | 200 | 230   | ns            |  |

| Q2 ZCD Voltage<br>Threshold                          | Vzcd                                                             |                                                                                                                                 |      | 4   |       | mV            |  |

| ZC Mask Time                                         | tZCD_Mask                                                        |                                                                                                                                 |      | 250 |       | ns            |  |

| Gate Drivers                                         |                                                                  |                                                                                                                                 |      |     |       | T             |  |

| HDRV1 Pull-Up<br>Resistance                          | RHDRV1_SRC                                                       | VBOOT1 - VSW1 = 5V,<br>VBOOT1 - VHDRV1 = 0.1V                                                                                   |      | 1   |       | Ω             |  |

| HDRV1 Pull-<br>Down Resistance                       | RHDRV1_SNK                                                       | VHDRV1 - Vsw1 = 0.1V                                                                                                            |      | 0.7 |       | Ω             |  |

| LDRV1 Pull-Up<br>Resistance                          | RLDRV1_SRC                                                       | VVDDP - VLDRV1 = 0.1V                                                                                                           |      | 2   |       | Ω             |  |

| LDRV1 Pull-<br>Down Resistance                       | RLDRV1_SNK                                                       | V <sub>LDRV1</sub> = 0.1V                                                                                                       |      | 0.4 |       | Ω             |  |

|                                                      |                                                                  |                                                                                                                                 |      | 30  |       |               |  |

| Dead Time                                            | tor                                                              | Programmable by 0x0F[7:6]                                                                                                       |      | 50  |       | ns            |  |

| Deau Tille                                           | tot                                                              |                                                                                                                                 |      | 70  |       | 115           |  |

|                                                      |                                                                  |                                                                                                                                 |      | 90  |       |               |  |

Copyright © 2022 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

DS6191A-00 December 2022 www.rich

| Parameter                                                         | Symbol        | Test Conditions                       | Min      | Тур        | Max        | Unit |

|-------------------------------------------------------------------|---------------|---------------------------------------|----------|------------|------------|------|

| SW1 Pull-Down<br>Period for<br>Charging<br>Bootstrap<br>Capacitor |               |                                       |          | 250        |            | ns   |

| Operating Frequency of Internal Charge Pump for BOOT1             |               |                                       |          | 10         |            | MHz  |

| Protections : Ove<br>(OVP, UVP, OCP, O                            |               | er-Voltage, Over-Current and External | Over-Tem | perature I | Protection | ns   |

| Input OVP Trip<br>Threshold                                       | Vovp_input    | 0x0C[7] = 1                           |          | 27         |            | V    |

| 0 1 10 /D T :                                                     |               |                                       |          | 115        |            |      |

| Output OVP Trip<br>Threshold                                      | Vovp          | Programmable by 0x0B[1:0]             |          | 120        |            | %    |

| THICSHOIL                                                         |               |                                       |          | 125        |            |      |

| Output OVP<br>Recovery<br>Threshold                               | VOVP_R        | P_R Hiccup mode of protection type    |          | 500        |            | mV   |

| Output OVP                                                        |               |                                       |          | 8          |            |      |

| Delay Time at                                                     | tovp_ext      | Programmable by 0x0B[3:2]             |          | 16         |            | μs   |

| VBUSC and                                                         |               |                                       |          | 32         |            |      |

| VBUSA Pins                                                        |               |                                       |          | 64         |            |      |

|                                                                   |               |                                       |          | 96         |            |      |

| Output OVP                                                        | tovp_int      | Programmable by 0x0B[5:4]             |          | 192        |            | μs   |

| Delay Time at<br>VOUT Pin                                         |               |                                       |          | 288        |            |      |

|                                                                   |               |                                       |          | 386        |            |      |

|                                                                   |               |                                       |          | 50         |            |      |

| Output UVP Trip                                                   | ) / · · · · · | Programmable by 0x0C[1:0]             |          | 60         |            | - %  |

| Threshold                                                         | VUVP          |                                       |          | 70         |            |      |

|                                                                   |               |                                       |          | 80         |            |      |

| Output UVP<br>Recovery<br>Threshold                               | Vuvp_r        | Hiccup mode of protection type        |          | 500        |            | mV   |

| Output UVP                                                        |               |                                       |          | 32         |            |      |

| Delay Time at                                                     | tuno eve      | Programmable by 0x0C[2:2]             |          | 64         |            |      |

| VBUSC and                                                         | tuvp_ext      | Programmable by 0x0C[3:2]             |          | 128        |            | μS   |

| VBUSA Pins                                                        |               |                                       |          | 256        |            |      |

|                                                                   |               |                                       |          | 256        |            |      |

| Output UVP Delay Time at                                          | tuvo int      | Programmable by 0x0CI5:41             |          | 512        |            | μs   |

| VOUT Pin                                                          | tuvp_int      | Programmable by 0x0C[5:4]             |          | 768        |            |      |

|                                                                   |               |                                       |          | 1024       |            |      |

| Peak Current<br>Protection                                        | ІРОСР         | R29 = $10m\Omega$ , $0x0A = 24h$      |          | 13.2       |            | Α    |

| Parameter                                         | Symbol         | Test Conditions                                     | Min                             | Тур                             | Max                             | Unit |  |

|---------------------------------------------------|----------------|-----------------------------------------------------|---------------------------------|---------------------------------|---------------------------------|------|--|

| Thermal<br>Shutdown                               | TsD            |                                                     |                                 | 150                             |                                 |      |  |

| Thermal<br>Shutdown<br>Hysteresis                 | ΔTsD           |                                                     |                                 | 25                              |                                 | °C   |  |

| Power Good and                                    | DIS            |                                                     |                                 |                                 |                                 |      |  |

| Power Good                                        | VTH_PG         | VOUT rising for % of VOUT, PGOOD from low to high   |                                 | 90                              |                                 | %    |  |

| Threshold                                         | ΔVTH_PG        | VOUT falling for % of VOUT, PGOOD from high to low  |                                 | 5                               |                                 | 70   |  |

| Power Good<br>Output Low<br>Voltage               | VPG_L          | ISINK = 1mA                                         |                                 |                                 | 0.4                             | V    |  |

| Discharge<br>Resistor at DIS<br>Pin               |                |                                                     |                                 | 6                               |                                 | Ω    |  |

| ADC Reporting                                     |                |                                                     | •                               |                                 |                                 |      |  |

| Input Voltage<br>Reporting                        |                | VVIN                                                | -2.5                            |                                 | 2.5                             | %    |  |

| Output Voltage                                    |                | Vvout ≤ 5V                                          | -2.5                            |                                 | 2.5                             | %    |  |

| Reporting                                         |                | VVOUT > 5V                                          | -2                              |                                 | 2                               |      |  |

| VBUSC Voltage                                     |                | Vvbusc = 0.8V                                       | -40                             |                                 | 40                              | mV   |  |

| Reporting                                         |                | Vvbusc ≥ 5V                                         | -2                              |                                 | 2                               | %    |  |

| TSEN Voltage<br>Reporting                         |                |                                                     | -30                             |                                 | 30                              | mV   |  |

|                                                   |                | VCSINP - VCSINN = 40mV,<br>VCSOUTP - VCSOUTN = 40mV | -2.5                            |                                 | 2.5                             |      |  |

| Input and Output                                  |                | VCSINP - VCSINN = 20mV,<br>VCSOUTP - VCSOUTN = 20mV | -4                              |                                 | 4                               | %    |  |

| Current Reporting                                 |                | VCSINP - VCSINN = 10mV,<br>VCSOUTP - VCSOUTN = 10mV | -7                              |                                 | 7                               | %    |  |

|                                                   |                | VCSINP - VCSINN = 5mV,<br>VCSOUTP - VCSOUTN = 5mV   | -15                             |                                 | 15                              |      |  |

| Charge-Pump Ga                                    | te Drivers (GP | C and GPA)                                          |                                 |                                 |                                 |      |  |

| Maximum GPC<br>Voltage                            | I VCPC         |                                                     | VVBUSC<br>+ 2 x<br>VVDD -<br>5V | VVBUSC<br>+ 2 x<br>VVDD -<br>3V | VVBUSC<br>+ 2 x<br>VVDD -<br>1V | V    |  |

| Maximum GPA<br>Voltage                            | VGPA           | VvBusa = 12V,<br>Rgpa-to-GND ≥ 2MΩ                  | VVBUSA<br>+ 2 x<br>VVDD -<br>5V | VVBUSA<br>+ 2 x<br>VVDD -<br>3V | VVBUSA<br>+ 2 x<br>VVDD -<br>1V | V    |  |

| On-Resistance of<br>the GPC/A Pull-<br>Low MOSFET |                |                                                     |                                 | 250                             | 350                             | Ω    |  |

Copyright © 2022 Richtek Technology Corporation. All rights reserved.

| Parameter                                                      | rameter Symbol Test Conditions |                                  | Min  | Тур | Max | Unit |  |

|----------------------------------------------------------------|--------------------------------|----------------------------------|------|-----|-----|------|--|

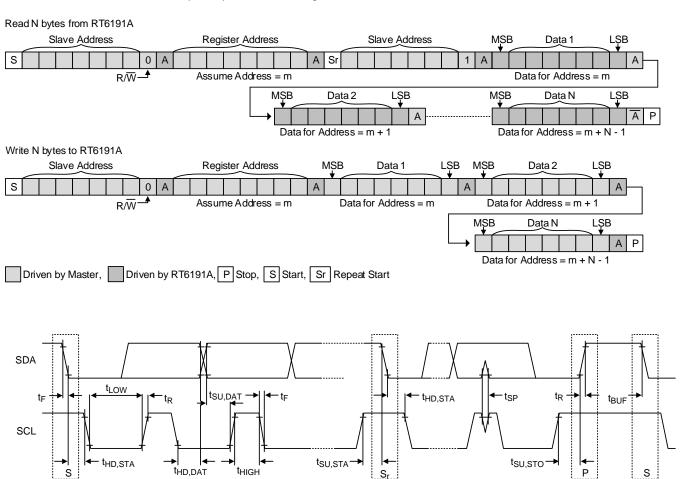

| I <sup>2</sup> C Interface (N                                  | lote 6)                        |                                  |      |     |     |      |  |

| SCL, SDA Input                                                 | ViH                            | Rising                           | 1.2  |     |     | V    |  |

| Voltage                                                        | VIL                            | Falling                          |      |     | 0.4 | V    |  |

|                                                                |                                | Fast mode                        |      | 400 |     | kHz  |  |

| SCL Clock Rate                                                 | fscl                           | Fast plus mode                   |      | 1   |     | MHz  |  |

|                                                                |                                | High speed mode, load 100pF max. |      |     | 3.4 | MHz  |  |

| Hold Time<br>(Repeated)<br>Start Condition.                    |                                | Fast mode                        | 0.6  | 1   |     |      |  |

| After this Period,<br>the First Clock<br>Pulse is<br>Generated | thd;sta                        | Fast plus mode                   | 0.26 | I   |     | μS   |  |

| Low Period of the                                              | t. a                           | Fast mode                        | 1.3  |     |     |      |  |

| SCL Clock                                                      | tLOW                           | Fast plus mode                   | 0.5  |     |     | μS   |  |

| High Period of the                                             | e thigh                        | Fast mode                        | 0.6  |     |     | μs   |  |

| SCL Clock                                                      |                                | Fast plus mode                   | 0.26 |     |     |      |  |

| Set-Up Time for a                                              | tsu;sta                        | Fast mode                        | 0.6  |     |     | μs   |  |

| Repeated START Condition                                       |                                | Fast plus mode                   | 0.26 |     |     |      |  |

| Data Hald Time                                                 | thd;dat                        | Fast mode                        | 0    |     |     | 0    |  |

| Data Hold Time                                                 |                                | Fast plus mode                   | 0    |     |     | μS   |  |

| Data Set-Up Time                                               | tsu;dat                        | Fast mode                        | 100  |     |     | ns   |  |

| Data Get-Op Time                                               |                                | Fast plus mode                   | 50   |     |     | 115  |  |

| Set-Up Time for                                                | toulotto                       | Fast mode                        | 0.6  |     |     |      |  |

| STOP Condition                                                 | tsu;sto                        | Fast plus mode                   | 0.26 |     |     | μS   |  |

| Bus Free Time between a STOP                                   |                                | Fast mode                        | 1.3  |     |     |      |  |

| and START Condition                                            | tBUF                           | Fast plus mode                   | 0.5  |     |     | μs   |  |

| Rising Time of both SDA and                                    | tr                             | Fast mode                        | 20   |     | 300 | ns   |  |

| SCL Signals                                                    |                                | Fast plus mode                   |      |     | 120 |      |  |

| Falling Time of both SDA and                                   | tF                             | Fast mode                        | 20   |     | 300 | ns   |  |

| SCL Signals                                                    |                                | Fast plus mode                   |      | -   | 120 |      |  |

| SDA Output Low<br>Sink Current                                 | loL                            | SDA voltage = 0.4V               | 2    |     |     | mA   |  |

- Note 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2. Devices are ESD sensitive. Handling precautions are recommended.

- Note 3. The device is not guaranteed to function outside its operating conditions.

- Note 4. For more information about thermal parameter, see the Application and Definition of Thermal Resistances report, AN061.

- Note 5. Guaranteed by design.

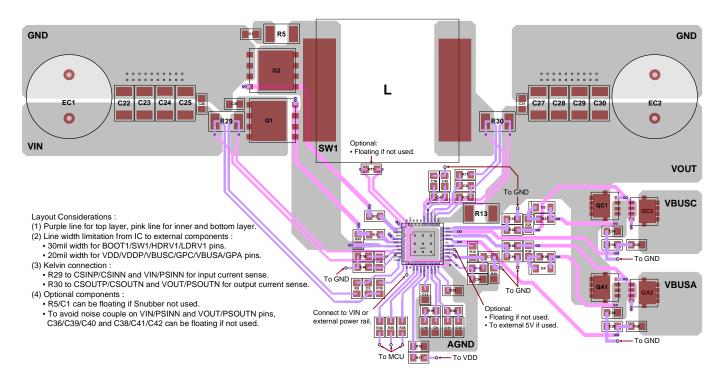

# **Typical Application Circuit**

## **Normal Application Circuit**

#### Note:

- (1)  $I^2C$  slave address is 0x2C when R17 = NC, R18 = 100k $\Omega$ .  $I^2C$  slave address is 0x2D when R17 = 100k $\Omega$ , R18 = NC.

- (2) Support 1C1A when VOUT = 5V.

- (3) \*: Optional components R5 and C1 are used for Snubber.

2022

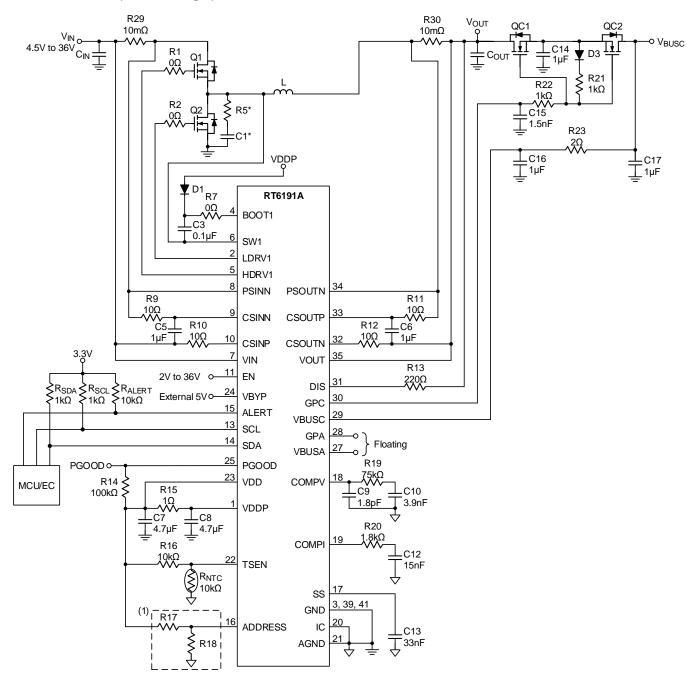

## RT6191A + MCU (with CC Logic) for Monitor

#### Note:

- (1)  $I^2C$  slave address is 0x2C when R17 = NC, R18 = 100k $\Omega$ .  $I^2C$  slave address is 0x2D when R17 = 100k $\Omega$ , R18 = NC.

- (2) VBUSA and GPA can be floating if VBUSC used only.

- (3) \*: Optional components R5 and C1 are used for Snubber.

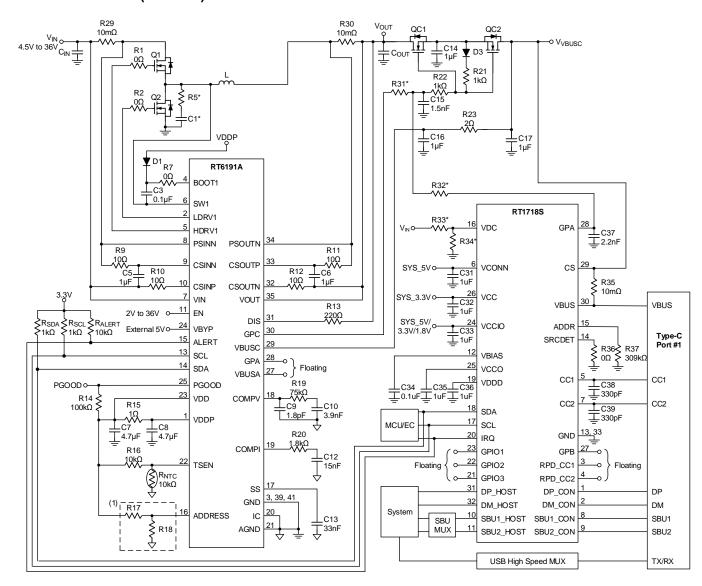

## RT6191A + TCPC IC (RT1718S) for Monitor

#### Note:

- $I^2$ C slave address is 0x2C when R17 = NC, R18 = 100kΩ.  $I^2$ C slave address is 0x2D when R17 = 100kΩ, R18 = NC.

- (2) VBUSA and GPA can be floating if VBUSC used only.

- \*: Optional components (3)

- √ R5 and C1 are used for Snubber.

- ✓ R31 =  $0\Omega$ , R32 = NC, QC1 and QC2 controlled by RT6191A. R31 = NC, R32 =  $0\Omega$ , QC1 and QC2 controlled by RT1718S.

- ✓ Refer to RT1718S datasheet to set R33 and R34 for VDC pin.

DS6191A-00

## Table 1. Recommended BOM

| Reference       | Qty | Part Number          | Description                                             | Package            | Manufacture         |

|-----------------|-----|----------------------|---------------------------------------------------------|--------------------|---------------------|

| U1              | 1   | RT6191A              | DC-DC Controller                                        | WQFN-40L 5x5       | RICHTEK             |

|                 | 1   | AMPI1770ED4R7MT      | 4.7μΗ                                                   | 17.0 x 17.0 x 7.0  | ARLITECH            |

| L1              | 1   | 7443551470           | 4.7μΗ                                                   | 12.8 x 12.8 x 6.2  | WÜRTH<br>ELEKTRONIK |

|                 | 1   | CMMB135T4R7MS        | 4.7μΗ                                                   | 13.45 x 12.6 x 4.8 | CYNTEC              |

| Cons            | 1   | 350ARHA101M08X8      | 100μF/35V/23mΩ                                          | EC-2P_8_3-5MM      | APAQ                |

| C <sub>IN</sub> | 4   | GRM31CR61H106KA12    | 10μF/50V                                                | C-1206             | MURATA              |

| 0               | 1   | 350ARHA101M08X8      | 100μF/35V/23m $\Omega$                                  | EC-2P_8_3-5MM      | APAQ                |

| Соит            | 4   | GRM31CR61H106KA12    | 10μF/50V                                                | C-1206             | MURATA              |

| R29, R30        | 2   | RLM-1632-6F-R010-FNH | Current Sense Resistor                                  | R-1206             | CYNTEC              |

| Q1              | 1   | SM4514NHKP           | 30V High-Side N-MOSFET for USB-PD 3.0 SPR Mode          | DFN5x6-8           | SINOPOWER           |

| QI              | 1   | SM4037NHKP           | 40V High-Side N-MOSFET for 28V of USB-PD 3.1 EPR Mode   | DFN5x6-8           | SINOPOWER           |

|                 | 1   | SM4512NHKP           | 30V Low-Side N-MOSFET for<br>USB-PD 3.0 SPR Mode        | DFN5x6-8           | SINOPOWER           |

| Q2              | 1   | SM4035NHKP           | 40V Low-Side N-MOSFET for<br>28V of USB-PD 3.1 EPR Mode | DFN5x6-8           | SINOPOWER           |

| QC1, QC2        | 4   | SM3425NHQA           | 30V Power Path N-MOSFET for USB-PD 3.0 SPR Mode         | DFN3.3x3.3-8       | SINOPOWER           |

| QA1, QA2 4      |     | SM3430NHQA           | 40V Power Path N-MOSFET for 28V of USB-PD 3.1 EPR Mode  | DFN3.3x3.3-8       | SINOPOWER           |

| D1, D3, D4      | 3   | 1N4148WS             | Diode                                                   | SOD-323            | PANJIT              |

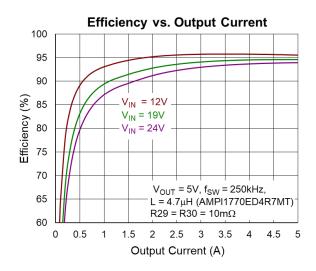

# **Typical Operating Characteristics**

www.richtek.com

Copyright © 2022 Richtek Technology Corporation. All rights reserved.

DS6191A-00 December 2022 www.richtek.com

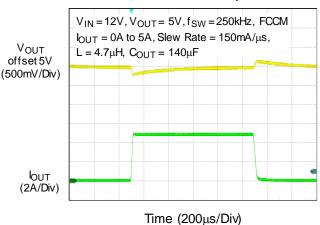

# **Load Transient Response**

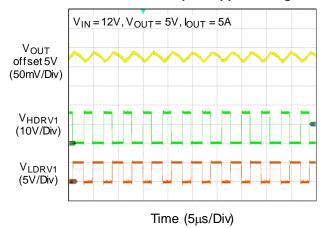

#### **Buck Mode Output Ripple Voltage**

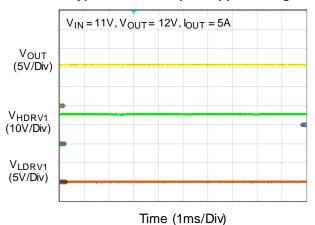

#### **Bypass Mode Output Ripple Voltage**

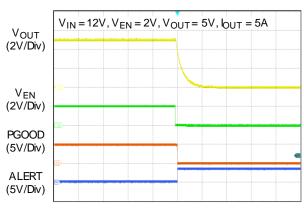

## **Power Off from VIN**

Power Off from EN

Time (500µs/Div)

Copyright © 2022 Richtek Technology Corporation. All rights reserved.

DS6191A-00 December 2022 www.richtek.com

Time (4s/Div)

www.richtek.com

# **Application Information**

A general RT6191A application circuit is shown in Typical Application Circuit section. External component selection is largely driven by the load requirement and begins with the operating frequency from setting register 0x0D[2:0]. Then the inductor (L), the input capacitor (CIN), and the output capacitor (COUT) can be determined in this section. In addition, other external components such as the internal regulator capacitor of VDD and VDDP pins, resistor and capacitor of the bootstrap network circuit, and the gate driver resistors for external power N-MOSMET will also be introduced. Finally, the discharge resistor from DIS pin to the output capacitor can be calculated to meet the USB power delivery specification.

#### **Inductor Selection**

The inductor selection trades off among size, cost, power conversion efficiency, and transient response requirements. Generally, three key inductor parameters are specified for operation of the device: inductor value (L), inductor saturation current (ISAT), and DC resistance (DCR). A good compromise between inductor size and power loss is from a 30% to 50% peak-to-peak ripple current to the IC rated current. The switching frequency, input voltage, output voltage, and selected inductor ripple current determines the inductor value as follows:

$$L = \frac{\left(V_{IN} - V_{OUT}\right)}{\Delta I_L \times f_{SW}} \times \frac{V_{OUT}}{V_{IN}}$$

Larger inductance values result in lower output ripple voltage and higher efficiency, but a slightly degraded load transient response. This result in additional phase lag in the loop and reduce the crossover frequency. As the ratio of the slope compensation ramp to the sensed current ramp increases, the current-mode system tilts towards voltage-mode control. Lower inductance values allow for smaller case size, but the increased ripple current lowers the effective input peak current-limit threshold and increases the AC losses in the inductor. To enhance the power conversion efficiency, choose a low-loss inductor with the lowest possible DC resistance that fits in the allotted dimensions. The inductor value determines not only the ripple current but also the load-

current value at which DCM/CCM switchover occurs. The selected inductor should have a saturation current rating greater than the peak current limit setting by RT6191A, and the core must be large enough not to saturate at the peak inductor current (IL\_PEAK):

$$\Delta I_{L} = \frac{\left(V_{IN} - V_{OUT}\right)}{L \times f_{SW}} \times \frac{V_{OUT}}{V_{IN}}$$

$$I_{L\_PEAK} = I_{OUT\_MAX} + \frac{1}{2} \times \Delta I_{L}$$

The current flowing through the inductor is the inductor ripple current plus the output current. During power up, faults or transient load conditions, the inductor current can increase above the peak inductor current level calculated above. In load transient conditions, the inductor current can increase up to the input peak current limit setting by RT6191A. For this reason, the most conservative approach is to specify an inductor with a saturation current rating equal to or greater than the input peak current limit rather than the peak inductor current.

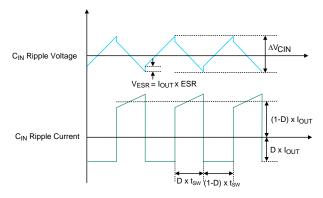

#### **Input Capacitor Selection**