# 3.5A, 1.2MHz, Synchronous Step-Down Converter

## **General Description**

The RT8086B is a high efficiency, synchronous step-down DC-DC converter. The available input voltage range is from 2.8V to 5.5V and the regulated output voltage is adjustable from 0.6V to 3.3V while delivering up to 3.5A of output current.

The internal synchronous low on-resistance power switches increase efficiency and eliminate the need for an external Schottky diode.

The current mode constant on-time operation with internal compensation allows the transient response to be optimized over a wide range of loads and output capacitors. The RT8086B is available in the UQFN-12L 2x2 (FC) package.

## **Ordering Information**

RT8086B □□

$^{ackslash}$ Package Type

QUF: UQFN-12L 2x2 (FC) (U-Type)

Lead Plating System

G: Green (Halogen Free and Pb Free)

#### Note:

Richtek products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Features**

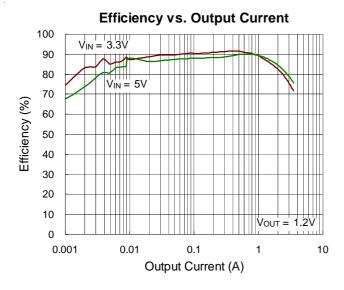

- High Efficiency Up to 95%

- Low  $R_{DS(ON)}$  Switches :  $50m\Omega/40m\Omega$

- 0.6V Reference Allows for Low Output Voltage

- Internal Compensation

- Input Voltage Range: 2.8V to 5.5V

- Adjustable Output Voltage from 0.6V to 3.3V

- 1.2MHz Switching Frequency

- Start-Up into Pre-Biased Load

- Built in Soft-Start

- Power Good Indication

- Cycle-by-Cycle Current Limit

- Input Under Voltage Lockout

- Output Under Voltage Protection (Hiccup)

- Thermal Shutdown Protection

- RoHS Compliant and Halogen Free

## **Applications**

- Smart Handheld devices

- Portable Instruments

- Battery-Powered Equipment

- Distributed Power Systems

# **Marking Information**

0Y : Product Code W : Date Code

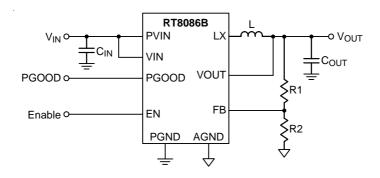

# **Simplified Application Circuit**

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

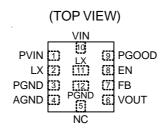

# **Pin Configuration**

UQFN-12L 2x2 (FC)

# **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                          |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PVIN     | Power input. The available input voltage range is from 2.8V to 5.5V. A $10\mu F$ or larger input capacitor is needed to reduce voltage spikes at the input.                                           |

| 2, 11   | LX       | Switch node. Output of the internal high side and low side MOSFETs.                                                                                                                                   |

| 3, 12   | PGND     | Power ground.                                                                                                                                                                                         |

| 4       | AGND     | Analog ground.                                                                                                                                                                                        |

| 5       | NC       | No internal connection.                                                                                                                                                                               |

| 6       | VOUT     | Sense input pin for output voltage.                                                                                                                                                                   |

| 7       | FB       | Feedback input. This pin used to set the output voltage of the converter to regulate to the desired value via an external resistive divider. The feedback reference voltage is 0.6V typically.        |

| 8       | EN       | Enable control input. A logic-high (1.2V < EN < 5.5V) enables the converter; a logic-low forces the IC into shutdown mode.                                                                            |

| 9       | PGOOD    | Power good indicator. The output of this pin is an open drain with internal pull-up resister to VIN. The output of this pin is pulled to high when the FB voltage is within 10%; otherwise it is Low. |

| 10      | VIN      | Supply voltage for internal control circuit. It is connected to PVIN inside the chip.                                                                                                                 |

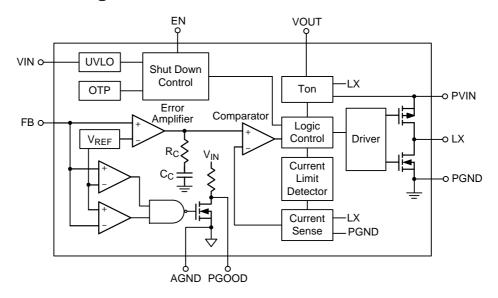

## **Functional Block Diagram**

## **Operation**

The RT8086B is a synchronous low voltage step-down converter that can support the input voltage range from 2.8V to 5.5V and the output current can be up to 3.5A. The RT8086B uses a constant on-time, current mode architecture. In normal operation, the high side P-MOSFET is turned on when the switch controller is set by the comparator and is turned off when the Ton comparator resets the switch controller.

Low side MOSFET peak current is measured by internal RSENSE. The error amplifier EA adjusts COMP voltage by comparing the feedback signal (V<sub>FB</sub>) from the output voltage with the internal 0.6V reference. When the load current increases, it causes a drop in the feedback voltage relative to the reference, then the COMP voltage rises to allow higher inductor current to match the load current.

### **UV** Comparator

If the feedback voltage ( $V_{FB}$ ) is lower than threshold voltage 0.2V, the UV comparator's output will go high and the switch controller will turn off the high side MOSFET. The output under voltage protection is designed to operate in Hiccup mode.

### **PGOOD Comparator**

When the feedback voltage ( $V_{FB}$ ) is higher than threshold voltage 0.54V and under 0.66V, the PGOOD open drain output will be high impedance.

### **Enable Comparator**

A logic-high enables the converter; a logic-low forces the IC into shutdown mode. There is an internal pull down  $1M\Omega$  resistor at EN pin.

### Soft-Start (SS)

An internal current source charges an internal capacitor to build the soft-start ramp voltage. The  $V_{FB}$  voltage will track the internal ramp voltage during soft-start interval. The typical soft-start time is 2ms.

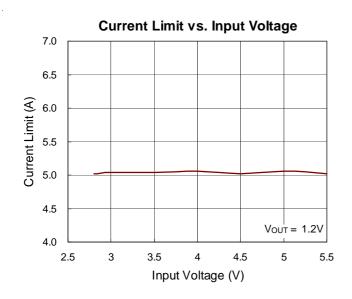

### **Over-Current Protection (OCP)**

The RT8086B provides over-current protection by detecting low side MOSFET valley inductor current. If the sensed valley inductor current is over the current limit threshold (4.5A min.), the OCP will be triggered. When OCP is tripped, the RT8086B will keep the over current threshold level until the over current condition is removed.

#### Thermal Shutdown (OTP)

The device implements an internal thermal shutdown function when the junction temperature exceeds 140°C. The thermal shutdown forces the device to stop switching when the junction temperature exceeds the thermal shutdown threshold. Once the die temperature decreases below the hysteresis of 20°C, the device reinstates the power up sequence.

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# Absolute Maximum Ratings (Note 1)

| Supply Input Voltage, PVIN, VIN                                             | - −0.3V to 6.5V        |

|-----------------------------------------------------------------------------|------------------------|

| Switch Node Voltage, LX                                                     | -0.3V to (PVIN + 0.3V) |

| < 50ns                                                                      | 5V to 7.5V             |

| Other Pins Voltage                                                          | 0.3V to 6V             |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                        |

| UQFN-12L 2x2 (FC)                                                           | - 1.25W                |

| Package Thermal Resistance (Note 2)                                         |                        |

| UQFN-12L 2x2 (FC), $\theta_{JA}$                                            | - 80°C/W               |

| UQFN-12L 2x2 (FC), $\theta_{JC}$                                            | - 7°C/W                |

| • Lead Temperature (Soldering, 10 sec.)                                     | - 260°C                |

| • Junction Temperature                                                      | - 150°C                |

| Storage Temperature Range                                                   | 65°C to 150°C          |

| • ESD Susceptibility (Note 3)                                               |                        |

| HBM (Human Body Model)                                                      | - 2kV                  |

| Recommended Operating Conditions (Note 4)                                   |                        |

| Supply Input Voltage                                                        | - 2.8V to 5.5V         |

### **Electrical Characteristics**

( $V_{IN} = 3.3V$ ,  $T_A = 25$ °C, unless otherwise specified)

| Parameter                      |                     | Symbol            | Test Conditions                                                              | Min   | Тур | Max   | Unit |  |

|--------------------------------|---------------------|-------------------|------------------------------------------------------------------------------|-------|-----|-------|------|--|

| Input Voltage                  |                     | PVIN              |                                                                              | 2.8   |     | 5.5   | V    |  |

| Feedback Reference Voltage     |                     | VREF              |                                                                              | 0.588 | 0.6 | 0.612 | V    |  |

| Feedback Leakage Current       |                     | I <sub>FB</sub>   | V <sub>FB</sub> = 3.3V                                                       |       |     | 1     | μΑ   |  |

| Quiescent Current              |                     |                   | Close loop, no load current                                                  |       | 60  |       |      |  |

| Shutdown Current               |                     |                   | Shutdown                                                                     |       |     | 1     | μΑ   |  |

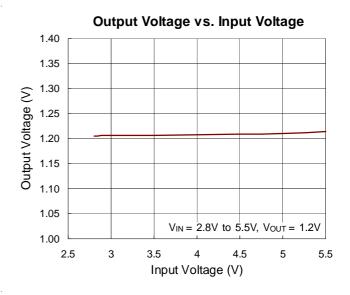

| Output Voltage Line Regulation |                     |                   | V <sub>IN</sub> = 2.8V to 5.5V                                               |       | 0.1 |       | %/V  |  |

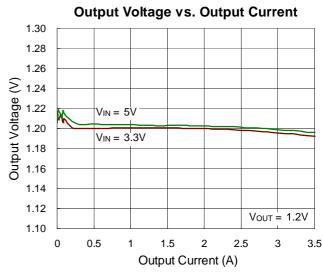

| Output Voltage Load Regulation |                     |                   | V <sub>IN</sub> = 5V, V <sub>OUT</sub> = 3.3V, I <sub>OUT</sub> = 0A to 3.5A |       | 0.4 |       | %    |  |

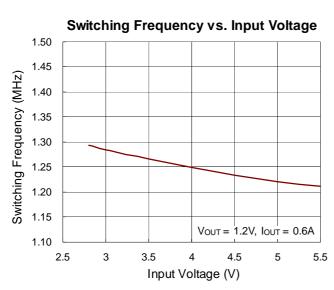

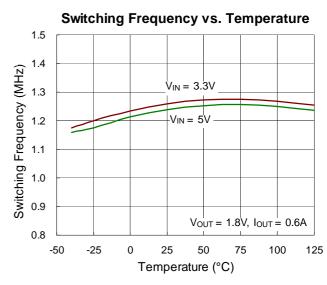

| Switching Frequen              | Switching Frequency |                   | V <sub>IN</sub> = 5V, V <sub>OUT</sub> = 1.2V                                |       | 1.2 |       | MHz  |  |

| Switch                         | High-Side           | R <sub>PMOS</sub> | I <sub>L</sub> X = 0.3A, V <sub>IN</sub> = 5V                                |       | 50  |       |      |  |

| On-Resistance                  | Low-Side            | R <sub>NMOS</sub> | I <sub>L</sub> X = 0.3A, V <sub>IN</sub> = 5V                                |       | 40  |       | mΩ   |  |

| Current Limit                  |                     | I <sub>LIM</sub>  | Valley current                                                               | 4.5   |     |       | Α    |  |

| Min. Off-Time                  |                     | toff              |                                                                              |       | 100 |       | ns   |  |

| Under Voltage Lockout          |                     |                   | V <sub>IN</sub> rising                                                       |       | 2.5 |       | V    |  |

| Threshold                      |                     |                   | V <sub>IN</sub> falling                                                      |       | 2.2 |       |      |  |

| Thermal Shutdown               |                     |                   |                                                                              |       | 140 |       | °C   |  |

| Enable Voltage                 | Logic-High          |                   |                                                                              | 1.2   | -   | 5.5   | V    |  |

|                                | Logic-Low           |                   |                                                                              |       |     | 0.4   | V    |  |

| Parameter                              | Symbol          | Test Conditions                                 |  | Тур | Max | Unit |

|----------------------------------------|-----------------|-------------------------------------------------|--|-----|-----|------|

| EN logue Current                       |                 | VEN = 2V                                        |  | 2   |     | ^    |

| EN Input Current                       |                 | VEN = 0V                                        |  | 0   |     | μΑ   |

| PGOOD Pin Trigger Delay                |                 |                                                 |  | 90  |     | μS   |

| PGOOD Pin Threshold (Relative to VOUT) |                 | FB with respect to the regulation               |  | ±10 |     | %    |

| PGOOD Open Drain<br>Impedance          | RPGOOD          | PGOOD = PVIN                                    |  | 500 |     | kΩ   |

| PGOOD On-Resistance<br>Impedance       |                 | PGOOD = Low                                     |  |     | 100 | Ω    |

| Soft-Start Time                        | T <sub>SS</sub> |                                                 |  | 2   |     | ms   |

| On Time                                | Ton             | V <sub>IN</sub> = 5V, V <sub>OUT</sub> = 1.2V 2 |  | 200 |     |      |

| On-Time                                |                 | V <sub>IN</sub> = 3.6V, V <sub>OUT</sub> = 1.2V |  | 277 |     | ns   |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

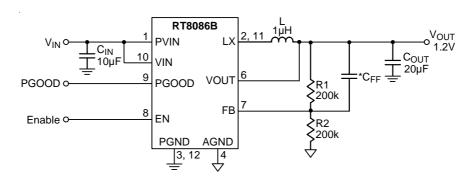

# **Typical Application Circuit**

\*: The feedforward capacitor CFF is optional for the optimization of transient response by increasing bandwidth and acceptable phase margin.

$$C_{FF} = \frac{1}{2\pi f_{CO}} \sqrt{\frac{1}{R1} \left(\frac{1}{R1} + \frac{1}{R2}\right)}$$

Where f<sub>CO</sub> is the unity gain crossover frequency of the control loop without the external feedforward capacitor installed.

**Table 1. Suggested Component Values**

| V <sub>OUT</sub> (V) | <b>R1 (k</b> Ω) | <b>R2 (k</b> Ω) | <b>L (</b> μ <b>H)</b> | C <sub>OUT</sub> (μF) |

|----------------------|-----------------|-----------------|------------------------|-----------------------|

| 1.2V                 | 200             | 200             | 1                      | 20                    |

| 1.8V                 | 200             | 100             | 1                      | 20                    |

| 2.5V                 | 200             | 63.4            | 1                      | 20                    |

| 3.3V                 | 200             | 44.2            | 1                      | 20                    |

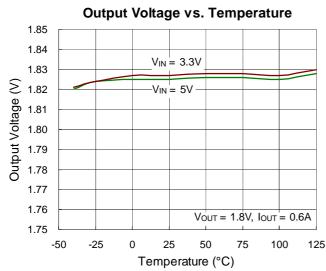

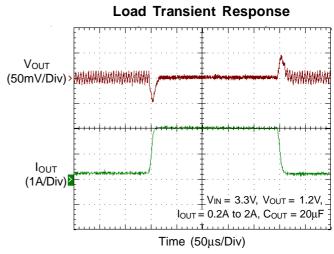

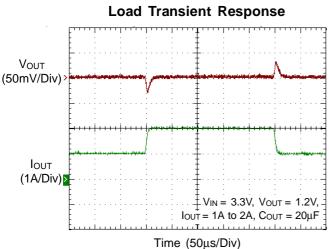

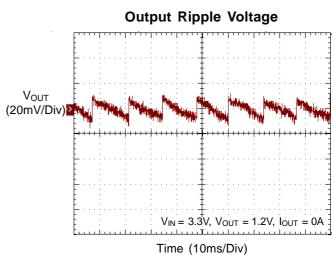

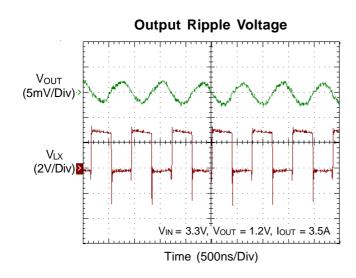

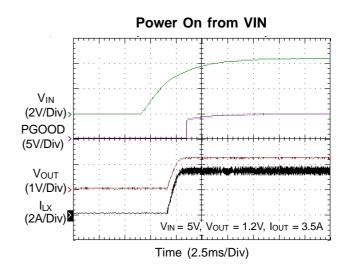

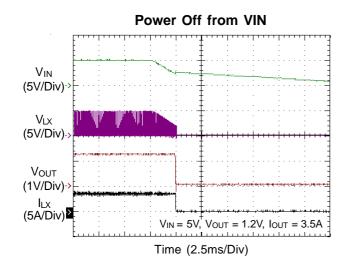

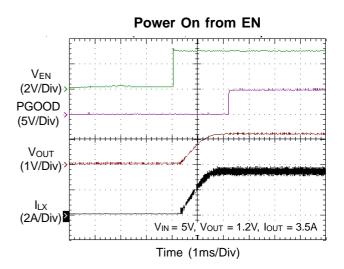

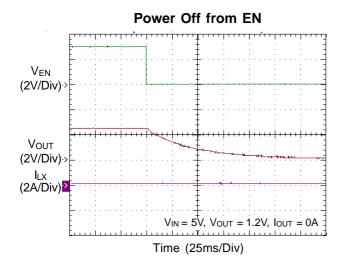

# **Typical Operating Characteristics**

Copyright ©2018 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

## **Application Information**

The RT8086B is a single-phase step-down converter. It provides single feedback loop, current mode control with fast transient response. An internal 0.6V reference allows the output voltage to be precisely regulated for low output voltage applications. A fixed switching frequency (1.2MHz) oscillator and internal compensation are integrated to minimize external component count. Protection features include over current protection, under voltage protection and over temperature protection.

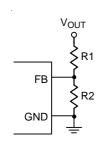

### **Output Voltage Setting**

Connect a resistive voltage divider at the FB between Vout and GND to adjust the output voltage. The output voltage is set according to the following equation:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R1}{R2}\right)$$

where V<sub>REF</sub> is the feedback reference voltage 0.6V (typ.).

Figure 1. Setting V<sub>OUT</sub> with a Voltage Divider

### **Chip Enable and Disable**

The EN pin allows for power sequencing between the controller bias voltage and another voltage rail. The RT8086B remains in shutdown if the EN pin is lower than 400mV. When the EN pin rises above the V<sub>EN</sub> trip point, the RT8086B begins a new initialization and soft-start cycle.

### **Internal Soft-Start**

The RT8086B provides an internal soft-start function to prevent large inrush current and output voltage overshoot when the converter starts up. The soft-start (SS) automatically begins once the chip is enabled. During softstart, the internal soft-start capacitor becomes charged and generates a linear ramping up voltage across the capacitor. This voltage clamps the voltage at the FB pin, causing PWM pulse width to increase slowly and in turn reduce the input surge current. The internal 0.6V reference takes over the loop control once the internal ramping-up voltage becomes higher than 0.6V.

### **UVLO Protection**

The RT8086B has input Under Voltage Lockout protection (UVLO). If the input voltage exceeds the UVLO rising threshold voltage (2.5V typ.), the converter resets and prepares the PWM for operation. If the input voltage falls below the UVLO falling threshold voltage during normal operation, the device will stop switching. The UVLO rising and falling threshold voltage has a hysteresis to prevent noise-caused reset.

### **Inductor Selection**

The switching frequency (on-time) and operating point (% ripple or LIR) determine the inductor value as shown below:

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{f_{SW} \times LIR \times I_{LOAD(MAX)} \times V_{IN}}$$

where LIR is the ratio of the peak-to-peak ripple current to the average inductor current.

Find a low loss inductor having the lowest possible DC resistance that fits in the allotted dimensions. The core must be large enough not to saturate at the peak inductor current (I<sub>PEAK</sub>):

$$I_{PEAK} = I_{LOAD(MAX)} + \left(\frac{LIR}{2} \times I_{LOAD(MAX)}\right)$$

The calculation above serves as a general reference. To further improve transient response, the output inductor can be further reduced. This relation should be considered along with the selection of the output capacitor.

### **Input Capacitor Selection**

High quality ceramic input decoupling capacitor, such as X5R or X7R, with values greater than 10µF are recommended for the input capacitor. The X5R and X7R ceramic capacitors are usually selected for power regulator capacitors because the dielectric material has less capacitance variation and more temperature stability.

Voltage rating and current rating are the key parameters when selecting an input capacitor. Generally, selecting an input capacitor with voltage rating 1.5 times greater than the maximum input voltage is a conservatively safe design.

The input capacitor is used to supply the input RMS current, which can be approximately calculated using the following equation:

$$I_{IN\_RMS} = I_{LOAD} \times \sqrt{\frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}$$

The next step is selecting a proper capacitor for RMS current rating. One good design uses more than one capacitor with low equivalent series resistance (ESR) in parallel to form a capacitor bank.

The input capacitance value determines the input ripple voltage of the regulator. The input voltage ripple can be approximately calculated using the following equation:

$$\Delta V_{IN} = \frac{I_{OUT(MAX)}}{C_{IN} \times f_{SW}} \times \frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

### **Output Capacitor Selection**

The output capacitor and the inductor form a low pass filter in the Buck topology. In steady state condition, the ripple current flowing into/out of the capacitor results in ripple voltage. The output voltage ripple (V<sub>P-P</sub>) can be calculated by the following equation :

$$V_{P\_P} = LIR \times I_{LOAD(MAX)} \times \left(ESR + \frac{1}{8 \times C_{OUT} \times f_{SW}}\right)$$

When load transient occurs, the output capacitor supplies the load current before the controller can respond. Therefore, the ESR will dominate the output voltage sag during load transient. The output voltage undershoot ( $V_{SAG}$ ) can be calculated by the following equation :

$$V_{SAG} = \Delta I_{LOAD} \times ESR$$

For a given output voltage sag specification, the ESR value can be determined.

Another parameter that has influence on the output voltage sag is the equivalent series inductance (ESL). The rapid change in load current results in di/dt during transient. Therefore, the ESL contributes to part of the voltage sag. Using a capacitor with low ESL can obtain better transient performance. Generally, using several capacitors connected in parallel can have better transient performance than using a single capacitor for the same total ESR.

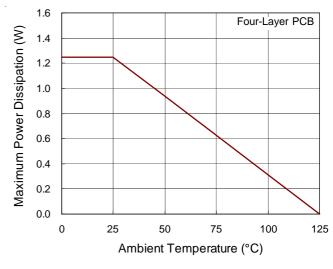

### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For UQFN-12L 2x2(FC) package, the thermal resistance,  $\theta_{JA}$ , is 80°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A$  = 25°C can be calculated by the following formula :

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (80^{\circ}C/W) = 1.25W$$

for UQFN-12L 2x2 (FC) package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 2 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 2. Derating Curve of Maximum Power Dissipation

Copyright © 2018 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

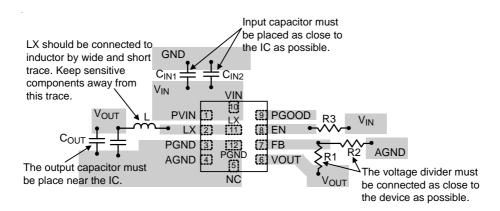

### **Layout Considerations**

Layout is very important in high frequency switching converter design. The PCB can radiate excessive noise and contribute to converter instability with improper layout. Certain points must be considered before starting a layout using the RT8086B.

- Make the traces of the main current paths as short and wide as possible.

- > Put the input capacitor as close as possible to the device pins (V<sub>IN</sub> and GND).

- LX node encounters high frequency voltage swings so it should be kept in a small area. Keep sensitive components away from the LX node to prevent stray capacitive noise pick-up.

- Ensure all feedback network connections are short and direct. Place the feedback network as close to the chip as possible.

- > The GND pin and Exposed Pad should be connected to a strong ground plane for heat sinking and noise protection.

- An example of PCB layout guide is shown in Figure 3 for reference.

Figure 3. PCB Layout Guide

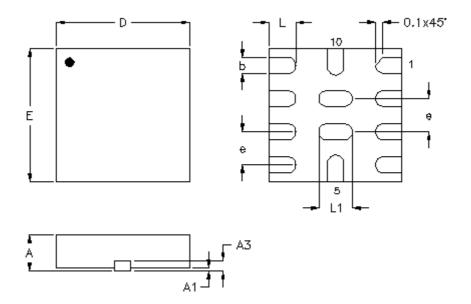

# **Outline Dimension**

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

|        | Min.         | Max.          | Min.                 | Max.  |  |

| А      | 0.500        | 0.600         | 0.020                | 0.024 |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002 |  |

| А3     | 0.100        | 0.152         | 0.004                | 0.006 |  |

| b      | 0.200        | 0.300         | 0.008                | 0.012 |  |

| D      | 1.900        | 2.100         | 0.075                | 0.083 |  |

| E      | 1.900        | 2.100         | 0.075                | 0.083 |  |

| е      | 0.5          | 500           | 0.0                  | )20   |  |

| L      | 0.350        | 0.450         | 0.014                | 0.018 |  |

| L1     | 0.450        | 0.550         | 0.018                | 0.022 |  |

U-Type 12L QFN 2x2 (FC) Package

## **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.