### Multi-Phase PWM Controller with PWM-VID Reference

### **General Description**

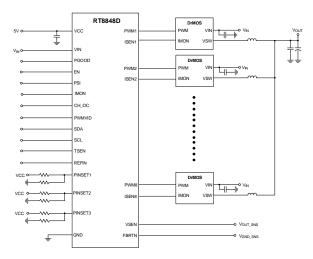

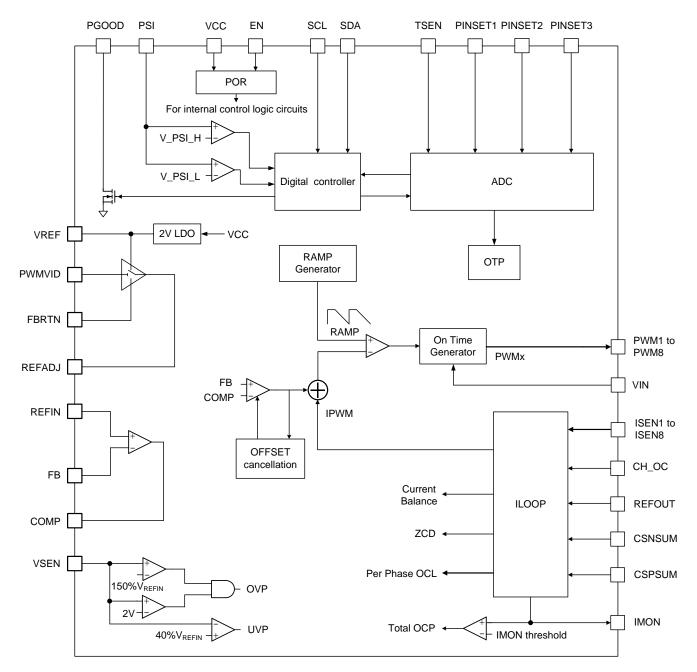

The RT8848D is a 8/7/6/5/4/3/2/1 multi-phase synchronous Buck controller which is optimized for graphic high-performance microprocessor and supports nVidia OVR4i+ spec with PWM-VID interface. The RT8848D adopts AC G-NAVP<sup>TM</sup> (Green Native AVP), which is Richtek's proprietary topology derived from finite DC gain of internal GM amplifier with current mode control. By utilizing the AC G-NAVP<sup>TM</sup> topology. the operating frequency of the RT8848D varies with VID, load and input voltage to further enhance the efficiency even in CCM. Besides, for current sensing application, the RT8848D can support either a traditional DCR network current sensing from inductor or a smart power stage (SPS) which can directly provide a current monitor signal (IMON).

The RT8848D features external reference input and PWM-VID dynamic output voltage control, in which the output voltage is regulated and tracks external input reference voltage. The RT8848D can set internal RAMP amplitude through PINSETx pin and this can optimize stability and load transient performance. The RT8848D also provides complete fault protection functions including over-voltage protection (OVP), under-voltage protection (UVP), channel over-current limit (CH\_OC), sum output current protection (SOC) and over-temperature protection (OTP).

### Features

- Multi-Phase PWM Controller

- PWM-VID Dynamic Voltage Control

- Support 1.8V PWM-VID Interface

- Power State Indicator

- LPC (Low Phase Count), PSI = Low

- ► APS (Auto Phase Shedding), PSI = Mid

- ► HPC (High Phase Count), PSI = High

- External Reference Input Control

- 8/7/6/5/4/3/2/1 Phase Hardware Setting

- Adjustable Soft-Start Time

- Adjustable Switching Frequency

- Adjustable Phase Current Balance

- Support Standby Mode

- UVP/OVP/OTP/SOC/CH\_OC/TSEN Protection

- Adjustable Protection Thresholds

- Power Good Indicator

- ADC Reporting for IMON, TSEN and VSEN

- Support I<sup>2</sup>C Interface for Programming

- RoHS Compliant and Halogen Free

#### **Applications**

GPU Core Power for OVR4i+ Spec

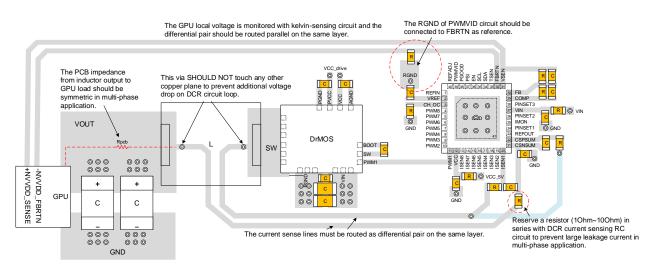

### **Simplified Application Circuit**

### **Ordering Information**

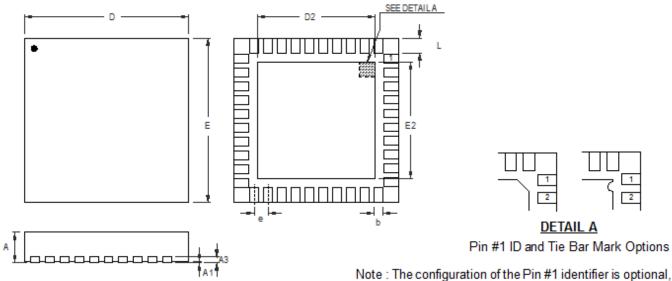

#### RT8848D 🖵 📮 📮

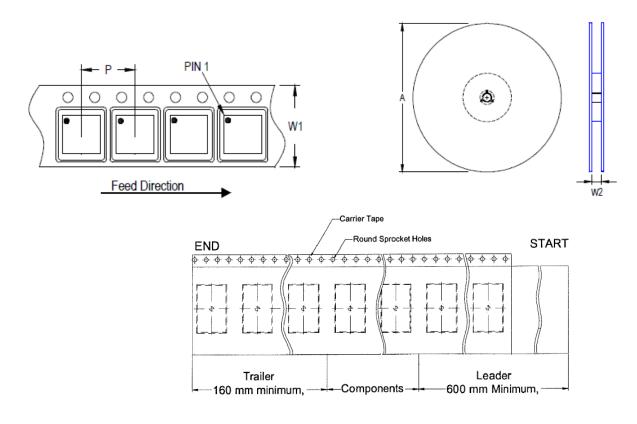

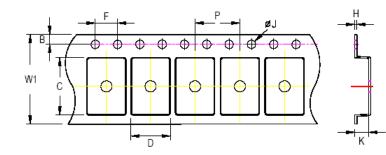

Pin 1 Orientation (2) : Quadrant 2, Follow EIA-481-D (Empty means Pin1 orientation is Quadrant 1) Package Type QW : WQFN-40L 5x5 (W-Type) Lead Plating System G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- ► RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

### **Marking Information**

RT8848D GQW YMDNN RT8848DGQW : Product Code YMDNN : Date Code

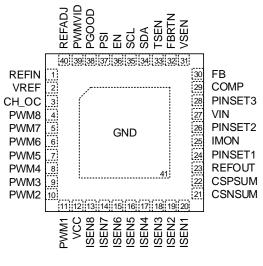

### **Pin Configuration**

(TOP VIEW)

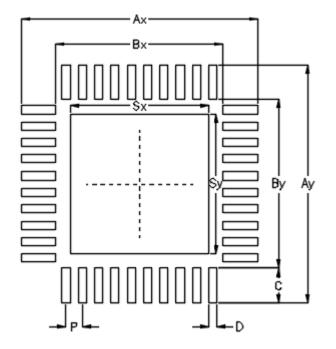

WQFN-40L 5x5

### **Functional Pin Description**

| Pin No.  | Pin Name       | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | REFIN          | External reference input. Connect this pin to an external voltage source through a RC filter (R = $2.2\Omega/0603$ and C = $1\mu$ F/0603) or connect to the output of REFADJ circuit.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2        | VREF           | Reference voltage output. Connect a $0.1\mu\text{F}/0603$ decoupling capacitor between VREF and GND. The reference voltage is 2V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3        | СН_ОС          | Channel current limit. Connect a resistor from CH_OC to GND to adjust<br>the per-phase current limit threshold. The resistor setup for current limit<br>threshold is detailed in Application Information section. Besides, if<br>CH_OC is left floating, voltage of CH_OC is fixed at 5V for maximum<br>current limit level.                                                                                                                                                                                                                                                                                 |

| 4 to 11  | PWM8 to PWM1   | PWM control output for phase 8 to phase 1 driver circuit.<br>As PWM output is high (pulled up to VCC), high-side MOSFET is turned<br>on. As PWM output is in tri-state level (1.65V or 1.9V), both MOSFETs<br>are turned off. As PWM output is low (pull down to GND), low-side<br>MOSFET is turned on.<br>In addition, the parasitic capacitor on the PWM pin should be smaller<br>than 100pF. Leave pin floating if the operating phase is disabled.                                                                                                                                                       |

| 12       | VCC            | Bias voltage for control logic. The required bias voltage for VCC is 5V typ. For avoiding noise disturbance, the supplied bias voltage must be stable. Besides, a RC filter (R = $2.2\Omega/0603$ and C = $1\mu$ F/0603) from bias voltage to VCC pin is necessary, and should be placed as close as physically possible to VCC pin. There is around 50mA sink current during POR duration, the maximum resistance of RC filter should be smaller than $2.2\Omega$ .                                                                                                                                         |

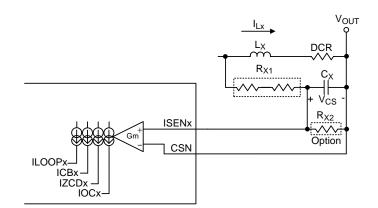

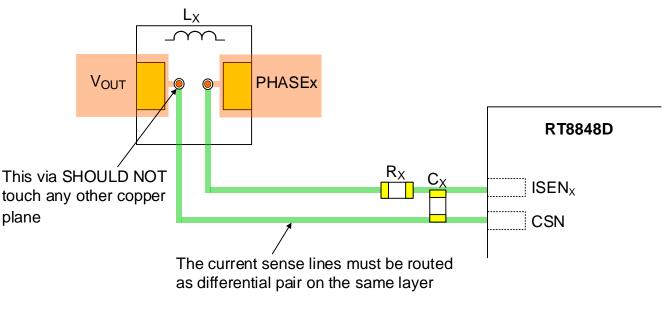

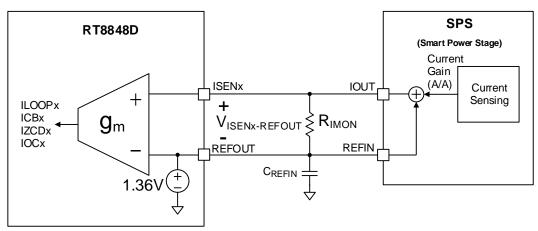

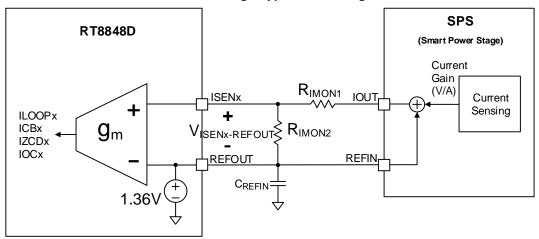

| 13 to 20 | ISEN8 to ISEN1 | Current sense inputs of phase 1 to phase 8. These pins can be used for differentially sensing output current from DCR current sensing network or connecting to IMON output pin of SPS (Smart Power Stage) for each phase. DO NOT add additional RC filter.<br>Besides, the ISENx pins can also be used for hardware setting of maximum phase number. When ISENx pin is pulled up to VCC with a $100k\Omega$ resistor, the PHASEx is disabled and the maximum phase number reduces to X-1. For example, if ISEN7 pin is pulled up to VCC, the maximum phase number is 6. Both PHASE7 and PHASE8 are disabled. |

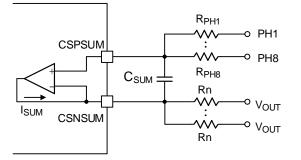

| 21       | CSNSUM         | Inverting input of total current sense amplifier. DO NOT add RC filter on this pin. Only add a decoupling cap. (10nF/0603) to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 22       | CSPSUM         | Non-inverting input of total current sense amplifier. DO NOT add additional RC filter on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 23       | REFOUT         | Reference output pin. As for SPS application by setting the PINSET1 to SPS mode, REFOUT outputs 1.38V (typ.) to the REFIN pin of SPS. Connect a $0.47\mu$ F/0603 decoupling capacitor near this pin, and the equivalent capacitance on this pin should be limited at ±10% of $0.47\mu$ F. Besides, as for DCR current sensing application by setting the PINSET1 to DCR mode, REFOUT is regarded as an input pin and it should be connected to the positive terminal of output capacitor. A small decoupling capacitor (10nF/0603) to GND is necessary.                                                      |

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24      | PINSET1  | PINSET 1 I/O pin. Connect a pair of voltage divider to adjust the internal function setting for "internal ramp amplitude", "soft-start slew rate", "PWM high-Z level", "AI gain" and "SPS selection". The design value of resistors is detailed in Application Information section. Moreover, DO NOT put any decoupling capacitor near this pin.                                                                                                                                                                                 |

| 25      | IMON     | Output current monitor. The output current of this pin is proportional to<br>the total load current. The total load current is sensed and flows out of<br>this pin, and a resistor from this pin to GND makes the IMON voltage<br>proportional to the total output current. The IMON resistor selection<br>should follow the application type (SPS or DCR). The guide is introduced<br>in Application Information section. Do not put any decoupling capacitor<br>near this pin since it affects the accuracy of IMON reporting. |

| 26      | PINSET2  | PINSET 2 I/O pin. Connect a pair of voltage divider to adjust the internal function setting for "per-phase switching frequency", "slave device address code", "middle drive control" and "operation phase number as PSI = L". The design value of resistors is detailed in Application Information section. Moreover, DO NOT put any decoupling capacitor near this pin.                                                                                                                                                         |

| 27      | VIN      | VIN monitor pin. It is recommended to place a RC filter before VIN pin for stable operation. The suggested design value of RC filter is R = $2.2\Omega/0603$ and C = $1\mu$ F/0603.                                                                                                                                                                                                                                                                                                                                              |

| 28      | PINSET3  | PINSET 3 I/O pin. Connect a pair of voltage divider to adjust the internal function setting for "auto phase shedding current threshold" and "soft-start phase number during cold-boot and warm-boot". The design value of resistors is detailed in Application Information section. Moreover, DO NOT put any decoupling capacitor near this pin. If PISET3 is not used, please leave this pin floating and DO NOT short this pin to GND.                                                                                         |

| 29      | COMP     | Output of control loop error amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 30      | FB       | Inverting input of the error amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

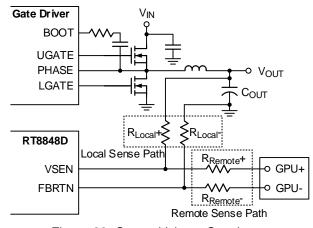

| 31      | VSEN     | Output voltage sensing input. This pin is the positive input from differential output voltage remote sense. Connect to the positive terminal of output capacitors at GPU side with a resistor ( $0\Omega/0603$ ) for OVP and UVP detection. Besides, to prevent output overvoltage when GPU is disconnected, connect to positive terminal of output capacitors at local side with a resistor ( $100\Omega/0603$ ).                                                                                                               |

| 32      | FBRTN    | Output voltage feedback return. This pin is the negative input from differential output voltage remote sense. Connect to the remote sensing ground at GPU side with a resistor ( $0\Omega/0603$ ). Besides, to prevent output overvoltage when GPU is disconnected, connect to output capacitors' ground at local side with a resistor ( $100\Omega/0603$ ).                                                                                                                                                                     |

| 33      | TSEN     | Thermal monitor input. Connect a voltage divider with a NTC thermistor<br>for VR temperature sensing or connect to the DrMOS's temperature<br>monitor output.                                                                                                                                                                                                                                                                                                                                                                    |

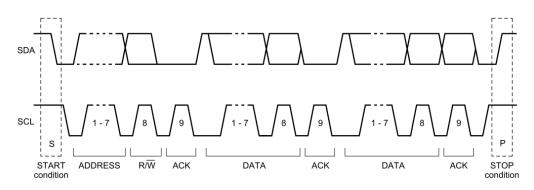

| 34      | SDA      | I <sup>2</sup> C data pin. This pin is the input and output of serial bus data signal.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 35      | SCL      | I <sup>2</sup> C clock pin. This pin is the input of serial bus clock signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 36      | EN       | Enable control input. Connect a resistor (R = $60k\Omega/0603$ ) to GND in parallel with a NMOS switch. As EN voltage is lower than 0.3V, RT8848D is in shutdown mode and all power rails are disabled. As EN is higher than 1.8V, RT8848D wakes up.                                                                                                                                                                                                                                                                             |

| RT | 8848 | D |

|----|------|---|

|----|------|---|

| Pin No.          | Pin Name | Pin Function                                                                                                                                                                                                                                                                          |

|------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37               | PSI      | Power state input. Depending on different input voltage levels of PSI, the controller can be operated in full phase mode (PSI > 1.6V), auto-phase shedding mode ( $0.8V < PSI < 1.2V$ ) or low phase count mode (PSI < 0.4V) separately.                                              |

| 38               | PGOOD    | Power good indicator. This open-drain is pulled low as UVP, OVP, OTP, EN low and output voltage is not regulated (such as before soft-start). An external pull-up resistor to VCC or other external rail is required, and a $10k\Omega$ pull-up resistor is recommended.              |

| 39               | PWMVID   | PWMVID input pin. The reference of output voltage can be programmed by adjusting the PWMVID input signal.                                                                                                                                                                             |

| 40               | REFADJ   | PWMVID output pin for output reference adjustment. Connect this pin with a RC filter to generate REFIN voltage. The recommended RC value is R = $6.19k\Omega$ (0603) and C = $4.7nF(0603)$ . Please refer to Application Information section for further information about RC filter. |

| 41 (Exposed Pad) | GND      | Ground. The exposed pad is the ground of logic control circuits. For<br>better power dissipation, it should be soldered to a large ground plane<br>with enough thermal vias.                                                                                                          |

### **Functional Block Diagram**

### RT8848D

### Operations

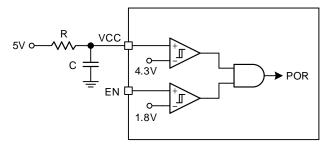

#### VCC Power-On Reset (POR), UVLO

The power ready detection circuit is shown in Figure 1. The VCC voltage is monitored for power-on reset with typically 4.3V rising edge threshold. There is around 200mV hysteresis voltage for the comparator. When VCC is above POR threshold, the controller starts up after EN is higher than 1.8V. In contrast, as EN pin is driven below 0.3V, the controller will be turned off, and all fault states are cleared. Moreover, for avoiding noise disturbance, the supplied bias voltage must be stable. A RC filter (R =  $2.2\Omega/0603$  and C =  $1\mu F/0603$ ) from bias voltage to VCC pin is necessary, and should be placed as close as possible to VCC pin. There is around 50mA sink current during POR duration, the maximum resistance of RC filter should be smaller than  $2.2\Omega$ .

Figure 1. Circuit of Power Ready Detection

#### **EN Control Circuit**

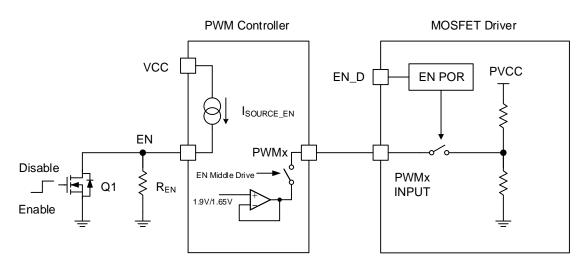

As PWM controller's VCC is higher than POR threshold (typically 4.3V), an internal ISOURCE\_EN current is generated. A simplified enable sequence control circuit is shown in Figure 2. There is a MOSFET, Q1, in parallel with REN to control the high/low status of EN. For first power-on, as Q1 is open, a source current (ISOURCE\_EN) flows through REN to GND to enable the controller, and the initial value of ISOURCE\_EN is 10µA during pin setting detection process. At the end of pin setting process, the ISOURCE\_EN increases to  $90\mu$ A and VEN is clamped by VCC at 4.5V. The controller will follow the power-on sequence setting to ramp up the output voltage with a determined ramp up slope (Please refer to the Power-On Sequence section). The recommended design value of REN is  $60k\Omega$ .

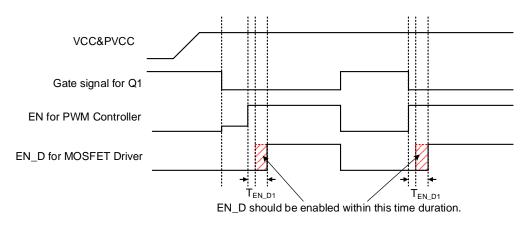

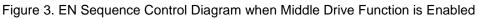

Besides, the RT8848D also offers a special Middle drive function to drive the PWM voltage at tri-state level to turn off both high-side and low-side MOSFETs. This function can be enabled or disabled by I<sup>2</sup>C register 0x43[3] or PINSET2. For most of drivers or DrMOSs in the market, they have built-in pull high and pull low resistors connected to PWM pins, therefore, the Middle drive function is not necessary. For some special products without internal driving capability for tri-state voltage, the Middle drive function can help to drive PWM pin at correct voltage level for normal operation. However, there is one important thing to be noticed for applying Middle drive function to DrMOS. Because of Middle drive function is disabled when controller EN logic is low, it requires around 50µs to reboot for normal operation. Therefore, the driver enable (EN\_D) and the controller EN should be synchronized to prevent the unknown operation during Middle drive reboot duration. The sequence of EN and EN\_D should follow the sequence as depicted in Figure 3. The delay time (T<sub>EN D1</sub>) from EN high to EN D high should be larger than 60µs and smaller than 100µs to prevent abnormal operation. On the other hand, for the applications without Middle drive function, the only sequence requirement between driver and controller is that the EN D of driver should be high 100µs (TEN D2) before controller EN logic goes high as shown in Figure 4.

Figure 2. Enable Sequence Control Circuit

Figure 4. EN Sequence Control Diagram when Middle Drive Function is Disabled

Copyright © 2022 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

DS8848D-00

November 2022

## RT8848D

#### Power-On and Power-Off Sequence

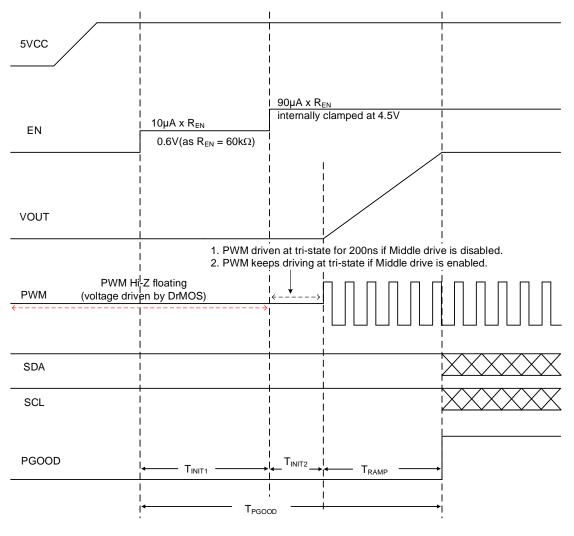

The RT8848D features a programmable soft-start function to limit the inrush current from power supply input. During the first power-on, the controller starts pin setting process when VEN > 0.5V within typical 0.5ms initialization time (TINIT1), where VEN is established by a sourcing current ISOURCE\_EN =  $10\mu$ A flowing through REN. After the end of pin setting process, the ISOURCE\_EN increases to 90uA and the VEN is clamped by VCC at 4.5V. When VEN >1.8V, there is an around 200µs delay time (TINIT2) before the controller starts soft-start process. In the 200µs delay time, the controller keeps the PWM pins in high-impedance status and REFOUT outputs to 1.38V (typ.) if SPS mode is applied. The ramping up slew rate (SRRAMP) of output voltage during soft-start process is determined by PINSET1 and can be modified by  $I^2C$  register 0x40[1]. The recommended soft-start slew rate is 1.5mV/µs for reducing inrush current during power-on. As output voltage reaches to VREFIN after soft-start process, PGOOD will be pulled high by external voltage source with a resistor. The power-on sequence of RT8848D at first power-on is shown in Figure 5. Generally, the duration of power-on sequence from EN goes high to PGOOD goes high is less than 1.5ms. Besides, the  $I^2C$  R/W access can only work after the end of VR power-on sequence. It should be noticed that the Middle drive function is default disabled at first power-on. The Middle drive function will be activated after finishing pin setting process and provide driving capability for PWM pins.

Copyright © 2022 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

## RICHTEK

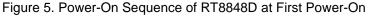

Moreover, if RT8848D is powered up through EN re-toggle after first power-on, there is no pin setting process during power-on sequence. VEN is directly established by a sourcing current ISOURCE\_EN =  $90\mu$ A flowing through REN. When VEN > 1.8V, there is an around 200 $\mu$ s delay time (TINIT2) before the controller starts soft-start process. In the 200 $\mu$ s delay time, the controller keeps the PWM pins in tri-state status and REFOUT outputs to 1.38V (typ.) if SPS mode is applied. The ramping up slew rate (SRRAMP) of output voltage

during soft-start process follows the PINSET1 setting, which is detected at first power-on. The power-on sequence of RT8848D by EN re-toggle after first power-on is shown in Figure 6. It should be noticed that the  $I^2C$  registers keep the data unless VCC power recycle and  $I^2C$  R/W access only works after VR power-on sequence. It should also be noticed that the EN control sequence between the controller and driver should follow EN signal control diagram as shown in Figure 3 if Middle drive function is necessary.

Figure 6. Power-On Sequence of RT8848D by EN re-toggle After First Power-On

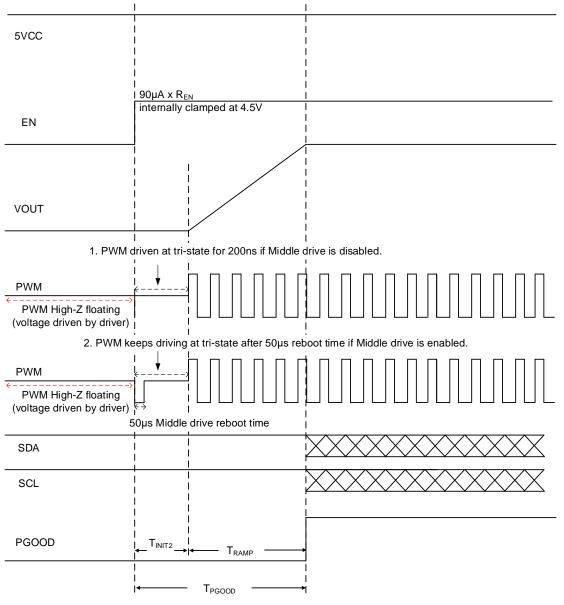

As VEN is pulled down to below 0.3V by external resistor or switch, the controller stops switching after 300ns delay and keeps all PWM output in tri-state. At the moment, the PGOOD signal is also pulled down by internal open-drain switch. In order to prevent short through from high-side MOSFET to low-side MOSFET, the PWM outputs a short low pulse before entering tri-state when PGOOD goes low. As a result, an internal switch will be turned on to

discharge the output capacitors through the route from VSEN trace to GND. The discharge impedance is around 70 $\Omega$ . Besides, for the application of SPS mode, the REFOUT is also discharged by an internal resistor when EN goes low. The power-off sequence of RT8848D by EN is shown in Figure 7.

Figure 7. Power-Off Sequence of RT8848D by EN

#### **PWMVID Function**

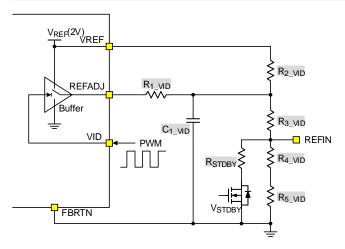

The RT8848D supports PWMVID function to dynamically adjust the REFIN voltage for different GPU operating conditions. As shown in Table 8, a PWMVID circuit consists of a PWM buffer, a bias VREF voltage and a RC filter. An external PWM signal is applied to VID pin, which controls the PWM buffer output's high/low status. The output of buffer(REFADJ) is integrated by the external RC filter, and divided by a resister network to achieve reference voltage(REFIN). The voltage of REFIN can be calculated as :

$$V_{\text{REFIN}} = V_{\text{REF}} \times D \times \frac{R_{2\_\text{VID}} // (R_{3\_\text{VID}} + R_{4\_\text{VID}} + R_{5\_\text{VID}})}{R_{1\_\text{VID}} + R_{2\_\text{VID}} // (R_{3\_\text{VID}} + R_{4\_\text{VID}} + R_{5\_\text{VID}})} \times \frac{R_{4\_\text{VID}} + R_{5\_\text{VID}}}{R_{3\_\text{VID}} + R_{4\_\text{VID}} + R_{5\_\text{VID}})} + \frac{R_{4\_\text{VID}} + R_{5\_\text{VID}}}{R_{4\_\text{VID}} + R_{4\_\text{VID}} + R_{5\_\text{VID}}} \times \frac{R_{4\_\text{VID}} + R_{5\_\text{VID}}}{R_{4\_\text{VID}} + R_{5\_\text{VID}} + R_{4\_\text{VID}} + R_{5\_\text{VID}}} \times \frac{R_{4\_\text{VID}} + R_{5\_\text{VID}}}{R_{4\_\text{VID}} + R_{4\_\text{VID}} + R_{5\_\text{VID}}} \times \frac{R_{4\_\text{VID}} + R_{5\_\text{VID}}}{R_{4\_\text{VID}} + R_{5\_\text{VID}} + R_{4\_\text{VID}} + R_{5\_\text{VID}}} \times \frac{R_{4\_\text{VID}} + R_{5\_\text{VID}}}{R_{4\_\text{VID}} + R_{4\_\text{VID}} + R_{5\_\text{VID}}}}$$

Figure 8. PWMVID Circuit

where VREF is the bias reference voltage (typically 2V), and D is the duty cycle of PWM input signal. For internal LDO compensation, a decoupling capacitor of  $0.1\mu$ F/0603 between VREF pin and local GND is necessary.

For PWMVID dynamic output voltage transition, the settling time that the output voltage transits from the old voltage to a new voltage depends on the time constant of PWMVID circuit, which can be calculated as :

$\tau = R_1 \text{ VID} / / R_2 \text{ VID} / (R_3 \text{ VID} + R_4 \text{ VID} + R_5 \text{ VID}) \times C_1 \text{ VID}$ The settling time TSET VID of REFIN transition is around 5 times of  $\tau$  which is independent of the voltage step size and PWM frequency.

#### $T_{SET VID} = 5 \times \tau$

Moreover, it should be noticed that the PWMVID function is only active after PGOOD goes high. Before activating PWMVID function, the REFADJ pin keeps at high impedance status.

#### **BOOT Mode and Standby Mode**

There are two operation modes included in PWMVID structure: boot mode and standby mode. In boot mode, the operation of output voltage ramps up in a power-on sequence. During boot mode, the controller ignores the PWMVID signal, and REFADJ enters high-impedance status before PGOOD goes high. The operating phase number in boot mode can be set via PINSET3 or I<sup>2</sup>C register 0x45[3:1].

During standby mode, GPU stops the PWMVID transaction and sends a standby control signal to enter standby mode. An additional switch in parallel with original PWMVID resistors will be switched on to

reduce the REFIN voltage. When VREFIN is lower than 0.15V, the controller enters standby mode and all PWM outputs enter tri-state. On the other hand, the controller exits standby mode once VREFIN is higher than 0.2V as standby control signal is released. The controller follows I<sup>2</sup>C register 0x45[3:1] setting to decide the phase number during VOUT reboot. Besides, the PGOOD signal keeps high in standby mode. The VREFIN in standby mode can be calculated as the following equation shows :

$V_{\text{REFIN}} = V_{\text{REF}} \times \frac{R_{\text{STDBY}} // (R_{4\_\text{VID}} + R_{5\_\text{VID}})}{R_{2\_\text{VID}} + R_{3\_\text{VID}} + R_{\text{STDBY}} // (R_{4\_\text{VID}} + R_{5\_\text{VID}})}$

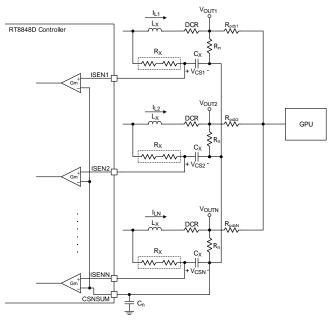

#### Current Balance

The RT8848D senses each phase current through ISENx pin for current balance. The sensed current ICBx is mirrored to the current balance circuit. comparing with the average current, and adjusting each phase PWM width to optimize current and thermal balance. The current balance circuit increases the duty cycle of the phase which has smaller phase current as compared to other rails and decreases the duty cycle of the phase which has larger phase current. In addition, there are some registers for improving the current balance performance when the default setting cannot achieve good current balance result. The current balance gain and current balance offset can be adjusted through I<sup>2</sup>C register 0x11~0x20. The settings for each register are summarized at the section of register tables below. It increases current balance gain of the phase which has larger current than other rails or reduces current balance gain of the phase which has smaller current than other rails. If current balance cannot be improved by adjusting current balance gain. add an offset on the phase which has larger phase current than other rails. Moreover, the RT8848D also provides total current balance gain settings (0x55[4:3], 0x5F[1:0]) to add more flexibility on improving the current balance result with different board layout conditions.

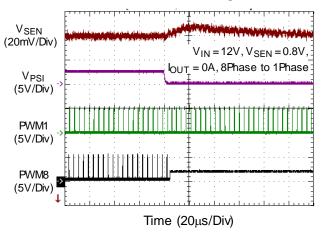

#### **Power State Input**

The RT8848D supports automatic phase shedding and adjustable high/low phase count according to PSI input voltage. There are three operation modes: High Phase Count (HPC) mode, Auto Phase Shedding (APS) mode

Copyright © 2022 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. www.richtek.com

## RICHTEK

#### and Low Phase Count (LPC) mode.

Table 1 shows recommended PSI setting voltage threshold of the three operation modes. In LPC mode, the operation phase number is determined by PINSET2 or  $I^2C$  register 0x4F[6:4]. The operation phase number with respect to register settings are listed in Table 2. In APS mode, the operation phase number dynamically

increases or decreases depending on output load current. In HPC mode, the controller operates in maximum phase number, which is determined by detecting the status of ISENx pins during PWM pin setting process at first power-on.

| •                        |                     |

|--------------------------|---------------------|

| Operation Mode           | PSI Voltage Setting |

| High Phase Count Mode    | 1.6V to 5.5V        |

| Auto Phase Shedding Mode | 0.8V to 1.2V        |

| Low Phase Count Mode     | 0V to 0.4V          |

Table 2 Operation Phase Number Setting in LPC Mode

#### Table 1. Operation Mode and PSI Voltage Setting

| Low Phase Count Register 0x4F[6:4] |     |  |  |  |  |  |

|------------------------------------|-----|--|--|--|--|--|

| 1Phase                             | 000 |  |  |  |  |  |

| 2Phase                             | 001 |  |  |  |  |  |

| 3Phase                             | 010 |  |  |  |  |  |

| 4Phase                             | 011 |  |  |  |  |  |

| 5Phase                             | 100 |  |  |  |  |  |

| 6Phase                             | 101 |  |  |  |  |  |

| 7Phase                             | 110 |  |  |  |  |  |

| 8Phase                             | 111 |  |  |  |  |  |

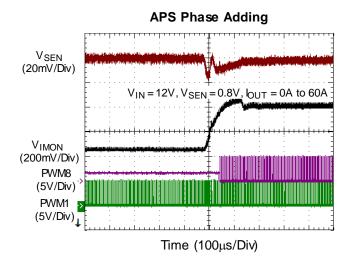

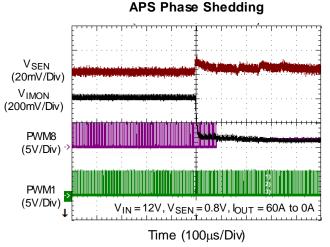

#### Auto Phase Shedding

The RT8848D provides Auto Phase Shedding (APS) function to dynamically change operating phase number depending on different output currents. The switching loss and conduction loss can be reduced in light load by reducing the phase number to improve light load efficiency. Moreover, the system efficiency can be optimized through changing phase number according to output load. The APS function is active when the following conditions are satisfied :

1. PSI pin voltage is within 0.8V to 1.2V.

2. APS function works as PGOOD goes high after power-on sequence

During the PWM pin setting process at first power-on, the APS current thresholds (APL1/APL2/APL3/APL4) are determined by PINSET3. After power-on, the APS current thresholds (APL1~APL4) can be modified by  $I^2C$  registers (0x01~0x04) respectively. The hysteresis of APL1/APL2/APL3/APL4 and operating phase number at each stage are also programmable through  $I^2C$  registers (0x05~0x08, 0x09~0x0D) as shown in Table 3 and Table 4. The APL1~APL4 thresholds can be calculated as :

VAPL1 = DEC(0x01[7:0]) x 12.5mV

VAPL2 = DEC(0x02[7:0]) x 12.5mV

VAPL3 = DEC(0x03[7:0]) x 12.5mV

VAPL4 = DEC(0x04[7:0]) x 12.5mV

Copyright © 2022 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

The VIMON reporting value is applied to compare with each APL threshold to change the phase number with regard to register setting. There are five current zones summarized as below :

If VIMON < VAPL1, the controller operates in phase number PH\_LCS0 as addressed in register 0x0D.

If VAPL1 < VIMON < VAPL2, the controller operates in phase number PH\_LCS1 as addressed in register 0x0C.

If VAPL2 < VIMON < VAPL3, the controller operates in phase number PH\_LCS2 as addressed in register 0x0B.

If VAPL3 < VIMON < VAPL4, the controller operates in phase number PH\_LCS3 as addressed in register 0x0A.

If  $V_{IMON} > V_{APL4}$ , the controller operates in phase number PH\_LCS4 as addressed in register 0x09.

When setting the operating phase number of each current zone, always keep the following rules :

$Rule1: PH\_LCS0 \leq PH\_LCS1 \leq PH\_LCS2 \leq PH\_LCS3 \leq PH\_LCS4$

Rule2:  $V_{APL1} \le V_{APL2} \le V_{APL3} \le V_{APL4}$

If violating either rule1 or rule2, the controller is forced into full phase operation mode. It requires to reboot VCC to unlock the APS logic latch in full phase mode.

The RT8848D also supports Soft Phase Shedding Down that there is a delay time (default =  $80\mu$ s) within each phase zone transition to prevent output undershoot or overshoot from PSI switching during down phase shedding. The delay time is configurable through I<sup>2</sup>C register 0x5D[2:0].

|         |                       | , 0                       | 5                     |                       |  |  |

|---------|-----------------------|---------------------------|-----------------------|-----------------------|--|--|

|         |                       | I <sup>2</sup> C Register |                       |                       |  |  |

| APL_HYS | APL_HYS1<br>0x05[2:0] | APL_HYS2<br>0x06[2:0]     | APL_HYS3<br>0x07[2:0] | APL_HYS4<br>0x08[2:0] |  |  |

| 0mV     | 000                   | 000                       | 000                   | 000                   |  |  |

| 12.5mV  | 001                   | 001                       | 001                   | 001                   |  |  |

| 25mV    | 010                   | 010                       | 010                   | 010                   |  |  |

| 37.5mV  | 011                   | 011                       | 011                   | 011                   |  |  |

| 50mV    | 100                   | 100                       | 100                   | 100                   |  |  |

| 62.5mV  | 101                   | 101                       | 101                   | 101                   |  |  |

| 75mV    | 110                   | 110                       | 110                   | 110                   |  |  |

| 87.5mV  | 111                   | 111                       | 111                   | 111                   |  |  |

Table 3. APL Hysteresis Register Setting

#### Table 4. Operating Phase Number in Each Current Zone

|                 | I <sup>2</sup> C Register |             |         |             |                      |             |     |

|-----------------|---------------------------|-------------|---------|-------------|----------------------|-------------|-----|

| Phase<br>Number | PH_LCS0<br>0x0D[2:0]      |             |         |             | PH_LCS4<br>0x09[2:0] |             |     |

| 1Phase          | 000                       |             |         | 000 000 000 | 000 000 000          | 000 000 000 | 000 |

| 2Phase          | 001                       | 001 001 001 | 001     | 001         |                      |             |     |

| 3Phase          | 010                       | 010         | 010     | 010         | 010                  |             |     |

| 4Phase          | 011                       | 011         | 011     | 011         | 011                  |             |     |

| 5Phase          | 100                       | 100 100 1   |         | 100         | 100                  |             |     |

| 6Phase          | 101                       | 101         | 101 101 | 101         | 101                  |             |     |

| 7Phase          | 110                       | 110         | 110     | 110         | 110                  |             |     |

| 8Phase          | 111                       | 111         | 111     | 111         | 111                  |             |     |

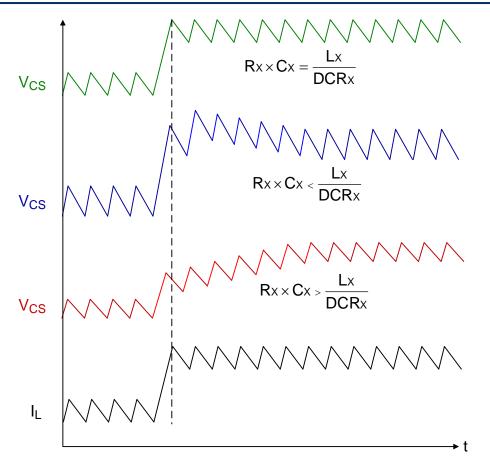

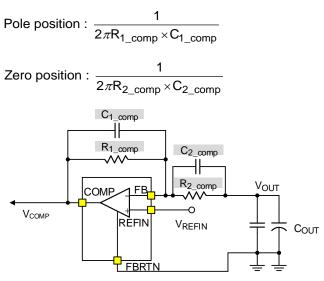

#### AC Droop

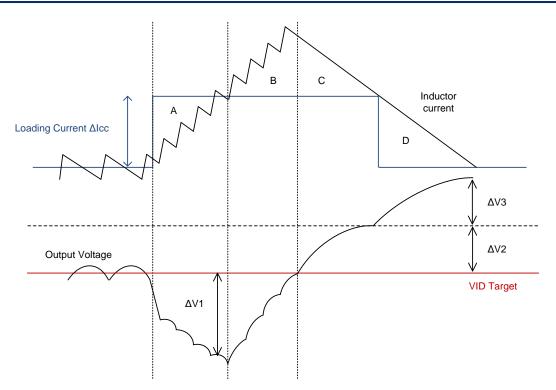

The RT8848D adopts an outstanding feature, i.e. AC-droop, to effectively suppress load transient ring back and to control overshoot well for zero loadline application. Figure 9 shows the condition without AC-droop control. The output voltage without AC-droop control has extra ring back  $\Delta$ V2 due to C area charge.

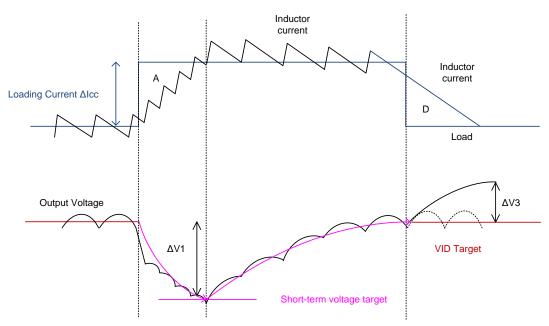

Figure 10 shows the condition with AC-droop control. While loading occurs, the controller temporarily changes VID target to short-term voltage target. Short-term voltage target is related to transient loading current  $\triangle$ ICC and can be represented as the following :

Short\_Term\_Voltage\_Target

DCR type

$\mathsf{AC\_DROOP} = \mathsf{V}_{\mathsf{CS\_SUM}} \times \frac{\mathsf{AI\_SET}}{\mathsf{AV}} = \frac{\mathsf{I}_{\mathsf{OUT\_SUM}} \times \mathsf{DCR}}{\mathsf{N}} \times \frac{\mathsf{AI\_SET}}{\mathsf{AV}}$

N = phase number, AV = EA gain = R1\_comp/R2\_comp

AI\_SET = 48/24/12/6

SPS type

$AC\_DROOP = \frac{V_{CS\_SUM}}{8} \times \frac{AI\_SET}{AV} = \frac{I_{OUT\_SUM} \times DCR}{8} \times \frac{AI\_SET}{AV}$

AI\_SET = 12/6/3/2

$AV = EA\_GAIN = R_1\_comp/R_2\_comp$

where the Vcs\_sum is the sum of current sensing signal from DCR sensing or SPS current sensing. For DCR sensing, the Vcs\_sum = VcsPsum - VcsNsum = IouT\_sum x DCR/N. The current gain (AI) can be set by Pin Setting of AI Gain. Users can adjust AI gain by I<sup>2</sup>C register 0x41[3:2] to set desired short-term voltage target. The short-term voltage target reverts to VID target slowly after approximately 100 $\mu$ s. The short-term voltage target can help inductor current not to exceed loading current too much and then the ring back can be suppressed. Referring to Figure 10, the overshoot amplitude is reduced to only  $\Delta$ V3.

Figure 9. Zero Loadline without AC-droop Control

Figure 10. Zero Loadline with AC-droop Control

#### **Power Good**

The PGOOD pin is an open-drain output, and requires a pull-up resistor ( $10k\Omega/0603$ ). During soft-start time period, the PGOOD remains low. When the output voltage reaches to REFIN voltage, PGOOD is pulled high and latched. If one of the protections (OVP/UVP/SOC/TSEN/OTP) is triggered or EN goes low during operation, the PGOOD will be pulled low immediately.

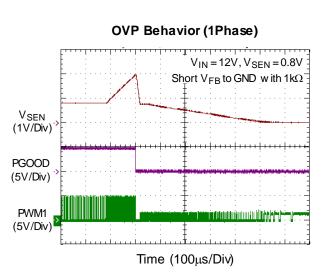

#### **Output Over-Voltage Protection (OVP)**

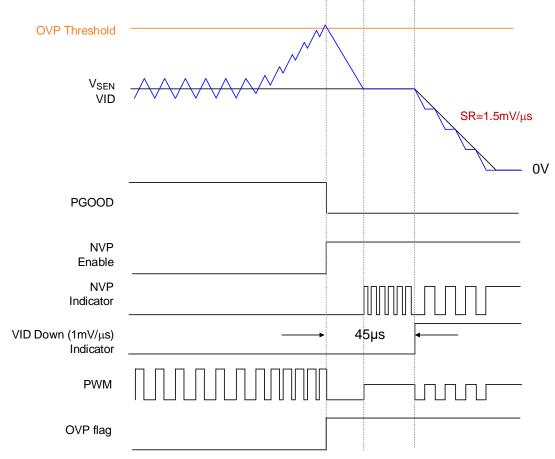

In order to prevent abnormal output high voltage which may induce catastrophic damage on chip or power devices, the RT8848D features an output OVP mechanism. According to different VREFIN voltage setup, the OVP threshold has two methods to define. First, if VREFIN is lower than 1.33V, the OVP threshold is fixed at absolute OVP protection threshold (typically 2V, programmable by I<sup>2</sup>C register 0x25[1:0]). Second, if VREFIN is higher than 1.33V, the OVP threshold is a relative OVP protection threshold, which equals to 1.5 times VREFIN (the weighting factor is programmable by I<sup>2</sup>C register 0x26[1:0]). A typical OVP protection mechanism is shown in Figure 11. When VSEN is larger than OVP threshold for longer than 1µs deglitch time, the OVP protection is triggered. In the moment, the PGOOD is pulled down and NVP function is enabled. The OVP status is also recorded in I<sup>2</sup>C register 0x2A[0]. After NVP function is enabled, the controller holds PWM at low status to discharge output capacitors until

### reaching VID reference. Besides, in order to prevent over large negative inductor current that may damage MOSFETs or driver, the controller switches PWM in tri-state or low pulse to regulate the output voltage at VID reference within 45 $\mu$ s before VID down. After 45 $\mu$ s delay time from the beginning of OVP triggering point, the controller starts to discharge the output voltage with a slow ramping down slew rate (1.5mV/ $\mu$ s). Within the soft-stop process, the controller holds PWM in tri-state as VSEN is higher than VID reference and holds PWM in low status as VSEN is larger than VID reference. Once OVP is triggered, the controller needs to re-toggle EN or re-cycle VCC to release from latched mode and clear I<sup>2</sup>C flag 0x2A[0].

Moreover, the OVP function can be enabled or disabled through  $I^2C$  register 0x29[0]. It should be noticed that only analog OVP protection function can be disabled, the digital indicator of OVP (0x2A[0]) will be asserted if OVP is detected.

Figure 11. Output Over-Voltage Protection Mechanism

## RT8848D

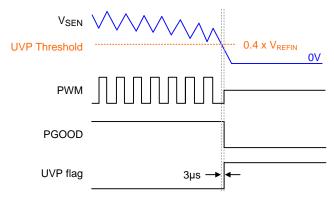

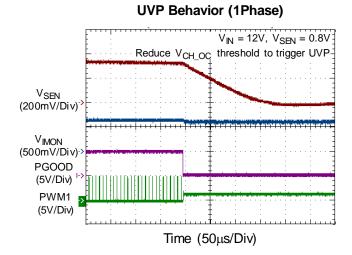

#### **Output Under-Voltage Protection (UVP)**

In order to prevent power stages from over-heating because of output voltage clamped by OCP, the RT8848D features an output UVP mechanism. A typical UVP protection mechanism is shown in Figure 12. If the output voltage drops below UVP trip threshold for longer than 3µs (typical), the UVP is triggered, and the controller forces all PWM outputs to tri-state, and an internal switch will be turned on to discharge the output capacitors through the route from VSEN trace to GND. The discharge impedance is around  $70\Omega$ . At the same time, the PGOOD is pulled down, and the UVP status is recorded in I<sup>2</sup>C register 0x2A[1]. Besides, the UVP threshold is programmable through I<sup>2</sup>C register 0x27[1:0]. The default threshold is 0.4 times VREFIN. Once UVP is triggered, the controller needs to re-toggle EN or re-cycle VCC to release from latched mode and clear I<sup>2</sup>C flag 0x2A[1].

Moreover, the UVP function can be enabled or disabled through I<sup>2</sup>C register 0x29[1]. It should be noticed that only analog UVP protection function can be disabled, and the digital indicator of UVP (0x2A[1]) will be asserted if UVP is detected. The UVP protection is masked during power-on sequence before PGOOD goes high.

Figure 12. Typical UVP Protection Mechanism

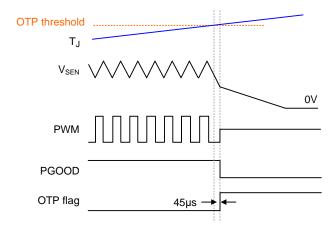

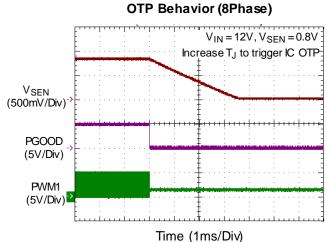

#### **Over-Temperature Protection (OTP)**

The RT8848D features an OTP circuitry to prevent die overheating due to excessive power dissipation. A typical OTP protection mechanism is shown in Figure 13. When die temperature exceeds 150°C (programmable through  $I^2C$  register 0x28[1:0]) for longer than 45µs deglitch time, the controller forces all

PWM outputs to tri-state. At the moment, the PGOOD is pulled down and the OTP status is recorded in I<sup>2</sup>C register 0x2A[3]. For continuous operation, provide adequate cooling so that the junction temperature does not exceed OTP threshold. Once OTP is triggered, the controller needs to re-toggle EN or re-cycle VCC to release from latched mode and clear I<sup>2</sup>C flag 0x2A[3].

RICHTEK

Moreover, the OTP function can be enabled or disabled through I<sup>2</sup>C register 0x29[3]. It should be noticed that only analog OTP protection function can be disabled, and the digital indicator of OTP (0x2A[3]) will be asserted if OTP is detected.

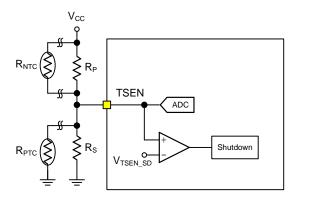

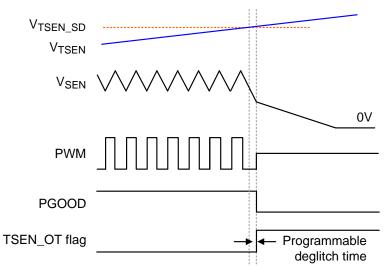

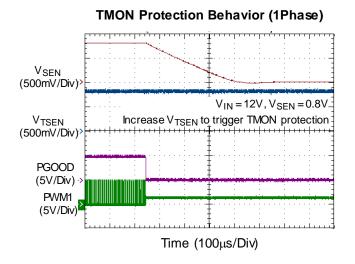

#### **TSEN Over-Temperature Protection (TSEN OTP)**

The RT8848D features TSEN protection function which monitors the local temperature of power stages (MOSFETs or power inductors) during heavy load operation to prevent devices from overheating and catastrophic damage. According to operation modes of the controller, the TSEN protection can be categorized as DCR mode application and SPS mode application. As shown in Figure 14, the VTSEN voltage is generated by a voltage divider. For different thermistor selection, the temperature can be monitored by a NTC or a PTC. For NTC case, a NTC thermistor is suggested to be placed near the hottest point of the power stage and in parallel with RP, generally close to the power inductor and low-side MOSFET at phase 1. Besides, for PTC case, a PTC thermistor should be placed in parallel with Rs and near the hottest point of the power stage. For both cases, as temperature rises, the VTSEN increases. The VTSEN voltage is then converted to 8-bit

### RT8848D

digital data by internal ADC converter. The ADC result is compared with VTSEN shutdown threshold, VTSEN\_SD, to trigger the protection mechanism. If VTSEN is higher than VTSEN\_SD (VTSEN\_SD = 0.8V) for longer than deglitch time, which is programmable through I<sup>2</sup>C register 0x33[1:0], the controller forces all PWM outputs to tri-state. At the moment, the PGOOD is pulled down and the TSEN OTP status is recorded in I<sup>2</sup>C register 0x2A[4]. The protection mechanism is shown in Figure 16.

For PTCthermistor case,  $V_{TSEN} = \frac{(R_S / / R_{PTC})}{R_P + (R_S / / R_{PTC})} \times V_{CC}$

For NTCthermistor case, V<sub>TSEN</sub> =  $\frac{R_S}{R_S + (R_P /\!/ R_{NTC})} \times V_{CC}$

Figure 14. TSEN Pin Application Circuit in DCR Mode

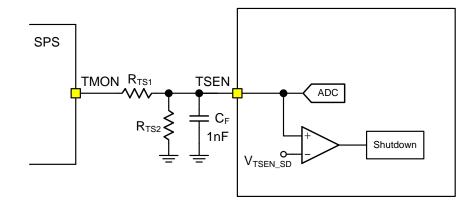

On the other hand, Figure 15 shows a SPS mode application. The TSEN pin is connected to the TMON pin of SPS IC with a decoupling capacitor (CF = 1nF/0603/6.3V) placed at local side of the controller to reduce noise coupling through layout trace. Generally, the temperature characteristic of SPS's TMON reporting is positive temperature coefficient. Therefore, as temperature rises, the VTSEN increases. The VTSEN voltage is then converted to 8-bit digital data by internal ADC converter. The ADC result is compared with VTSEN shutdown threshold, VTSEN\_SD, to trigger the protection mechanism. If VTSEN is larger than VTSEN\_SD (VTSEN\_SD = 0.8V) for longer than deglitch time, which is programmable through I<sup>2</sup>C register 0x33[1:0], the controller forces all PWM outputs to tri-state. At the moment, the PGOOD is pulled down, and the TSEN OTP status is recorded in I<sup>2</sup>C register 0x2A[4]. Besides, the design of RTS1 and RTS2 are based on the transfer function of TJ and VTMON from SPS's datasheet. The protection mechanism is shown in Figure 16.

$$V_{\text{TSEN}} = \frac{R_{\text{TS2}}}{R_{\text{TS1}} + R_{\text{TS2}}} \times V_{\text{TMON}}$$

Figure 15. TSEN Pin Application Circuit in SPS Mode

Figure 16. TSEN OTP Protection Mechanism with NTC or PTC

For both SPS mode and DCR mode, the controller needs to re-toggle EN or re-cycle VCC to release from latched mode and clear I<sup>2</sup>C flag 0x2A[4] after TSEN OTP is triggered. Moreover, the TSEN OTP function can be enabled or disabled through I<sup>2</sup>C register 0x29[4]. It should be noticed that only analog TSEN OTP protection function can be disabled, the digital indicator of TSEN OTP (0x2A[4]) will be asserted if TSEN OTP is detected.

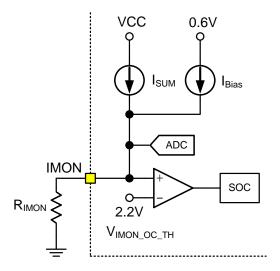

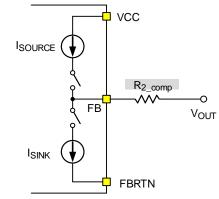

#### Sum Over-Current Protection (SOCP)

The RT8848D provides Sum Over-Current Protection (SOCP) to prevent power system from over-current operation. The SOCP protection circuit is shown in Figure 17. First, the per-phase inductor currents are added together to generate a mirrored current ISUM. The ISUM is in parallel with a IBIAS, which provides a fixed 0.6V offset on VIMON, and flowing out from IMON

pin to an external resistor, RIMON. The voltage across RIMON is then converted to 8-bit digital data by internal ADC converter. The ADC result is compared with SOCP threshold, VIMON\_OC\_TH (programmable through I<sup>2</sup>C register 0x24[5:0]), to trigger the protection mechanism. According to the application type (SPS type or DCR type), the VIMON has different calculation formulas. The formulas are demonstrated as below :

For SPS type, VIMON (V) = VCs\_SUM (V)/8 x 1.5 x RIMON (kΩ) + 0.6V

For DCR type, VIMON (V) = VCS\_SUM (V) x 1.5 x RIMON (kΩ) + 0.6V

, where Vcs\_sum is the current sensing voltage from DCR sum current sensing network or SPS's IMON feedback signal. It should be noticed that SPS's Vcs\_sum current is the sum of current signal inputs from ISEN1 to ISEN8. Therefore, the selection of

### **RT8848D**

RIMON for a specified total load current protection can be derived as below :

For SPS type, RIMON (k $\Omega$ ) = [ VIMON\_OC\_TH (V) - 0.6V ] / VCS\_SUM,max (V) / 1.5 x 8

For DCR type, RIMON (k $\Omega$ ) = [ VIMON\_OC\_TH (V) - 0.6V ] / VCS\_SUM,max (V) / 1.5

, where  $\mathsf{VCS\_SUM},\mathsf{max}$  is the current sensing voltage at the specified limitation of total load current.

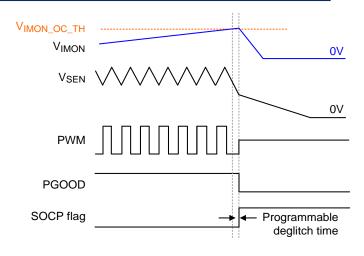

The protection mechanism of SOCP is shown in Figure 18. As the total load current increases, the voltage of VIMON increases proportionally. If VIMON is larger than VIMON\_OC\_TH for longer than deglitch time, which is programmable through I<sup>2</sup>C register 0x23[1:0], the controller forces all PWM outputs to tri-state. At the moment, the PGOOD is pulled down and the SOCP status is recorded in I<sup>2</sup>C register 0x2A[2]. Once SOCP is triggered, the controller needs to re-toggle EN or re-cycle VCC to release from latched mode and clear I<sup>2</sup>C flag 0x2A[2].

Moreover, the SOCP function can be enabled or disabled through  $I^2C$  register 0x29[2]. It should be noticed that only analog SOCP protection function can be disabled; the digital indicator of SOCP (0x2A[2]) will be asserted if SOCP is detected. DO NOT put any decoupling capacitor near IMON pin since it affects the accuracy of IMON reporting.

Figure 18. Sum OCP Protection Mechanism

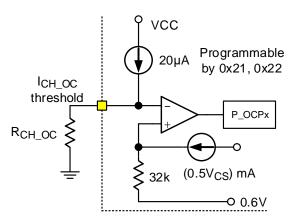

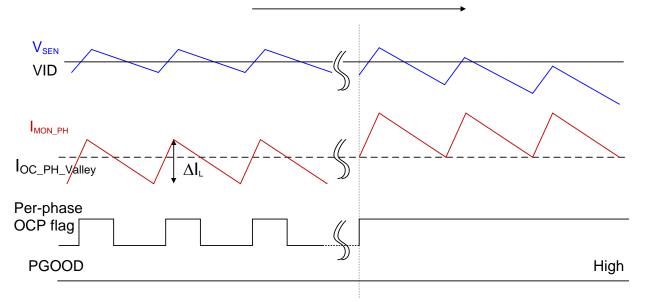

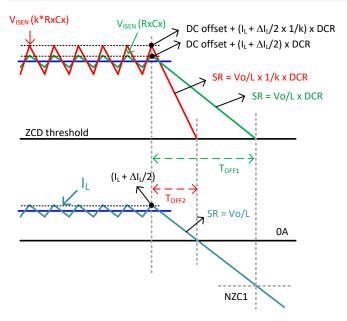

# Per-Phase Over-Current Protection (Per-Phase OCP)

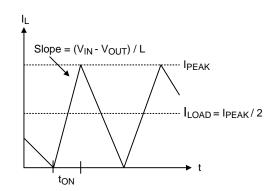

The RT8848D features per-phase current limit mechanism to prevent over-current event. The per-phase current limit circuit employs a unique "valley" current sensing algorithm. If the magnitude of the current sense signal is above the current limit threshold, the PWM is not allowed to initiate a new cycle. The per-phase OCP protection circuit is shown in Figure 19. The per-phase current limit threshold is decided by the differential voltage across RCH OC, VCH OC, which is generated by an internal current source (programmable through I<sup>2</sup>C register 0x21[7:0], 0x22[7:0]). When DCR sensing circuit is adopted, in order to ensure the accuracy of current signal over a wide range of temperatures, it is recommended to use a PTC thermistor in parallel with RCH OC. The PTC thermistor should be placed near power inductor at phase 1. Then, the current limit threshold can be calculated by the following equation :

$$V_{CH OC}(V) = 20\mu \times R_{CH OC}(\Omega)$$

$$\mathsf{OC\_PH\_Valley}(\mathsf{A}) = \frac{\mathsf{V}_{\mathsf{CH\_OC}}(\mathsf{V}) - 0.6}{16 \times \mathsf{DCR}(\Omega)}$$

Where the I<sub>OC\_PH\_Valley</sub> is the per-phase inductor valley current limit threshold and DCR is the inductor's DCR resistor. For SPS type application, the DCR represents the current reporting gain of SPS chip. Moreover, it should be noticed that the per-phase OCP

limits the inductor valley current instead of average current. When average output current is larger than (IOC\_PH\_Valley +  $\Delta$ IL/2), the output voltage will start to ramp down because inductor valley current is limited by OCP threshold. The output capacitor is discharged by the current deviation between inductor current and output load. Besides, the OCP indicator is detected dynamically according to the comparator output of per-phase OCP protection circuit. The protection mechanism of per-phase OCP is shown in Figure 20. The per-phase OCP flag (recorded in I<sup>2</sup>C register 0x2B[7:0]) is asserted as inductor sensing current, IMON PH, is larger than IOC PH. On the other hand, if inductor sensing current is lower than IOC\_PH, the OCP flag is de-asserted. There is around 100ns comparator delay time in per-phase OCP protection circuit. Also, the PGOOD remains at high status during OCP process.

In addition, for multi-phase application with common-N DCR current sensing circuit, the PCB impedance from inductor output point to VOUT remoting point (GPU side) induces a DC offset on current feedback signal as shown in Figure 36 in Application Information section.

$$V_{CSi} = \frac{\left(1 + \frac{sL}{DCR}\right)}{\left(1 + sC_{X}R_{X}\right)} \times DCR \times I_{Li} + \frac{I_{Li} \times R_{pcbi} - \frac{1}{N} \times \sum_{i=1}^{N} I_{Li} \times R_{pcbi}}{\left(1 + sC_{X}R_{X}\right)}$$

The OCP design threshold should be adjusted according to Rpcb values. There are OCP gains which are programmable through  $I^2C$  registers (0x21[7:0], 0x22[7:0]) to adjust OCP threshold for each phase based on V<sub>CH\_OC</sub>, which is decided by R<sub>CH\_OC</sub>. The OCP threshold with OCP gain factor for each phase can be represented as below :

$$I_{OC\_PH\_Valley}(A) = \frac{V_{CH\_OC}(V) \times OCP\_gain - 0.6}{16 \times DCR(\Omega)}$$

RICHTEK

When considering the Rpcb term in current sensing feedback signal, the OCP should follow below methods to design. The OCP gain is applied to compensate the Rpcb term offset on DCR term (real current signal). The design target is to make each phase's real OCP threshold equal. Therefore, the one with Rpcb\_min should be programmed with minimum OCP gain (ex. 0.7x). And the equation can be simplified as below :

$$I_{OC} \times (DCR + R_{pcb\_min} - R_{pcb\_avg}) \times 16 + 0.6V = V_{CH\_OC} \times 0.7$$

The other phases should follow the Rpcb deviation value to choose the suitable OCP gain.

$$OCP\_gain = \frac{I_{OC} \times (DCR + R_{pcb\_n} - R_{pcb\_avg}) \times 16 + 0.6}{V_{CH\_OC}}$$

, where Rpcb\_n is the Rpcb trace value of phase N.

For different types of application, if per-phase OCP is not necessary, users can disable the per-phase OCP function by  $I^2C$  register 0x4D[1:0].

Figure 19. Per-Phase OCP Protection Circuit

Output Current Increasing

Figure 20. Per-Phase OCP Protection Mechanism

#### **ADC Function**

The RT8848D supports analog to digital converter (ADC) to monitor VSEN, VIMON and VTSEN voltages. The ADC function is initialized and starts to work after PGOOD signal has been pulled high. The ADC circuits for VSEN and TSEN operates periodically with time space of 40.5µs and the ADC circuit for VIMON operates periodically with time space of 13.5µs. Users can access the ADC results from I<sup>2</sup>C registers 0x2E[7:0], 0x2F[7:0] and 0x30[7:0] for voltage of VIMON, VSEN and VTSEN respectively. The voltage measurement reported in these registers are an average measurement over time period defined in I<sup>2</sup>C register 0x31[1:0], 0x32[1:0] and 0x33[1:0] respectively. Besides, the ADC circuit for VIMON conversion will shorten the operation time space to 6.75µs when SOCP is triggered to prevent power stage from over-current operation. The SOCP delay time can be programmed by I<sup>2</sup>C register 0x23[1:0]. The definition of registers are summarized in the section of register tables below.

### Absolute Maximum Ratings (Note 1)

| • VIN to GND                                          | - –0.3 to 28V  |

|-------------------------------------------------------|----------------|

| VCC to GND                                            | - –0.3 to 6V   |

| • FBRTN to GND                                        | - –0.3 to 0.3V |

| Other Pins                                            | - –0.3 to 6V   |

| <ul> <li>Power Dissipation, PD @ TA = 25°C</li> </ul> |                |

| WQFN-40L 5x5                                          | - 3.63W        |

| Package Thermal Resistance (Note 2)                   |                |

| WQFN-40L 5x5, θJA                                     | - 27.5°C/W     |

| WQFN-40L 5x5, θJC                                     | - 6°C/W        |

| Lead Temperature (Soldering, 10 sec.)                 | - 260°C        |

| Junction Temperature                                  | - 150°C        |

| Storage Temperature Range                             | -65°C to 150°C |

| ESD Susceptibility (Note 3)                           |                |

| НВМ                                                   | 2kV            |

### Recommended Operating Conditions (Note 4)

| ٠ | Input Voltage, VIN         | 2.8 to 24V     |

|---|----------------------------|----------------|

| ٠ | Supply Voltage, Vvcc       | 4.5 to 5.5V    |

| • | Junction Temperature Range | –40°C to 125°C |

### **Electrical Characteristics**

(VVCC = 5V, typical values are referenced to  $T_A = T_J = 25^{\circ}$ C, Min and Max Values are referenced to  $T_A = T_J$  from  $-10^{\circ}$ C to  $105^{\circ}$ C, unless other noted)

| Parameter                          | Symbol     | Test Conditions          | Min  | Тур  | Max  | Unit |

|------------------------------------|------------|--------------------------|------|------|------|------|

| PWM Controller                     | •          |                          |      |      |      |      |

| VCC Supply Voltage                 | Vvcc       |                          | 4.5  | 5    | 5.5  | V    |

| VCC Supply Current                 | Ivcc       | EN = high, not switching |      | 10   | 15   | mA   |

| VCC Shutdown Current               | ISHDN      | EN = 0V                  |      |      | 200  | μA   |

| VCC POR Threshold                  |            | VCC rising voltage       | 4.1  | 4.3  | 4.5  | V    |

| VCC UVLO Threshold                 |            | VCC falling voltage      | 3.9  | 4.1  | 4.3  | V    |

| POR Hysteresis                     |            |                          | 90   | 200  | 310  | mV   |

| Reference Voltage                  | ·          |                          |      |      |      |      |

| Reference Voltage                  | Vref       |                          | 1.98 | 2    | 2.02 | V    |

| REFOUT Output<br>Voltage           | VREFOUT    |                          | 1.3  | 1.38 | 1.45 | V    |

| REFIN Standby Voltage              | VREFIN_STD | VREFIN < 0.15V           |      |      | 0.15 | V    |

| External REFIN Voltage             | VREFIN     |                          | 0.25 |      | 2    | V    |

| PWMVID Input Voltage               |            |                          | -    |      |      |      |

| PWMVID Input Voltage<br>Logic-High | Vpwmvid_h  |                          | 1.2  |      |      | V    |

| PWMVID Input Voltage<br>Logic-Low  | VPWMVID_L  |                          |      |      | 0.6  | V    |

| Parameter                                      | Symbol          | Test Conditions                                                           | Min   | Тур | Мах   | Unit  |

|------------------------------------------------|-----------------|---------------------------------------------------------------------------|-------|-----|-------|-------|

| PWMVID Tri-state<br>Voltage                    | Vpwmvid_tri     |                                                                           | 0.8   |     | 1     | V     |

| Soft-Start                                     | •               | 1                                                                         | 1     | 1   | 1     | 1     |

| Soft-Start Ramp Up<br>Slew Rate                |                 | Slew rate set to 3mV/µs                                                   | 2.5   | 3   | 3.5   | mV/μs |

| PGOOD Blanking Time                            | tpgood          | From EN go high to PGOOD go high                                          |       |     | 2     | ms    |

| EN and Logic Input                             |                 |                                                                           | -     |     |       |       |

|                                                | Ven1_h          | REN = 60kΩ, ISOURCE_EN = 10 $\mu$ A                                       | 0.5   |     |       |       |

| EN Threshold                                   | Ven1_L          | Nei - 00κs2, 1300κce_en - 10μλ                                            |       |     | 0.3   | - v   |

|                                                | Ven2_h          | REN = 60kΩ, ISOURCE_EN = 90 $\mu$ A                                       | 1.8   |     |       |       |

|                                                | Ven2_L          | $\frac{1}{10000000000000000000000000000000000$                            |       |     | 1.6   |       |

| EN Deglitch Time                               |                 | V <sub>EN</sub> is higher than high threshold or lower than low threshold |       | 1.6 |       | μS    |

| Leakage Current of<br>PGOOD, PSI               |                 |                                                                           | -1    |     | 1     | μA    |

| PSI Input Voltage                              |                 | ·                                                                         |       |     |       |       |

| PSI Logic High<br>Threshold                    | Vpsi_h          |                                                                           | 1.6   |     |       | V     |

| PSI Logic Tri-State<br>Threshold               | Vpsi_hiz        |                                                                           | 0.8   |     | 1.2   | V     |

| PSI Logic Low<br>Threshold                     | Vpsi_L          |                                                                           |       |     | 0.4   | V     |

| Frequency Setting                              |                 | 1                                                                         |       |     |       |       |

| Frequency Setting                              | fsw             | fsw = 300kHz, ILOAD = 0A                                                  | 270   | 300 | 330   | kHz   |

| Minimum PWM Pulse<br>Width                     | tpwm_min        |                                                                           |       | 50  |       | ns    |

| IPINSET (For PINSET1, P                        | INSET2 and PINS | SET3)                                                                     | 1     | 1   |       |       |

| PIN SET Current                                | IPINSET         | VPINSETx = 1V, VVCC = 5V                                                  | 79.2  | 80  | 80.8  | μA    |

| EA/GM Amplifier                                |                 | 1                                                                         | 1     |     |       |       |

| Input Offset                                   | VEAOFS          |                                                                           | -3    |     | 3     | mV    |

| CS Amplifier                                   | 1               | 1                                                                         | 1     | 1   | I     | 1     |

| Input Offset                                   | VEAOFS          |                                                                           | -1    |     | 1     | mV    |

| Protection Function                            |                 | 1                                                                         | 1     | 1   | 1     | 1     |

| Relative Over-Voltage<br>Protection Threshold  | VROVP           | VREFIN ≥ 1.33V                                                            | 142.5 | 150 | 157.5 | %     |

| Absolute Over-Voltage<br>Protection Threshold  | VABOVP          | Vrefin < 1.33V,                                                           | 1.9   | 2   | 2.1   | V     |

| OV Fault Delay                                 |                 | FB forced above OV threshold                                              |       | 1   | 2     | μS    |

| Relative Under-Voltage<br>Protection Threshold | Vruvp           |                                                                           | 35    | 40  | 45    | %     |

| Parameter                            | Symbol       | Test Conditions                               | Min  | Тур  | Max  | Unit |

|--------------------------------------|--------------|-----------------------------------------------|------|------|------|------|

| UV Fault Delay                       |              | FB forced above UV threshold                  | 2    | 4    | 6    | μS   |

| Thermal Shutdown<br>Threshold        | TSD          |                                               |      | 150  |      | °C   |

| Per Phase OC<br>Threshold            | Vcs_ph       | (VISENPx – VCSNSUM)<br>when VCH_OC_SET = 1.6V | 56   | 62.5 | 69   | mV   |

| Channel OC Source<br>Current         | Існ_ос       | Vvcc = 5V                                     | 19.6 | 20   | 20.4 | μΑ   |

| Sum OC Protection<br>Threshold       | VIMON_SOC_TH | Vvcc = 5V, 0x24[5:0] = 0x00                   | 2.1  | 2.2  | 2.3  | V    |

| TSEN Protection<br>Threshold Voltage | VTSEN_TH     | Vvcc = 5V, PTC Application                    | 0.72 | 0.8  | 0.88 | V    |

| PWM Driving Capability               | /            |                                               |      |      |      |      |

| PWM Source<br>Resistance             | Rpwm_src     | Pull up to VCC                                | 15   | 25   | 35   | Ω    |

| PWM Sink Resistance                  | Rpwm_snk     | Pull down to GND                              |      | 7    | 12   | Ω    |

| PWM Tri-state Voltage                |              | Vvcc = 5V, 0x40[0] = 0                        | 1.65 | 1.9  | 2.15 | V    |

|                                      | VPWM_Tri     | ri $V_{VCC} = 5V, 0x40[0] = 1$                |      | 1.65 | 1.9  | V    |

| Power Good Indicator                 |              |                                               |      |      |      |      |

| PGOOD Output Low<br>Level            | Vpgood       | ISINK = 4mA                                   |      |      | 0.3  | V    |

| PGOOD Leakage<br>Current             | IPGOOD_Leak  | Vpgood = 5V                                   |      |      | 1    | μA   |

| I <sup>2</sup> C Interface (SDA&SC   | L)           |                                               |      |      |      |      |

| Input High Level                     | VIH_I2C      |                                               | 1    |      |      | V    |

| Input Low Level                      | VIL_I2C      |                                               |      |      | 0.6  | V    |

| SDA Pull Down<br>Resistance          | RDOWN_I2C    |                                               |      | 7    | 12   | Ω    |

| Leakage Current                      | ILEAK_I2C    |                                               |      |      | 1    | μA   |

| ADC Voltage Range                    |              |                                               |      |      |      |      |

| TSEN ADC                             | VTSEN_ADC    | ADC = 12.5mV/step                             | 0    |      | 3.2  | V    |

| IMON ADC                             | VIMON_ADC    | ADC = 6.25mV/step                             | 0.6  |      | 2.2  | V    |

| VSEN ADC                             | VVSEN_ADC    | ADC = 6.25mV/step                             | 0    |      | 1.6  | V    |

|                                      |              |                                               |      |      |      |      |

**Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precautions are recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

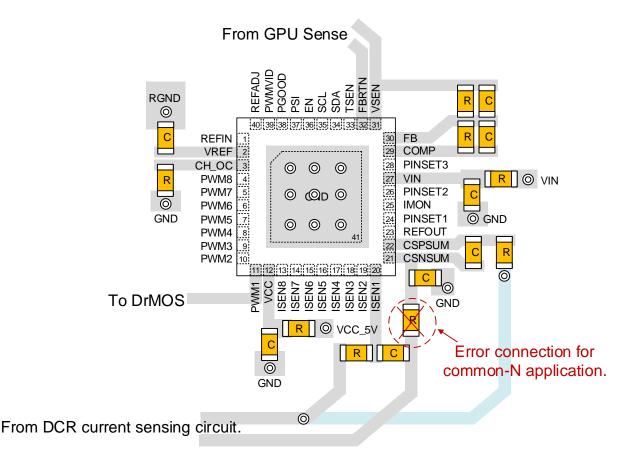

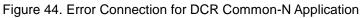

### **Typical Application Circuit**

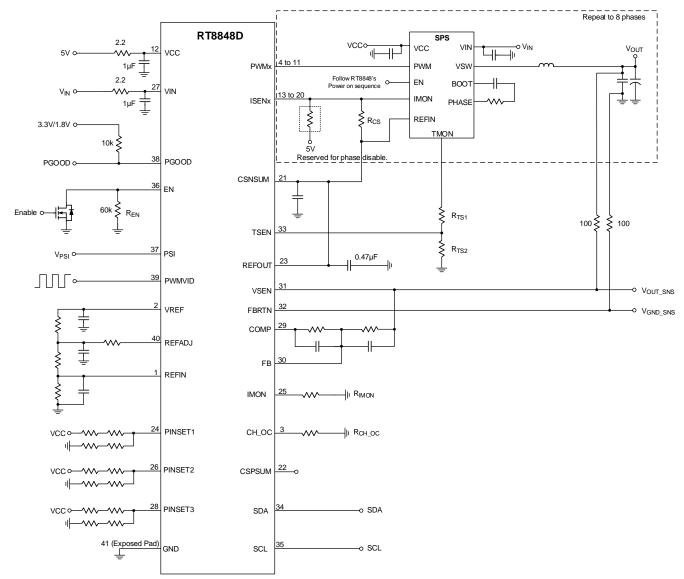

Figure 21. Typical Application Circuit for RT8848D with SPS's IMON Configuration

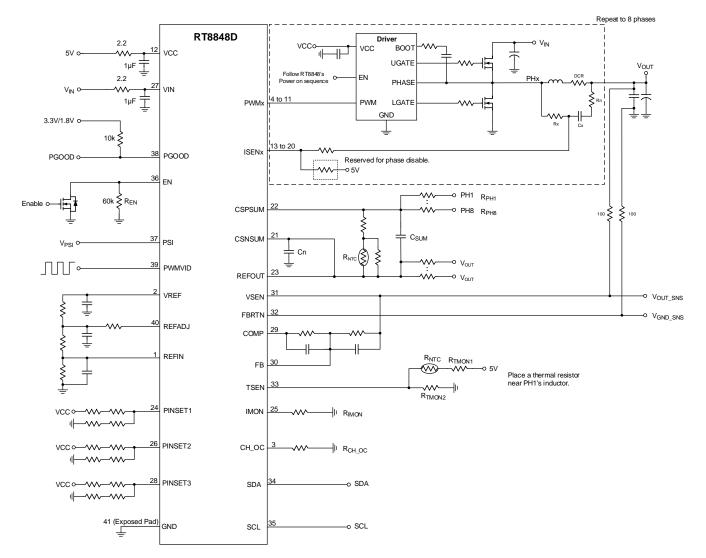

Figure 22. Typical Application Circuit for RT8848D with DCR Current Sense Configuration

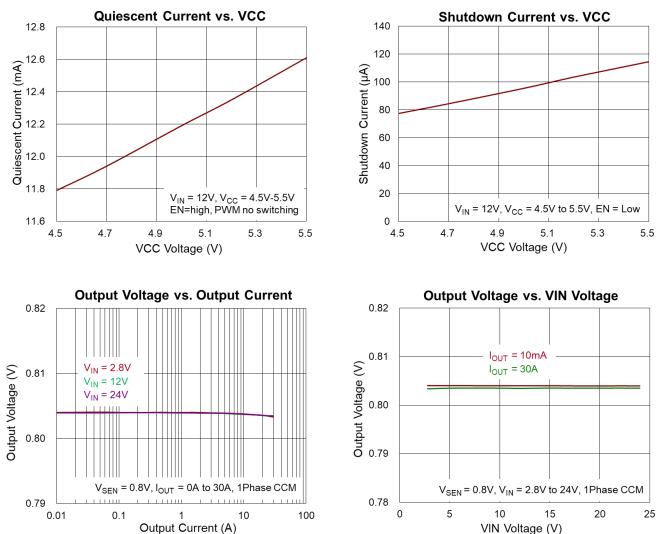

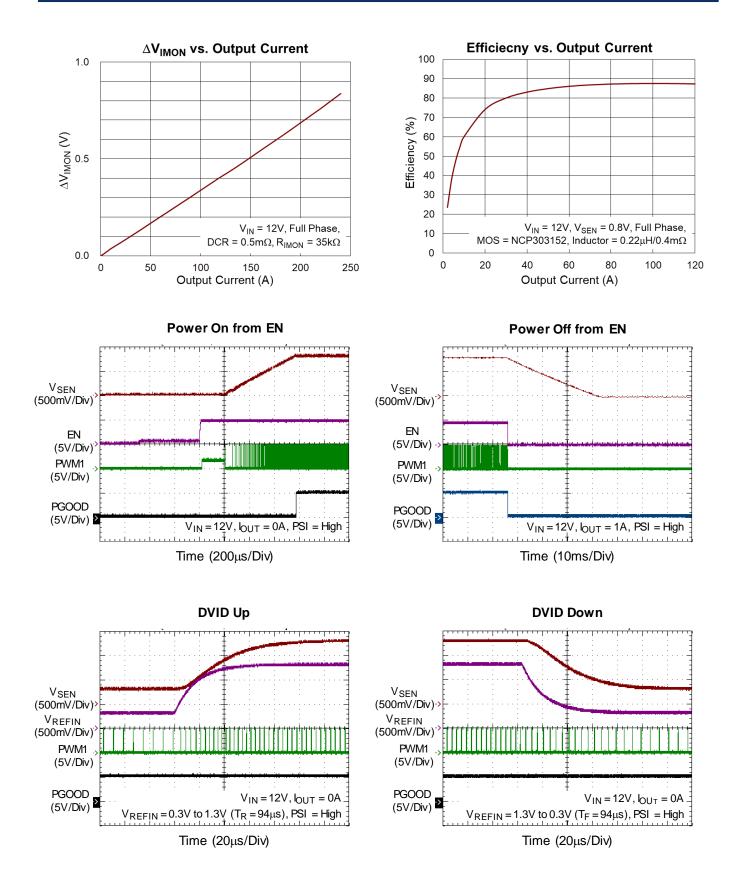

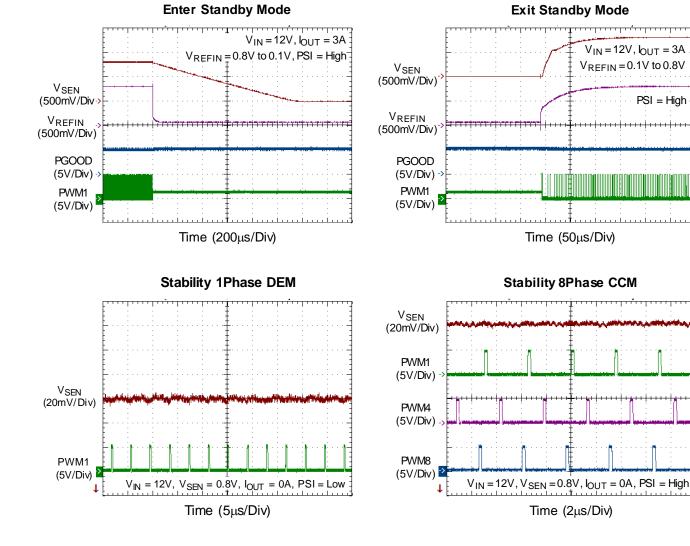

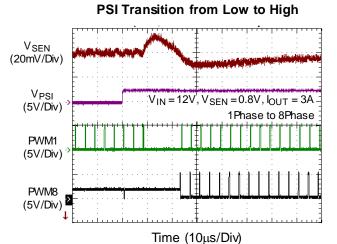

### **Typical Operating Characteristics**

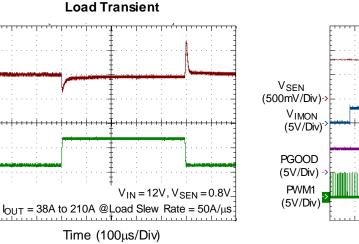

Performance waveforms are tested on the evaluation board of the Typical Application Circuit,  $V_{IN} = 12V$ ,  $V_{SEN} = 0.8V$ ,  $f_{SW} = 300$ kHz,  $L = 0.22\mu$ H,  $C_{OUT} = 330\mu$ F/2V POSCAP x 8pcs +  $22\mu$ F/6.3V/X5R/0805 x 48pcs +  $22\mu$ F/6.3V/X5R/0603 x 80pcs,  $T_C = 25^{\circ}$ C, unless otherwise noted.

Copyright © 2022 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. www.richtek.com DS8848D-00 November

PSI = High

V<sub>SEN</sub> (100mV/Div)

VILOAD

(300mV/Div)

t

Sum OCP Behavior (8Phase)

### **Application Information**

Richtek's component specification does not include the following information in the Application Information section. Thereby no warranty is given regarding its validity and accuracy. Customers should take responsibility to verify their own designs and to ensure the functional suitability of their components and systems.

#### **PINSET Pin Setting**

The RT8848D features PINSET pin setting function for multi-functional programming. There are total three PINSET groups provided by RT8848D to support different application configurations. The PINSET functions are defined with related  $I^2C$  registers, and the function assignments are summarized in Table 5.

|                 | Bit3                                         | Bit2                              | Bit1                          | Bit0                           |  |

|-----------------|----------------------------------------------|-----------------------------------|-------------------------------|--------------------------------|--|

| PINSET1_V: 0x40 | Ramp Amplitude                               |                                   | Soft-start Slew Rate          | PWM Tri-state<br>Voltage Level |  |

| PINSET1_I: 0x41 | Al Gain                                      |                                   | SPS/DCR Mode<br>Selection     |                                |  |

| PINSET2_V: 0x42 | Per-phase Switching Frequency                |                                   | Address Code for Slave Device |                                |  |

| PINSET2_I: 0x43 | Middle Drive<br>Enable/Disable               | Operating Phase Number in PSI = L |                               |                                |  |

| PINSET3_V: 0x44 | APL Thresholds                               |                                   |                               |                                |  |

| PINSET3_I: 0x45 | Operating Phase Number during Cold/Warm Boot |                                   |                               |                                |  |

#### Table 5. PINSET Function Assignments

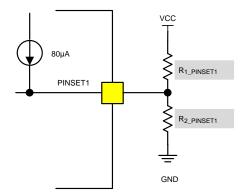

For PINSET1 pin setting circuit as shown in Figure 23, a pair of voltage dividers is used to set up the internal ramp amplitude, soft-start slew rate, PWM tri-state voltage level, AI gain and SPS/DCR mode selection. There is an internal current source ( $80\mu$ A) flowing out from PINSET1 pin to external resistor. The voltage across R<sub>2\_PINSET1</sub> is then sensed by internal sensor and decoded to decide the PINSET1 configuration. Besides, the ramp amplitude can also be set via I<sup>2</sup>C register 0x4F[3:0]. The soft-start slew rate can be set via I<sup>2</sup>C register 0x40[1]. The PWM tri-state voltage level cab be set via I<sup>2</sup>C register 0x40[0]. The AI gain can be set via I<sup>2</sup>C register 0x41[3:2]. The SPS/DCR mode selection can be set via I<sup>2</sup>C register 0x41[1].

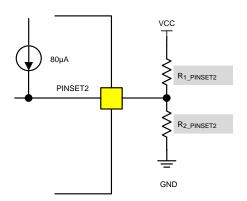

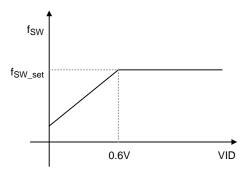

For PINSET2 pin setting circuit as shown in Figure 24, a pair of voltage dividers is used to set up the per-phase switching frequency, address code for slave device, middle drive function and operating phase number in PSI = L. There is an internal current source ( $80\mu$ A) flowing out from PINSET2 pin to external resistor. The voltage across R2\_PINSET2 is then sensed by internal sensor and decoded to decide the PINSET2 configuration. Besides, the per-phase switching frequency can also be set via I<sup>2</sup>C register 0x0F[4:0]. The address code for slave device can be set via I<sup>2</sup>C register 0x42[1:0]. The middle drive function can be set via I<sup>2</sup>C register 0x43[3]. The operating phase number in PSI=L can be set via I<sup>2</sup>C register 0x4F[6:4].

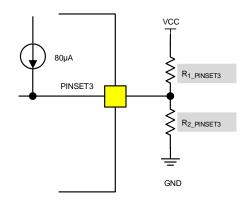

For PINSET3 pin setting circuit as shown in Figure 25, a pair of voltage dividers is used to set up the APL thresholds and operating phase number during cold/warm boot. There is an internal current source ( $80\mu$ A) flowing out from PINSET3 pin to external resistor. The voltage across R2\_PINSET3 is then sensed by internal sensor and decoded to decide the PINSET3 configuration. Besides, the APL thresholds can also be set via I<sup>2</sup>C register 0x01[7:0] to 0x04[7:0] respectively. The operating phase number during cold/warm boot can be set via I<sup>2</sup>C register 0x45[3:1]. If PINSET3 is not necessary, users can leave this pin floating and the default setting for RT8848D is shown in Table 6. It should be noticed that APS function is disabled by 0x2D[0]=1 and PSI logic is also locked at high logic, which makes RT8848D operate in full phase condition. If users want to enable APS and PSI function after power-on, the APS function can be turned on by register 0x2D[0]=0 and PSI function can be activated by register 0x2D[2]=0.

Figure 25. PINSET3 Pin Setting Circuit

Figure 23. PINSET1 Pin Setting Circuit

Figure 24. PINSET2 Pin Setting Circuit

| Register  | Default Code | Function Setting                                                                |  |  |

|-----------|--------------|---------------------------------------------------------------------------------|--|--|

| 0x44[3:0] | 1000         | APL1 = 0.2V<br>APL2 = 0.4V<br>APL3 = 0.8V<br>APL4 = 1.2V                        |  |  |

| 0x45[3:1] | 111          | Operation phase number during soft-start = 8Phase                               |  |  |

| 0x2D[2]   | 1            | Internal PSI logic locks at high logic no matter external PSI pin configuration |  |  |

| 0x2D[0]   | 1            | Disable APS mode and operating in full phase mode                               |  |  |

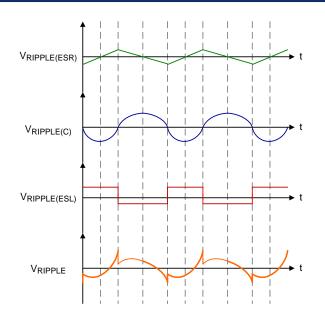

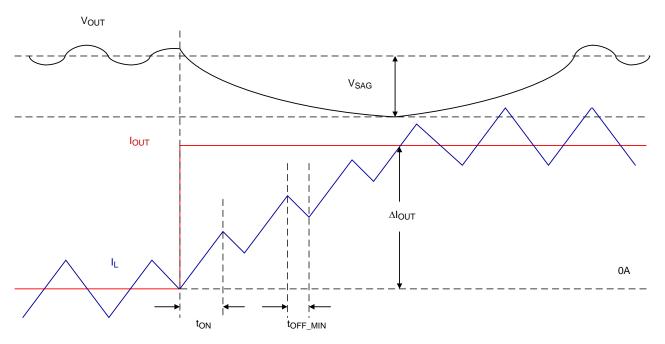

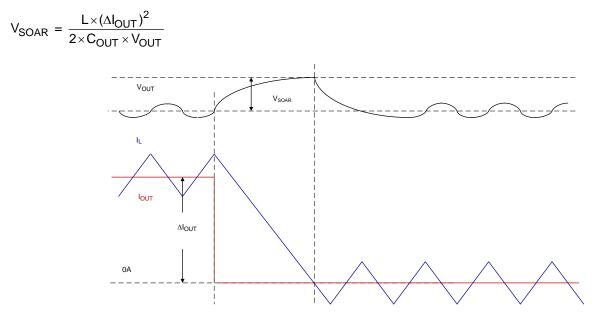

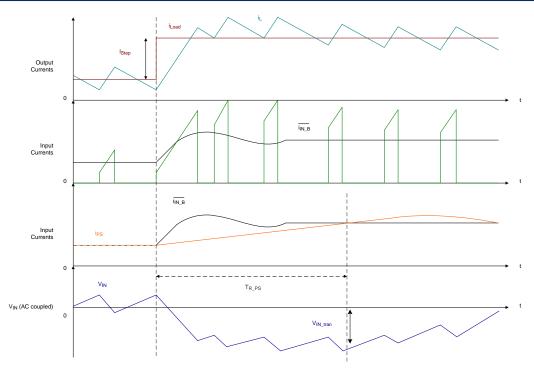

#### Table 6. Register Setting Configuration as PINSET3 is Floating