# Advanced 4/3/2/1-Phase PWM Controller with Embedded Drivers for CPU Core Power Supply

#### **General Description**

The RT8862 is an advanced 4/3/2/1-phase synchronous buck controller with 2 integrated MOSFET drivers for Intel VR11/VR10 and AMD K8/K8\_M2 CPUs power application. RT8862 adopts state-of-the-art dynamic phase control capability. That achieves high efficiency over wide load range. It uses differential inductor DCR current sense to achieve phase current balance and active voltage positioning. Other features include adjustable operating frequency, adjustable soft start, power good indication, external error-amp compensation, over voltage protection, over current protection and enable/shutdown for various application. RT8862 comes to a small footprint with WQFN-48L 7x7 package.

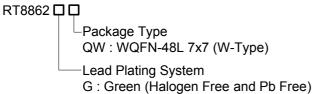

## **Ordering Information**

#### Note:

Richtek products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

## **Applications**

- Desktop CPU Core Power

- Low Voltage, High Current DC/ DC Converter

#### **Features**

- Support Dynamic Phase Control

- 12V Power Supply Voltage

- 4/3/2/1-Phase Power Conversion

- 2 Embedded MOSFET Drivers

- Internal Regulated 5V Output

- VID table for INTEL VR11.1/VR10.x and AMD K8/ K8 M2 CPUs

- Continuous Differential Inductor DCR Current Sense

- Adjustable Soft Start

- Adjustable Frequency (300kHz typ.)

- Power Good Indication

- Adjustable Over Current Protection

- Over Voltage Protection

- VRHOT Sensing with External Thermistor

- IMON Output Current Indication

- Power State Indicator (PSI)

- Small 48-Lead WQFN Package

- RoHS Compliant and Halogen Free

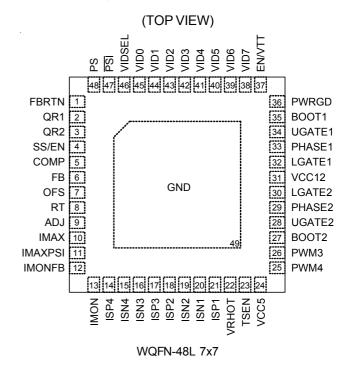

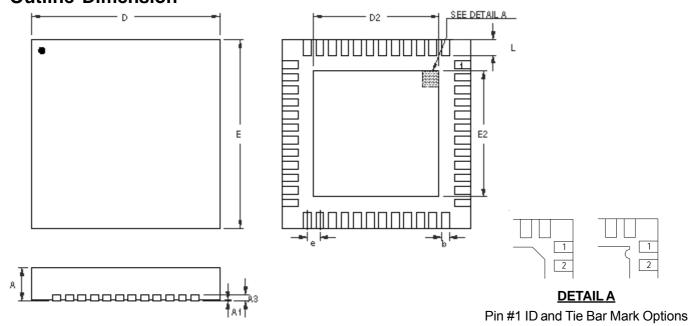

## **Pin Configuration**

## **Part Status**

| Part No   | Status   | Package Type | Lead plating System              |

|-----------|----------|--------------|----------------------------------|

| RT8862GQW | Obsolete | WQFN-48L 7x7 | Green (Halogen Free and Pb Free) |

The part status values are defined as follows:

Active: Device is in production and is recommended for new designs.

**Lifebuy**: The device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs.

**Preview**: Device has been announced but is not in production.

**Obsolete**: Richtek has discontinued the production of the device.

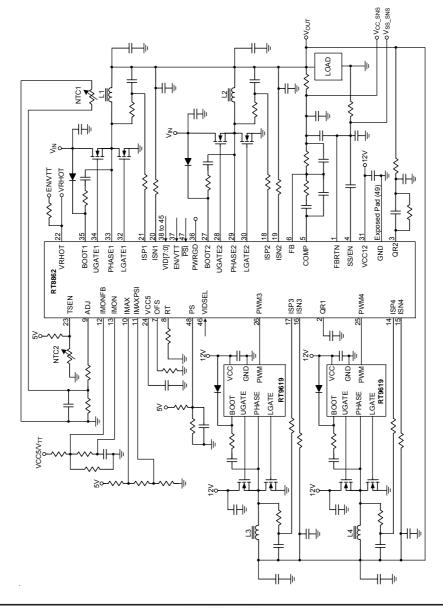

## **Typical Application Circuit**

Table 1. VR11.1 VID Code Table

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage |

|------|------|------|------|------|------|------|------|---------|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | OFF     |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | OFF     |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1.60000 |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1.59375 |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1.58750 |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1.58125 |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1.57500 |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1.56875 |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1.56250 |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1.55625 |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1.55000 |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1.54375 |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 1.53750 |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1.53125 |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 1.52500 |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1.51875 |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 1.51250 |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1.50625 |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1.50000 |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 1.49375 |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 1.48750 |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 1.48125 |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0    | 1.47500 |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1.46875 |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1.46250 |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1.45625 |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1.45000 |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1.44375 |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1.43750 |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1.43125 |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1.42500 |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1.41875 |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1.41250 |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1.40625 |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1.40000 |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage |

|------|------|------|------|------|------|------|------|---------|

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1.39375 |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1.38750 |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1.38125 |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 1.37500 |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1.36875 |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1.36250 |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 1.35625 |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1.35000 |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 1.34375 |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | 1.33750 |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1.33125 |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1.32500 |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1.31875 |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1.31250 |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1.30625 |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1.30000 |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1.29375 |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1.28750 |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1.28125 |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1.27500 |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1.26875 |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1.26250 |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1.25625 |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1.25000 |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1.24375 |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1.23750 |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1.23125 |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1.22500 |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1.21875 |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1.21250 |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1    | 1.20625 |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0    | 1.20000 |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 1.19375 |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 1.18750 |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1    | 1.18125 |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage |

|------|------|------|------|------|------|------|------|---------|

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0    | 1.17500 |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1    | 1.16875 |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 1.16250 |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1    | 1.15625 |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 1.15000 |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1    | 1.14375 |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1.13750 |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 1    | 1.13125 |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0    | 1.12500 |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1    | 1.11875 |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 1.11250 |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 1.10625 |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0    | 1.10000 |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 1    | 1.09375 |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 1.08750 |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1    | 1.08125 |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 0    | 1.07500 |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 1    | 1.06875 |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 0    | 1.06250 |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 1    | 1.05625 |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0    | 1.05000 |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1    | 1.04375 |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0    | 1.03750 |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1    | 1.03125 |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0    | 1.02500 |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1    | 1.01875 |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 1.01250 |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 1.00625 |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0    | 1.00000 |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1    | 0.99375 |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0    | 0.98750 |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1    | 0.98125 |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | 0.97500 |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | 0.96875 |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0    | 0.96250 |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 0.95625 |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage |

|------|------|------|------|------|------|------|------|---------|

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0    | 0.95000 |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1    | 0.94375 |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0    | 0.93750 |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1    | 0.93125 |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 0    | 0.92500 |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1    | 0.91875 |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0.91250 |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1    | 0.90625 |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 0    | 0.90000 |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1    | 0.89375 |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 0.88750 |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 0.88125 |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 0.87500 |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 0.86875 |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0.86250 |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 0.85625 |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 0.85000 |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 0.84375 |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 0.83750 |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 0.83125 |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0.82500 |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0.81875 |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0.81250 |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0.80625 |

| 1    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0.80000 |

| 1    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0.79375 |

| 1    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0.78750 |

| 1    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0.78125 |

| 1    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0.77500 |

| 1    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0.76875 |

| 1    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0.76250 |

| 1    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0.75625 |

| 1    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0.75000 |

| 1    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0.74375 |

| 1    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0.73750 |

| 1    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0.73125 |

**RT8862**

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage |

|------|------|------|------|------|------|------|------|---------|

| 1    | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0.72500 |

| 1    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0.71875 |

| 1    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0.71250 |

| 1    | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0.70625 |

| 1    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0.70000 |

| 1    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0.69375 |

| 1    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0.68750 |

| 1    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0.68125 |

| 1    | 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0.67500 |

| 1    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0.66875 |

| 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0.66250 |

| 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0.65625 |

| 1    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0.65000 |

| 1    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0.64375 |

| 1    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0.63750 |

| 1    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0.63125 |

| 1    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0.62500 |

| 1    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0.61875 |

| 1    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0.61250 |

| 1    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0.60625 |

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0.60000 |

| 1    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0.59375 |

| 1    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0.58750 |

| 1    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0.58125 |

| 1    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0.57500 |

| 1    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0.56875 |

| 1    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0.56250 |

| 1    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0.55625 |

| 1    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0.55000 |

| 1    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 0.54375 |

| 1    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | 0.53750 |

| 1    | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0.53125 |

| 1    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0.52500 |

| 1    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0.51875 |

| 1    | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0.51250 |

| 1    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0.50625 |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | Voltage |

|------|------|------|------|------|------|------|------|---------|

| 1    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0.50000 |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | OFF     |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | OFF     |

Copyright ©2021 Richtek Technology Corporation. All rights reserved.

Table 2. Output Voltage Program (VRD10.x + VID6)

|      |      |      | Naminal Output Valta va DACOUT |      |      |      |                               |

|------|------|------|--------------------------------|------|------|------|-------------------------------|

| VID4 | VID3 | VID2 | VID1                           | VID0 | VID5 | VID6 | Nominal Output Voltage DACOUT |

| 0    | 1    | 0    | 1                              | 0    | 1    | 1    | 1.60000V                      |

| 0    | 1    | 0    | 1                              | 0    | 1    | 0    | 1.59375V                      |

| 0    | 1    | 0    | 1                              | 1    | 0    | 1    | 1.58750V                      |

| 0    | 1    | 0    | 1                              | 1    | 0    | 0    | 1.58125V                      |

| 0    | 1    | 0    | 1                              | 1    | 1    | 1    | 1.57500V                      |

| 0    | 1    | 0    | 1                              | 1    | 1    | 0    | 1.56875V                      |

| 0    | 1    | 1    | 0                              | 0    | 0    | 1    | 1.56250V                      |

| 0    | 1    | 1    | 0                              | 0    | 0    | 0    | 1.55625V                      |

| 0    | 1    | 1    | 0                              | 0    | 1    | 1    | 1.55000V                      |

| 0    | 1    | 1    | 0                              | 0    | 1    | 0    | 1.54375V                      |

| 0    | 1    | 1    | 0                              | 1    | 0    | 1    | 1.53750V                      |

| 0    | 1    | 1    | 0                              | 1    | 0    | 0    | 1.53125V                      |

| 0    | 1    | 1    | 0                              | 1    | 1    | 1    | 1.52500V                      |

| 0    | 1    | 1    | 0                              | 1    | 1    | 0    | 1.51875V                      |

| 0    | 1    | 1    | 1                              | 0    | 0    | 1    | 1.51250V                      |

| 0    | 1    | 1    | 1                              | 0    | 0    | 0    | 1.50625V                      |

| 0    | 1    | 1    | 1                              | 0    | 1    | 1    | 1.50000V                      |

| 0    | 1    | 1    | 1                              | 0    | 1    | 0    | 1.49375V                      |

| 0    | 1    | 1    | 1                              | 1    | 0    | 1    | 1.48750V                      |

| 0    | 1    | 1    | 1                              | 1    | 0    | 0    | 1.48125V                      |

| 0    | 1    | 1    | 1                              | 1    | 1    | 1    | 1.47500V                      |

| 0    | 1    | 1    | 1                              | 1    | 1    | 0    | 1.46875V                      |

| 1    | 0    | 0    | 0                              | 0    | 0    | 1    | 1.46250V                      |

| 1    | 0    | 0    | 0                              | 0    | 0    | 0    | 1.45625V                      |

| 1    | 0    | 0    | 0                              | 0    | 1    | 1    | 1.45000V                      |

| 1    | 0    | 0    | 0                              | 0    | 1    | 0    | 1.44375V                      |

| 1    | 0    | 0    | 0                              | 1    | 0    | 1    | 1.43750V                      |

| 1    | 0    | 0    | 0                              | 1    | 0    | 0    | 1.43125V                      |

| 1    | 0    | 0    | 0                              | 1    | 1    | 1    | 1.42500V                      |

| 1    | 0    | 0    | 0                              | 1    | 1    | 0    | 1.41875V                      |

| 1    | 0    | 0    | 1                              | 0    | 0    | 1    | 1.41250V                      |

| 1    | 0    | 0    | 1                              | 0    | 0    | 0    | 1.40625V                      |

| 1    | 0    | 0    | 1                              | 0    | 1    | 1    | 1.40000V                      |

| 1    | 0    | 0    | 1                              | 0    | 1    | 0    | 1.39375V                      |

| 1    | 0    | 0    | 1                              | 1    | 0    | 1    | 1.38750V                      |

| 1    | 0    | 0    | 1                              | 1    | 0    | 0    | 1.38125V                      |

| 1    | 0    | 0    | 1                              | 1    | 1    | 1    | 1.37500V                      |

| 1    | 0    | 0    | 1                              | 1    | 1    | 0    | 1.36875V                      |

| 1    | 0    | 1    | 0                              | 0    | 0    | 1    | 1.36250V                      |

|      |      |      | Naminal Outrot Valtage DACOUT |      |      |      |                               |

|------|------|------|-------------------------------|------|------|------|-------------------------------|

| VID4 | VID3 | VID2 | VID1                          | VID0 | VID5 | VID6 | Nominal Output Voltage DACOUT |

| 1    | 0    | 1    | 0                             | 0    | 0    | 0    | 1.35625V                      |

| 1    | 0    | 1    | 0                             | 0    | 1    | 1    | 1.35000V                      |

| 1    | 0    | 1    | 0                             | 0    | 1    | 0    | 1.34375V                      |

| 1    | 0    | 1    | 0                             | 1    | 0    | 1    | 1.33750V                      |

| 1    | 0    | 1    | 0                             | 1    | 0    | 0    | 1.33125V                      |

| 1    | 0    | 1    | 0                             | 1    | 1    | 1    | 1.32500V                      |

| 1    | 0    | 1    | 0                             | 1    | 1    | 0    | 1.31875V                      |

| 1    | 0    | 1    | 1                             | 0    | 0    | 1    | 1.31250V                      |

| 1    | 0    | 1    | 1                             | 0    | 0    | 0    | 1.30625V                      |

| 1    | 0    | 1    | 1                             | 0    | 1    | 1    | 1.30000V                      |

| 1    | 0    | 1    | 1                             | 0    | 1    | 0    | 1.29375V                      |

| 1    | 0    | 1    | 1                             | 1    | 0    | 1    | 1.28750V                      |

| 1    | 0    | 1    | 1                             | 1    | 0    | 0    | 1.28125V                      |

| 1    | 0    | 1    | 1                             | 1    | 1    | 1    | 1.27500V                      |

| 1    | 0    | 1    | 1                             | 1    | 1    | 0    | 1.26875V                      |

| 1    | 1    | 0    | 0                             | 0    | 0    | 1    | 1.26250V                      |

| 1    | 1    | 0    | 0                             | 0    | 0    | 0    | 1.25625V                      |

| 1    | 1    | 0    | 0                             | 0    | 1    | 1    | 1.25000V                      |

| 1    | 1    | 0    | 0                             | 0    | 1    | 0    | 1.24375V                      |

| 1    | 1    | 0    | 0                             | 1    | 0    | 1    | 1.23750V                      |

| 1    | 1    | 0    | 0                             | 1    | 0    | 0    | 1.23125V                      |

| 1    | 1    | 0    | 0                             | 1    | 1    | 1    | 1.22500V                      |

| 1    | 1    | 0    | 0                             | 1    | 1    | 0    | 1.21875V                      |

| 1    | 1    | 0    | 1                             | 0    | 0    | 1    | 1.21250V                      |

| 1    | 1    | 0    | 1                             | 0    | 0    | 0    | 1.20625V                      |

| 1    | 1    | 0    | 1                             | 0    | 1    | 1    | 1.20000V                      |

| 1    | 1    | 0    | 1                             | 0    | 1    | 0    | 1.19375V                      |

| 1    | 1    | 0    | 1                             | 1    | 0    | 1    | 1.18750V                      |

| 1    | 1    | 0    | 1                             | 1    | 0    | 0    | 1.18125V                      |

| 1    | 1    | 0    | 1                             | 1    | 1    | 1    | 1.17500V                      |

| 1    | 1    | 0    | 1                             | 1    | 1    | 0    | 1.16875V                      |

| 1    | 1    | 1    | 0                             | 0    | 0    | 1    | 1.16250V                      |

| 1    | 1    | 1    | 0                             | 0    | 0    | 0    | 1,15625V                      |

| 1    | 1    | 1    | 0                             | 0    | 1    | 1    | 1.15000V                      |

| 1    | 1    | 1    | 0                             | 0    | 1    | 0    | 1.14375V                      |

| 1    | 1    | 1    | 0                             | 1    | 0    | 1    | 1.13750V                      |

| 1    | 1    | 1    | 0                             | 1    | 0    | 0    | 1.13125V                      |

| 1    | 1    | 1    | 0                             | 1    | 1    | 1    | 1.12500V                      |

| 1    | 1    | 1    | 0                             | 1    | 1    | 0    | 1.11875V                      |

Copyright ©2021 Richtek Technology Corporation. All rights reserved.

|      |      |      | Pin  | Name |      |      | No official Control (Notice of DACOUT |

|------|------|------|------|------|------|------|---------------------------------------|

| VID4 | VID3 | VID2 | VID1 | VID0 | VID5 | VID6 | Nominal Output Voltage DACOUT         |

| 1    | 1    | 1    | 1    | 0    | 0    | 1    | 1.11250V                              |

| 1    | 1    | 1    | 1    | 0    | 0    | 0    | 1.10625V                              |

| 1    | 1    | 1    | 1    | 0    | 1    | 1    | 1.10000V                              |

| 1    | 1    | 1    | 1    | 0    | 1    | 0    | 1.09375V                              |

| 1    | 1    | 1    | 1    | 1    | 0    | 1    | OFF                                   |

| 1    | 1    | 1    | 1    | 1    | 0    | 0    | OFF                                   |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | OFF                                   |

| 1    | 1    | 1    | 1    | 1    | 1    | 0    | OFF                                   |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1.08750V                              |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1.08125V                              |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1.07500V                              |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1.06875V                              |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1.06250V                              |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1.05625V                              |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1.05000V                              |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1.04375V                              |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1.03750V                              |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1.03125V                              |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1.02500V                              |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1.01875V                              |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1.01250V                              |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 1.00625V                              |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1.00000V                              |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0.99375V                              |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0.98750V                              |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0.98125V                              |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0.97500V                              |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0.96875V                              |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0.96250V                              |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0.95625V                              |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0.95000V                              |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0.94375V                              |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0.93750V                              |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0.93125V                              |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0.92500V                              |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0.91875V                              |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0.91250V                              |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0.90625V                              |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0.90000V                              |

|      |      |      |      | Naminal Cutaut Valtaga DACOLIT |      |      |                               |

|------|------|------|------|--------------------------------|------|------|-------------------------------|

| VID4 | VID3 | VID2 | VID1 | VID0                           | VID5 | VID6 | Nominal Output Voltage DACOUT |

| 0    | 0    | 1    | 1    | 1                              | 1    | 0    | 0.89375V                      |

| 0    | 1    | 0    | 0    | 0                              | 0    | 1    | 0.88750V                      |

| 0    | 1    | 0    | 0    | 0                              | 0    | 0    | 0.88125V                      |

| 0    | 1    | 0    | 0    | 0                              | 1    | 1    | 0.87500V                      |

| 0    | 1    | 0    | 0    | 0                              | 1    | 0    | 0.86875V                      |

| 0    | 1    | 0    | 0    | 1                              | 0    | 1    | 0.86250V                      |

| 0    | 1    | 0    | 0    | 1                              | 0    | 0    | 0.85625V                      |

| 0    | 1    | 0    | 0    | 1                              | 1    | 1    | 0.85000V                      |

| 0    | 1    | 0    | 0    | 1                              | 1    | 0    | 0.84375V                      |

| 0    | 1    | 0    | 1    | 0                              | 0    | 1    | 0.83750V                      |

| 0    | 1    | 0    | 1    | 0                              | 0    | 0    | 0.83125V                      |

Table 3. Output Voltage Program (K8)

| VID4 | VID3 | VID2 | VID1 | VID0 | Nominal Output Voltage DACOUT |

|------|------|------|------|------|-------------------------------|

| 0    | 0    | 0    | 0    | 0    | 1.550                         |

| 0    | 0    | 0    | 0    | 1    | 1.525                         |

| 0    | 0    | 0    | 1    | 0    | 1.500                         |

| 0    | 0    | 0    | 1    | 1    | 1.475                         |

| 0    | 0    | 1    | 0    | 0    | 1.450                         |

| 0    | 0    | 1    | 0    | 1    | 1.425                         |

| 0    | 0    | 1    | 1    | 0    | 1.400                         |

| 0    | 0    | 1    | 1    | 1    | 1.375                         |

| 0    | 1    | 0    | 0    | 0    | 1.350                         |

| 0    | 1    | 0    | 0    | 1    | 1.325                         |

| 0    | 1    | 0    | 1    | 0    | 1.200                         |

| 0    | 1    | 0    | 1    | 1    | 1.275                         |

| 0    | 1    | 1    | 0    | 0    | 1.250                         |

| 0    | 1    | 1    | 0    | 1    | 1.225                         |

| 0    | 1    | 1    | 1    | 0    | 1.200                         |

| 0    | 1    | 1    | 1    | 1    | 1.175                         |

| 1    | 0    | 0    | 0    | 0    | 1.150                         |

| 1    | 0    | 0    | 0    | 1    | 1.125                         |

| 1    | 0    | 0    | 1    | 0    | 1.100                         |

| 1    | 0    | 0    | 1    | 1    | 1.075                         |

| 1    | 0    | 1    | 0    | 0    | 1.050                         |

| 1    | 0    | 1    | 0    | 1    | 1.025                         |

| 1    | 0    | 1    | 1    | 0    | 1.000                         |

| 1    | 0    | 1    | 1    | 1    | 0.975                         |

| 1    | 1    | 0    | 0    | 0    | 0.950                         |

| 1    | 1    | 0    | 0    | 1    | 0.925                         |

| 1    | 1    | 0    | 1    | 0    | 0.900                         |

| 1    | 1    | 0    | 1    | 1    | 0.875                         |

| 1    | 1    | 1    | 0    | 0    | 0.850                         |

| 1    | 1    | 1    | 0    | 1    | 0.825                         |

| 1    | 1    | 1    | 1    | 0    | 0.800                         |

| 1    | 1    | 1    | 1    | 1    | Shutdown                      |

Note: (1) 0 : Connected to GND

(2) 1 : Open

Table 4. Output Voltage Program (K8\_M2)

|      |      | I    | Pin Name |      |      | Naminal Output Valtage DACOLIT |

|------|------|------|----------|------|------|--------------------------------|

| VID5 | VID4 | VID3 | VID2     | VID1 | VID0 | Nominal Output Voltage DACOUT  |

| 0    | 0    | 0    | 0        | 0    | 0    | 1.5500                         |

| 0    | 0    | 0    | 0        | 0    | 1    | 1.5250                         |

| 0    | 0    | 0    | 0        | 1    | 0    | 1.5000                         |

| 0    | 0    | 0    | 0        | 1    | 1    | 1.4750                         |

| 0    | 0    | 0    | 1        | 0    | 0    | 1.4500                         |

| 0    | 0    | 0    | 1        | 0    | 1    | 1.4250                         |

| 0    | 0    | 0    | 1        | 1    | 0    | 1.4000                         |

| 0    | 0    | 0    | 1        | 1    | 1    | 1.3750                         |

| 0    | 0    | 1    | 0        | 0    | 0    | 1.3500                         |

| 0    | 0    | 1    | 0        | 0    | 1    | 1.3250                         |

| 0    | 0    | 1    | 0        | 1    | 0    | 1.3000                         |

| 0    | 0    | 1    | 0        | 1    | 1    | 1.2750                         |

| 0    | 0    | 1    | 1        | 0    | 0    | 1.2500                         |

| 0    | 0    | 1    | 1        | 0    | 1    | 1.2250                         |

| 0    | 0    | 1    | 1        | 1    | 0    | 1.2000                         |

| 0    | 0    | 1    | 1        | 1    | 1    | 1.1750                         |

| 0    | 1    | 0    | 0        | 0    | 0    | 1.1500                         |

| 0    | 1    | 0    | 0        | 0    | 1    | 1.1250                         |

| 0    | 1    | 0    | 0        | 1    | 0    | 1.1000                         |

| 0    | 1    | 0    | 0        | 1    | 1    | 1.0750                         |

| 0    | 1    | 0    | 1        | 0    | 0    | 1.0500                         |

| 0    | 1    | 0    | 1        | 0    | 1    | 1.0250                         |

| 0    | 1    | 0    | 1        | 1    | 0    | 1.0000                         |

| 0    | 1    | 0    | 1        | 1    | 1    | 0.9750                         |

| 0    | 1    | 1    | 0        | 0    | 0    | 0.9500                         |

| 0    | 1    | 1    | 0        | 0    | 1    | 0.9250                         |

| 0    | 1    | 1    | 0        | 1    | 0    | 0.9000                         |

| 0    | 1    | 1    | 0        | 1    | 1    | 0.8750                         |

| 0    | 1    | 1    | 1        | 0    | 0    | 0.8500                         |

| 0    | 1    | 1    | 1        | 0    | 1    | 0.8250                         |

| 0    | 1    | 1    | 1        | 1    | 0    | 0.8000                         |

| 0    | 1    | 1    | 1        | 1    | 1    | 0.7750                         |

| 1    | 0    | 0    | 0        | 0    | 0    | 0.7625                         |

| 1    | 0    | 0    | 0        | 0    | 1    | 0.7500                         |

|      | Pin Name |      |      |      | Name's at Octoor Valters DACOUT |                               |

|------|----------|------|------|------|---------------------------------|-------------------------------|

| VID5 | VID4     | VID3 | VID2 | VID1 | VID0                            | Nominal Output Voltage DACOUT |

| 1    | 0        | 0    | 0    | 1    | 0                               | 0.7375                        |

| 1    | 0        | 0    | 0    | 1    | 1                               | 0.7250                        |

| 1    | 0        | 0    | 1    | 0    | 0                               | 0.7125                        |

| 1    | 0        | 0    | 1    | 0    | 1                               | 0.7000                        |

| 1    | 0        | 0    | 1    | 1    | 0                               | 0.6875                        |

| 1    | 0        | 0    | 1    | 1    | 1                               | 0.6750                        |

| 1    | 0        | 1    | 0    | 0    | 0                               | 0.6625                        |

| 1    | 0        | 1    | 0    | 0    | 1                               | 0.6500                        |

| 1    | 0        | 1    | 0    | 1    | 0                               | 0.6375                        |

| 1    | 0        | 1    | 0    | 1    | 1                               | 0.6250                        |

| 1    | 0        | 1    | 1    | 0    | 0                               | 0.6125                        |

| 1    | 0        | 1    | 1    | 0    | 1                               | 0.6000                        |

| 1    | 0        | 1    | 1    | 1    | 0                               | 0.5875                        |

| 1    | 0        | 1    | 1    | 1    | 1                               | 0.5750                        |

| 1    | 1        | 0    | 0    | 0    | 0                               | 0.5625                        |

| 1    | 1        | 0    | 0    | 0    | 1                               | 0.5500                        |

| 1    | 1        | 0    | 0    | 1    | 0                               | 0.5375                        |

| 1    | 1        | 0    | 0    | 1    | 1                               | 0.5250                        |

| 1    | 1        | 0    | 1    | 0    | 0                               | 0.5125                        |

| 1    | 1        | 0    | 1    | 0    | 1                               | 0.5000                        |

| 1    | 1        | 0    | 1    | 1    | 0                               | 0.4875                        |

| 1    | 1        | 0    | 1    | 1    | 1                               | 0.4750                        |

| 1    | 1        | 1    | 0    | 0    | 0                               | 0.4625                        |

| 1    | 1        | 1    | 0    | 0    | 1                               | 0.4500                        |

| 1    | 1        | 1    | 0    | 1    | 0                               | 0.4375                        |

| 1    | 1        | 1    | 0    | 1    | 1                               | 0.4250                        |

| 1    | 1        | 1    | 1    | 0    | 0                               | 0.4125                        |

| 1    | 1        | 1    | 1    | 0    | 1                               | 0.4000                        |

| 1    | 1        | 1    | 1    | 1    | 0                               | 0.3875                        |

| 1    | 1        | 1    | 1    | 1    | 1                               | 0.3750                        |

Note: (1) 0 : Connected to GND

(2) 1 : Open

<sup>(3)</sup> The voltage above are load independent for desktop and server platforms. For mobile platforms the voltage above correspond to zero load current.

## **Functional Pin Description**

| Pin No.             | Pin Name               | Pin Function                                                                                                  |

|---------------------|------------------------|---------------------------------------------------------------------------------------------------------------|

| 1                   | FBRTN                  | Negative Remote Sense Pin of Output Voltage.                                                                  |

| 2                   | QR1                    | Quick Response Setting Pins for Load Transition.                                                              |

| 3                   | QR2                    | Quick Response Setting Pins for Load Transition.                                                              |

| 4                   | SS/EN                  | Connect this pin to GND by a capacitor to adjust soft start time. Pull this pin to GND to disable controller. |

| 5                   | COMP                   | Output of the Error-Amplifier and Input of the PWM Comparator.                                                |

| 6                   | FB                     | Inverting Input of the Error-Amplifier.                                                                       |

| 7                   | OFS                    | Connect this pin to GND or 5V by a resistor to set no-load offset voltage.                                    |

| 8                   | RT                     | Connect this Pin to GND by a Resistor to Adjust Frequency.                                                    |

| 9                   | ADJ                    | Connect this Pin to GND by a Resistor to Set Load Line.                                                       |

| 10                  | IMAX                   | Negative Input of OCP Comparator. (Positive input of OCP comparator is ADJ).                                  |

| 11                  | IMAXPSI                | OCP Setting in Power Saving Mode.                                                                             |

| 12                  | IMONFB                 | Current Monitor Gain/Offset Adjustment.                                                                       |

| 13                  | IMON                   | Current Monitor Output.                                                                                       |

| 14, 17, 18, 21      | ISP4, ISP3, ISP2, ISP1 | Positive Current Sense Pin of phase 1, 2, 3 and 4.                                                            |

| 15, 16, 19, 20      | ISN4, ISN3, ISN2, ISN1 | Negative Current Sense Pin of phase 1, 2, 3 and 4.                                                            |

| 22                  | VRHOT                  | Temperature Monitor Output.                                                                                   |

| 23                  | TSEN                   | Temperature Sense Input.                                                                                      |

| 24                  | VCC5                   | 5V LDO Output for System Power Supply.                                                                        |

| 25, 26              | PWM4, PWM3             | PWM Output for Phase 4 and Phase 3.                                                                           |

| 27, 35              | BOOT2, BOOT1           | Bootstrap Supply for Phase 2 and Phase 1.                                                                     |

| 28, 34              | UGATE2, UGATE1         | Upper Gate Driver for Phase 2 and Phase 1.                                                                    |

| 29, 33              | PHASE2, PHASE1         | Switching Node of Phase 2 and Phase 1.                                                                        |

| 30, 32              | LGATE2, LGATE1         | Lower Gate Driver for Phase 2 and Phase 1.                                                                    |

| 31                  | VCC12                  | IC Power Supply. Connect to 12V.                                                                              |

| 36                  | PWRGD                  | Power Good Indicator.                                                                                         |

| 37                  | EN/VTT                 | VTT Voltage Detector Input.                                                                                   |

| 38 to 45            | VID7 to VID0           | Voltage Identification Input for DAC.                                                                         |

| 47                  | PSI                    | Power Status Indicator II.                                                                                    |

| 48                  | PS                     | Dynamic Phase Control Threshold Input.                                                                        |

| 46                  | VIDSEL                 | VID DAC Selection Pin.                                                                                        |

| 49<br>(Exposed pad) | GND                    | The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.           |

#### **VID Table Selection**

| TID TUDIO CONCUION |         |        |  |  |  |  |  |

|--------------------|---------|--------|--|--|--|--|--|

| VIDSEL             | VID [7] | Table  |  |  |  |  |  |

| VTT                | Х       | VR11   |  |  |  |  |  |

| GND                | Χ       | VR10.x |  |  |  |  |  |

| VCC5               | VTT     | K8     |  |  |  |  |  |

| VCC5               | GND     | K8_M2  |  |  |  |  |  |

Copyright ©2021 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

DS8862-03 September 2021

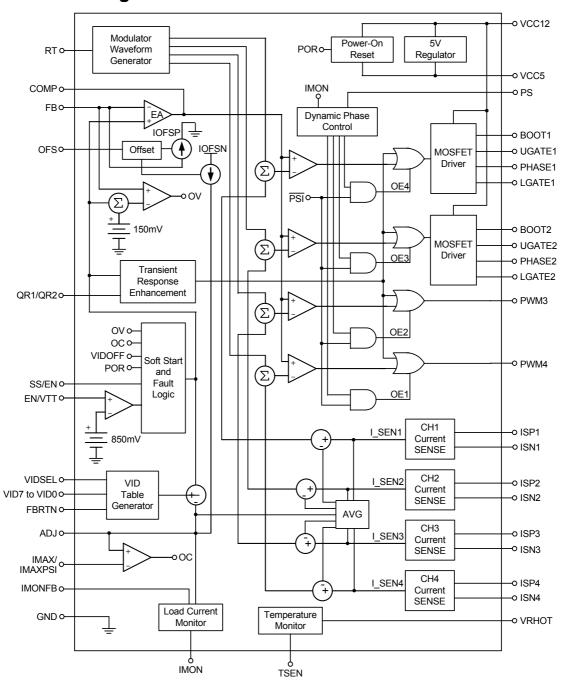

## **Function Block Diagram**

## Absolute Maximum Ratings (Note 1)

| Supply Input Voltage                                                        |                                                       |

|-----------------------------------------------------------------------------|-------------------------------------------------------|

| • BOOTx to PHASEx                                                           |                                                       |

| PHASEx to GND                                                               |                                                       |

| DC                                                                          |                                                       |

| < 20ns                                                                      | 5V to 30V                                             |

| • UGATEx to GND                                                             | $(V_{PHASE} - 0.3V)$ to $(V_{BOOT} + 0.3V)$           |

| < 20ns                                                                      | (V <sub>PHASE</sub> – 5V) to (V <sub>BOOT</sub> + 5V) |

| • LGATEx to GND                                                             | (GND – 0.3V) to (V <sub>CC</sub> + 0.3V)              |

| < 20ns                                                                      | (GND- 5V) to (V <sub>CC</sub> + 5V)                   |

| • Others Pins                                                               | – 0.3V to 6.5V                                        |

| Input/Output Voltage                                                        |                                                       |

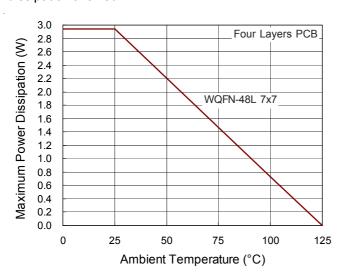

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                                                       |

| WQFN-48L 7x7                                                                | 2.941W                                                |

| Package Thermal Resistance (Note 2)                                         |                                                       |

| WQFN–48L 7x7, $\theta_{JA}$                                                 | 34°C/W                                                |

| WQFN-48L 7x7, $\theta_{JC}$                                                 | 7°C/W                                                 |

| Junction Temperature                                                        | 150°C                                                 |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C                                                 |

| ESD Susceptibility (Note 3)                                                 |                                                       |

| HBM (Human Body Mode)                                                       | 2kV                                                   |

| MM (Machine Mode)                                                           | 200V                                                  |

## **Recommended Operating Conditions** (Note 4)

| <ul> <li>Supply Voltage, \</li> </ul> | VCC12       | - 12V ± 10%   |

|---------------------------------------|-------------|---------------|

| <ul> <li>Junction Tempera</li> </ul>  | ature Range | 40°C to 125°C |

• Ambient Temperature Range ----- 0°C to 70°C

#### **Electrical Characteristics**

(VCC12 = 12V,  $V_{GND}$  = 0V,  $T_A$  = 25°C, unless otherwise specified)

| Parameter              | Symbol               | Test Conditions                   | Min  | Тур | Max  | Unit |

|------------------------|----------------------|-----------------------------------|------|-----|------|------|

| VCC12 Supply Input     |                      |                                   |      |     |      |      |

| VCC12 Supply Voltage   | VCC12                |                                   | 10.8 | 12  | 13.2 | V    |

| VCC12 Supply Current   | I <sub>CC</sub>      |                                   |      | 6   |      | mA   |

| VCC5 Power             |                      |                                   |      |     |      |      |

| VCC5 Supply Voltage    | VCC5                 | I <sub>LOAD</sub> = 10mA (Note 6) | 4.75 | 5.0 | 5.25 | V    |

| VCC5 Output Sourcing   | I <sub>VCC5</sub>    |                                   | 10   |     |      | mA   |

| Power On Reset         |                      |                                   |      |     |      |      |

| VCC12 Rising Threshold | V <sub>VCC12TH</sub> | VCC12 Rising                      | 9.2  | 9.6 | 10   | V    |

| VCC12 Hysteresis       | V <sub>VCC12HY</sub> | VCC12 Falling                     |      | 0.9 |      | V    |

| VCC5 Rising Threshold  | V <sub>V</sub> CC5TH |                                   | 4.4  | 4.6 | 4.8  | V    |

| VCC5 Hysteresis        | V <sub>VCC5HY</sub>  |                                   |      | 0.4 |      | V    |

| Parameter                  | Symbol               | Test Conditions                                              | Min  | Тур  | Max  | Unit |

|----------------------------|----------------------|--------------------------------------------------------------|------|------|------|------|

| EN/VTT                     |                      |                                                              |      |      | l    |      |

| EN/VTT Rising Threshold    | V <sub>ENVTT</sub>   | EN/VTT Rising                                                | 0.8  | 0.85 | 0.9  | V    |

| Enable Hysteresis          | VENVTTHY             | EN/VTT Falling                                               | _    | 100  | _    | mV   |

| Reference Voltage accura   | су                   | -                                                            |      |      |      |      |

|                            | Ī                    | 1V to 1.6V                                                   | -0.5 |      | 0.5  | %    |

| DAC Accuracy               |                      | 0.8V to 1V                                                   | -5   |      | 5    | mV   |

| -                          |                      | 0.5V to 0.8V                                                 | -8   |      | 8    | mV   |

| Error Amplifier            |                      |                                                              |      |      |      |      |

| DC Gain                    | A <sub>DC</sub>      | No Load                                                      |      | 80   |      | dB   |

| Gain-Bandwidth             | GBW                  | C <sub>LOAD</sub> = 10pF                                     |      | 10   |      | MHz  |

| Slew Rate                  | SR                   | CLOAD = 10pF                                                 | 10   |      |      | V/μs |

| Output voltage range       | V <sub>COMP</sub>    | - 10, i.s i.e.                                               | 0.5  |      | 3.6  | V    |

| Max Current                | I <sub>EA_SLEW</sub> | Slew                                                         | 300  |      |      | μΑ   |

| Power Sequence             |                      |                                                              |      |      |      |      |

| PWRGD Low Voltage          | V <sub>PGOOD</sub>   | I <sub>PWRGD</sub> = 4mA                                     |      |      | 0.4  | V    |

| Soft-Start Delay           | T <sub>D1</sub>      | - Miles                                                      |      | 2    |      | ms   |

| V <sub>BOOT</sub> Duration | T <sub>D3</sub>      |                                                              |      | 0.8  |      | ms   |

| PWRGD Delay                | T <sub>D5</sub>      | Measured the time form V <sub>BOOT</sub> change to PWRGD = 1 |      | 1.6  |      | ms   |

| Current Sense Amplifier    |                      |                                                              |      |      |      |      |

| Max Current                | I <sub>GMMAX</sub>   | V <sub>CSP</sub> = 1.3V<br>Sink Current from CSN             | 100  |      |      | μΑ   |

| Input Offset Voltage       | Voscs                |                                                              | -2   | 0    | 2    | mV   |

| Running Frequency          | f <sub>OSC</sub>     | $R_{RT} = 40 k\Omega$                                        | 270  | 300  | 330  | kHz  |

| RT Pin Voltage             | V <sub>RT</sub>      | $R_{RT} = 40 k\Omega$                                        | 0.76 | 0.8  | 0.84 | V    |

| Ramp Slope                 | $V_{RAMP}$           | $R_{RT} = 40 k\Omega$                                        |      | 22   |      | %/V  |

| Soft Start                 |                      |                                                              |      |      |      |      |

| Soft Start Current         | I <sub>SS1</sub>     | Slew                                                         | 12   | 16   | 20   | μА   |

| VID Change Current         | I <sub>SS2</sub>     | Slew                                                         | 120  | 160  | 200  | μА   |

| Gate Driver                |                      |                                                              |      |      |      |      |

| UGATE Drive Source         | Rugatesr             | BOOT – PHASE = 8V<br>250mA Source Current                    |      | 1    |      | Ω    |

| UGATE Drive Sink           | R <sub>UGATEsk</sub> | BOOT – PHASE = 8V<br>250mA Sink Current                      |      | 1    |      | Ω    |

| LGATE Drive Source         | R <sub>LGATEsr</sub> | V <sub>LGATE</sub> = 8V                                      |      | 1    |      | Ω    |

| LGATE Drive Sink           | R <sub>LGATEsk</sub> | 250mA Sink Current                                           |      | 0.8  |      | Ω    |

| Protection                 |                      |                                                              |      |      | 1    |      |

| Over-Voltage Threshold     | V <sub>OVP</sub>     | Sweep FB Voltage, V <sub>FB</sub> – V <sub>EAP</sub>         | 125  | 150  | 175  | mV   |

| Over-Current Threshold     | V <sub>OCP</sub>     | Sweep IMAX Voltage, V <sub>IMAX</sub> – V <sub>ADJ</sub>     | -10  | 0    | 10   | mV   |

| Parameter                                            | Symbol                           | Test Conditions                                    | Min  | Тур                            | Max   | Unit |

|------------------------------------------------------|----------------------------------|----------------------------------------------------|------|--------------------------------|-------|------|

| Dynamic Characteristic                               |                                  |                                                    |      |                                |       |      |

| UGATE Rise Time                                      | t <sub>rUGATE</sub>              |                                                    |      | 15                             | -     | ns   |

| UGATE Fall Time                                      | tfUGATE                          | Ciss = 3000n                                       |      | 10                             |       | ns   |

| LGATE Rise Time                                      | t <sub>rLGATE</sub>              | Ciss = 3000p                                       |      | 15                             |       | ns   |

| LGATE Fall Time                                      | t <sub>fLGATE</sub>              |                                                    |      | 10                             | 1     | ns   |

| Current Sourcing from PS pin to Set V <sub>ps2</sub> | I <sub>ps</sub>                  | When V <sub>ps2</sub> Is Needed by Control Circuit | 86.4 | 96                             | 105.6 | μΑ   |

| Input Threshold                                      |                                  |                                                    |      |                                |       |      |

| VID7 to VID0,<br>VIDSEL Rising Threshold             | VID7 to 0,<br>V <sub>IDSEL</sub> | VID7 to VID0 Rising,<br>VIDSEL Rising              |      | 1/2V <sub>TT</sub> +<br>12.5mV |       | V    |

| VID7 to VID0 Hysteresis                              | VID7 to 0_Hy                     | VID7 to VID0 Falling                               |      | 25                             |       | mV   |

| PSI Rising Threshold                                 | V <sub>PSI</sub>                 | PSI Rising                                         |      | 1/2V <sub>TT</sub> +<br>12.5mV |       | V    |

- **Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2.  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a high effective four layers thermal conductivity test board of JEDEC 51-7 thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. The maximum output voltage of power monitor will be restricted by EN/VTT pin input voltage.

- Note 6. Test condition: RT8862 normal operating, an extra static DC current load 10mA applying at VCC5 pin.

## **Typical Operating Characteristics**

## **Application Information**

The RT8862 is a 4/3/2/1-phase synchronous buck DC/DC converter with 2 embedded MOSFET drivers. The internal VID DAC is designed to interface with the Intel VR11.x/ 10.x and AMD K8/K8 M2 compatible CPUs.

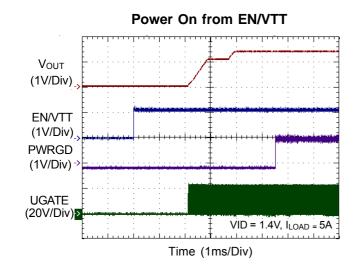

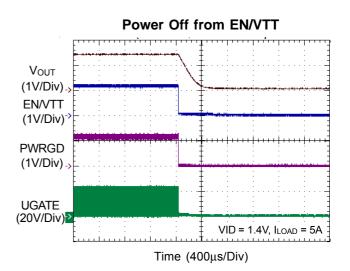

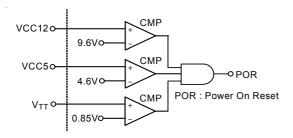

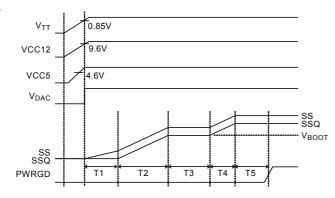

#### **Power Ready Detection**

During start-up, the RT8862 will detect VCC12, VCC5 and  $V_{TT}$ . When VCC12 > 9.6V, VCC5 > 4.6V and  $V_{TT}$  > 0.85V, POR will go high. POR (Power On Reset) is the internal signal to indicate all powers are ready to let the RT8862 and the companioned MOSFET drivers work properly. When POR = L, the RT8862 will try to turn off both high side and low side MOSFETs.

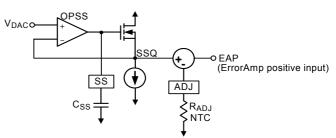

Figure 1. Circuit for Power Ready Detection

#### **Phase Detection**

The number of operational phases is determined by the internal circuitry that monitors the ISNn voltages during start up. Normally, the RT8862 operates as a 4-phase PWM controller. Pull ISN4 and ISP4 to VCC5 programs 3-phase operation. Pull ISN3 and ISP3 to VCC5 programs 2-phase operation. The RT8862 detects the voltage of ISN4 and ISN3 POR rising edge. At the rising edge, the RT8862 detects whether the voltage of ISN4 and ISN3 are higher than "VCC5 – 1V" respectively to decide how many phases should be active. Phase detection is only active during start up. When POR = H, the number of operational phases is determined and latched. The unused PWM pins can be connected either to 5V, GND or left floating.

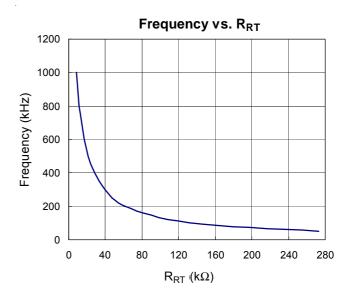

#### **Phase Switching Frequency**

The phase switching frequency of the RT8862 is set by an external resistor connected from the RT pin to GND. The frequency follows the graph in Figure 2.

Figure 2. R<sub>RT</sub> vs Phase Switching Frequency

#### **Soft Start**

Output current of OPSS (ISS) is limited and variant

Figure 4. Circuit for Soft Start and Dynamic VID

The V<sub>OUT</sub> start-up time is set by a capacitor from the SS pin to GND. In power on reset state (POR = L), the SS pin is held at GND. After power on reset stae (POR = H) and an extra delay of  $1600\mu s$ ,  $V_{SS}$  and  $V_{SSQ}$  begin to rise till  $V_{SSQ} = V_{BOOT}$ . When  $V_{SSQ} = V_{BOOT}$ , the RT8862 stays in this state for 800µs, waiting for valid VID code sent by CPU. After receiving valid VID code, V<sub>OUT</sub> continues ramping up or down to the voltage specified by VID code. Before PWRGD = H, output current of OPSS  $(I_{SS})$  is limited to  $\mu A$  (I<sub>SS1</sub>). When PWRGD = H, I<sub>SS</sub> is limited to  $80\mu A$  (I<sub>SS2</sub>). The soft start waveform is shown in Figure 5.

Figure 5. Soft Start Waveforms

$V_{\text{OUT}}$  will trace  $V_{\text{EAP}}$  which is equal to " $V_{\text{SSQ}} - V_{\text{ADJ}}$ ".  $V_{\text{ADJ}}$  is a small voltage signal which is proportional to  $I_{\text{OUT}}$ . This voltage is used to generate loadline and will be described later. T1 is the delay time from power\_on\_reset state to the beginning of  $V_{\text{OUT}}$  rising.

T1 =

$$1600\mu s + 0.6V \times C_{SS} / I_{SS1}$$

(1)

T2 is the soft start time from  $V_{OUT} = 0$  to  $V_{OUT} = V_{BOOT}$ .

$$T2 = V_{BOOT} \times C_{SS} / I_{SS1}$$

(2)

T3 is the dwelling time for  $V_{OUT} = V_{BOOT}$ . T3 = 800us.

T4 is the soft start time from  $V_{OUT} = V_{BOOT}$  to  $V_{OUT} = V_{DAC}$ .

$$T4 \sim = |V_{DAC} - V_{BOOT}| \times C_{SS}/I_{SS1}$$

(3)

T5 is the power good delay time, T5  $\sim$ = 1600 $\mu$ s.

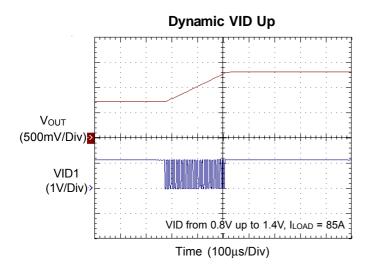

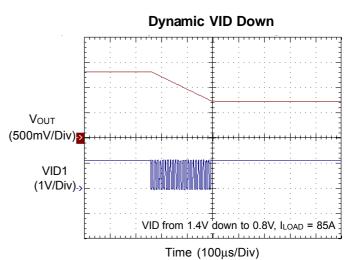

#### **Dynamic VID**

The RT8862 can accept VID input changing while the controller is running. This allows the output voltage (V<sub>OUT</sub>) to change while the DC/DC converter is running and supplying current to the load. This is commonly referred to as VID on-the-fly (OTF). A VID OTF can occur under either light or heavy load conditions. The CPU changes the VID inputs in multiple steps from the start code to the finish code. This change can be positive or negative. Theoretically, V<sub>OUT</sub> should follow V<sub>DAC</sub> which is a staircase waveform. In RT8862, as mentioned in soft start session,  $V_{DAC}$  slew rate is limited by  $I_{SS2}/C_{SS}$  when PWRGD = H. This slew rate limiter works as a low pass filter of V<sub>DAC</sub> and makes the bandwidth of V<sub>DAC</sub> waveform finite. By smoothening V<sub>DAC</sub> staircase waveform, V<sub>OUT</sub> will no longer overshoot or undershoot. On the other hand, CSS will increase the settling time of V<sub>OUT</sub> during VID OTF. In most cases, 1nF to 30nF ceramic capacitor is suitable for Css.

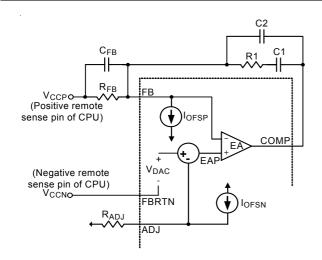

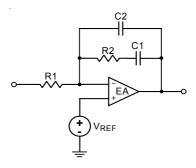

#### **Output Voltage Differential Sensing**

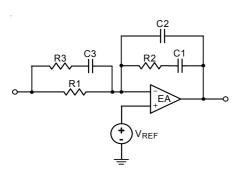

The RT8862 uses differential sensing by a high gain low offset Error Amplifier. The CPU voltage is sensed between the FB and FBRTN pins. A resistor ( $R_{FB}$ ) connects FB pin and the positive remote sense pin of the CPU ( $V_{CCP}$ ). FBRTN pin connects to the negative remote sense pin of CPU ( $V_{CCN}$ ) directly. The Error Amplifier compares EAP (=  $V_{DAC}$  – $V_{ADJ}$ ) with the  $V_{FB}$  to regulate the output voltage.

#### No Load Offset

In Figure 6,  $I_{OFSN}$  or  $I_{OFSP}$  are used to generate no-load offset. Either  $I_{OFSN}$  or  $I_{OFSP}$  is active during normal operation. It should be noted that users can only enable one polarity of no-load offset. Do not connect OFS pin to GND and to  $V_{CC5}$  at the same time. Connect a resistor from OFS pin to GND to activate  $I_{OFSN}$ .  $I_{OFSN}$  flows through  $R_{ADJ}$  from ADJ pin to GND. In this case, negative no-load offset voltage  $(V_{OFSN})$  is generated.

$$V_{OFSN} = I_{OFSN} \times R_{ADJ} = 0.8 \times R_{ADJ}/R_{OFS}$$

(4)

Connect a resistor from OFS pin to  $V_{CC}5$  to activate  $I_{OFSP}$ .  $I_{OFSP}$  flows through  $R_{FB}$  from the  $V_{CCP}$  to FB pin. In this case, positive no-load offset voltage ( $V_{OFSP}$ ) is generated.

When OFS pin is connected to VCC5 through a resistor, the positive no-load offset can be calculated as:

$$V_{OFSP} = I_{OFSP} \times R_{FB} = 6.4 \times \frac{R_{FB}}{R_{OFS}}$$

(5)

The RT8862 provides wide range no-load positive offset for over-clocking applications. The  $I_{OFSP}$  capability can supply from  $30\mu A$  to  $640\mu A$ , which means in Equation (5),  $R_{OFS}$  can range from  $240k\Omega$  to  $10k\Omega$ . Other resistances of  $R_{OFS}$  exceeding this range can also provide no-load positive offset but cannot be guaranteed by Equation (5).

Figure 6. Circuit for V<sub>OUT</sub> Differential Sensing and No Load Offset

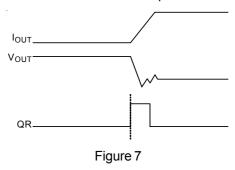

#### **Load Transient Quick Response**

The RT8862 utilizes a new quick response feature to supply heavy load current demand during instantaneous load application transient. The RT8862 detects load transient and reacts via VOUT pin. When VOUT drops during load application transient, the quick response comparator will send asserted signals to turn on high side MOSFETs and turn off low side MOSFETs. The QR signal will turn on all phase's high side MOSFETs while turning off low side MOSFETs also. Therefore, the influence of total quick response function of RT8862 is adjustable, and the magnitude of quick response is flexible via fine-tuning the resistor connected to QR1 or QR2 pin.

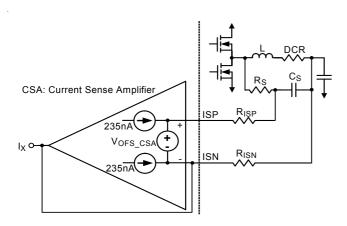

#### **Output Current Sensing**

The RT8862 provides low input offset current-sense amplifier (CSA) to monitor the output current of every phase. Output current of CSA (Ix[n]) is used for phase current balance and active voltage position. In this inductor current sensing topology, R<sub>S</sub> and C<sub>S</sub> must be set according to the equation below:

$$L/DCR = R_S \times C_S \tag{6}$$

Then the output current of CSA will follow the equation

$$I_X = [I_L \times DCR - V_{OFS-CSA} + 235n \times (R_{CSP} - R_{CSN})]$$

$$/R_{CSN}$$

(7)

235nA is typical value of CSA input offset current. V<sub>OFS-CSA</sub> is the input offset voltage of CSA. V<sub>OFS-CSA</sub> of RT8862 is smaller than +/- 1mV. Usually, "Vofs-csa + 235n x (R<sub>CSP</sub> - R<sub>CSN</sub>)" is negligible except at very light load and the equation can be simplified as the equation below:

$$I_X = I_L \times DCR/R_{CSN}$$

(8)

#### Loadline

Output current of CSA is summed and averaged in the RT8862. Then  $0.5\Sigma(I_X[n])$  is sent to ADJ pin. Because  $\Sigma I_X[n]$  is a PTC (Positive Temperature Coefficient) current, an NTC (Negative Temperature Coefficient) resistor is needed to connect ADJ pin to GND. If the NTC resistor is properly selected to compensate the temperature coefficient of  $I_X[n]$ , the voltage on ADJ pin will be proportional to I<sub>OUT</sub> without temperature effect. In the RT8862, the positive input of Error Amplifier is "VDAC - $V_{ADJ}$ ".  $V_{OUT}$  will follow " $V_{DAC} - V_{ADJ}$ ", too. Thus, the output voltage decreasing linearly with I<sub>OUT</sub> is obtained. The loadline is defined as

LL(loadline) =

$$\Delta V_{OUT}/\Delta I_{OUT} = \Delta V_{ADJ}/\Delta I_{OUT}$$

= 0.5 x DCR x R<sub>ADJ</sub>/R<sub>CSN</sub> (9)

Briefly, the resistance of RADJ sets the resistance of loadline. The temperature coefficient of R<sub>ADJ</sub> compensates the temperature effect of loadline.

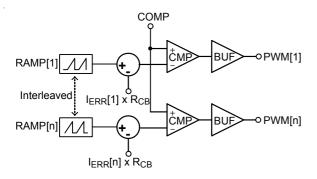

#### **Current Balance**

In Figure 8,  $I_X[n]$  is the current signal which is proportional to current flowing through phase n. In Figure 9, the current error signals  $I_{ERR}n$  (=  $I_X[n] - AVG(I_X[n])$ ) are used to raise or lower the internal sawtooth waveforms (RAMP[1] to RAMP[n]) which are compared with Error Amplifier output (COMP) to generate PWM signal. The raised sawtooth waveform will decrease the PWM duty of the corresponding phase while the lowered will increase. Eventually, current flowing through each phase will be balanced.

Figure 8. Circuit for Phase Current Sensing

Figure 9. Circuit for Phase Current Balance

#### **Adjusting Phase Current**

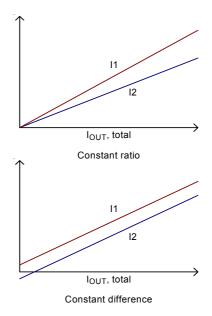

If phase current is not balanced due to asymmetric PCB layout of power stage, external resistors can be adjusted to correct current imbalance. Figure 10 shows two types of current imbalance, constant ratio type and constant difference type.

If the initial current distribution is constant ratio type, according to Equation (8), reduce R<sub>CSN</sub>[1] can reduce I<sub>L</sub>[1] and improve current balance. If the initial current distribution is constant difference type, according to Equation (7), increase R<sub>CSP</sub>[1] can reduce I<sub>L</sub>[1] and improve current balance.

Figure 10. Phase Current vs. Total Current

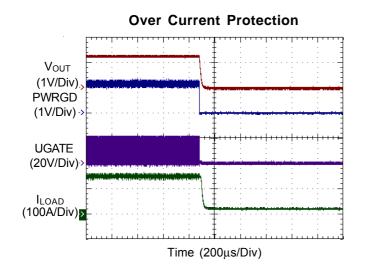

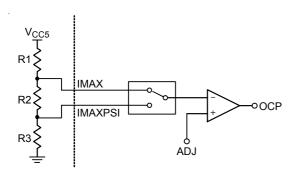

#### **Over Current Protection (OCP)**

RT8862 provides single phase OCP and multi-phase OCP according to the operation condition. In Figure 11, single phase OCP (IMAXPSI) and multi-phase OCP (IMAX) thresholds can be set by external resistors:

$$V_{IMAX} = V_{CC5} \times \frac{R2 + R3}{R1 + R2 + R3}$$

(10)

$$V_{\text{IMAXPSI}} = V_{\text{CC5}} \times \frac{R3}{R1 + R2 + R3} \tag{11}$$

Once V<sub>ADJ</sub> is larger than the negative input of CP comparator, OCP will be triggered and latched, and RT8862 will turn off both high side and low side MOSFETs of all phases. A 20us delay after OCP detection is used to prevent false trigger.

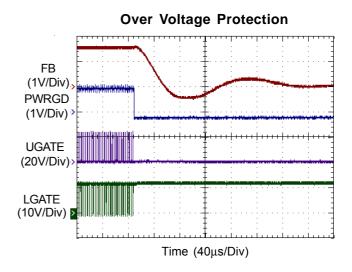

#### **Over Voltage Protectiom (OVP)**

The over voltage protection monitors the output voltage via the FB pin. Once V<sub>FB</sub> exceeds "V<sub>EAP</sub> + 150mV", OVP is triggered and latched. RT8862 will try to turn on low side MOSFET and turn off high side MOSFET to protect CPU. A 20us delay is used in OVP detection circuit to prevent false trigger.

Figure 11. Over Current Protection

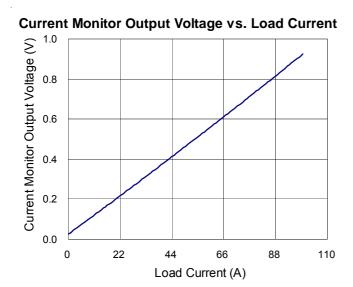

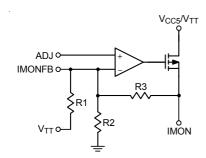

#### **Output Current Monitoring (IMON)**

The RT8862 senses load current and output a voltage signal to indicate the instantaneous load current status. Since the sensed total current is injected into the resistors connected to ADJ pin, ADJ voltage than is used for IMON function as shown in Figure 12. Through the resistor network R1, R2 and R3, IMON voltage will be proportional to ADJ pin voltage according to the Equation :

$$V_{IMON} = \frac{R3}{R1 /\!\!/ R2 /\!\!/ R3} \times V_{ADJ} - \frac{R3}{R1} \times V_{TT}$$

(12)

Figure 12. Output Current Monitoring

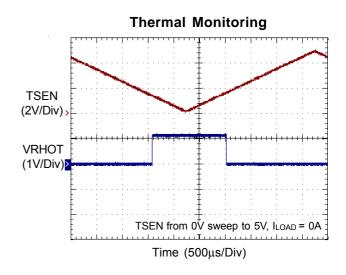

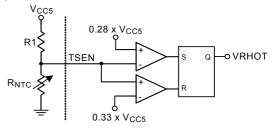

#### **Thermal Monitoring (VRHOT)**

The RT8862 provides thermal monitoring function via sensing TSEN pin voltage. Through the voltage divider R1 and R<sub>NTC</sub>, the voltage of TSEN is typically set to be higher than  $0.33 \times V_{CC5}$  when ambient temperature is lower than VRHOT assertion target. When ambient temperature rises, TSEN voltage will fall, and VRHOT signal will be set to high if TSEN voltage drops below 0.28 x V<sub>CC5</sub>. Accordingly, VRHOT will be reset to low once TSEN voltage rises above 0.33 x V<sub>CC5</sub>. Correctly choose the resistance of R1 and R<sub>NTC</sub> can assert and de-assert VRHOT accurately at target ambient temperature.

Figure 13. Thermal Monitoring

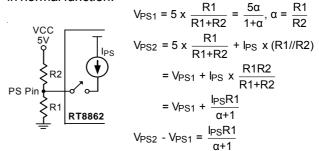

#### Power State Indicator (PSI)

The RT8862 supports PSI# function for VR11.1 CPUs and platform users. The RT8862 will monitor PSI pin input voltage to change the operating state. When PSI is high (higher than  $1/2 V_{TT} + 12.5 mV$ ), the RT8862 operates as a full-phase interleaving PWM controller and all phases are active. When input voltage is low (lower than  $V_{TT}$  + 12.5mV), the RT8862 will change to single phase operation mode and only phase 1 is active. Since phase 2 includes embedded driver, the RT8862 will automatically disable phase 2 by forcing UGATE2 and LGATE2 into high impedance state when input voltage is low. The RT8862 will also disable phase 3 and phase 4 by sending continuous tri-state signals (~2.5V) from PWM3 and PWM4 to external drivers when input voltage is low. Therefore, 2 external drivers which support tri-state shutdown should be used if PSI function is considered, and the RT9619 is recommended to be the external drivers for VR11.1 compatibility.

During PSI asserted period, e.g., input voltage is low, if the RT8862 receives dynamic VID change command, the RT8862 will enter interleaving mode operation and all phases will be activated. PSI command will be ignored during dynamic VID operation, and PSI will be blanked for about 100us after dynamic VID change is completed.

#### **Dynamic Phase Control**

RT8862 has the ability of automatically control phase numbers according to the total load current. This feature optimizes system efficiency over a wide load range. Connect a resistive voltage divider to PS pin to define the two thresholds,  $V_{PS1}$  and  $V_{PS2}$ , for the dynamic phase control. Because the IMON pin voltage (V<sub>IMON</sub>) represents the total current, the controller compares PS pin voltage  $(V_{PS1}$  and  $V_{PS2})$  with  $V_{IMON}$  to decide the number of operating phase. See Table 1 for the dynamic phase control mechanism.

| _ | _  |   | -   |   |

|---|----|---|-----|---|

| П | โล | h | le. | 1 |

|                     |                     | Operating phases |           |           |  |  |

|---------------------|---------------------|------------------|-----------|-----------|--|--|

| V <sub>PS1</sub>    | V <sub>PS2</sub>    | Max.             | Max.      | Max.      |  |  |

|                     |                     | phase=4          | phase=3   | phase=2   |  |  |

| < V <sub>IMON</sub> | < V <sub>IMON</sub> | 4-phase          | 3-phase   | 2-phase   |  |  |

| - VIMON             |                     | operation        | operation | operation |  |  |

| - \/                | > V <sub>IMON</sub> | 3-phase          | 2-phase   | 2-phase   |  |  |

| < V <sub>IMON</sub> |                     | operation        | operation | operation |  |  |

| > \/                | > V <sub>IMON</sub> | 2-phase          | 1-phase   | 1-phase   |  |  |

| > V <sub>IMON</sub> |                     | operation        | operation | operation |  |  |

If Max. Phase number = 3, it means phase 4 is disabled by pulling ISN4 to 5V before power up. If Max. phase number = 2, it means phase 4 and phase 3 are disabled by pulling ISN4 and ISN3 to 5V before power up.

The IMON pin voltage of RT8862 is clamped below VCC5. Users can get more design flexibility to implement auto phase control feature by higher IMON voltage. Note that the linearity of IMON can be guaranteed when  $V_{IMON}$  < 2.5V. A 1 $\mu$ F bypass capacitor connected to a clean ground is necessary at IMON pin.

Further more, the RT8862 utilizes true interleaving during auto phase shedding process. i.e. 4-phase :  $90^{\circ}$ , 3-phase :  $120^{\circ}$ , and 2-phase :  $180^{\circ}$ . By doing so, ripple uniformity is guaranteed in steady state.

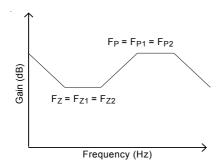

#### **Dynamic Phase Control Principles**

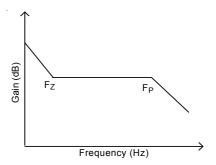

The RT8862 change to higher number of phase operation when  $V_{IMON}$  is higher than  $V_{PS1}$  or  $V_{PS2}$ . No hysteresis and extra delay exists during an up phase decision.