## I<sup>2</sup>C Interface PMIC with 6-Channel WLED Driver and 4-LDO

### **General Description**

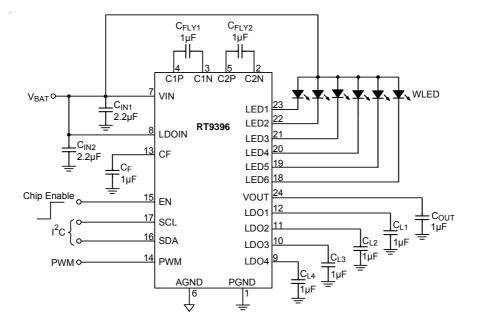

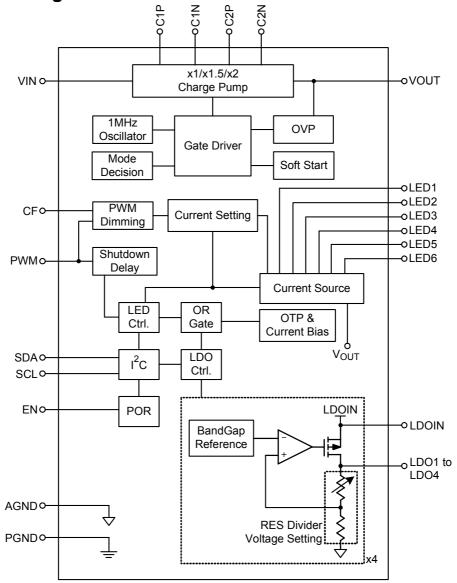

The RT9396 is a power management IC (PMIC) for backlighting and phone camera applications. The PMIC contains a 6-Channel charge pump white LED driver and four low dropout linear regulators.

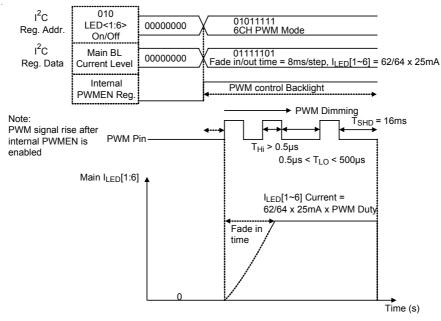

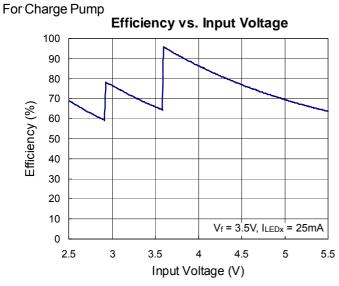

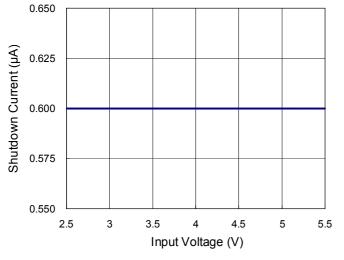

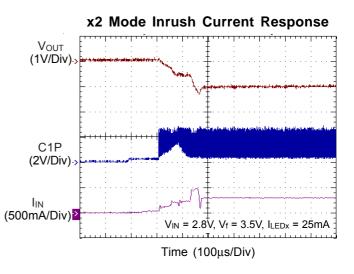

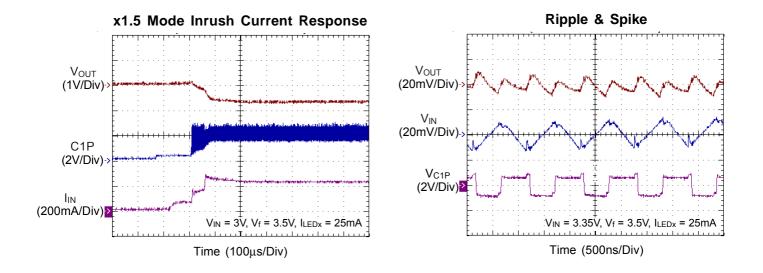

The charge pump drives up to 6 white LEDs with regulated constant current for uniform intensity. Each channel (LED1 to LED6) supports up to 25mA of current. These 6-Channels can be also programmed as 4 plus 2-Channels or 5 plus 1-Channel with different current setting for auxiliary LED application. The RT9396 maintains highest efficiency by utilizing a x1/x1.5/x2 fractional charge pump and low dropout current regulators. An internal 6-bit DAC is used for backlight brightness control. Users can easily configure up to 64 steps of LED current via the l<sup>2</sup>C interface control.

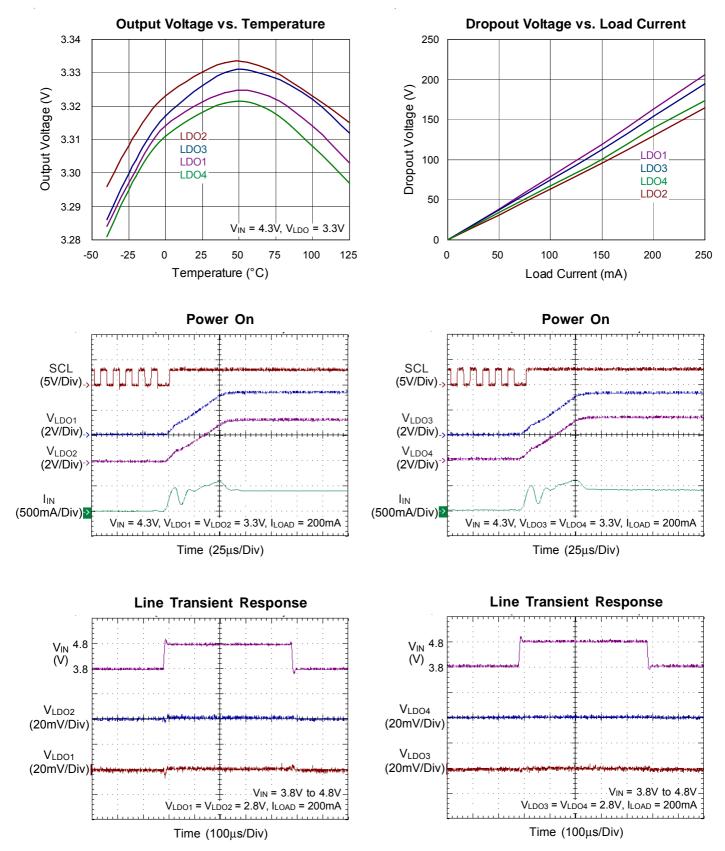

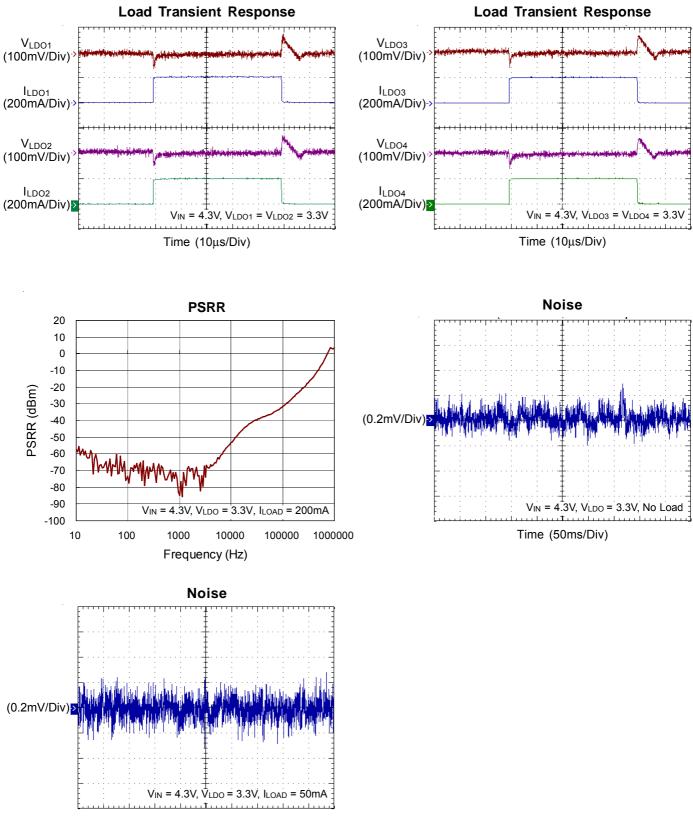

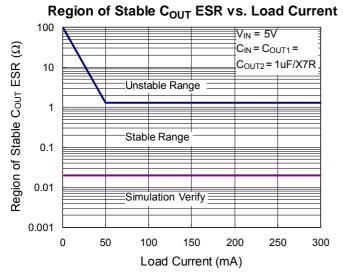

The RT9396 also comprises low noise, low dropout regulators, which provide up to 200mA of current for each of the four channels. The four LDOs deliver 3% output accuracy and low dropout voltage of 200mV @ 200mA. Users can easily configure LDO output voltage via the I<sup>2</sup>C interface control. The LDOs also provide current limiting and over temperature functions.

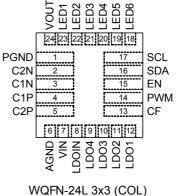

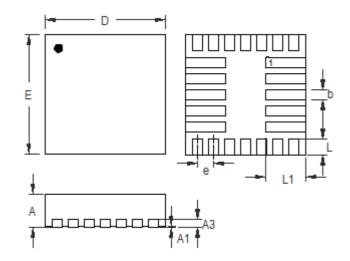

The RT9396 is available in a WQFN-24L 3x3 package.

### **Ordering Information**

RT9396

Package Type QW : WQFN-24L 3x3 (COL) (W-Type)

Lead Plating System G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

### Features

- Tri-Mode (x1/x1.5/x2) Charge Pump

- Maximum 25mA x 6-Channel LED Backlighting Output Current

- Support Main/Sub (4+2/5+1) LED Function

- 64 Steps Programmable LED Current

- Support PWM Dimming Function

- Fade In/Out Via I<sup>2</sup>C Control

- 4 Low Dropout Regulators

- Maximum 200mA x 4-Channel LDO Output Current

- 16-Level LDO Output Voltage Setting

- I<sup>2</sup>C Programmable Independent LDO Channel ON/OFF Control

- Over Temperature Protection

- Thin 24-Lead WQFN Package

- RoHS Compliant and Halogen Free

### Applications

- Cellular Phones

- PDAs and Smart Phones

### **Pin Configurations**

(TOP VIEW)

## **RT9396**

## **Marking Information**

JP=YM DNN JP= : Product Code YMDNN : Date Code

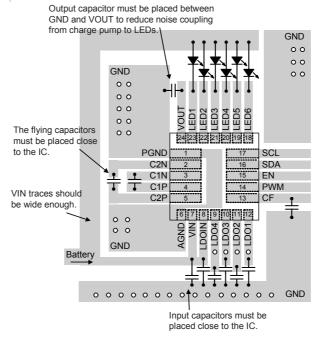

## **Typical Application Circuit**

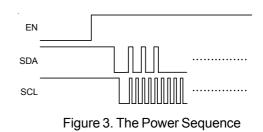

### **Timing Diagram**

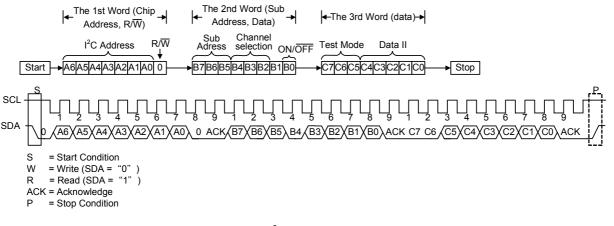

#### 16-step Voltage LDO Channel I<sup>2</sup>C Writing Cycles of LDOX ON/OFF Setting Address Selection B1 B0 Start 0 0 0 0 0 0 1 B4 В3 B2 0 0 0 СЗ C2 C1 C0 Stop 1 1 0 0 LD03+ LD02+ D04+ LD01 I<sup>2</sup>C Writing Cycles of Backlighting I (LED1~6) Fade In/Out Backlight Channel 64-step Current Setting Address ON/OFF Setting 0 0 B3 B2 B1 B0 C7 C6 C5 C4 C3 C2 C1 C0 Start 0 0 0 0 0 1 B4 Stop 1 1 1 LED5+ LED6-₹ €~ PWMEN+ LED4 LED1~3-BLON Fade In/Out Setting: 01: Every Step of Fade In/Out = 8 ms 10: Every Step of Fade In/Out = 16 ms 11: Every Step of Fade In/Out = 32 ms • I<sup>2</sup>C Writing Cycles of Backlighting II (Main: LED1~5, Sub: LED6) Fade In/Out Backlight Channel Setting Main 64-step Current Setting ON/OFF Address Main Start 1 0 1 0 1 0 0 0 0 1 1 0 B3 B2 B1 B0 C7 C6 C5 C4 C3 C2 C1 C0 Stop LED1~3**→** Main ON PWMEN+ LED5+ LED4 Main Fade In/Out Setting: 01: Every Step of Fade In/Out = 8 ms 10: Every Step of Fade In/Out = 16 ms 11: Every Step of Fade In/Out = 32 ms Backlight Channel Fade In/Out Sub Setting Sub 64-step Current Setting Address ON/OFF C7 Start 0 0 0 0 0 0 B0 Stop 1 1 1 0 1 0 0 C6C5C4 C3 C2C1C0 1 1 4 LED6 -Sub ON Sub Fade In/Out Setting: 01: Every Step of Fade In/Out = 8 ms 10: Every Step of Fade In/Out = 16 ms 11: Every Step of Fade In/Out = 32 ms • I<sup>2</sup>C Writing Cycles of Backlighting III (Main: LED1~4, Sub: LED5~6) Backlight Channel Fade In/Out Address Main ON/OFF Setting Main 64-step Current Setting C7 B1 B0 Start 0 0 0 0 0 0 0 0 B2 0 C6 C5 C4 C3 C2 C1 C0 Stop 1 4 ♠ 4 Main Fade In/Out Setting: PWMEN LED4 LED1~3 S 01: Every Step of Fade In/Out = 8 ms **Jain** 10: Every Step of Fade In/Out = 16 ms 11: Every Step of Fade In/Out = 32 ms Backlight Channel Fade In/Out Sub Sub 64-step Current Setting Address ON/OFF Setting Start 1 0 1 0 1 0 0 0 0 0 1 0 0 0 В0 C7 C6 C5 C4 C3 C2 C1 C0 Stop ED5~6-Sub Fade In/Out Setting: Sub ON 01: Every Step of Fade In/Out = 8 ms 10: Every Step of Fade In/Out = 16 ms 11: Every Step of Fade In/Out = 32 ms

Figure 2. Control Sequences of LDO Setting and LED Dimming

RT9396

## **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                              |

|---------|----------|---------------------------------------------------------------------------|

| 1       | PGND     | Charge Pump Ground.                                                       |

| 2       | C2N      | Fly Capacitor 2 Negative Connection.                                      |

| 3       | C1N      | Fly Capacitor 1 Negative Connection.                                      |

| 4       | C1P      | Fly Capacitor 1 Positive Connection.                                      |

| 5       | C2P      | Fly Capacitor 2 Positive Connection.                                      |

| 6       | AGND     | Ground for LDO1 to LDO4.                                                  |

| 7       | VIN      | Charge Pump Power Input. Connect this pin to LDOIN pin.                   |

| 8       | LDOIN    | LDO Power Input. Connect this pin to VIN pin.                             |

| 9       | LDO4     | LDO4 Output.                                                              |

| 10      | LDO3     | LDO3 Output.                                                              |

| 11      | LDO2     | LDO2 Output.                                                              |

| 12      | LDO1     | LDO1 Output.                                                              |

| 13      | CF       | PWM Filter Capacitor Connection.                                          |

| 14      | PWM      | PWM Dimming Control Input.                                                |

| 15      | EN       | Chip Enable (Active High).                                                |

| 16      | SDA      | I <sup>2</sup> C Data Input.                                              |

| 17      | SCL      | I <sup>2</sup> C Clock Input.                                             |

| 18      | LED6     | Current Sink for LED6.                                                    |

| 19      | LED5     | Current Sink for LED5.                                                    |

| 20      | LED4     | Current Sink for LED4.                                                    |

| 21      | LED3     | Current Sink for LED3.                                                    |

| 22      | LED2     | Current Sink for LED2.                                                    |

| 23      | LED1     | Current Sink for LED1.                                                    |

| 24      | VOUT     | Charge Pump Output. Connect a 1µF ceramic capacitor between VOUT and GND. |

## **Function Block Diagram**

#### Table 1. 16-Step LDO Output Voltage Setting

| C3 | C2 | C1 | C0 | LDO1 &<br>LDO2 Output<br>Voltage (V) | LDO3 & LDO4<br>Output<br>Voltage (V) | C3 | C2 | C1 | C0 | LDO1 &<br>LDO2 Output<br>Voltage (V) | LDO3 & LDO4<br>Output<br>Voltage (V) |

|----|----|----|----|--------------------------------------|--------------------------------------|----|----|----|----|--------------------------------------|--------------------------------------|

| 0  | 0  | 0  | 0  | 1                                    | 1.1                                  | 1  | 0  | 0  | 0  | 2.5                                  | 2.2                                  |

| 0  | 0  | 0  | 1  | 1.1                                  | 1.2                                  | 1  | 0  | 0  | 1  | 2.6                                  | 2.3                                  |

| 0  | 0  | 1  | 0  | 1.2                                  | 1.4                                  | 1  | 0  | 1  | 0  | 2.7                                  | 2.4                                  |

| 0  | 0  | 1  | 1  | 1.3                                  | 1.7                                  | 1  | 0  | 1  | 1  | 2.8                                  | 2.5                                  |

| 0  | 1  | 0  | 0  | 1.5                                  | 1.8                                  | 1  | 1  | 0  | 0  | 2.9                                  | 2.8                                  |

| 0  | 1  | 0  | 1  | 1.6                                  | 1.9                                  | 1  | 1  | 0  | 1  | 3                                    | 2.85                                 |

| 0  | 1  | 1  | 0  | 1.8                                  | 2                                    | 1  | 1  | 1  | 0  | 3.1                                  | 3.2                                  |

| 0  | 1  | 1  | 1  | 2.1                                  | 2.1                                  | 1  | 1  | 1  | 1  | 3.3                                  | 3.3                                  |

WLED

Current (mA)

.....

|    |    |    |    |    | Ta | able 2. 64-Step      | NLEC | Curr | ent Se | etting |   |

|----|----|----|----|----|----|----------------------|------|------|--------|--------|---|

| C5 | C4 | C3 | C2 | C1 | C0 | WLED<br>Current (mA) |      | C5   | C4     | СЗ     |   |

| 0  | 0  | 0  | 0  | 0  | 0  | 0.39                 |      | 1    | 0      | 0      |   |

| 0  | 0  | 0  | 0  | 0  | 1  | 0.78                 |      | 1    | 0      | 0      | ľ |

| 0  | 0  | 0  | 0  | 1  | 0  | 1.17                 |      | 1    | 0      | 0      | t |

| 0  | 0  | 0  | 0  | 1  | 1  | 1.56                 |      | 1    | 0      | 0      | ľ |

| 0  | 0  | 0  | 1  | 0  | 0  | 1.95                 |      | 1    | 0      | 0      | Ī |

| 0  | 0  | 0  | 1  | 0  | 1  | 2.34                 |      | 1    | 0      | 0      | Ī |

| 0  | 0  | 0  | 1  | 1  | 0  | 2.73                 |      | 1    | 0      | 0      | Ī |

| 0  | 0  | 0  | 1  | 1  | 1  | 3.13                 |      | 1    | 0      | 1      | Ī |

| 0  | 0  | 1  | 0  | 0  | 0  | 3.52                 |      | 1    | 0      | 1      | ſ |

| 0  | 0  | 1  | 0  | 0  | 1  | 3.91                 |      | 1    | 0      | 1      | Ī |

| 0  | 0  | 1  | 0  | 1  | 0  | 4.3                  |      | 1    | 0      | 1      | Ī |

| 0  | 0  | 1  | 0  | 1  | 1  | 4.69                 | İ    | 1    | 0      | 1      | ſ |

| 0  | 0  | 1  | 1  | 0  | 0  | 5.08                 |      | 1    | 0      | 1      | Ī |

| 0  | 0  | 1  | 1  | 0  | 1  | 5.47                 | İ    | 1    | 0      | 1      | Γ |

| 0  | 0  | 1  | 1  | 1  | 0  | 5.86                 |      | 1    | 0      | 1      | Ī |

| 0  | 0  | 1  | 1  | 1  | 1  | 6.25                 | İ    | 1    | 1      | 0      | Γ |

| 0  | 1  | 0  | 0  | 0  | 0  | 6.64                 |      | 1    | 1      | 0      | Ī |

| 0  | 1  | 0  | 0  | 0  | 1  | 7.03                 |      | 1    | 1      | 0      | Ī |

| 0  | 1  | 0  | 0  | 1  | 0  | 7.42                 | İ    | 1    | 1      | 0      | Ī |

| 0  | 1  | 0  | 0  | 1  | 1  | 7.81                 |      | 1    | 1      | 0      | Ī |

| 0  | 1  | 0  | 1  | 0  | 0  | 8.2                  | İ    | 1    | 1      | 0      | ſ |

| 0  | 1  | 0  | 1  | 0  | 1  | 8.59                 |      | 1    | 1      | 0      | Ī |

| 0  | 1  | 0  | 1  | 1  | 0  | 8.98                 |      | 1    | 1      | 0      | Ī |

| 0  | 1  | 0  | 1  | 1  | 1  | 9.38                 |      | 1    | 1      | 1      | Ī |

| 0  | 1  | 1  | 0  | 0  | 0  | 9.77                 |      | 1    | 1      | 1      | ľ |

| 0  | 1  | 1  | 0  | 0  | 1  | 10.16                | İ    | 1    | 1      | 1      | ſ |

| 0  | 1  | 1  | 0  | 1  | 0  | 10.55                |      | 1    | 1      | 1      | t |

| 0  | 1  | 1  | 0  | 1  | 1  | 10.94                |      | 1    | 1      | 1      | t |

| 0  | 1  | 1  | 1  | 0  | 0  | 11.33                |      | 1    | 1      | 1      | t |

| 0  | 1  | 1  | 1  | 0  | 1  | 11.72                |      | 1    | 1      | 1      | Ì |

| 0  | 1  | 1  | 1  | 1  | 0  | 12.11                |      | 1    | 1      | 1      | t |

| 0  | 1  | 1  | 1  | 1  | 1  | 12.5                 |      |      |        | -      | - |

#### Table 2. 64-Step WLED Current Setting

| 1 | 0 | 0 | 0 | 0 | 0 | 12.89 |

|---|---|---|---|---|---|-------|

| 1 | 0 | 0 | 0 | 0 | 1 | 13.28 |

| 1 | 0 | 0 | 0 | 1 | 1 | 14.06 |

| 1 | 0 | 0 | 1 | 0 | 0 | 14.45 |

| 1 | 0 | 0 | 1 | 0 | 1 | 14.84 |

| 1 | 0 | 0 | 1 | 1 | 0 | 15.23 |

| 1 | 0 | 0 | 1 | 1 | 1 | 15.63 |

| 1 | 0 | 1 | 0 | 0 | 0 | 16.02 |

| 1 | 0 | 1 | 0 | 0 | 1 | 16.41 |

| 1 | 0 | 1 | 0 | 1 | 0 | 16.8  |

| 1 | 0 | 1 | 0 | 1 | 1 | 17.19 |

| 1 | 0 | 1 | 1 | 0 | 0 | 17.58 |

| 1 | 0 | 1 | 1 | 0 | 1 | 17.97 |

| 1 | 0 | 1 | 1 | 1 | 0 | 18.36 |

| 1 | 0 | 1 | 1 | 1 | 1 | 18.75 |

| 1 | 1 | 0 | 0 | 0 | 0 | 19.14 |

| 1 | 1 | 0 | 0 | 0 | 1 | 19.53 |

| 1 | 1 | 0 | 0 | 1 | 0 | 19.92 |

| 1 | 1 | 0 | 0 | 1 | 1 | 20.31 |

| 1 | 1 | 0 | 1 | 0 | 0 | 20.7  |

| 1 | 1 | 0 | 1 | 0 | 1 | 21.09 |

| 1 | 1 | 0 | 1 | 1 | 0 | 21.48 |

| 1 | 1 | 0 | 1 | 1 | 1 | 21.88 |

| 1 | 1 | 1 | 0 | 0 | 0 | 22.27 |

| 1 | 1 | 1 | 0 | 0 | 1 | 22.66 |

| 1 | 1 | 1 | 0 | 1 | 0 | 23.05 |

| 1 | 1 | 1 | 0 | 1 | 1 | 23.44 |

| 1 | 1 | 1 | 1 | 0 | 0 | 23.83 |

| 1 | 1 | 1 | 1 | 0 | 1 | 24.22 |

| 1 | 1 | 1 | 1 | 1 | 0 | 24.61 |

| 1 | 1 | 1 | 1 | 1 | 1 | 25    |

C2

C1

**C0**

## Absolute Maximum Ratings (Note 1)

| • Supply Input Voltage, V <sub>IN</sub>        | - –0.3V to 6V    |

|------------------------------------------------|------------------|

| Output Voltage, V <sub>OUT</sub>               | 6V to 0.3V       |

| Other Pins                                     | - –0.3V to 6V    |

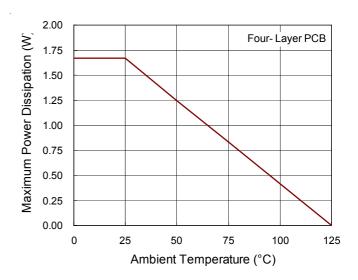

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                  |

| WQFN-24L 3x3                                   | - 1.667W         |

| Package Thermal Resistance (Note 2)            |                  |

| WQFN-24L 3x3, θ <sub>JA</sub>                  | - 60°C/W         |

| • Junction Temperature                         | - 150°C          |

| • Lead Temperature (Soldering, 10 sec.)        | - 260°C          |

| Storage Temperature Range                      | - –65°C to 150°C |

| ESD Susceptibility (Note 3)                    |                  |

| HBM (Human Body Mode)                          | - 2kV            |

| MM (Machine Mode)                              | - 200V           |

## Recommended Operating Conditions (Note 4)

| Supply Input Voltage, VIN, VLDOIN | 2.8V to 5V     |

|-----------------------------------|----------------|

| Junction Temperature Range        | –40°C to 125°C |

| Ambient Temperature Range         | –40°C to 85°C  |

### **Electrical Characteristics**

$(V_{IN} = V_{LDOIN} = 3.6V, C_{IN} = 2.2\mu F, C_{OUT} = 1\mu F, C_{FLY1} = C_{FLY2} = 1\mu F, V_F = 3.5V, I_{LEDx} = 25mA, T_A = 25^{\circ}C$ , unless otherwise specification)

| Parameter                                                            | Symbol            | Test Conditions                                           | Min | Тур  | Max  | Unit |  |  |  |

|----------------------------------------------------------------------|-------------------|-----------------------------------------------------------|-----|------|------|------|--|--|--|

| Input Power Supply                                                   |                   |                                                           |     |      |      |      |  |  |  |

| Under-Voltage Lockout Threshold                                      | Vuvlo             | V <sub>IN</sub> Rising.                                   | 1.8 | 2.1  | 2.5  | V    |  |  |  |

| Under-Voltage Lockout Hysteresis                                     | $\Delta V_{UVLO}$ |                                                           |     | 200  |      | mV   |  |  |  |

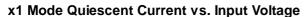

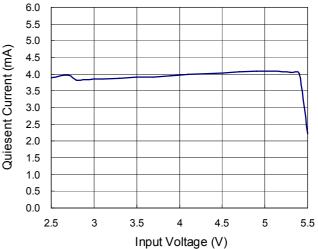

| Quiescent of x1 Mode                                                 | I <sub>Q_x1</sub> | x1 Mode, V <sub>IN</sub> = 5V, No Load,<br>LDO[1:4] OFF   |     | 1    | 2    | mA   |  |  |  |

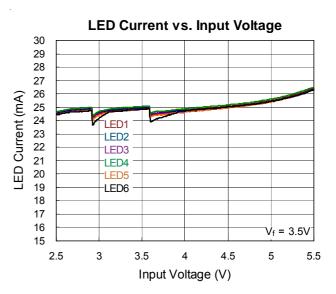

| Quiescent of x2 Mode                                                 | I <sub>Q_x2</sub> | x2 Mode, V <sub>IN</sub> = 3.5V, No Load,<br>LDO[1:4] OFF |     | 3.5  | 5    | mA   |  |  |  |

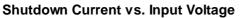

| Shutdown Current                                                     | I <sub>SHDN</sub> | V <sub>IN</sub> = 5V, V <sub>EN</sub> = 0V                |     | 0.5  | 1    | μA   |  |  |  |

| Charge Pump WLED Driver                                              | -                 |                                                           |     |      |      |      |  |  |  |

| Backlight I <sub>LEDx</sub> Accuracy                                 |                   |                                                           | -5  | 0    | 5    | %    |  |  |  |

| Backlight Current Matching                                           |                   |                                                           | -3  | 0    | 3    | %    |  |  |  |

| Dropout Voltage                                                      |                   |                                                           |     | 70   |      | mV   |  |  |  |

| Charge Pump                                                          | •                 |                                                           |     |      | •    |      |  |  |  |

| Oscillator Frequency                                                 |                   |                                                           |     | 1000 |      | kHz  |  |  |  |

| x1 Mode to x1.5 Mode<br>Transition Voltage (V <sub>IN</sub> falling) |                   | V <sub>f</sub> = 3.5V, I <sub>OUT</sub> = 150mA           |     | 3.6  | 3.75 | V    |  |  |  |

| Mode Transition Hysteresis                                           |                   | V <sub>f</sub> = 3.5V, I <sub>OUT</sub> = 150mA           |     | 250  |      | mV   |  |  |  |

| Over Voltage Protection                                              |                   | V <sub>IN</sub> = 4.5V                                    | 5.2 | 5.5  | 5.8  | V    |  |  |  |

## RT9396

| RICHTEK |

|---------|

|---------|

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Paramete                                       | er         | Symbol              | Test Conditions                       | Min  | Тур | Max | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------|---------------------|---------------------------------------|------|-----|-----|------|

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LDO1 to LDO4                                   |            | •                   | •                                     |      | •   |     |      |

| Dutput voltage Range  By I <sup>2</sup> C Setting  1.1   3.3  V    VOUT Accuracy $I_{OUT} = 1mA$ 3  3  %    Line Regulation $V_{IN} = (V_{OUT} + 0.3V)$ to 5V or<br>$V_{IN} > 2.5V$ , whichever is larger    0.2  %/V    Load Regulation $1mA < I_{OUT} < 200mA$ 0.6  %    Current Limit  ILIM  RLOAD = 1Ω  230  350  600  mA    Quiescent Current  I.Q  4-Channel All Turn On   140  200  µA    Shutdown Current  I.ShDN    160   °C    Z interface  SN, SDA,SCL Pull Low Current  I.SD   20   °C    SDA Output Low Voltage  VCL    0.4  V    SDA SCL Pull Low Current  I.EN    0.4  V    SDA Output Low Voltage  VCL    0.4  V    SCL Clock Kigh Period  thign  0.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Input Voltage                                  |            |                     | V <sub>IN</sub> = 2.8V to 5V          | 2.8  |     | 5   | V    |

| VOUT AccuracyIouT = 1mA-33%Line Regulation $V_{IN} = (V_{OUT} + 0.3V)$ to 5V or<br>$V_{IN} > 2.5V$ , whichever is larger0.2%/VLoad Regulation $1mA < I_{OUT} < 200mA$ 0.6%Current LimitILIM $R_{LOAD} = 1\Omega$ 230350600mAQuiescent CurrentI.g.4-Channel All Turn On140200 $\mu A$ Shutdown CurrentI.g. $T_{SD}$ 160°CThemal ShutdownTSD160°CThemal Shutdown Hysteresis $\Lambda T_{SD}$ 20°CThemal Shutdown Hysteresis $\Lambda T_{SD}$ 20°C <b>2</b> Cinterface100 $\mu A$ 0.4VEN, SDA, SCLLogic-HighVIH1.4VThreshold VoltageVCL0.4VSDA Output Low VoltageVCL400KHzSCL Clock FrequencyfscL $\mu S$ SOL Ock High PeriodtHgh0.6 $\mu S$ SDA Data Setup Timetsu_DAT0.6 $\mu S$ SDA Data HOLD Timeth_D_DAT0.6 $\mu S$ SDA Data Setup Time for STOP Conditiontsu_STO0.6 $\mu S$ SDA Data HOLD Timeth_D_DAT0.050.9 $\mu S$ Start                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Dropout Voltage                                |            |                     | $V_{IN} \ge 2.8V$ , $I_{OUT}$ = 200mA |      |     | 200 | mV   |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Output voltage Range                           |            |                     | By I <sup>2</sup> C Setting           | 1.1  |     | 3.3 | V    |

| $\begin{tabular}{ c                                   $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VOUT Accuracy                                  |            |                     | I <sub>OUT</sub> = 1mA                | -3   |     | 3   | %    |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Line Regulation                                |            |                     |                                       |      |     | 0.2 | %/V  |

| Quiescent CurrentIQ<br>IQ<br>A4-Channel All Turn On140200<br>µAShutdown CurrentI<br>SHDNT<br>SD1µAThemal Shutdown Hysteresis $\Delta T_{SD}$ 160°CThemal Shutdown Hysteresis $\Delta T_{SD}$ 100°C <b>2°C interface</b> 20°C°C <b>2°C interface</b> 510µAEN, SDA, SCLLogic-HighVIH1.4VIbreshold VoltageVolt0.4VSDA Output Low VoltageVCL0.4VSCL Clock FrequencyfScL400kHzSCL Clock Low Periodthigh0.6µsHold Time START Conditionthigh0.6µsSDA Data Setup Timetsu_DAT0.050.9µsSetup Time for STOP Conditiontsu_STO0.6µsSoDA Data HOLD Timetbugtsu_STO0.6µsSetup Time for STOP Conditiontsu_STO0.6µsSup Stree Time Between STOP and<br>Start Conditiontsu_STO0.6µsPWM Dimming ControlV0.5µsPWM Dimming Low Timeµs0.5µsPWM Dimming Low Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Load Regulation                                |            |                     | 1mA < I <sub>OUT</sub> < 200mA        |      |     | 0.6 | %    |

| Shutdown CurrentIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII <td>Current Limit</td> <td></td> <td>I<sub>LIM</sub></td> <td></td> <td>230</td> <td>350</td> <td>600</td> <td>mA</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Current Limit                                  |            | I <sub>LIM</sub>    |                                       | 230  | 350 | 600 | mA   |

| Thermal ShutdownT SD160 $^{\circ}$ CThermal Shutdown Hysteresis $\Delta T_{SD}$ 20 $^{\circ}$ C $^{2}$ C interfaceEN, SDA, SCL Pull Low CurrentIEN510 $\mu$ AEN, SDA, SCLLogic-HighVIH1.4VThreshold VoltageVCL0.4VSDA Output Low VoltageVCL0.4VSCL Clock FrequencyfSCL400kHzSCL Clock Low PeriodtLow1.3 $\mu$ sSCL Clock High PeriodtHigh0.6 $\mu$ sHold Time START ConditiontHg_STR0.6 $\mu$ sSDA Data Setup TimetSU_DAT100 $\mu$ sSDA Data HOLD TimetHD_DAT0.050.9 $\mu$ sStart ConditiontSU_STO0.6 $\mu$ sSDA Data HOLD TimetBUF1.3 $\mu$ sStart ConditiontBUFtBUF1.3 $\mu$ sPWM Dimming ControltBUF0.5500 $\mu$ sPWM Dimming Low Time0.5500 $\mu$ s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Quiescent Current                              |            | l <sub>Q</sub>      | 4-Channel All Turn On                 |      | 140 | 200 | μA   |

| Thermal Shutdown Hysteresis $\Delta T_{SD}$ 20°C $^{2}C$ interfaceEN, SDA,SCL Pull Low CurrentIEN510 $\mu$ AEN, SDA, SCLLogic-HighVIH1.4VThreshold VoltageVcL0.4VSDA Output Low VoltageVcL0.4VSCL Clock FrequencyfScL400kHzSCL Clock Low PeriodtLow1.3 $\mu$ sSCL Clock High PeriodtHigh0.6 $\mu$ sHold Time START ConditiontHg_STR0.6 $\mu$ sSDA Data Setup TimetSu_DAT0.050.9 $\mu$ sSetup Time for STOP ConditiontSu_STO0.6 $\mu$ sBus Free Time Between STOP and<br>START ConditiontBUF1.3 $\mu$ sPWM Dimming Frequency1200kHzPWM Dimming Frequency1200kHzPWM Dimming Low Time0.5 $\mu$ s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Shutdown Current                               |            | I <sub>SHDN</sub>   |                                       |      |     | 1   | •    |

| $^{2}$ C interfaceImage: second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second s | Thermal Shutdown                               |            | T <sub>SD</sub>     |                                       |      | 160 |     | -    |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Thermal Shutdown Hy                            | steresis   | $\Delta T_{SD}$     |                                       |      | 20  |     | °C   |

| EN, SDA, SCL<br>Threshold VoltageLogic-High<br>Logic-Low $V_{IH}$ 1.4VSDA Output Low VoltageVCL0.4VSCL Clock FrequencyfsCL0.4VSCL Clock Low PeriodtLow1.3400SCL Clock High PeriodtHigh0.6 $\mu$ sSCL Clock High PeriodtHugh0.6 $\mu$ sScl Clock High PeriodtHugh0.6 $\mu$ sScl Data Start ConditiontHo_STR0.6 $\mu$ sSDA Data Setup Timetsu_DAT100nsSDA Data HOLD TimetHo_DAT0.050.9 $\mu$ sSetup Time for STOP Conditiontsu_STO0.6 $\mu$ sBus Free Time Between STOP and<br>START ConditiontBuF1.3 $\mu$ sPWM Dimming Control $\mu$ s $\mu$ sPWM Dimming Frequency1200kHzPWM Dimming Low Time0.5 $\mu$ s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I <sup>2</sup> C interface                     |            |                     |                                       |      |     |     |      |

| InterpretationInterpretationInterpretationInterpretationThreshold VoltageLogic-LowVIL0.4VSDA Output Low VoltageVCL0.4VSCL Clock Frequency $f_{SCL}$ 400kHzSCL Clock Low Periodthigh0.6 $\mu$ sSCL Clock High Periodthigh0.6 $\mu$ sSCL Clock High Periodthigh0.6 $\mu$ sHold Time START Conditionthigh0.6 $\mu$ sSetup Time for Repeat STARTtsu_STR0.6 $\mu$ sSDA Data Setup Timetsu_DAT0.050.9 $\mu$ sSetup Time for STOP Conditiontsu_STO0.6 $\mu$ sSetup Time for STOP Conditiontsu_STO0.6 $\mu$ sSus Free Time Between STOP and START Conditiontsu_STO0.6 $\mu$ sPWM Dimming ControltsuF1.3 $\mu$ sPWM Dimming High Time0.50.5 $\mu$ sPWM Dimming Low Time0.5500 $\mu$ s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | EN, SDA,SCL Pull Lov                           | v Current  | I <sub>EN</sub>     |                                       |      | 5   | 10  | μA   |

| SDA Output Low Voltage  V <sub>CL</sub> 0.4  V    SCL Clock Frequency  f <sub>SCL</sub> 400  kHz    SCL Clock Low Period  t <sub>Low</sub> 1.3    μs    SCL Clock High Period  tHigh  0.6    μs    SCL Clock High Period  tHigh  0.6    μs    Hold Time START Condition  tHD_STR  0.6    μs    Setup Time for Repeat START  tSU_STR  0.6    μs    SDA Data Setup Time  tSU_DAT  100    ns    SDA Data HOLD Time  tHD_DAT  0.05   μs    Setup Time for STOP Condition  tSU_STO  0.6   μs    Setup Time for STOP Condition  tSU_STO  0.6   μs    Bus Free Time Between STOP and<br>START Condition  tBuF  1.3   μs    PWM Dimming Frequency  0.5 <td< td=""><td>EN, SDA, SCL</td><td>Logic-High</td><td></td><td></td><td>1.4</td><td></td><td></td><td>V</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EN, SDA, SCL                                   | Logic-High |                     |                                       | 1.4  |     |     | V    |

| SCL Clock Frequency $f_{SCL}$ 400kHzSCL Clock Low Period $t_{Low}$ 1.3 $\mu$ sSCL Clock High Period $t_{High}$ 0.6 $\mu$ sSCL Clock High Period $t_{High}$ 0.6 $\mu$ sHold Time START Condition $t_{HD_STR}$ 0.6 $\mu$ sSetup Time for Repeat START $t_{SU_STR}$ 0.6 $\mu$ sSDA Data Setup Time $t_{SU_DAT}$ 100 $n$ sSDA Data HOLD Time $t_{HD_DAT}$ 0.050.9 $\mu$ sSetup Time for STOP Condition $t_{SU_STO}$ 0.6 $\mu$ sBus Free Time Between STOP and START Condition $t_{BUF}$ 1.3 $\mu$ sPWM Dimming Frequency1200kHzPWM Dimming High Time0.5 $\mu$ sPWM Dimming Low Time0.5500 $\mu$ s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Threshold Voltage                              | Logic-Low  | VIL                 |                                       |      |     | 0.4 | V    |

| SCL Clock Low Period  tLow  1.3    μs    SCL Clock High Period  tHigh  0.6    μs    SCL Clock High Period  tHigh  0.6    μs    Hold Time START Condition  tHD_STR  0.6    μs    Setup Time for Repeat START  tSU_STR  0.6    μs    SDA Data Setup Time  tSU_DAT  100    ns    SDA Data Setup Time  tHD_DAT  0.05   0.9  μs    Setup Time for STOP Condition  tSU_STO  0.6    μs    Setup Time for STOP Condition  tSU_STO  0.6    μs    Bus Free Time Between STOP and START Condition  tBUF  1.3    μs    PWM Dimming Control  tBUF  0.5    μs    PWM Dimming High Time  0.5    μs    PWM Dimming Low Time  0.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SDA Output Low Volta                           | ge         | V <sub>CL</sub>     |                                       |      |     | 0.4 | V    |

| SCL Clock High Period  tHigh  0.6   μs    Hold Time START Condition  tHD_STR  0.6   μs    Setup Time for Repeat START  tsu_STR  0.6   μs    SDA Data Setup Time  tsu_DAT  0.05   μs    SDA Data Setup Time  tHD_DAT  0.05   ns    SDA Data HOLD Time  tHD_DAT  0.05   μs    Setup Time for STOP Condition  tsu_STO  0.6   μs    Bus Free Time Between STOP and START Condition  tBUF  1.3   μs    PWM Dimming Control  tBUF  1.3   μs    PWM Dimming Frequency  1   μs    PWM Dimming High Time  0.5   μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SCL Clock Frequency                            |            | f <sub>SCL</sub>    |                                       |      |     | 400 | kHz  |

| Hold Time START Condition $t_{HD_STR}$ 0.6 $\mu_S$ Setup Time for Repeat START $t_{SU_STR}$ 0.6 $\mu_S$ SDA Data Setup Time $t_{SU_DAT}$ 100 $$ $\mu_S$ SDA Data HOLD Time $t_{HD_DAT}$ 0.050.9 $\mu_S$ Setup Time for STOP Condition $t_{SU_STO}$ 0.6 $$ $\mu_S$ Bus Free Time Between STOP and<br>START Condition $t_{BUF}$ 1.3 $$ $$ $\mu_S$ PWM Dimming ControlPWM Dimming Frequency1 $$ $200$ kHzPWM Dimming Low Time0.5 $$ $$ $\mu_S$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SCL Clock Low Period                           |            | t <sub>Low</sub>    |                                       | 1.3  |     |     | μS   |

| Setup Time for Repeat STARTtsu_STR0.6 $\mu$ sSDA Data Setup Timetsu_DAT100nsSDA Data HOLD TimetHD_DAT0.050.9 $\mu$ sSetup Time for STOP Conditiontsu_STO0.6 $\mu$ sBus Free Time Between STOP and<br>START ConditiontBUF1.3 $\mu$ sPWM Dimming ControlPWM Dimming Frequency1200kHzPWM Dimming High Time0.5 $\mu$ sPWM Dimming Low Time1500 $\mu$ s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SCL Clock High Period                          | b          | t <sub>High</sub>   |                                       | 0.6  |     |     | μS   |

| SDA Data Setup Time $t_{SU_DAT}$ 100nsSDA Data HOLD Time $t_{HD_DAT}$ 0.050.9 $\mu s$ Setup Time for STOP Condition $t_{SU_STO}$ 0.6 $\mu s$ Bus Free Time Between STOP and<br>START Condition $t_{BUF}$ 1.3 $\mu s$ PWM Dimming ControlPWM Dimming Frequency1200kHzPWM Dimming High Time0.5 $\mu s$ PWM Dimming Low Time0.5 $500$ $\mu s$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Hold Time START Cor                            | ndition    | thd_str             |                                       | 0.6  |     |     | μS   |

| SDA Data HOLD TimetHD_DAT0.050.9μsSetup Time for STOP Conditiont <sub>SU_STO</sub> 0.6μsBus Free Time Between STOP and<br>START Conditiont <sub>BUF</sub> 1.3μsPWM Dimming Controlrequency1200kHzPWM Dimming Frequency0.5μsPWM Dimming Low Time0.5μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Setup Time for Repea                           | t START    | t <sub>SU_STR</sub> |                                       | 0.6  |     |     | μS   |

| Setup Time for STOP Conditiont_SU_STO0.6μBus Free Time Between STOP and<br>START Conditiont_BUF1.3μsPWM Dimming ControlPWM Dimming Frequency1200kHzPWM Dimming High Time0.5μsPWM Dimming Low Time0.5μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SDA Data Setup Time                            |            | t <sub>SU_DAT</sub> |                                       | 100  |     |     | ns   |

| Bus Free Time Between STOP and<br>START Conditiont_BUF1.3μsPWM Dimming ControlPWM Dimming Frequency1200kHzPWM Dimming High Time0.5μsPWM Dimming Low Time0.5500μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SDA Data HOLD Time                             | 9          | thd_dat             |                                       | 0.05 |     | 0.9 | μS   |

| START Conditiont_BUF1.3μsPWM Dimming ControlPWM Dimming Frequency1200kHzPWM Dimming High Time0.5μsPWM Dimming Low Time0.5500μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Setup Time for STOP                            | Condition  | t <sub>SU_STO</sub> |                                       | 0.6  |     |     | μS   |