## SHA-256 Battery Authenticator with 34 Bytes User Memory

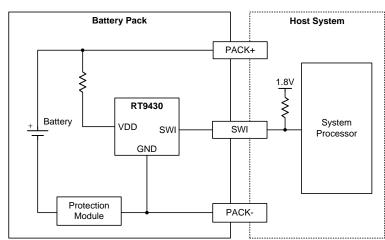

### **General Description**

The RT9430 battery authenticator uses challenge and response authentication based on SHA-256 (FIPS 180-3) hash algorithm to ensure that the battery pack is certified by the original manufacturer.

The device supports 34 bytes of programmable nonvolatile memory for users to access battery information, 4 bytes Device\_ID for chip supplier information and system user information, and 8 bytes unique ROM ID for chip identification code. The RT9430 communicates over the single-wire Interface.

### **Ordering Information**

## RT9430 - O O O Pin 1 Orientation\*\*\* (2) : Quadrant 2, Follow EIA-481-D Key Version Code

———Package Type WTC : TWL-CSP-6B 1.46x1.16 (BSC)

### Features

- SHA-256 FIPS 180-3 Symmetric-Key-Based Secure Authentication Model

- 34 Bytes of User NVM

- 32 Bytes of Secret

- 8 Bytes of ROM\_ID

- 4 Bytes of Device\_ID

- Support NVM Write and Read Protect

- Supports Anonymous Authentication Mode

- Single-Wire Interface Bit Rate 50kbps, Supports Normal Mode and Fast Mode

- TWL-CSP 1.46x1.16mm Package

### **Applications**

- Smartphones

- Portable Applications

Note :

\*\*\*Empty means Pin1 orientation is Quadrant 1

Richtek products are :

- ► RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

## **Simplified Application Circuit**

## **Marking Information**

7T : Product Code W : Date Code

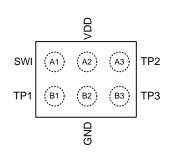

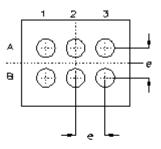

### **Pin Configuration**

TWL-CSP-6B 1.46x1.16 (BSC)

| Pin No. | Pin Name | Pin Function              |

|---------|----------|---------------------------|

| A1      | SWI      | Single-wire interface.    |

| A2      | VDD      | Power supply input.       |

| A3      | TP2      | Test pin, connect to GND. |

| B1      | TP1      | Test pin, connect to SWI. |

| B2      | GND      | Device ground.            |

| B3      | TP3      | Test pin, connect to GND. |

### **Functional Pin Description**

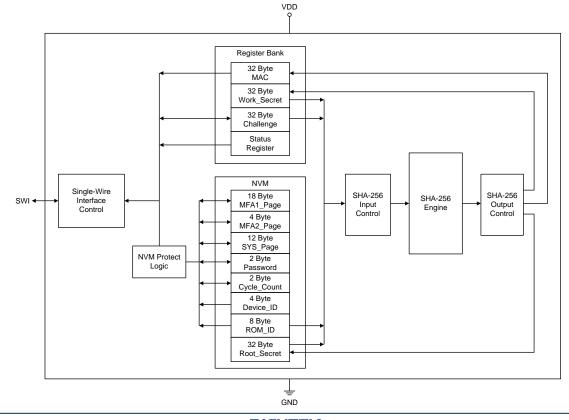

### **Functional Block Diagram**

RICHTEK Copyright © 2020 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation. www.richtek.com DS9430-00

## **RT9430**

| Absolute Maximum Ratings (Note 1)              |                |

|------------------------------------------------|----------------|

| Voltage on VDD Pin Relative to GND             | -0.3V to 5.5V  |

| Voltage on SWI Pin Relative to GND             | -0.3V to 5.5V  |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                |

| TWL-CSP-6B 1.46x1.16 (BSC) 2                   | 2.13W          |

| Package Thermal Resistance (Note 2)            |                |

| TWL-CSP-6B 1.46x1.16 (BSC), θ <sub>JA</sub> 4  | ₩6.9°C/W       |

| Lead Temperature (Soldering, 10 sec.)2         | 260°C          |

| Junction Temperature 1                         | 50°C           |

| Storage Temperature Range                      | -65°C to 150°C |

| ESD Susceptibility (Note 3)                    |                |

| HBM (Human Body Model) 8                       | 3kV            |

#### **Recommended Operating Conditions** (Note 4)

| Supply Voltage, VDD        | 2.8V to 5.0V   |

|----------------------------|----------------|

| Ambient Temperature Range  | –40°C to 85°C  |

| Junction Temperature Range | –40°C to 150°C |

### **Electrical Characteristics**

(2.8V  $\leq$  V\_{DD}  $\leq$  5.0V,  $T_{A}$  = 25°C, unless otherwise specified)

| Parameter                     | Symbol            | Test Conditions       | Min | Тур | Max | Unit   |

|-------------------------------|-------------------|-----------------------|-----|-----|-----|--------|

| Power                         |                   |                       |     |     |     |        |

| Idle Current                  | IDLE              | SWI Idle              |     | 2   | 5   | μA     |

| 10                            |                   |                       |     |     |     |        |

| SWI Input High                | VIH               |                       | 1.1 |     |     | V      |

| SWI Input Low                 | VIL               |                       |     |     | 0.4 | V      |

| SWI Output Low                | VOL               | I <sub>OL</sub> = 5mA |     |     | 0.4 | V      |

| NVM                           |                   | •                     |     |     |     |        |

| Programming Current           | I <sub>PROG</sub> |                       |     | 100 | 400 | μΑ     |

| Programming Time              | tPROG             | 4 byte                |     | 7.5 | 15  | ms     |

| Write/Erase Cycling Endurance | Ncy               | -40°C to 150°C        | 10k |     |     | Cycles |

| Data Retention                | tDR               |                       | 10  |     |     | Years  |

| SHA-256 Engine                |                   | •                     | ·   |     |     |        |

| Computation Current           | I <sub>SHA</sub>  |                       |     | 1   |     | mA     |

| Computation Time              | <b>t</b> SHA      |                       |     | 100 |     | μS     |

## **Electrical Characteristics : Single-Wire Interface**

(2.8V  $\leq$  V\_{DD}  $\leq$  5.0V, T\_A = 25°C, unless otherwise specified)

| Parameter                 | Symbol               | Test Conditions    | Min  | Тур | Max | Unit |

|---------------------------|----------------------|--------------------|------|-----|-----|------|

| Fast Mode Timing          |                      |                    |      |     | •   |      |

| Break Time                | t <sub>B</sub>       |                    | 38   |     | 46  | μS   |

| Break Recovery Time       | tBREC                |                    | 15   |     | 20  | μS   |

| Host Write 1              | t <sub>HW1</sub>     |                    | 2    |     | 12  | μS   |

| Host Write 0              | tHWO                 |                    | 16   |     | 26  | μS   |

| Host Write Recovery Time  | tHREC                |                    | 2    |     |     | μS   |

| Host Send Start Time      | <b>t</b> HSTA        |                    | 2    |     | 6   | μS   |

| Host Sample Time          | <b>t</b> HSAM        |                    | 14   |     | 20  | μS   |

| Device Write 1 Cycle Time | tDW1_CYC             |                    | 14   |     |     | μS   |

| Device Write 0 Cycle Time | tDW0_CYC             |                    | 28   |     |     | μS   |

| Device Write 1            | t <sub>DW1</sub>     |                    | 8    |     | 12  | μS   |

| Device Write 0            | tDW0                 |                    | 22   |     | 26  | μS   |

| SWI Line Rising Time      | trise                |                    |      |     | 100 | ns   |

| SWI Line Falling Time     | t <sub>FALL</sub>    |                    |      |     | 100 | ns   |

| Normal Mode Timing        |                      |                    |      |     |     |      |

| Break Time                | tB                   |                    | 110  |     | 130 | μS   |

| Break Recovery Time       | tBREC                |                    | 60   |     | 70  | μS   |

| Host Write 1              | tHW 1                |                    | 40   |     | 60  | μS   |

| Host Write 0              | tHWO                 |                    | 70   |     | 90  | μS   |

| Host Write Recovery Time  | tHREC                |                    | 40   |     |     | μS   |

| Host Send Start Time      | <b>t</b> HSTA        |                    | 6    |     | 46  | μS   |

| Host Sample Time          | <b>t</b> HSAM        |                    | 62   |     | 78  | μS   |

| Device Write 1 Cycle Time | t <sub>DW1_CYC</sub> |                    | 62   |     |     | μS   |

| Device Write 0 Cycle Time | tDW0_CYC             |                    | 92   |     |     | μS   |

| Device Write 1            | t <sub>DW1</sub>     |                    | 50   |     | 60  | μS   |

| Device Write 0            | tDW0                 |                    | 80   | -   | 90  | μS   |

| SWI Line Rising Time      | trise                |                    |      |     | 250 | ns   |

| SWI Line Falling Time     | tFALL                |                    |      |     | 250 | ns   |

| Chip Reset Low Time       | <b>t</b> CRSTL       | Chip reset         | 1000 |     |     | μs   |

| SWI Reset Low Time        | t <sub>RSTL</sub>    | SWI protocol reset | 250  |     |     | μS   |

| SWI Reset High Time       | trsth                | SWI protocol reset | 128  |     |     | ms   |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- **Note 2.**  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effective-thermalconductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

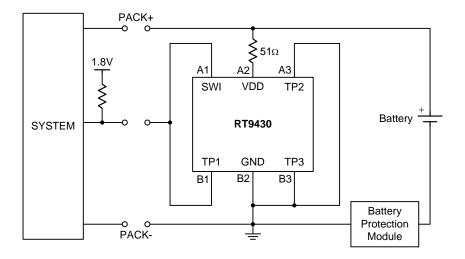

## **Typical Application Circuit**

### **Application Information**

#### SHA-256 Authentication

The RT9430 supports SHA-256 authentication with 256 bytes Root Secret to ensure host system uses the certificated battery pack. In order to prevent Root\_Secret being revealed, the RT9430 performed a unique authentication that Root\_Secret will only exist in the RT9430.

180-3 Authentication is using SHA-256 FIPS Symmetric-Key-Based secure authentication model. The 64 bytes message block consists of a 32 bytes Root Secret, a 32 bytes challenge and optional 8 bytes unique ROM ID to replace challenge block. RT9430 returns a 32 bytes MAC after SHA-256 authentication. If this MAC matches an identical one generated by a host system, the authentication process is successful. Contact Richtek for detail description.

#### Memory

The RT9430 battery authenticator supports 34 bytes non-volatile memory for storing user programmable data MFA\_Page1, MFA\_Page2, SYS\_Page.

Each memory space has different access modes and also supports permanently lock function.

Contact Richtek for detail description.

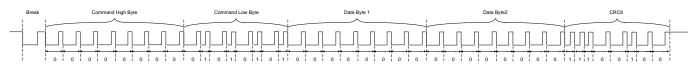

#### **Single-Wire Interface Commands**

The RT9430 uses the corresponding commands to perform authentication and access NVM through the Single-Wire Interface protocol. All command lengths are fixed to 2 bytes, and the length of data to be written or read according to the command. The command must be attached by a 1 byte CRC for transmission error detection. The CRC is calculated by passing the command and data through the CRC8,  $X^8 + X^2 + X + 1$ equation.

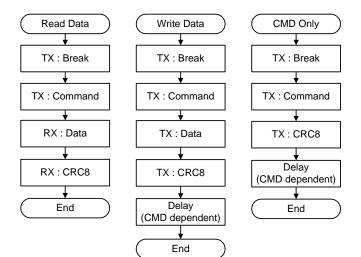

The RT9430 commands divides into Read, Write and CMD only, depends on command attribute. Figure 1 shows the host system command flow, all communication sequence follow this flow.

Figure 1. Host System Command Flow

#### Cycle Count

Cycle count maintains a total count of the battery charge cycles stored in nonvolatile memory.

Host system can increase cycle count by sending a CYCLE COUNT command to the RT9430.

#### **Device ID**

Device\_ID include 4 bytes data for chip supplier and system user information. Device\_ID is read only data and can be read in every access mode.

#### ROM ID

8 bytes unique ROM ID for chip identification code. ROM\_ID is read only data and can be read in every access mode

#### Single-Wire Interface

The RT9430 battery authenticator adopts the SWI (Single-Wire Interface) to perform bidirectional data commination to host system. The MSB of the data is transmitted first, and the data is Big-Endian order. The SWI pin is open-drain and requires an external pull-up resistor.

The command length of the SWI protocol is fixed to 2 bytes. The length of the data to be written or read according to different commands. Finally, a 1 byte CRC code must be attached. The CRC Code is calculated using the equations of CRC8 ( $X^8 + X^2 + X + 1$ ).

2020

#### Break

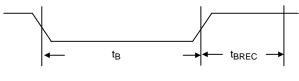

The host initiates communication by the Break command. Immediately after the completion of the Break command, the MSB of the command is transmitted. When the RT9430 receives the Break command in the idle state, the chip begins to receive the command transmitted from the host. Please note that the Break command is required to initialize the SWI before all communications begin. In addition, through the pulse width of different Break, it can be determined SWI communication speed is Normal mode or Fast Mode. If the Break does not meet the pulse width specification, the chip will ignore the following received command.

Receiving Break during communication will reset the current SWI communication and proceed to the next command.

Figure 2. Break

#### **Host Write Bit**

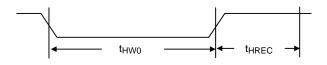

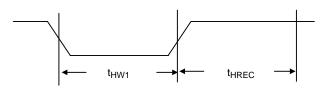

Figure 3 and Figure 4 illustrates the waveform of host write bit .The host needs to meet the timing specifications to ensure the correctness of data transmission.

Figure 3. Host Write 1

Figure 4. Host Write 0

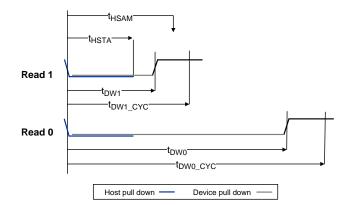

#### **Host Read Bit**

When the host sends a read command, after the 2 bytes command is transmitted, the host needs to continue to read the RT9430 returns data. Each bit is triggered by the host to ensure data integrity.

The receive bit begins after the host pulls the SWI level low, and the host releases SWI after  $t_{HSTA}$ . When RT9430 detects the falling edge, it starts to pull down the SWI level at the same time, and releases the SWI according to the transfer bit at the corresponding time ( $t_{DW1}$ ,  $t_{DW0}$ ). The host must read the SWI level at  $t_{HSAM}$ after pulling down the SWI level, SWI high level for read bit 1 and the low level for bit 0.

When the host receives bit 1, it needs to delay  $t_{DW1_CYC}$  then process the next bit; when the host receives bit 0, it needs to delay  $t_{DW0_CYC}$  then process the next bit.

Figure 5. Host Read Bit

#### SWI Reset

If the SWI is held high for longer than  $t_{RSTH}$ ; or if the low time is exceeded for  $t_{RSTL}$ , the SWI state machine will perform a reset. If the host does not receive the expected response from the chip, or if the host needs to reset the SWI during communication, the host can use SWI to held low time for more than  $t_{RSTL}$  to reset the SWI.

Figure 6. SWI Bit Steam

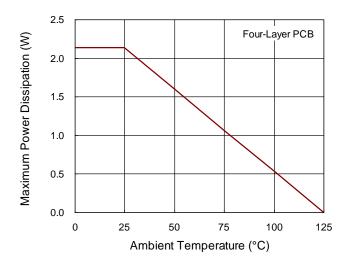

#### **Thermal Considerations**

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula :

$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{J}\mathsf{A}}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-toambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a TWL-CSP-6B 1.46x1.16 (BSC) package, the thermal resistance,  $\theta_{JA}$ , is 46.9°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A = 25^{\circ}$ C can be calculated as below :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (46.9^{\circ}C/W) = 2.13W$  for a TWL-CSP-6B 1.46x1.16 (BSC) package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 7 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 7. Derating Curve of Maximum Power Dissipation

#### **Command Summary Table**

| Name           | Symbol           | Command | Data   | Access<br>Mode |     | Description                                                             |

|----------------|------------------|---------|--------|----------------|-----|-------------------------------------------------------------------------|

|                |                  |         | Length | USER           | SYS |                                                                         |

|                | READ_STATUS      | 0x0055  | 2      | R              | R   | Status register                                                         |

| Status         | READ_CMD_CRC     | 0x0051  | 1      | R              | R   | Read latest received command CRC                                        |

|                | AUTH_WO_ROM_ID   | 0x8150  | 0      | W              | W   | Computes SHA-256 without<br>unique ROM_ID to replace<br>challenge block |

|                | AUTH_WI_ROM_ID   | 0x8151  | 0      | W              | W   | Computes SHA-256 with unique<br>ROM_ID to replace challenge<br>block    |

| Authentication | GEN_WORK_SECRET  | 0x8105  | 0      | W              | W   | Generates new work secret                                               |

|                | WRITE_CHALLENGE  | 0x8115  | 32     | W              | W   | Write challenge                                                         |

|                | READ_CHALLENGE   | 0x0115  | 32     | R              | R   | Read challenge                                                          |

|                | READ_MAC         | 0x0125  | 32     | R              | R   | Read MAC                                                                |

|                | READ_ROM_ID      | 0x0135  | 8      | R              | R   | Read unique ROM_ID                                                      |

|                | ANONYMOUS_AUTH   | 0x8215  | 0      | W              | W   | Anonymous authentication                                                |

| Secret         | LOCK_ROOT_SECRET | 0x8235  | 0      | W              | W   | Permanently lock root secret                                            |

| Manage         | LOCK_MFA1        | 0x8245  | 0      | W              | W   | Permanently lock MFA1 page                                              |

|                | LOCK_MFA2        | 0x8255  | 0      | W              | W   | Permanently lock MFA2 page                                              |

| SEAL /         | UNSEAL_SYS       | 0x8410  | 2      | W              | W   | Unseal SYS mode by SYS_PWD                                              |

| UNSEAL         | SEAL_NVM         | 0x8480  | 0      | W              | W   | Seal SYS mode to USER mode                                              |

|                | WRITE_MFA1       | 0x8800  | 18     | W              | W   | Write data to the MFA1 page                                             |

|                | WRITE_MFA2       | 0x8801  | 4      | W              | W   | Write data to the MFA2 page                                             |

|                | WRITE_SYS        | 0x8802  | 12     |                | W   | Write data to the SYS page                                              |

|                | WRITE_SYS_PWD    | 0x8804  | 2      |                | W   | Change SYS_PWD                                                          |

| NVM            | READ_MFA1        | 0x0800  | 18     | R              | R   | Read data from MFA1 page                                                |

|                | READ_MFA2        | 0x0801  | 4      | R              | R   | Read data from MFA2 page                                                |

|                | READ_SYS         | 0x0802  | 12     |                | R   | Read data from SYS page                                                 |

|                | READ_SYS_PWD     | 0x0804  | 2      |                | R   | Read SYS_PWD                                                            |

|                | READ_DEVICE_ID   | 0x0805  | 4      | R              | R   | Read Device ID                                                          |

| Detter         | INC_CYC_CNT      | 0x9055  | 0      | W              | W   | Increase cycle count                                                    |

| Battery        | READ_CYC_CNT     | 0x1055  | 2      | R              | R   | Read cycle count                                                        |

| Reset          | RESET            | 0xA055  | 0      | W              | W   | Reset the RT9430                                                        |

## **RT9430**

#### **Status Register**

| Bit | Mode | SYMBOL        | OL Definition                              |   |

|-----|------|---------------|--------------------------------------------|---|

| 15  | R    | Reserved      | Reserved                                   | 0 |

| 14  | R    | MFA2_LCK      | MFA_Page2 locked                           | 0 |

| 13  | R    | MFA1_LCK      | MFA_Page1 locked                           | 0 |

| 12  | R    | RT_SECRET_LCK | Root_Secret locked                         | 0 |

| 11  | R    | Reserved      | Reserved                                   | 0 |

| 10  | R    | CHALLENGE_RDY | Challenge ready                            | 0 |

| 9   | R    | MAC_RDY       | MAC ready                                  | 0 |

| 8   | R    | WK_SECRET_RDY | Work Secret ready                          | 0 |

| 7   | R/C  | SWI_TIMEOUT   | SWI timeout occurs                         | 0 |

| 6   | R/C  | SWI_CRC_ERR   | Received error CRC                         | 0 |

| 5   | R    | Reserved      | Reserved                                   | 0 |

| 4   | R    | Reserved      | Reserved                                   | 0 |

| 3   | R/C  | RI            | Reset flag                                 | 1 |

| 2   | R    | BUSY          | Device is busy with an internal operation. | 0 |

| 1   | R    | Reserved      | Reserved                                   | 0 |

| 0   | R    | SYS_MODE      | SYS Mode unsealed                          | 0 |

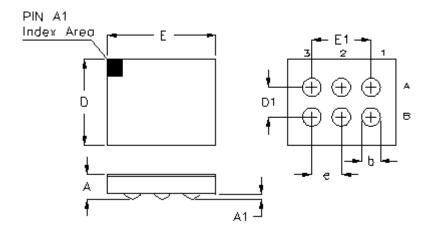

## **Outline Dimension**

| Symbol | Dimensions | n Millimeters | <b>Dimensions In Inches</b> |       |  |

|--------|------------|---------------|-----------------------------|-------|--|

| Symbol | Min        | Max           | Min                         | Max   |  |

| A      | 0.310      | 0.350         | 0.012                       | 0.014 |  |

| A1     | 0.060      | 0.080         | 0.002                       | 0.003 |  |

| b      | 0.220      | 0.280         | 0.009                       | 0.011 |  |

| E      | 1.420      | 1.500         | 0.056                       | 0.059 |  |

| E1     | 0.8        | 300           | 0.031                       |       |  |

| D      | 1.120      | 1.200         | 0.044                       | 0.047 |  |

| D1     | 0.400      |               | 0.016                       |       |  |

| е      | 0.4        | 100           | 0.016                       |       |  |

6B TWL-CSP 1.46x1.16 Package (BSC)

Copyright © 2020 Richtek Technology Corporation. All rights reserved.

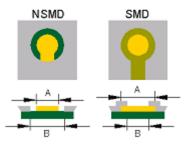

## **Footprint Information**

| Deakage                 | Number of | Tuno | Footprint Dimension (mm) |       |       | Toloropoo |  |

|-------------------------|-----------|------|--------------------------|-------|-------|-----------|--|

| Package                 | Pin       | Туре | е                        | А     | В     | Tolerance |  |

|                         | 6         | NSMD | 0.400                    | 0.250 | 0.350 | .0.025    |  |

| TWL-CSP1.46x1.16-6(BSC) | 6         | SMD  | 0.400                    | 0.260 | 0.250 | ±0.025    |  |

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

#### RICHTEK

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2020 Richtek Technology Corporation. All rights reserved.

www.richtek.com