# **RT9440**

# 2 to 5 Series Cell Fuel Gauge with Integrated Protection Solution for Li-Ion Battery Packs

## 1 General Description

The RT9440 device is a highly accurate and integrated solution for 2 to 5 series cell fuel gauge and protection It features autonomous cell balancing, protection, and charger control.

The RT9440 integrates highly accurate analog peripherals, measures and maintains an accurate record of available capacity, voltage, current, and temperature. It reports the battery pack parameters to the system host controller via the SMBus interface.

The recommended junction temperature range spans from  $-40^{\circ}$ C to  $125^{\circ}$ C, while the ambient temperature range extends from  $-40^{\circ}$ C to  $85^{\circ}$ C.

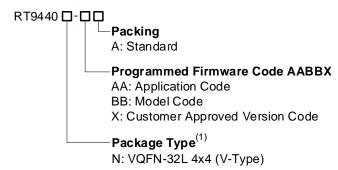

# 2 Ordering Information

#### Note 1.

Richtek products are Richtek Green Policy compliant and marked with <sup>(1)</sup> indicates compatible with the current requirements of IPC/JEDEC J-STD-020.

# 3 Applications

- Notebooks

- Power Tools

- Drones

- Tablets

- UPS/Battery Backup Systems

- Medical Equipment

- Handheld Vacuum Cleaners and Vacuum Robots

## 4 Features

- State of Charge (SOC) Calculated by VoltaicGauge<sup>TM</sup> with Current Sensing (VGCS)

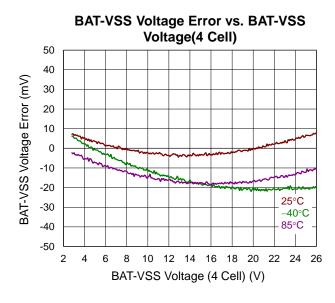

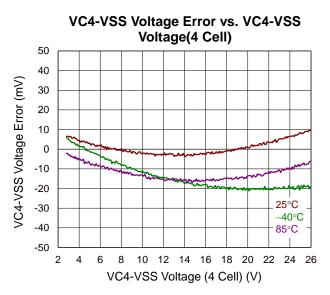

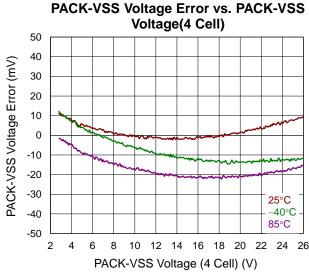

- Voltage Measurement: ±3mV

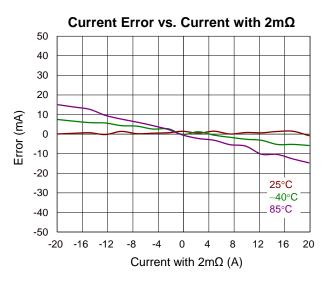

- Current Measurement: ±0.5%

- Battery Temperature Measurement: ±1°C (TA = 0°C to 45°C)

- Hardware Current Protection: ±1mV

- Autonomous Cell Balance

- Configurable Protection Levels and Delay Times for Voltage, Temperature, and Current Protection

- Support Both Voltage-Base and SOC-Base Cell Balance

- 1.5V to 3.3V Configurable VOUT Power Supply

- High-Side N-Channel MOSFET Drivers

- Auxiliary Overcurrent Protection by High-Side N-Channel MOSFET Drop Voltage

- Low Power Consumption

- Normal Mode: 240μA

- Sleep Mode Options: 70μA to 125μA

- Deep Sleep Mode: 30μA

- Shutdown Mode: 1.6μA

- Low Value Sense Resistor:  $0.5m\Omega$  to  $10m\Omega$

- SHA-1/SHA-256/ECC Authentication

- Hardware Load and Charger Detection

- Support Intel<sup>®</sup> Dynamic Battery Power Technology (DBPT V2.0)

- Support Battery Trip Point (BTP)

- Lifetime Data Log and Black Box Recorder

- LED Display Driver Pins with Scan Function

- FUSE Driver

- Support up to 1MHz SMBus Interface

- IATA Support

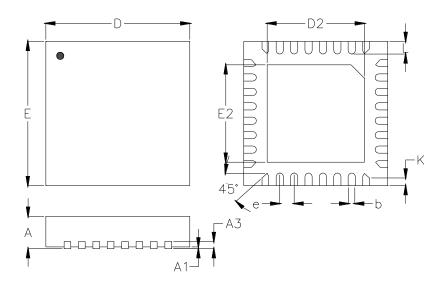

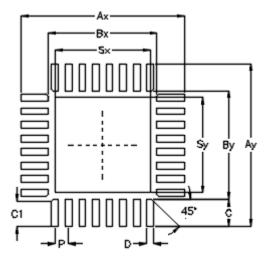

- 32 Pin VQFN Package with 0.4mm Pitch

# **5 Marking Information**

JT=: Product Code YMDAN: Date Code

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

RICHTEK

is a registered trademark of Richtek Technology Corporation.

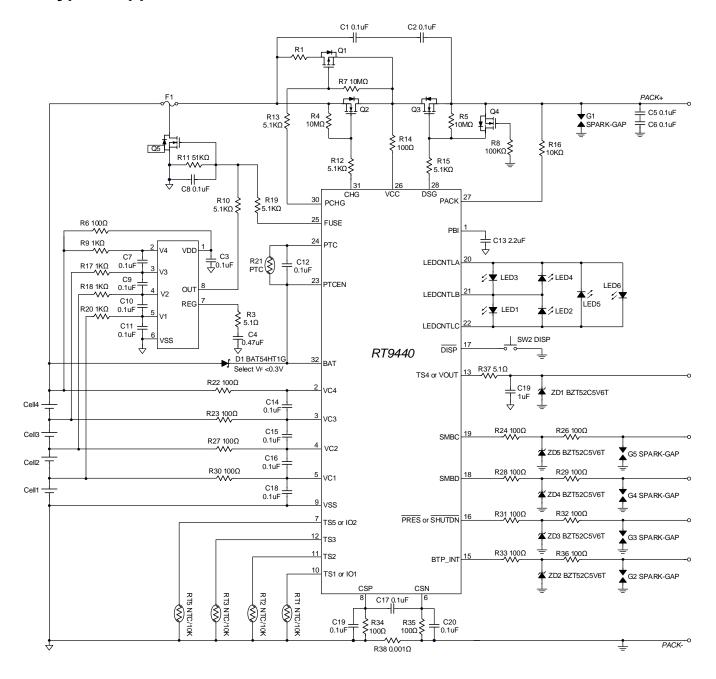

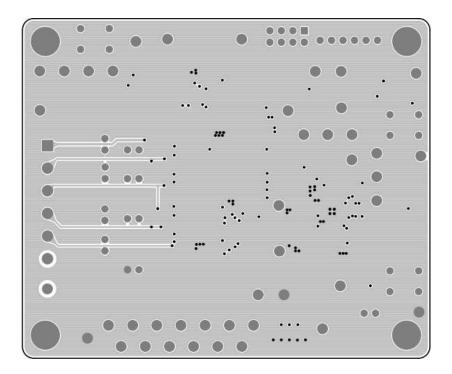

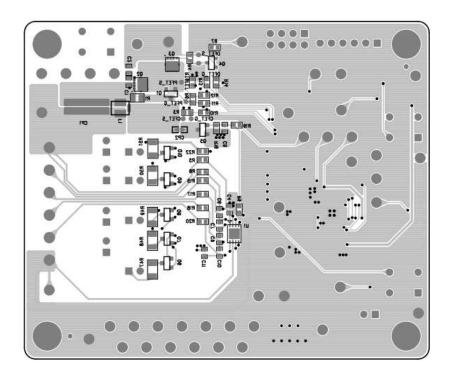

# **6 Simplified Application Circuit**

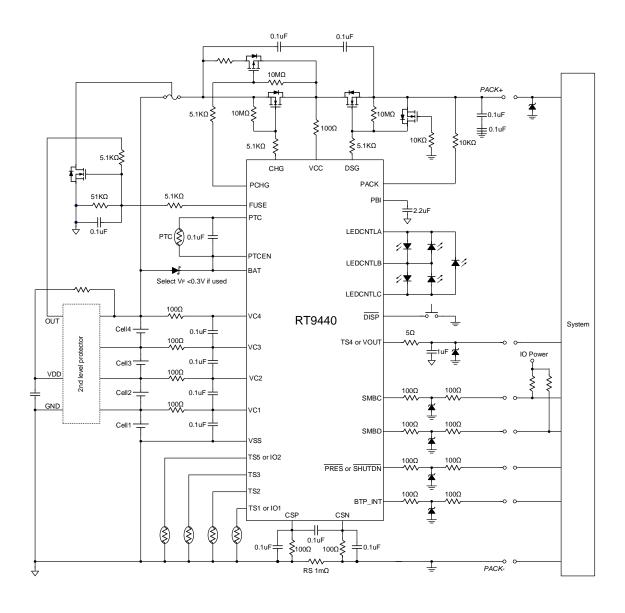

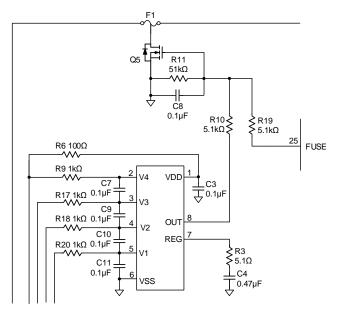

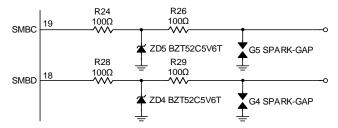

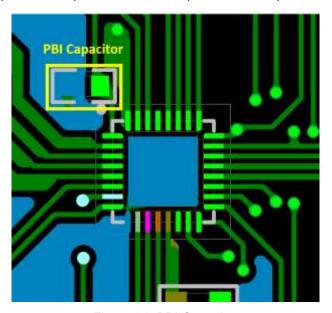

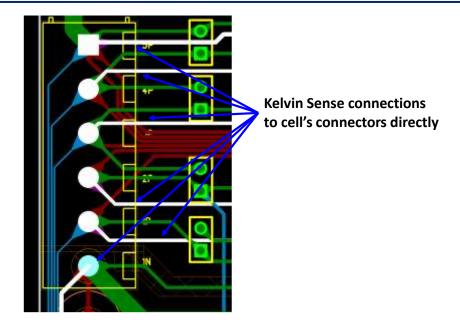

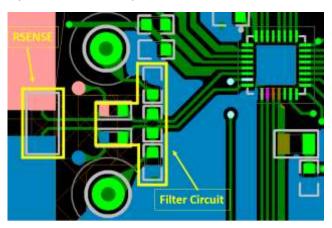

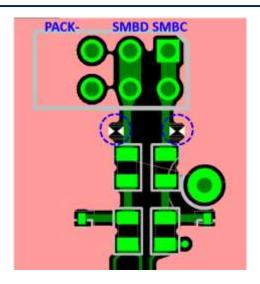

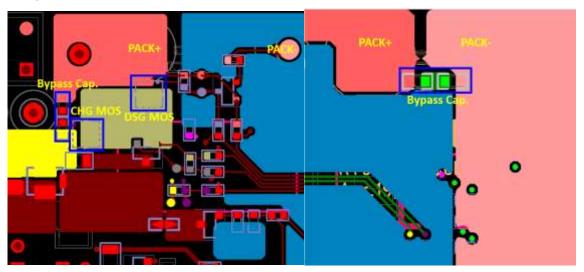

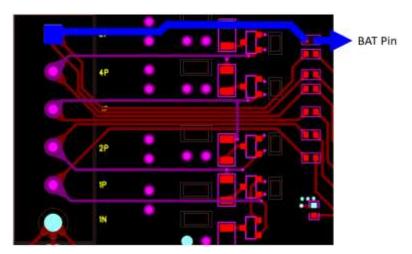

## 6.1 4-cell Application Circuit

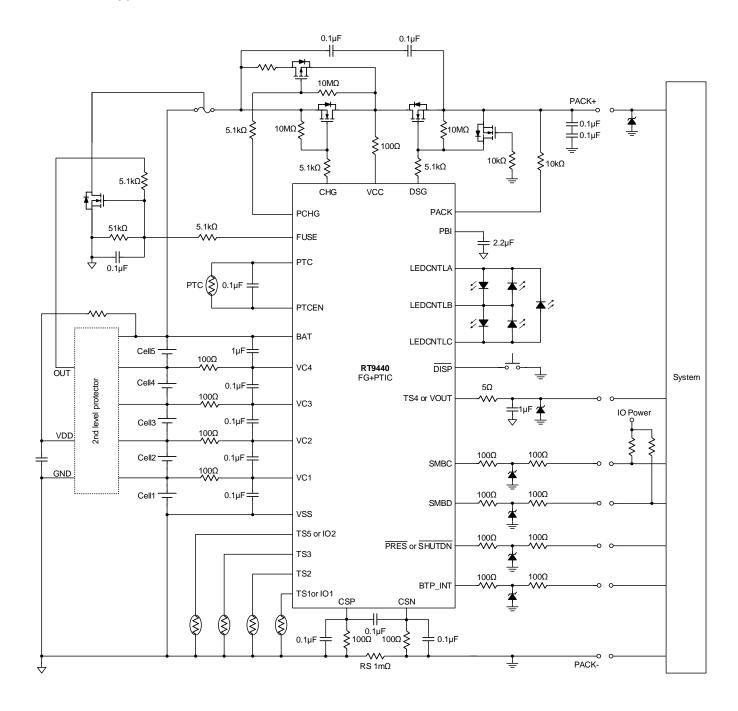

#### 6.2 5-cell Application Circuit

## **Table of Contents**

| 1  | Gene   | ral Description1                                     |    | 17.15  | FUSE Driver                             | 31    |

|----|--------|------------------------------------------------------|----|--------|-----------------------------------------|-------|

| 2  | Order  | ring Information1                                    |    | 17.16  | PTC Permanent Failure                   | 31    |

| 3  | Appli  | cations1                                             |    | 17.17  | Battery Trip Point (BTP)                | 31    |

| 4  | Featu  | res1                                                 |    | 17.18  | Emergency Shutdown                      | 31    |

| 5  | Marki  | ng Information1                                      |    | 17.19  | System Present Operation                | 32    |

| 6  | Simpl  | ified Application Circuit2                           |    | 17.20  | 2-Series, 3-Series, 4-Series, or        |       |

|    | 6.1    | 4-cell Application Circuit2                          |    |        | 5-Series Cell Configuration             | 32    |

|    | 6.2    | 5-cell Application Circuit3                          |    | 17.21  | Communication                           | 32    |

| 7  | Pin C  | onfiguration 5                                       |    | 17.22  | SMBus On and Off State                  | 32    |

| 8  | Funct  | ional Pin Description5                               |    | 17.23  | SBS Commands                            | 32    |

| 9  | Funct  | ional Block Diagram7                                 |    | 17.24  | Authentication                          | 32    |

| 10 | Pin B  | lock Diagram8                                        |    | 17.25  | Cell Voltage Measurement Circuit        | 32    |

| 11 | Absol  | ute Maximum Ratings11                                |    | 17.26  | Current Measurement Circuit             | 33    |

| 12 | Recor  | mmended Operating Conditions12                       |    | 17.27  | External Temperature Measurement Circu  | it 33 |

| 13 | Electr | rical Characteristics12                              |    | 17.28  | PACK Detection Circuit                  | 34    |

| 14 | Timin  | g Diagram22                                          |    | 17.29  | PBI Capacitor                           | 34    |

| 15 | Typica | al Application Circuit23                             |    | 17.30  | High-Side NMOS FETs and                 |       |

| 16 | Typica | al Operating Characteristics24                       |    |        | PMOS FET Control Circuit                | 34    |

| 17 | Appli  | cation Information25                                 |    | 17.31  | Fuse Pin Control Circuit                | 35    |

|    | 17.1   | Fuel Gauge25                                         |    | 17.32  | PTC Over-Temperature Detection Circuit. | 36    |

|    | 17.2   | Power Mode25                                         |    | 17.33  | LEDs Control Circuit                    | 36    |

|    | 17.3   | Measurement26                                        |    | 17.34  | VOUT Circuit                            | 36    |

|    | 17.4   | Primary (1st Level) Safety Features26                |    | 17.35  | SMBus Circuit                           | 36    |

|    | 17.5   | Secondary (2 <sup>nd</sup> Level) Safety Features 27 |    | 17.36  | System Present Circuit                  | 37    |

|    | 17.6   | Charge Control28                                     |    | 17.37  | Thermal Considerations                  | 37    |

|    | 17.7   | Cell Balancing Control29                             |    | 17.38  | Layout Considerations                   | 38    |

|    | 17.8   | Auxiliary LDO Provides Two Features29                | 18 | Outlir | ne Dimension                            | 44    |

|    | 17.9   | Load Detection and Charger Detection29               | 19 | Footp  | print Information                       | 45    |

|    | 17.10  | Black Box Recorder30                                 | 20 | Packi  | ng Information                          | 46    |

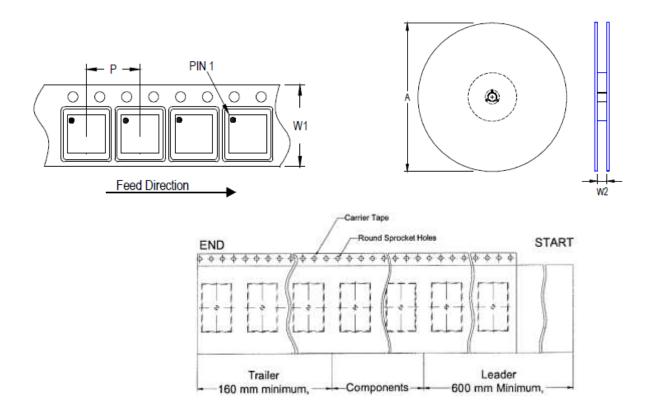

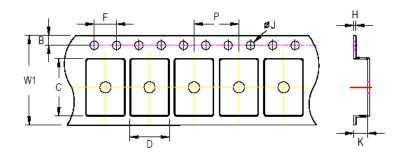

|    | 17.11  | Lifetime Data Log30                                  |    | 20.1   | Tape and Reel Data                      | 46    |

|    | 17.12  | Intel® Dynamic Battery Power Technology              |    | 20.2   | Tape and Reel Packing                   |       |

|    |        | (DBPT V2.0)31                                        |    | 20.3   | Packing Material Anti-ESD Property      | 48    |

|    | 17.13  | IATA Support31                                       | 21 | Datas  | heet Revision History                   | 49    |

|    | 17.14  | LED Display31                                        |    |        |                                         |       |

www.richtek.com

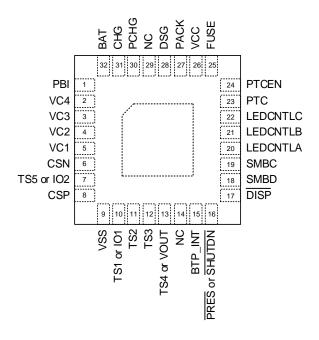

# 7 Pin Configuration

(TOP VIEW)

VQFN-32L 4x4

# 8 Functional Pin Description

| Pin No. | Pin Name   | Pin Function                                                                                                                                                       |

|---------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

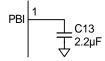

| 1       | PBI        | Power backup pin.                                                                                                                                                  |

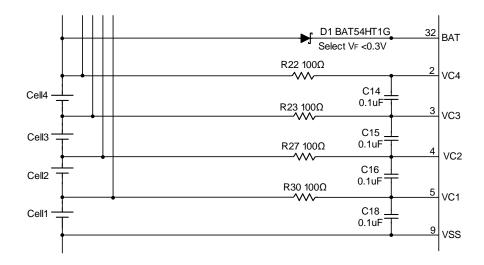

| 2       | VC4        | The voltage input pin is for the 4 <sup>th</sup> cell. The balance current input is for the 4th cell.                                                              |

| 3       | VC3        | The voltage input pin is for the 3 <sup>rd</sup> cell.  The balance current input is for the 3rd cell and return the balance current for the 4 <sup>th</sup> cell. |

| 4       | VC2        | The voltage input pin is for the 2 <sup>nd</sup> cell.  The balance current input is for the 2nd cell and return the balance current for the 3 <sup>rd</sup> cell. |

| 5       | VC1        | The voltage input pin is for the 1 <sup>st</sup> cell.  The balance current input is for the 1st cell and return the balance current for the 2 <sup>nd</sup> cell. |

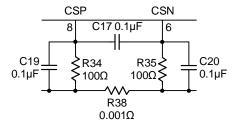

| 6       | CSN        | Battery current sensing negative input.                                                                                                                            |

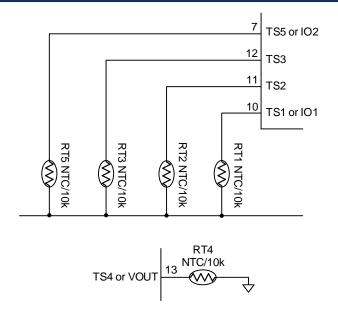

| 7       | TS5 or IO2 | Temperature sensor 5 measurement input pin, or multi-function GPIO.                                                                                                |

| 8       | CSP        | Battery current sensing positive input.                                                                                                                            |

| 9       | VSS        | Ground.                                                                                                                                                            |

| 10      | TS1 or IO1 | Temperature sensor 1 measurement input pin, or multi-function GPIO.                                                                                                |

| 11      | TS2        | Temperature sensor 2 measurement input pin.                                                                                                                        |

| 12      | TS3        | Temperature sensor 3 measurement input pin.                                                                                                                        |

| Pin No. | Pin Name          | Pin Function                                                                                                                                                                                                   |

|---------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

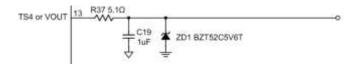

| 13      | TS4 or VOUT       | Temperature sensor 4 measurement input pin or it can be used as the power supply for VOUT.                                                                                                                     |

| 14, 29  | NC                | There is no internal connection.                                                                                                                                                                               |

| 15      | BTP_INT           | Battery Trip Point (BTP) interrupt output pin. It should be connected to VSS if it is not being used.                                                                                                          |

| 16      | PRES or<br>SHUTDN | Host system present input for removable battery pack or emergency shutdown for non-removable battery pack input pin. No need external pull up resistor. It should be connected to VSS if it is not being used. |

| 17      | DISP              | This pin is used to control the LED display It should be connected to VSS if it is not being used.                                                                                                             |

| 18      | SMBD              | SMBus data pin.                                                                                                                                                                                                |

| 19      | SMBC              | SMBus clock pin.                                                                                                                                                                                               |

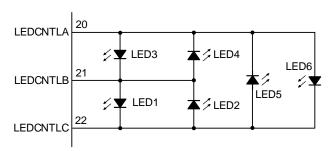

| 20      | LEDCTLA           | LED display segment that drives the external LEDs. It should be left unconnected if not being used.                                                                                                            |

| 21      | LEDCTLB           | LED display segment that drives the external LEDs. It should be left unconnected if not being used.                                                                                                            |

| 22      | LEDCTLC           | LED display segment that drives the external LEDs. It should be left unconnected if not being used.                                                                                                            |

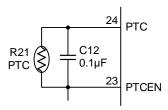

| 23      | PTC               | Safety PTC thermistor input pin. To disable, connect both PTC and PTCEN to VSS.                                                                                                                                |

| 24      | PTCEN             | Safety PTC thermistor enable input pin. Connect to BAT. To disable, connect both PTC and PTCEN to VSS.                                                                                                         |

| 25      | FUSE              | Fuse drive output pin. It should be connected to VSS if it is not being used.                                                                                                                                  |

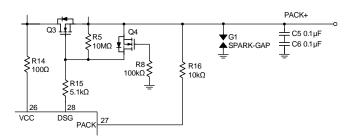

| 26      | VCC               | Secondary power supply input pin.                                                                                                                                                                              |

| 27      | PACK              | Pack sense input pin.                                                                                                                                                                                          |

| 28      | DSG               | N-Channel MOSFET drive output pin for discharge MOSFET control.                                                                                                                                                |

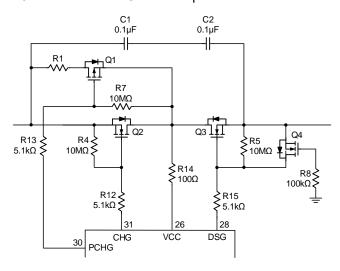

| 30      | PCHG              | PMOS pre-charge MOSFET drive output pin.                                                                                                                                                                       |

| 31      | CHG               | N-Channel MOSFET drive output pin for charge MOSFET control.                                                                                                                                                   |

| 32      | BAT               | Primary power supply input pin. The voltage input pin is for the 5 <sup>th</sup> cell. The balance current input is for the 5 <sup>th</sup> cell.                                                              |

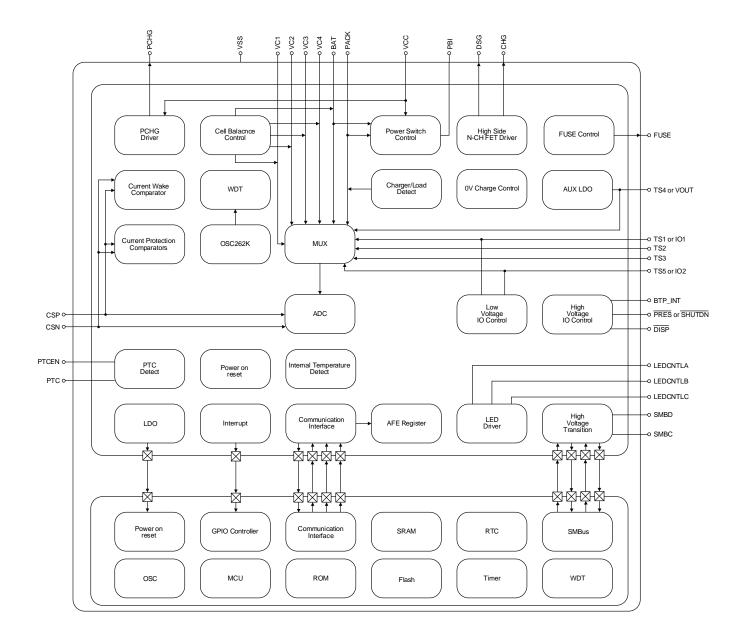

# 9 Functional Block Diagram

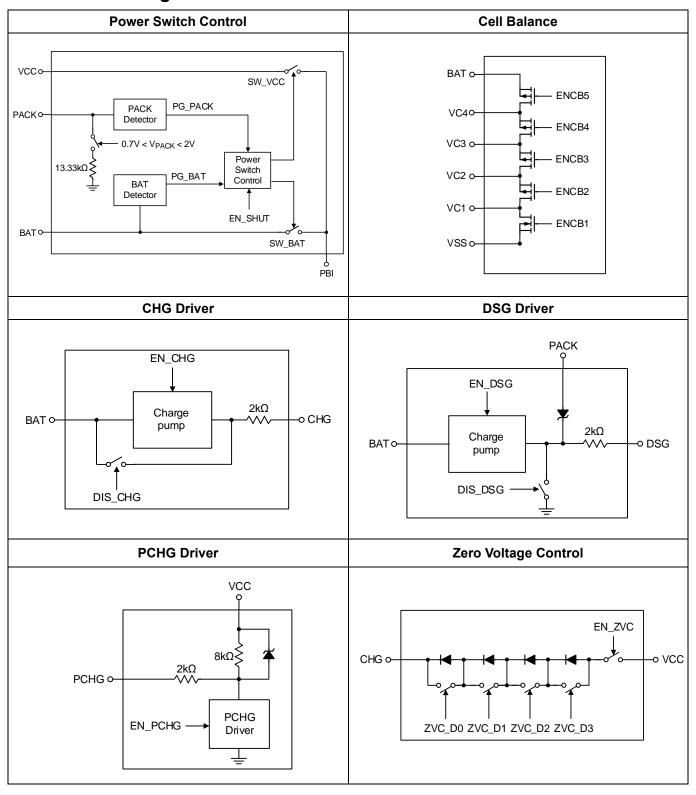

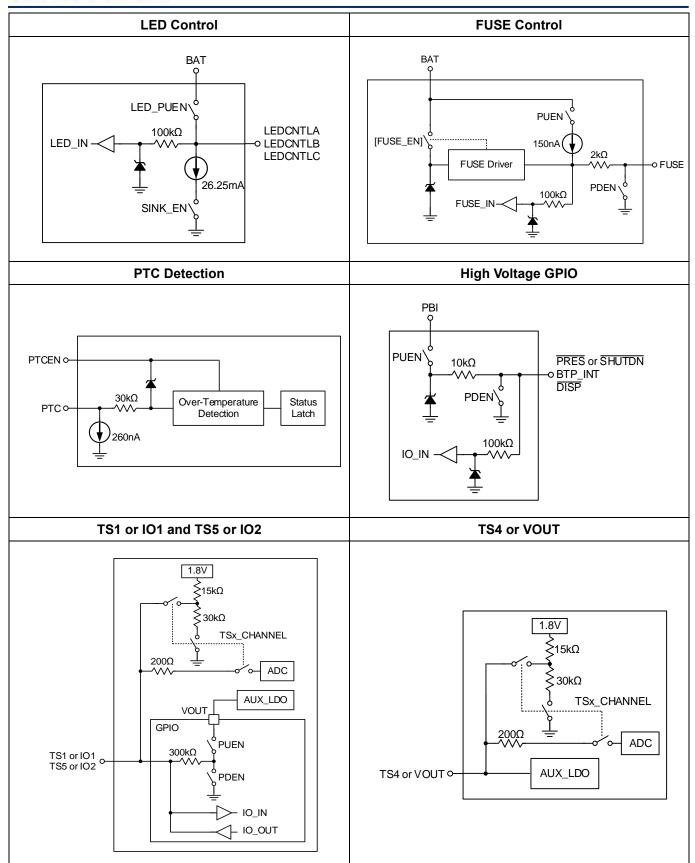

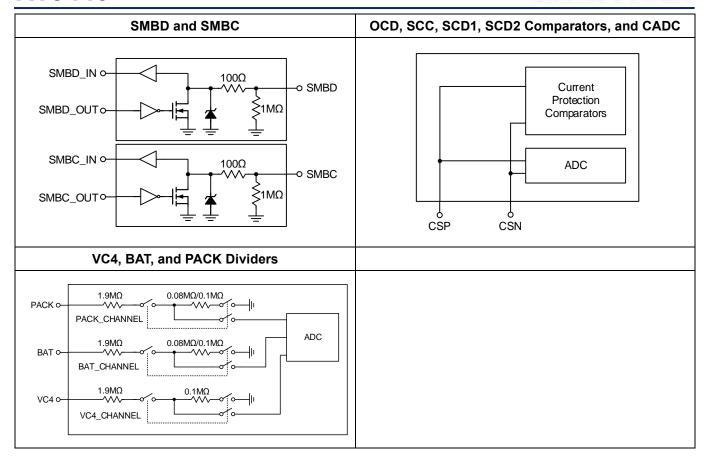

# 10 Pin Block Diagram

# 11 Absolute Maximum Ratings

#### (Note 2)

| Supply Voltage on VCC, PBI Pin to VSS                                       | 0.3V to 30V                               |

|-----------------------------------------------------------------------------|-------------------------------------------|

| Input Voltage on PACK, PRES, BTP_INT, DISP to VSS                           | 0.3V to 30V                               |

| Input Voltage on SMB, SMBD to VSS                                           | 0.3V to 30V                               |

| Input Voltage on PTC, PTCEN, LEDCNTLA,                                      |                                           |

| LEDCNTLB, LEDCNTLC to VSS                                                   | 0.3V to 30V                               |

| Input Voltage on CSP, CSN to VSS                                            | 0.3V to 0.3V                              |

| Input Voltage on BAT                                                        | VC4 - 0.3V to VC4 + 8.5V or VSS + 30V     |

| Input Voltage on VC4                                                        | VC3 - 0.3V to VC3 + 8.5V or VSS + 30V     |

| Input Voltage on VC3                                                        | VC2 - 0.3V to VC2 + 8.5V or VSS + 30V     |

| Input Voltage on VC2                                                        | VC1 - 0.3V to VC1 + 8.5V or VSS + 30V     |

| Input Voltage on VC1                                                        | VSS - 0.3V to VSS + 8.5V or VSS + 30V     |

| Input Voltage on BAT to PACK (5 Cells Connection)                           | VPACK - 0.3V to VPACK + 8.5V              |

| Input Voltage on VC4 to PACK (4 Cells Connection)                           | VPACK - 0.3V to VPACK + 8.5V              |

| Output on CHG, DSG to VSS                                                   | 0.3V to 36V                               |

| Output on PCHG, FUSE to VSS                                                 | 0.3V to 30V                               |

| • Input Voltage on TS1, TS2, TS3, TS4, TS5 to VSS                           | 0.3V to 5.5V                              |

| Functional Temperature                                                      | 40°C to 85°C                              |

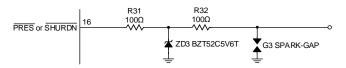

| <ul> <li>Power Dissipation, PD @ TA = 25°C</li> </ul>                       |                                           |

| VQFN-32L 4x4                                                                | 3.59W                                     |

| • Package Thermal Resistance (Note 3)                                       |                                           |

| VQFN-32L 4x4, θJA                                                           | 27.8°C/W                                  |

| VQFN-32L 4x4, θJC                                                           |                                           |

| Lead Temperature (Soldering, 10 sec.)                                       |                                           |

| Junction Temperature                                                        |                                           |

| Storage Temperature Range                                                   | 65°C to 150°C                             |

| • ESD Susceptibility (Note 4)                                               |                                           |

| HBM (Human Body Model)                                                      | 2kV                                       |

| Note 2 Stranges havend these listed under "Absolute Maximum Patings" may as | use permanent damage to the device. These |

- Note 2. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 3.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A$  = 25°C with the component mounted on a high effective-thermalconductivity four-layer test board on a JEDEC 51-7 thermal measurement standard. θ<sub>JC</sub> is measured at the bottom of the package.

- Note 4. Devices are ESD sensitive. Handling precautions are recommended.

# 12 Recommended Operating Conditions

## (Note 5)

| Voltage on BAT, VCC, PBI Pin to VSS                   | 2.8V to 26V                |

|-------------------------------------------------------|----------------------------|

| Input Voltage Range, PACK, SMBC,                      |                            |

| SMBD, PRES, BTP_INT, DISP to VSS                      | 0V to 26V                  |

| Input Voltage Range, PTC, PTCEN,                      |                            |

| LEDCNTLA, LEDCNTLB, LEDCNTLC to VSS                   | 0V to VBAT                 |

| Input Voltage Range, CSP, CSN to VSS                  | 0.2V to 0.2V               |

| Input Voltage Range, VC4                              | Vvc3 to Vvc3 + 5V          |

| Input Voltage Range, VC3                              | Vvc2 to Vvc2 + 5V          |

| Input Voltage Range, VC2                              | Vvc1 to Vvc1 + 5V          |

| Input Voltage Range, VC1                              | 0V to 5V                   |

| Input Voltage Range, BAT to PACK (5 cells connection) | VPACK - 0.2V to VPACK + 5V |

| Input Voltage Range, VC4 to PACK (4 cells connection) | VPACK - 0.2V to VPACK + 5V |

| Output Voltage Range, CHG, DSG to VSS                 | VBAT to VBAT + 12V         |

| Output Voltage Range, PCHG to VSS                     | Vvcc - 8V to Vvcc          |

| Output Voltage Range, FUSE to VSS                     | 0V to 26V                  |

| Input Voltage Range, TS1, TS2, TS3, TS4, TS5 to VSS   | 0V to 3.3V                 |

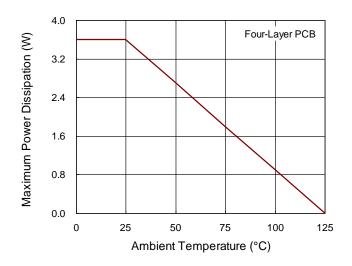

| External Capacitor, PBI                               | 2.2μF                      |

|                                                       |                            |

Note 5. The device is not guaranteed to function outside its operating conditions.

## 13 Electrical Characteristics

(Typical values are at  $T_A$  = 25°C and  $V_{BAT}$  = 14.4V, Min./Max. values are at  $T_A$  = -40°C to 85°C and 2.8V  $\leq$   $V_{BAT}$   $\leq$  26V, unless otherwise noted.)

• Ambient Temperature Range ----- --- -40°C to 85°C • Junction Temperature Range ----- -40°C to 125°C

| Parameter                     | Symbol         | Test Conditions                        | Min  | Тур  | Max  | Unit |  |  |  |  |

|-------------------------------|----------------|----------------------------------------|------|------|------|------|--|--|--|--|

| Supply Current                | Supply Current |                                        |      |      |      |      |  |  |  |  |

| Normal Mode                   | INORMAL        | CHG on. DSG on, no Flash write         |      | 240  |      | μА   |  |  |  |  |

| Class Mada                    | ISLEEP         | CHG off, DSG on, no SBS communication  |      | 125  |      | - μΑ |  |  |  |  |

| Sleep Mode                    |                | CHG off, DSG off, no SBS communication |      | 70   |      |      |  |  |  |  |

| Deep Sleep Mode               | IDEEPSLEEP     | VOUT only                              |      | 30   |      | μА   |  |  |  |  |

| Shutdown Mode                 | ISHDN          |                                        |      | 1.6  |      | μΑ   |  |  |  |  |

| Power Supply Control          |                |                                        |      |      |      |      |  |  |  |  |

| BAT to VCC Switchover Voltage | Vswitchover-   | VBAT < VSWITCHOVER-                    | 2.55 | 2.65 | 2.75 | V    |  |  |  |  |

**RT9440**

| Parameter                                             | Symbol          | Test Conditions                                                       | Min    | Тур   | Max    | Unit |

|-------------------------------------------------------|-----------------|-----------------------------------------------------------------------|--------|-------|--------|------|

| VCC to BAT Switchover Voltage                         | Vswitchover+    | VBAT > VSWITCHOVER- + VHYS                                            | 2.95   | 3.1   | 3.25   | V    |

| Switchover Voltage<br>Hysteresis                      | VHYS            | Vswitchover+ -<br>Vswitchover-                                        |        | 450   |        | mV   |

| BAT Pin Leakage Current                               | ILK_BAT         | BAT pin, BAT = 0V, VCC = 25V, PACK = 25V                              | 1      | I     | 1      | μΑ   |

| VCC Pin Leakage Current                               | ILK_VCC         | VCC pin, BAT = 25V, VCC = 0V, PACK = 0V                               |        |       | 1      | μΑ   |

| BAT and PACK Pin Leakage<br>Current                   | ILK_BAT_PACK    | BAT and PACK terminals,<br>BAT = 0V, VCC = 0V, PACK=<br>0V, PBI = 25V | 1      | 1     | 1      | μΑ   |

| Internal Pull-Down<br>Resistance                      | RPACK_PD        | 0.7V < VPACK < 2V                                                     | 8.5    | 13.33 | 19     | kΩ   |

| Start-Up Voltage                                      | Vsu+            | VPACK > VSHUTDOWN+                                                    | 2.65   |       | 2.85   | V    |

| Shutdown Voltage                                      | VSHDN-          | VPACK < VSHUTDOWN-                                                    | 2.55   | I     | 2.75   | V    |

| <b>Current Wake Detector</b>                          |                 |                                                                       |        |       |        |      |

|                                                       |                 |                                                                       | ±0.075 | ±0.15 | ±0.225 | mV   |

|                                                       | VWAKE           | Maga Maga                                                             | ±0.15  | ±0.3  | ±0.45  | mV   |

| \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                |                 |                                                                       | ±0.3   | ±0.6  | ±0.9   | mV   |

| Wakeup Voltage Threshold                              |                 | VCSP - VCSN                                                           | ±0.6   | ±1.2  | ±1.8   | mV   |

|                                                       |                 |                                                                       | ±1.2   | ±2.4  | ±3.6   | mV   |

|                                                       |                 |                                                                       | ±2.4   | ±4.8  | ±7.2   | mV   |

| Time from Application of<br>Current to Wake Interrupt | twake           |                                                                       |        | 0.2   | 0.5    | ms   |

| Wake Comparator Startup<br>Time                       | twake_su        |                                                                       | 1      | 3.35  | 1      | ms   |

| Cell Balancing                                        |                 |                                                                       |        |       |        |      |

| Internal Cell Balancing<br>Resistance                 | R_CB            | RDS(ON) for internal MOSFET switch at 3V< VDS <4.5V                   |        | 100   | 200    | Ω    |

| SMBD and SMBC                                         |                 |                                                                       |        |       |        |      |

| High-Level Input                                      | VIH             |                                                                       | 1.3    |       |        | V    |

| Low-Level Input                                       | VIL             |                                                                       |        |       | 0.8    | V    |

| Output Voltage Low                                    | Vol             | IOL = 1.5mA                                                           |        |       | 0.4    | V    |

| Pull-Down Resistance                                  | R <sub>PD</sub> |                                                                       | 0.6    | 1     | 1.5    | МΩ   |

| PRES, BTP_INT, and DISP                               |                 |                                                                       |        |       |        |      |

| High-Level Input                                      | VIH             |                                                                       | 1.3    |       |        | V    |

| Low-Level Input                                       | VIL             |                                                                       |        |       | 0.55   | V    |

| Outrot Valta and Hinda                                | Vон             | PRES, BTP_INT and DISP,<br>VBAT > 5.5V, IOH = -0μA                    | 3.5    |       | 5      | V    |

| Output Voltage High                                   | VOR             | PRES, BTP_INT and DISP,<br>$V_{BAT} > 5.5V$ , $I_{OH} = -10\mu A$     | 1.8    |       | 5      |      |

| Output Voltage Low                                    | VoL             | I <sub>OL</sub> = 1.5mA                                               |        |       | 0.4    | V    |

| Parameter                                                | Symbol        | Test Conditions                                                                                        | Min            | Тур   | Max  | Unit |

|----------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------|----------------|-------|------|------|

| PRES Input Leakage<br>Current                            | ILK_PRES      | PRES pin, BAT = 2.8V, PRES = 26V                                                                       |                |       | 1    | μΑ   |

| BTP_INT Input Leakage<br>Current                         | ILK_BTP_INT   | BTP_INT pin, BAT = 2.8V,<br>BTP_INT = 26V                                                              | I              | 1     | 1    | μΑ   |

| DISP Input Leakage Current                               | ILK_DISP      | DISP pin, BAT = 2.8V, DISP = 26V                                                                       |                |       | 1    | μΑ   |

| Output Reverse Resistance                                | Ro            | Between PRES or BTP_INT or DISP and PBI                                                                | 8              | 20    |      | kΩ   |

| LEDCTLA, LEDCTLB, and L                                  | EDCTLC        |                                                                                                        |                |       |      |      |

| High-Level Input                                         | VIH           |                                                                                                        | 1.4            |       |      | V    |

| Low-Level Input                                          | VIL           |                                                                                                        |                |       | 0.5  | V    |

| Output Voltage High                                      | Vон           | VBAT > 3.3V, IOH = −22.5mA                                                                             | VBAT -<br>1.6V |       |      | V    |

| High-Level Output Current Protection                     | Isc           |                                                                                                        | -30            | -45   | -60  | mA   |

| Low-Level Output Current                                 | IOL           | VBAT > 3.3V, VOH = 0.4V                                                                                | 19.5           | 26.25 | 33   | mA   |

| Input Leakage Current                                    | ILK           | LEDCNTLA/B/C pin,<br>LEDCNTLA/B/C = BAT = 25V                                                          |                |       | 1    | μΑ   |

| Frequency of LED Pattern                                 | fLEDCNTLx     |                                                                                                        |                | 180   |      | Hz   |

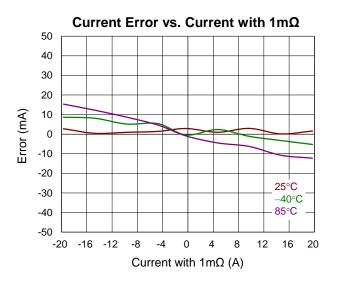

| Current Measurement                                      |               |                                                                                                        |                |       |      |      |

| Input Voltage Range                                      |               | VCSP - VCSN                                                                                            | -0.1           |       | 0.1  | V    |

| Offset Error                                             | IOERR         | VCSP - VCSN  = 0mV                                                                                     | -6             | ±3.5  | 6    | μV   |

| Gain Error                                               | IGERR         | VCSP - VCSN  = 100mV                                                                                   | -0.5           | ±0.2  | 0.5  | %    |

| Effective Input Resistance                               | R_CC_IN       |                                                                                                        |                | 2.7   |      | MΩ   |

| Conversion Time                                          | t_CC_CONV     | Single conversion in normal mode                                                                       |                | 125   |      | ms   |

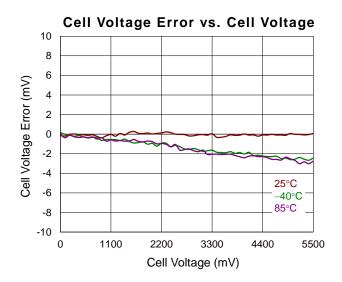

| Voltage Measurement                                      |               |                                                                                                        |                |       |      |      |

| Input Voltage Range<br>(Differential Cell Input<br>Mode) | VADC_IN_CELLS |                                                                                                        | 0              |       | 5    | V    |

| Input Voltage Range<br>(Divider Measurement<br>Mode)     | VADC_IN_DIV   | Applicable to divider measurements using the BAT, VC4 and PACK, pins relative to VSS.                  | 0              |       | 26   | V    |

|                                                          |               | VVC4 - VVC3, VVC3 - VVC2,<br>VVC2 - VVC1, VVC1 - VVSS                                                  | -10            | ±3    | 10   | mV   |

| Cell Voltage Measurement<br>Accuracy                     | VCELL_ACC     | $V_{BAT} - V_{VC4}$ , impedance between top node of $5^{th}$ cell and the BAT pin is under $0.3\Omega$ | -12.5          | ±5    | 12.5 | mV   |

| Parameter                                   | Symbol       | Test Conditions                                                                                                                                                                                         | Min   | Тур   | Max   | Unit      |

|---------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-----------|

| MOSFET Voltage Drop                         | VALORET LOS  | $V_{BAT} - V_{PACK}$ , Impedance between top node of $5^{th}$ cell and the BAT pin is under $0.3\Omega$ and without Schottky diode $7.5V < V_{BAT} \le 26V$                                             | -12.5 | ±5    | 12.5  | m\/       |

| Measurement Accuracy                        | VMOSFET_ACC  | VBAT – VPACK, Impedance between top node of $5^{th}$ cell and the BAT pin is under $0.3\Omega$ and without Schottky diode $2.8V \le VBAT \le 7.5V$                                                      | -32.5 | ±20   | 32.5  | mV        |

|                                             |              | Vvc4 - Vvss                                                                                                                                                                                             | -50   | ±15   | 50    | mV        |

| Stack Voltage Measurement<br>Accuracy       | VSTACK_ACC   | VBAT – VVSS, Impedance<br>between top node of 5 <sup>th</sup> cell<br>and the BAT pin is under<br>0.3Ω and without Schottky<br>diode                                                                    | -62.5 | ±25   | 62.5  | mV        |

| PACK Pin Voltage<br>Measurement<br>Accuracy | VPACK_ACC)=  | VPACK - VVSS                                                                                                                                                                                            | -50   | ±15   | 50    | mV        |

| Effective Input Resistance                  | R_ADC_IN)=   |                                                                                                                                                                                                         |       | 15.3  |       | $M\Omega$ |

| Conversion Time                             | t_ADC_CONV)= | Single conversion in normal mode                                                                                                                                                                        |       | 10    | 1     | ms        |

| High-Side N-MOSFET Drive                    | rs           |                                                                                                                                                                                                         |       |       |       |           |

| DSG MOSFET Turn-On                          | \/           | Ratio = (VDSG - VBAT) / VBAT,<br>3.4V < VBAT < 5V<br>Connect a $10M\Omega$ resistor<br>between PACK and DSG                                                                                             | 2.133 | 2.333 | 2.433 |           |

| Ratio                                       | VDSG_RATIO   | Ratio = $(V_{DSG} - V_{BAT}) / V_{BAT}$ ,<br>2.8V $\leq V_{BAT} \leq 3.4V$<br>Connect a 10M $\Omega$ resistor<br>between PACK and DSG                                                                   | 1.93  | 2.18  | 2.433 |           |

| CHG MOSFET Turn-On                          | V            | Ratio = (VCHG - VBAT) / VBAT,<br>3.4V < VBAT < 5V<br>Connect a 10MΩ resistor<br>between BAT and CHG                                                                                                     | 2.133 | 2.333 | 2.433 |           |

| Ratio                                       | Vchg_ratio   | Ratio = (VCHG - VBAT) / VBAT, $2.8V \le VBAT \le 3.4V$<br>Connect a $10M\Omega$ resistor between BAT and CHG                                                                                            | 1.93  | 2.08  | 2.23  |           |

| DSG MOSFET Turn-On<br>Voltage               | VDSGON       | VDSGON = VDSG − VBAT, VBAT $\geq$ 5V, connect a 10MΩ resistor between PACK and DSG                                                                                                                      | 10.5  | 11.5  | 12.5  | V         |

| CHG MOSFET Turn-On<br>Voltage               | Vchgon       | $\label{eq:chgon} \begin{array}{l} \text{VCHGON} = \text{VCHG} - \text{VBAT},  \text{VBAT} \\ \geq 5\text{V}, \\ \text{connect a 10M}\Omega \text{ resistor} \\ \text{between BAT and CHG} \end{array}$ | 10.5  | 11.5  | 12.5  | ٧         |

| DSG MOSFET Turn-Off<br>Voltage              | VDSGOFF      | VDSGOFF = VDSG $-$ VPACK, connect a 10M $\Omega$ resistor between PACK and DSG                                                                                                                          | -0.4  |       | 0.4   | <b>V</b>  |

| Parameter                                        | Symbol   | Test Conditions                                                                                                                                                | Min            | Тур | Max  | Unit |

|--------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|------|------|

| CHG MOSFET Turn-Off<br>Voltage                   | VCHGOFF  | VCHGOFF = VCHG $-$ VBAT,<br>VGS resistor = $10M\Omega$                                                                                                         | -0.4           | -   | 0.4  | V    |

| DSG Rise Time<br>(0% to 35% V <sub>DSGON</sub> ) | tr_dsg   | Connect a $C_L = 4.7 nF$<br>between DSG and PACK,<br>a 5.1k $\Omega$ resistor between<br>DSG and $C_L$ ,<br>a 10M $\Omega$ resistor between<br>PACK and DSG    |                | 200 | 500  | μs   |

| CHG Rise Time<br>(0% to 35% VCHGON)              | tr_chg   | Connect a $C_L = 4.7 nF$ between CHG and BAT, a 5.1k $\Omega$ resistor between CHG and $C_L$ , a 10M $\Omega$ resistor between BAT and CHG                     |                | 200 | 500  | μs   |

| DSG Fall Time<br>(VDSGON to 1V)                  | tF_DSG   | Connect a $C_L = 4.7 nF$<br>between DSG and PACK,<br>a 5.1k $\Omega$ resistor between<br>DSG and $C_L$ ,<br>a 10M $\Omega$ resistor between<br>PACK and DSG    |                | 40  | 100  | μs   |

| CHG Fall Time<br>(VDSGON to 1V)                  | tF_CHG   | Connect a $C_L = 4.7 nF$<br>between CHG and BAT,<br>a 5.1k $\Omega$ resistor between<br>CHG and $C_L$ ,<br>a 10M $\Omega$ resistor between<br>BAT and CHG      |                | 40  | 100  | μs   |

| PCHG P-MOSFET Drivers                            |          |                                                                                                                                                                |                |     |      |      |

| PCHG MOSFET Turn-On<br>Voltage                   | VPCHGON  | $\begin{array}{l} \text{VPCHGON} = \text{VVCC - VPCHG}, \\ \text{VGs resistor} = 10 \text{M}\Omega \end{array}$                                                | 6              | 7   | 8    | V    |

| PCHG MOSFET Turn-Off<br>Voltage                  | VPCHGOFF | $\begin{array}{l} \text{VPCHGOFF} = \text{VVCC - VPCHG}, \\ \text{VGS resistor} = 10 \text{M}\Omega \end{array}$                                               | -0.4           | -   | 0.4  | V    |

| PCHG Rise Time (10% to 90% VPCHGON)              | tr_pchg  | $V_{VCC}$ ≥ 8V, connect a C <sub>L</sub> = 4.7nF between PCHG and VCC, a 5.1kΩ resistor between PCHG and C <sub>L</sub> , a 10MΩ resistor between PCHG and VCC |                | 40  | 200  | μs   |

| PCHG Fall Time (90% to 10% VPCHGON)              | tf_PCHG  | $V$ VCC ≥ 8V, connect a CL = 4.7nF between PCHG and VCC, a 5.1k $\Omega$ resistor between PCHG and CL, a 10M $\Omega$ resistor between PCHG and VCC            |                | 40  | 200  | μs   |

| Fuse Driver                                      |          |                                                                                                                                                                |                |     |      |      |

| Output Voltage High                              | Vон      | $V_{BAT} \geq 8V, \ C_L = 1nF, \\ I_{OH} = 0 \mu A$                                                                                                            | 8              | 9.6 | 10.7 | V    |

| Output Voltage High                              | VOH      | $VBAT < 8V, CL = 1nF, \\ IOH = 0\mu A$                                                                                                                         | VBAT –<br>0.1V |     | VBAT | V    |

| Output Voltage Low                               | VoL      | IoL = 1.5mA                                                                                                                                                    |                | -   | 0.4  | V    |

| High-Level Input                                 | ViH      |                                                                                                                                                                | 1.5            | 2   | 2.5  | V    |

| Low-Level Input                                  | VIL      |                                                                                                                                                                |                |     | 0.54 | V    |

| Parameter                                 | Symbol      | Test Conditions                                 | Min  | Тур  | Max | Unit   |

|-------------------------------------------|-------------|-------------------------------------------------|------|------|-----|--------|

| Internal Pull-Up Current                  | IAFEFUSE_PU | VBAT ≥ 8V, VAFEFUSE = VSS                       | 100  | 150  | 330 | nA     |

| Output Impedance                          | RAFEFUSE    |                                                 | 1.4  | 2    | 2.6 | kΩ     |

| Fuse Trip Detection Delay                 | tDLY        |                                                 | 128  |      | 256 | μS     |

| Fuse Output Rise Time                     | tR          | $VBAT \ge 8V$ , $CL = 1nF$ , $VOH = 0V$ to $5V$ |      | 5    | 20  | μS     |

| Internal Temperature Sens                 | or          |                                                 |      |      |     |        |

| Internal Temperature<br>Measurement Error | INTGERR     |                                                 |      | ±3   | ŀ   | °C     |

| TS1, TS2, TS3, TS4, and TS                | S5          |                                                 |      |      |     |        |

| Input Voltage Range                       | VIN         |                                                 | -0.3 |      | 3.3 | V      |

| Internal Resistance                       | D TO        | Pull-up resistance                              |      | 15   |     | kΩ     |

| Internal Resistance                       | R_TS        | Pull-down resistance                            |      | 30   | -   | kΩ     |

| PTC and PTCEN                             |             |                                                 |      |      |     |        |

| PTC Trip Resistance                       | RTRIP       |                                                 | 1.3  | 2.1  | 4   | MΩ     |

| PTC Trip Voltage                          | VPTC_TRIP   | VPTC_TRIP = VPTCEN - VPTC                       | 490  | 540  | 645 | mV     |

| Internal PTC Current Bias                 | IPTC        |                                                 | 160  | 260  | 375 | nA     |

| PTC Delay Time                            | tDLY_PTC    |                                                 | 40   | 80   | 145 | ms     |

| Program Flash                             |             | •                                               |      |      |     |        |

| Data Retention                            |             |                                                 | 10   |      |     | Years  |

| Flash Programming Write Cycles            |             |                                                 | 100k |      |     | Cycles |

| Word Programming Time                     | tprogword   |                                                 |      |      | 10  | μS     |

| Mass-Erase Time                           | tmasserase  |                                                 |      |      | 100 | ms     |

| Page-Erase Time                           | tpageerase  |                                                 |      |      | 6   | ms     |

| Flash-Read Current                        | IFLASHREAD  |                                                 |      | 3.37 | 4   | mA     |

| Flash-Write Current                       | IFLASHWRITE |                                                 |      |      | 2.7 | mA     |

| Flash-Erase Current                       | IFLASHERASE |                                                 |      |      | 1.2 | mA     |

| Data Flash                                |             |                                                 |      | •    |     |        |

| Data Retention                            |             |                                                 | 10   |      |     | Years  |

| Flash Programming Write Cycles            |             |                                                 | 100k |      |     | Cycles |

| Word Programming Time                     | tprogword   |                                                 |      |      | 10  | μS     |

| Mass-Erase Time                           | tmasserase  |                                                 |      |      | 40  | ms     |

| Page-Erase Time                           | tpageerase  |                                                 |      |      | 6   | ms     |

| Flash-Read Current                        | IFLASHREAD  |                                                 |      |      | 4   | mA     |

| Flash-Write Current                       | IFLASHWRITE |                                                 |      |      | 2.7 | mA     |

| Flash-Erase Current                       | IFLASHERASE |                                                 |      |      | 1.2 | mA     |

| Parameter                                | Symbol           | Test Conditions                                                               | Min | Тур  | Max  | Unit |

|------------------------------------------|------------------|-------------------------------------------------------------------------------|-----|------|------|------|

| OCD, SCC, SCD1, and SCD                  | 2 Current Protec | tion Thresholds                                                               | •   |      |      |      |

| OCD Detection Threshold                  | \\\              | Vcsp – Vcsn, extend range                                                     | -32 |      | -92  | \/   |

| Voltage Range                            | Vocd             | Vcsp - Vcsn, normal range                                                     | -2  |      | -32  | mV   |

| OCD Detection Threshold                  | 11/000           | Vcsp – Vcsn, extend range                                                     |     | -4   |      | m\/  |

| Voltage Program Step                     | ΔVOCD            | Vcsp – Vcsn, normal range                                                     |     | -2   |      | mV   |

| SCD1 Detection Threshold                 | VscD1            | VCSP - VCSN, extend range                                                     | -80 |      | -220 | mV   |

| Voltage Range                            | VSCD1            | VCSP - VCSN, normal range                                                     | -10 |      | -80  | IIIV |

| SCD1 Detection Threshold                 | ΔVSCD1           | VCSP – VCSN, extend range                                                     |     | -20  |      | mV   |

| Voltage Program Step                     | AVSCDI           | Vcsp - Vcsn, normal range                                                     |     | -10  |      | IIIV |

| SCD2 Detection Threshold                 | VscD2            | VCSP – VCSN, extend range                                                     | -80 |      | -220 | mV   |

| Voltage Range                            | VSCD2            | VCSP - VCSN, normal range                                                     | -10 |      | -80  | IIIV |

| SCD2 Detection Threshold                 | ΔVSCD2           | VCSP - VCSN, extend range                                                     |     | -20  | -    | mV   |

| Voltage Program Step                     | AVSCD2           | VCSP - VCSN, normal range                                                     |     | -10  | 1    | IIIV |

| SCC Detection Threshold                  | Vscc             | VCSP - VCSN, extend range                                                     | 80  | -    | 220  | mV   |

| Voltage Range                            | VSCC             | VCSP - VCSN, normal range                                                     | 10  |      | 80   |      |

| SCC Detection Threshold                  | ΔVscc            | V <sub>CSP</sub> – V <sub>CSN</sub> , extend range                            |     | 20   | 1    | mV   |

| Voltage Program Step                     | AVSCC            | VCSP - VCSN, normal range                                                     |     | 10   |      |      |

| OCD, SCC, SCD1, and SCD                  | 2 Current Protec | tion Timing                                                                   |     |      |      |      |

| OCD Detection Delay Time                 | tocd             |                                                                               | 1   | -    | 31   | ms   |

| OCD Detection Delay Time<br>Program Step | Δtocd            |                                                                               |     | 2    |      | ms   |

| CCD4 Detection Delevi Time               | <b>4</b>         | Extend delay time                                                             | 0   |      | 1850 |      |

| SCD1 Detection Delay Time                | tscD1            | Normal delay time                                                             | 0   |      | 915  | μS   |

| SCD1 Detection Delay Time                | Atoon            | Extend delay time                                                             |     | 121  |      |      |

| Program Step                             | ∆tSCD1           | Normal delay time                                                             |     | 61   |      | μS   |

| CCD2 Detection Delevi Time               | toops            | Extend delay time                                                             | 0   |      | 915  |      |

| SCD2 Detection Delay Time                | tSCD2            | Normal delay time                                                             | 0   |      | 458  | μS   |

| SCD2 Detection Delay Time                | 440000           | Extend delay time                                                             |     | 61   |      | _    |

| Program Step                             | ∆tSCD2           | Normal delay time                                                             |     | 30.5 |      | μS   |

| SCC Detection Delay Time                 | tscc             |                                                                               | 0   |      | 915  | μS   |

| SCC Detection Delay Time<br>Program Step | Δtscc            |                                                                               |     | 61   |      | μs   |

| Current Fault Delay Time<br>Accuracy     | tACC             | VCSP - VCSN = VT - 3mV for OCD, SCD1, and SC2, VCSP - VCSN = VT + 3mV for SCC |     |      | 160  | μs   |

| OCD, SCC, SCD1, and SCD                  | 2 Current Protec | tion Accuracy                                                                 | ı   | T    |      |      |

|                                          |                  | Setting  < 32mV                                                               | -1  |      | 1    |      |

| OCD Detection Accuracy                   | VOCD_ACC         | Setting  = 32mV to 64mV                                                       | -2  |      | 2    | mV   |

|                                          |                  | Setting  = 64mV to 92mV                                                       | -4  |      | 4    | 1    |

| Parameter                             | Symbol       | Test Conditions                   | Min   | Тур    | Max   | Unit |

|---------------------------------------|--------------|-----------------------------------|-------|--------|-------|------|

| SCD1, SCD2 Detection<br>Accuracy      | Vscd_acc     | Setting  < 40mV                   | -1    |        | 1     | mV   |

|                                       |              | Setting  = 40mV to 80mV           | -2    |        | 2     |      |

|                                       |              | Setting  = 80mV to 150mV          | -4    |        | 4     |      |

|                                       |              | Setting  > 150mV                  | -7    |        | 7     |      |

| SCC Detection Accuracy                | Vscc_acc     | Setting  < 40mV                   | -1    |        | 1     | mV   |

|                                       |              | Setting  = 40mV to 80mV           | -2    |        | 2     |      |

|                                       |              | Setting  = 80mV to 150mV          | -4    |        | 4     |      |

|                                       |              | Setting  > 150mV                  | -7    |        | 7     |      |

| Load Detection                        |              |                                   |       |        |       |      |

| Load Remove Threshold                 | VLD          | VPACK > VLD                       | 0.9   | 1      | 1.1   | V    |

| Internal Current from BAT to          |              |                                   | 9     | 10     | 11    | μΑ   |

|                                       | ISOURCE      |                                   | 18    | 20     | 22    |      |

| PACK for Load Detection               | ISOURCE      |                                   | 27    | 30     | 33    |      |

|                                       |              |                                   | 36    | 40     | 44    |      |

| Detection Delay Time                  | tDLY_LD      |                                   |       | 10     | 1     | ms   |

| Charger Detection                     |              |                                   |       |        |       |      |

| Charger Remove Threshold              | VCD          | VBAT > VPACK                      | 0.07  | 0.1    | 0.15  | V    |

| Detection Delay Time                  | tDLY_CD      |                                   |       | 2      |       | ms   |

| Low Frequency Oscillator              |              |                                   |       |        |       |      |

| Operating Frequency Low               | fosc_Low     |                                   |       | 262.14 | ŀ     | kHz  |

| Operating Accuracy Low                | ferr_low     |                                   | -2.5  | ±0.25  | 2.5   | %    |

| High Frequency Oscillator             |              |                                   |       |        |       |      |

| Operating Frequency High              | fosc_HIGH    |                                   |       | 4      |       | MHz  |

| Operating Accuracy High               | fERR_HIGH    |                                   | -10   |        | 10    | %    |

| Auxiliary LDO Power Suppl             | у            |                                   |       |        |       |      |

|                                       | Vout         |                                   | 3.14  | 3.30   | 3.47  |      |

|                                       |              |                                   | 2.85  | 3.00   | 3.15  |      |

| Programming Output<br>Voltage         |              | CL = 1μF                          | 2.38  | 2.50   | 2.63  | V    |

|                                       |              |                                   | 1.71  | 1.80   | 1.89  |      |

|                                       |              |                                   | 1.425 | 1.5    | 1.575 |      |

| Output Current                        | Гоит         | C <sub>L</sub> = 1μF              |       |        | 2     | mA   |

| The Time for Vout Ready               | trdy         | CL = 1μF                          |       |        | 1     | ms   |

| Output Short Circuit Current<br>Limit | ILIM_VOUT_SC | Vout = VSS, CL = 1μF              | 8     |        | 20    | mA   |

| SMBus, 100kHz                         |              |                                   |       |        |       |      |

| Clock Operating Frequency             | fsмв         | Slave mode, SMBC duty cycle = 50% | 10    |        | 100   | kHz  |

|                                       |              |                                   |       |        |       |      |

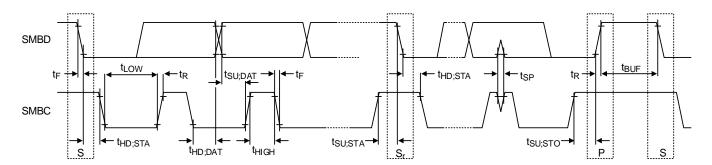

| Parameter                                  | Symbol    | Test Conditions                   | Min | Тур | Max  | Unit |

|--------------------------------------------|-----------|-----------------------------------|-----|-----|------|------|

| Bus Free Time STOP to START                | tBUF      |                                   | 4.7 |     |      | μS   |

| START Condition Hold Time                  | thd:start |                                   | 4.0 |     |      | μS   |

| Setup Repeated START                       | tsu:start |                                   | 4.7 |     |      | μS   |

| Setup Time STOP Condition                  | tsu:stop  |                                   | 4.0 |     |      | μS   |

| Data Hold Time                             | thd:dat   |                                   | 0   |     |      | ns   |

| Data Setup Time                            | tsu:dat   |                                   | 250 |     |      | ns   |

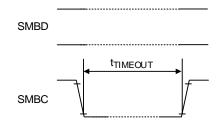

| Error Signal Detect Time                   | tтімеоит  |                                   | 25  |     | 35   | ms   |

| Low Period of the SMBC<br>Clock            | tLOW      |                                   | 4.7 |     |      | μS   |

| High Period of the SMBC<br>Clock           | thigh     |                                   | 4   |     |      | μS   |

| Clock Rise Time                            | tR        | 10% to 90%                        |     |     | 1000 | ns   |

| Clock Fall Time                            | tF        | 90% to 10%                        |     |     | 300  | ns   |

| Cumulative Clock Low Slave Extend Time     | tLOW_SEXT |                                   |     |     | 25   | ms   |

| Cumulative Clock Low<br>Master Extend Time | tLOW_MEXT |                                   |     |     | 10   | ms   |

| SMBus, 400kHz                              |           |                                   |     |     |      |      |

| Clock Operating Frequency                  | fsmb      | Slave mode, SMBC duty cycle = 50% |     |     | 400  | kHz  |

| Bus Free Time STOP to START                | tBUF      |                                   | 1.3 |     |      | μS   |

| START Condition Hold Time                  | thd:Start |                                   | 0.6 |     |      | μS   |

| Setup Repeated START                       | tsu:start |                                   | 0.6 |     |      | μS   |

| Setup Time STOP Condition                  | tsu:stop  |                                   | 0.6 |     |      | μS   |

| Data Hold Time                             | thd:dat   |                                   | 0   |     |      | ns   |

| Data Setup Time                            | tsu:dat   |                                   | 100 |     |      | ns   |

| Error Signal Detect Time                   | tтімеоит  |                                   | 25  |     | 35   | ms   |

| Low Period of the SMBC<br>Clock            | tLOW      |                                   | 1.3 |     |      | μS   |

| High Period of the SMBC<br>Clock           | tHIGH     |                                   | 0.6 |     |      | μS   |

| Clock Rise Time                            | tR        | 10% to 90%                        | 20  |     | 300  | ns   |

| Clock Fall Time                            | tF        | 90% to 10%                        | 20  |     | 300  | ns   |

| Cumulative Clock Low Slave Extend Time     | tLOW_SEXT |                                   |     |     | 25   | ms   |

| Cumulative Clock Low<br>Master Extend Time | tLOW_MEXT |                                   |     |     | 10   | ms   |

| SMBus, 1MHz                                | •         |                                   | •   | •   | •    |      |

| Clock Operating Frequency                  | fsmb      | Slave mode, SMBC duty cycle = 50% |     |     | 1    | MHz  |

**RT9440**

| Parameter                                  | Symbol    | Test Conditions | Min  | Тур | Max | Unit |

|--------------------------------------------|-----------|-----------------|------|-----|-----|------|

| Bus Free Time STOP to START                | tBUF      |                 | 0.5  |     |     | μS   |

| START Condition Hold Time                  | thd:start |                 | 0.26 |     |     | μS   |

| Setup Repeated START                       | tsu:start |                 | 0.26 |     |     | μS   |

| Setup Time STOP Condition                  | tsu:stop  |                 | 0.26 |     |     | μS   |

| Data Hold Time                             | thd:dat   |                 | 0    |     |     | ns   |

| Data Setup Time                            | tsu:dat   |                 | 50   |     |     | ns   |

| Error Signal Detect Time                   | tтімеоит  |                 | 25   |     | 35  | ms   |

| Low Period of the SMBC<br>Clock            | tLOW      |                 | 0.5  |     |     | μS   |

| High Period of the SMBC<br>Clock           | thigh     |                 | 0.26 |     |     | μS   |

| Clock Rise Time                            | tR        | 10% to 90%      |      |     | 120 | ns   |

| Clock Fall Time                            | tF        | 90% to 10%      | 20   |     | 120 | ns   |

| Cumulative Clock Low Slave Extend Time     | tLOW_SEXT |                 |      |     | 25  | ms   |

| Cumulative Clock Low<br>Master Extend Time | tLOW_MEXT |                 |      |     | 10  | ms   |

# 14 Timing Diagram

Figure 1. SMBus Timing Diagram

Figure 2. SMBus Timeout Condition

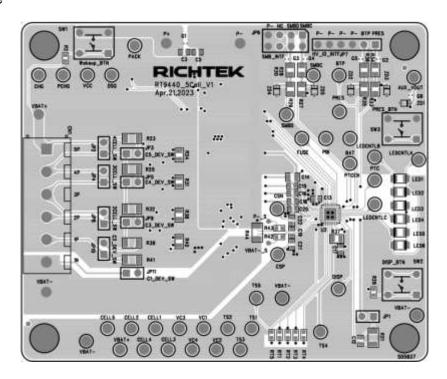

# 15 Typical Application Circuit

# 16 Typical Operating Characteristics

## 17 Application Information

#### (Note 6)

The RT9440 device provides a complete fuel gauging solution for 2-to-5 series cell battery pack applications. It also fully integrates cell balancing, protection, charger control, and authentication for 2-to-5 series cell battery packs.

#### 17.1 Fuel Gauge

The RT9440 uses the VGCS algorithm to calculate the state of charge in battery cells. The VGCS algorithm is a hybrid fuel gauge algorithm with voltage-based core (VoltaicGauge<sup>TM</sup>), iterating battery voltage and dynamic difference of battery voltage. Then it is optimized with current information to adjust the delta SOC and integrate it into the overall SOC. The VGCS algorithm also includes temperature and load compensation, and aging compensation functions, providing both short-term accurate and long-term stability in SOC results.

#### 17.2 Power Mode

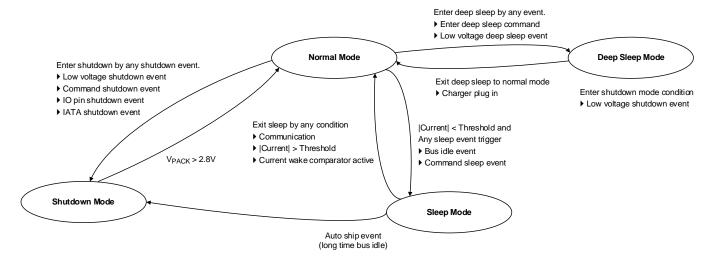

The RT9440 supports four power modes to decrease power usage.

- In normal mode, the RT9440 performs measurements, calculations, protection decisions, and data updates at 250ms intervals. Between these intervals, the RT9440 is in idle status to reduce power consumption.

- In sleep mode, the RT9440 performs measurements, calculations, protection decisions, and data updates at

adjustable intervals (default 5 second). Between these intervals, the RT9440 is in idle status to decrease power

usage. The RT9440 has a wake function that enables exit from sleep mode when current flow or failure is detected.

- In deep sleep mode, the RT9440 turns off all MOSFETs and hardware current protection, and executes measurements, calculations, and data updates at adjustable intervals (default 60 seconds). Between these intervals, the RT9440 is in idle status to reduce power consumption and turns off SMBus communication. The RT9440 has a wake function that enables exit from deep sleep mode when a charger is plugged in.

- In shutdown mode, the RT9440 is completely disabled.

Figure 3. Power Mode State Machine

#### 17.3 Measurement

The RT9440 supports voltage, current and temperature measurements.

The RT9440 uses internal ADC to measure voltage and updates the voltage every 0.25 seconds in the normal mode. This data is also used to calculate the VGCS gas gauging.

- Up to 5 cell voltage measurement

- Stack cell voltage

- Pack pin voltage

- High-side MOSFET drop voltage measurement

The RT9440 uses the CSP and CSN inputs to measure and calculate the battery charge and discharge current.

• Supports current measurement with  $0.5 m\Omega$  to  $10 m\Omega$  current sense resistance.

The RT9440 has an internal temperature sensor and inputs for up to 5 external temperature sensors.

- Supports up to 5 channels of external NTC temperature measurement.

- TS1, TS2, TS3, TS4, and TS5 can be optionally configured for general ADC measurement, with a measurement range of 0V to 3.3V.

- Internal temperature measurement.

TS1, TS2, TS3, TS4 and TS5 can be individually enabled and configured for cell or MOSFET temperature usage and use a different thermistor profile.

## 17.4 Primary (1<sup>st</sup> Level) Safety Features

The RT9440 supports a full coverage of battery and system protection features that can be easily configured. For detailed descriptions of each protection function, refer to the RT9440 Technical Reference Manual.

It includes two types of protection: hardware protection and software protection.

- · Hardware protection

- Overcurrent in discharge protection

- · Short circuit in charge protection

- · Short circuit in discharge protection with 2 levels

- Software protection

- · Cell overvoltage protection

- Cell undervoltage protection

- Overcurrent in charge protection in 2 levels

- Overcurrent in discharge protection in 2 levels

- · Over-temperature in charge protection

- Over-temperature in discharge protection

- Under-temperature in charge protection

- · Under-temperature in discharge protection

- Over-temperature MOSFET protection

- · Pre-charge timeout protection

- · Host watchdog timeout protection

- · Fast charge timeout protection

- Overcharge protection

- · Overcharging voltage protection

- · Overcharging current protection

- Over pre-charge current protection

Overcurrent protection by CHG+DSG MOSFET drop voltage

## 17.5 Secondary (2<sup>nd</sup> Level) Safety Features

The secondary safety features of the RT9440 can be used to indicate more serious faults via the FUSE pin. This pin is used to blow an in-line fuse and permanently disable the battery pack.

For detailed descriptions of each protection function, refer to the RT9440 Technical Reference Manual.

- Safety cell overvoltage permanent failure

- Safety cell undervoltage permanent failure

- · Safety overcurrent in charge permanent failure

- Safety overcurrent in discharge permanent failure

- Safety overtemperature cell permanent failure

- · Safety overtemperature MOSFET permanent failure

- · Cell balancing permanent failure

- Qmax imbalance permanent failure

- Capacity degradation permanent failure

- Voltage imbalance at rest permanent failure

- · Voltage imbalance active permanent failure

- Charge MOSFET permanent failure

- Discharge MOSFET permanent failure

- Fuse failure permanent failure

- AFE register permanent failure

- 2nd protection permanent failure

- PTC permanent failure

- · Open thermistor permanent failure

- · Program memory checksum permanent failure

- · Data memory permanent failure

- AFE communication permanent failure

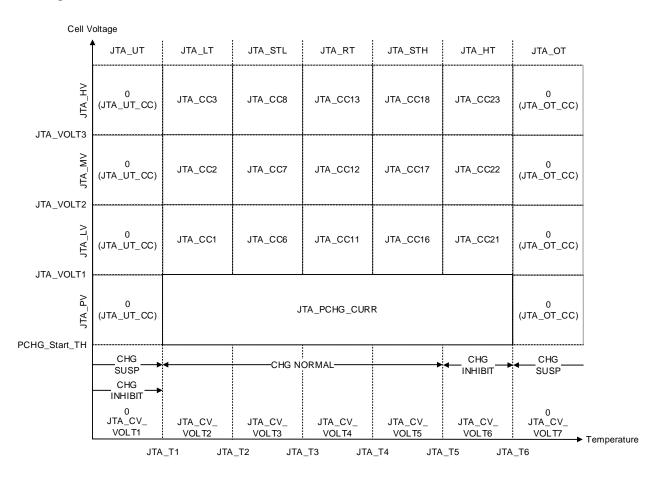

The RT9440 charge control features include:

- Supports JEITA temperature ranges and reports the charging voltage and the charging current according to the active temperature and voltage range

- 7-stage programmable temperature range

- 3-stage programmable voltage range

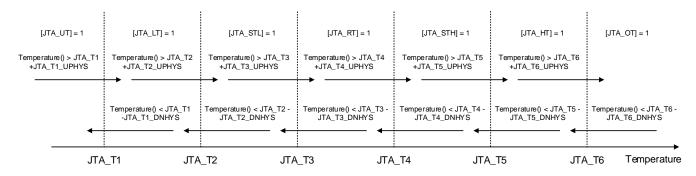

- · Bidirectional hysteresis for temperature and voltage

#### 17.6 **Charge Control**

Figure 4. JEITA Temperature and Voltage Range

Figure 5. Bidirectional Hysteresis

- Report the charging current and charging voltage after compensation to a smart charger using SMBus broadcasts.

- Report the compensated charging voltage for voltage drop of MOSFET.

- Report the compensated charging voltage due to degradation by temperature and voltage to prevent cell swelling.

- Report the compensated charging voltage and charging current due to degradation by cycle, SOH or runtime.

- Supports pre-charging and zero-voltage charging.

- Supports charge inhibit and charge suspend if battery pack temperature is out of temperature range.

- Reports charging fault and also indicates charge status via charge and discharge alarms.

#### 17.7 Cell Balancing Control

The RT9440 supports passive cell balancing with embedded bypass switches and can balance multiple cells simultaneously during charging or rest. The cell balance algorithm determines the capacity needed to be bypassed to balance of all cells. The RT9440 also supports voltage-base cell balancing. With up to 10mA bypass current using internal bypass switches, the device can achieve higher cell balance current by using an external cell balancing circuit.

#### 17.8 Auxiliary LDO Provides Two Features

The auxiliary LDO provides a configurable output voltage from 1.5V to 3.3V and delivers up to 6mA output current. It can drive the always-on circuit, such as the RTC power and it is also used for GPIO power source.

- The RT9440 can work in deep sleep mode to reduce quiescent but keep VOUT to drive always-on circuits (e.g., RTC).

- VOUT turns off when cell voltage is lower than configurable threshold to prevent over discharge, over-temperature, under-temperature, battery removal, or abnormal current consumption.

#### 17.9 Load Detection and Charger Detection

The load and charge detection feature stops the MOSFETs from toggling on and off continuously when there is a persistent faulty condition.

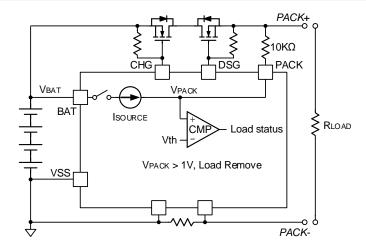

- Load detection can monitor the PACK pin voltage. If the PACK pin voltage is over 1V, the load is considered removed.

- The device integrates a source current to detect the PACK pin voltage. The current level can be configured from 10μA to 40μA.

For example, if the BAT voltage is 16V, the load equivalent resistance is  $30k\Omega$ , and the configured load detection source current is  $20\mu A$ :

- If the load is present, the PACK voltage is 0.8V (under 1V).

- If the load is removed, the PACK voltage is 16V (over 1V).

Figure 6. Load Detection

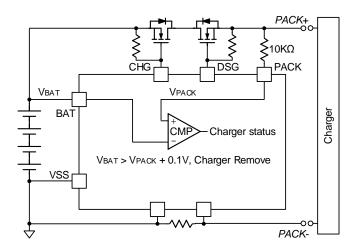

• Charger detection can compare the BAT pin voltage with the PACK pin voltage. If the differential voltage between the BAT pin voltage and the PACK pin voltage is over 0.1V, the charger is considered removed.

For example, if the BAT voltage is 16V and the charger CV is 17.6V:

- If the charger is present, the differential voltage between the BAT pin voltage and the PACK pin voltage is 1.6V.

- If the charger is removed, the differential voltage between the BAT pin voltage and the PACK pin voltage is 0.7V (body diode forward voltage).

Figure 7. Charger Detection

#### 17.10 Black Box Recorder

- Record the last three safety statuses to black box when permanent failure occurs.

- Update the lifetime log when a permanent failure occurs.

- Record additional three permanent failure statuses to black box after the first permanent failure occurs.

#### 17.11 Lifetime Data Log

The RT9440 supports lifetime logging of important battery data. The following data are updated every 10 hours if a difference is detected between values in RAM and data flash:

- Maximum and minimum cell voltages

- Maximum delta cell voltage

RICHTEK

- Maximum charge current

- Maximum discharge current

- Maximum average discharge current

- Maximum average discharge power

- Maximum and minimum cell temperature

- Maximum delta cell temperature

- Maximum and minimum internal sensor temperature

- Maximum MOSFET temperature

- Number of safety events occurrences and the last cycle of the occurrence

- Number of valid charge termination and the last cycle of the valid charge termination

- Number of Qmax updates and the last cycle of the Qmax updates

- Number of shutdown events

- Cell balancing time for each cell

- Total FW runtime and time spent in each temperature range.

## 17.12 Intel® Dynamic Battery Power Technology (DBPT V2.0)

The RT9440 supports DBPT V2.0 by providing the available max power and max current to prevent system reset or trigger termination voltage under peak loading.

#### 17.13 IATA Support

The RT9440 supports several commands and procedures to satisfy the IATA criteria when the battery pack is in shipping.

#### 17.14 LED Display

The RT9440 can drive up to 6-segment LED display for remaining capacity indication and/or a permanent failure code indication.

#### 17.15 FUSE Driver

The RT9440 can use FUSE driver to blow an in-line fuse and permanently disable the battery pack.

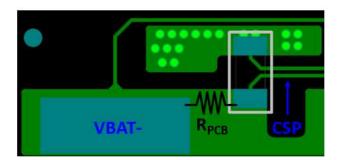

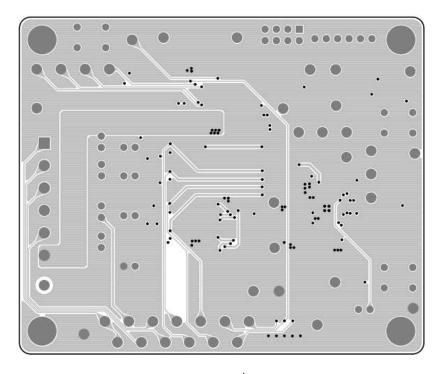

#### 17.16 PTC Permanent Failure