# 5A 1-4 Cell Buck-Boost Switching Battery Charger

### **General Description**

The RT9492 is a highly-integrated 5A Buck-Boost switch mode battery charge management and system power path management device for 1-4 cell Li-Ion and Li-polymer battery. The low impedance power path optimizes switch-mode operation efficiency, reduces battery charging time and extends battery life during discharging phase. The I<sup>2</sup>C serial interface with charging and system settings makes the device a truly flexible solution.

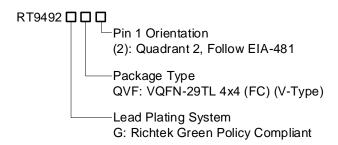

### **Ordering Information**

#### Note:

Richtek products are Richtek Green Policy Compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

## **Applications**

- Smart Phone/Tablet/Chrome Book

- Drone

- Portable Device and Accessory

#### **Features**

- High Efficiency, 750kHz/1MHz/1.5MHz

Programmable Frequencies, Synchronous

Switch-Mode Buck-Boost Charger

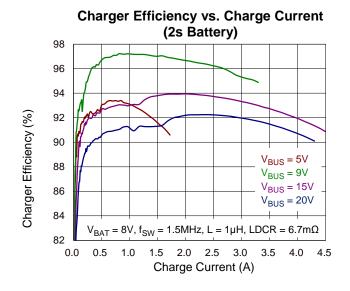

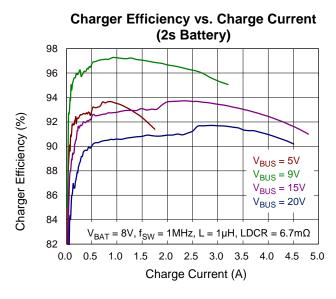

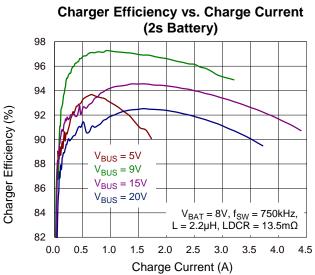

- ► 96.7% Charge Efficiency at 2A with 9V Input and 8V Battery

- ▶ Support 3.6V to 24V Input Voltage Range

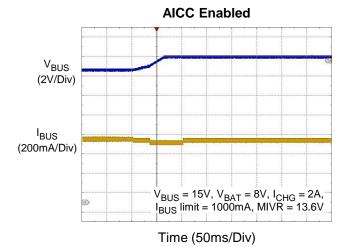

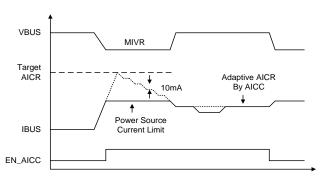

- ► Average Input Current Regulation (AICR)

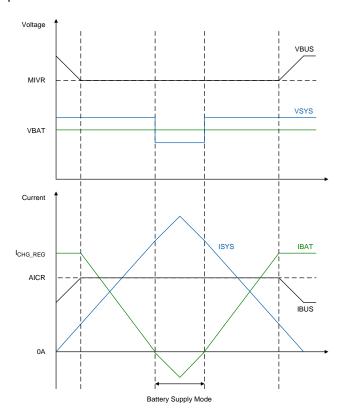

- ► Minimum Input Voltage Regulation (MIVR)

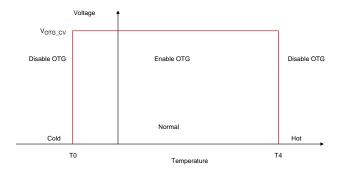

- Supports USB On-The-Go (OTG)

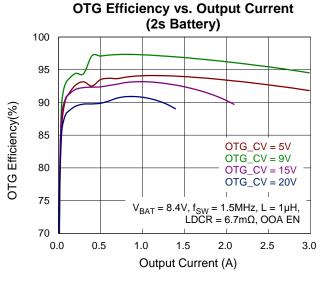

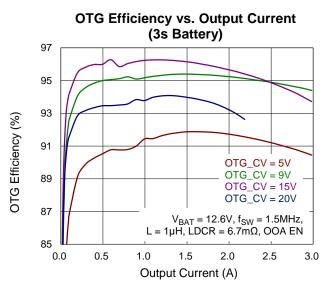

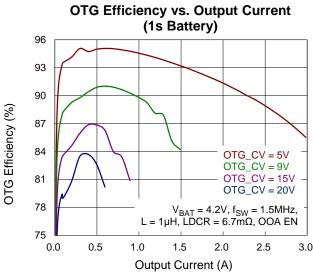

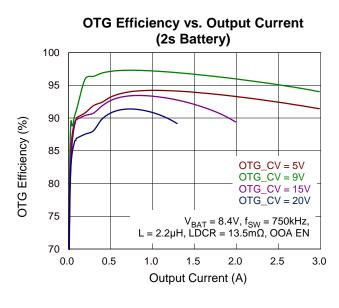

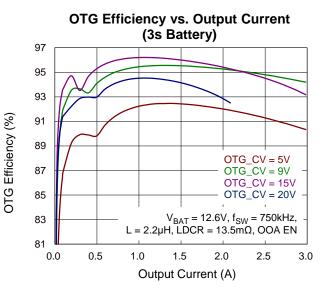

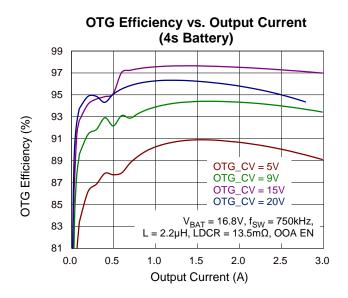

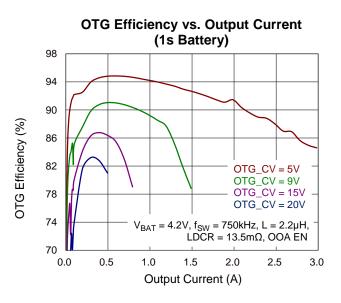

- ▶ 93.4% OTG Efficiency at 2A with 8.4V Battery and 5V Output

- ► Output Voltage with 10mV Resolution to Support USB-PD

- ► BAT Current Limit Regulation (BCLR)

- Supports Dual Input Selection

- Supports BC1.2, Host Mode and FRS/Seamless

- Low Battery Quiescent Current

- High Accuracy for Charger CV and ICHG

- Protection

- ► Over-Temperature Protection (OTP)

- ▶ Junction Thermal Regulation (JTR)

- ▶ Input Protection (VAC OVP/VBUS OVP/OCP)

- ▶ Battery Overvoltage Protection (VBAT OVP)

- ► System Voltage Protection (VSYS OVP/UVP)

- ► System Over-Load Protection (VSYS OLP)

- ► Cycle-by-Cycle Overcurrent Protection (OCP)

- ▶ OTG Low Battery Protection (OTG LBP)

- ► OTG Voltage Protection (OTG OVP/UVP)

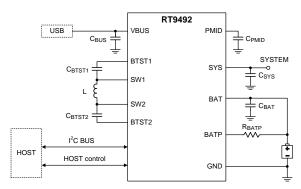

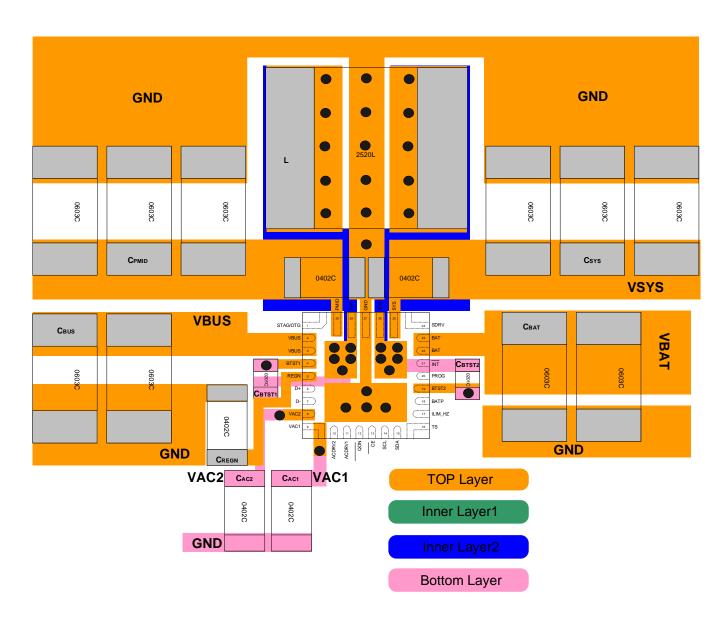

## **Simplified Application Circuit**

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

RICHTEK

is a registered trademark of Richtek Technology Corporation.

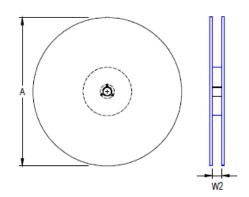

# **Marking Information**

GT=: Product Code YMDNN: Date Code

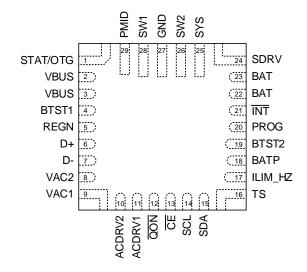

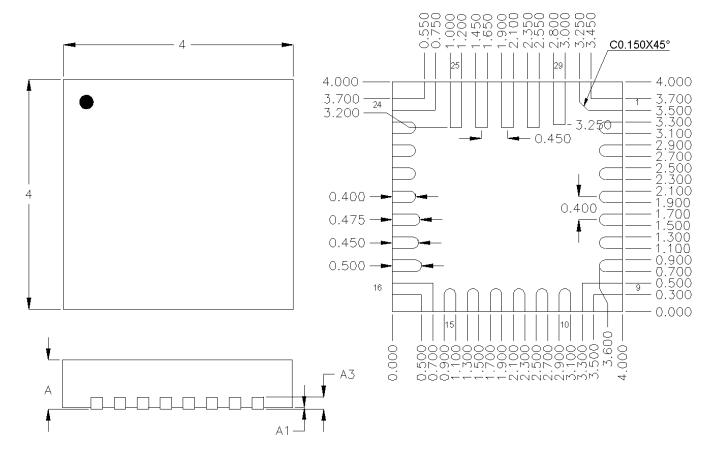

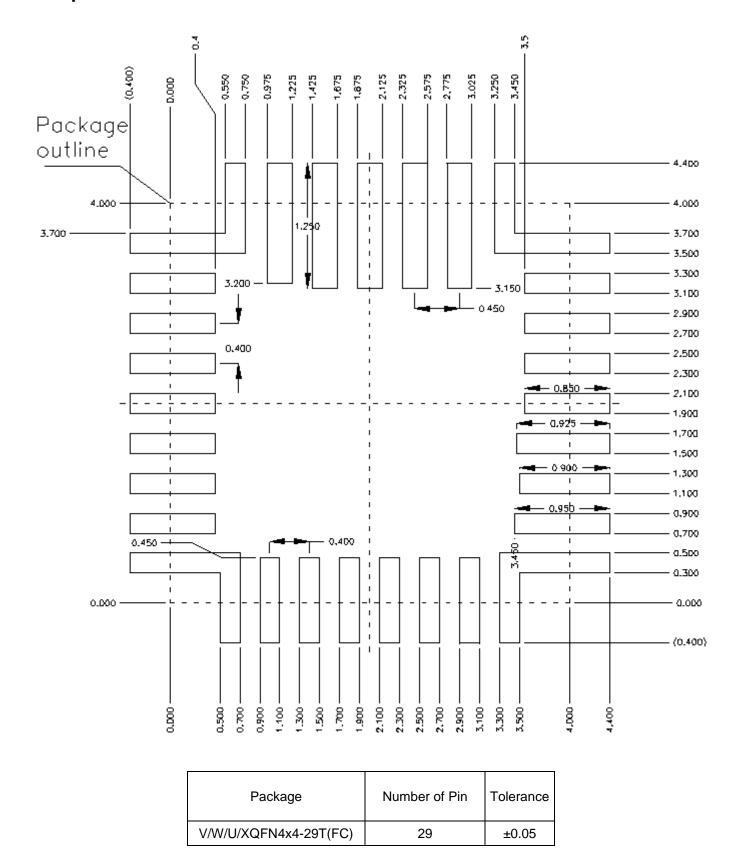

# **Pin Configuration**

(TOP VIEW)

VQFN-29TL 4x4 (FC)

## **Device Comparison**

| Part Number             | RT9490                      | RT9492                      |

|-------------------------|-----------------------------|-----------------------------|

| DEVICE_ID, REG0x48[6:3] | 1100                        | 1110                        |

| VAC_OVP, REG0x10[5:4]   | 7V (Default), 12V, 22V, 26V | 7V, 12V, 18V, 26V (Default) |

| PG Pin                  | Yes                         | NA                          |

| IBAT Pin                | Yes                         | NA                          |

| BATN Pin                | Yes                         | NA                          |

| ADC                     | Yes                         | NA                          |

| Package                 | WL-CSP-56B 2.93x3.46 (BSC)  | VQFN-29TL 4x4 (FC)          |

# **Functional Pin Description**

| Pin No. | Pin Name | I/O | Pin Function                                                                                                                                                                                                                                                                                 |

|---------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | STAT/OTG | DIO | Open-drain charger status output. Connect the STAT pin to a logic rail via $2.2k\Omega$ to $10k\Omega$ resistor. The STAT pin indicates charger status. Open-drain OTG mode enable control input. Active high. Connect the OTG pin to a logic rail via $2.2k\Omega$ to $10k\Omega$ resistor. |

| 2, 3    | VBUS     | Р   | Charger input voltage. The internal current sensing circuit is connected between VBUS and PMID. Connect two $10\mu F$ capacitors from VBUS to GND and place as close as possible to VBUS.                                                                                                    |

| 4       | BTST1    | Р   | The high-side switching MOSFET (Q1) driver positive supply. Internally, the BTST1 is connected to the cathode of the bootstrap diode. Connect the 47nF bootstrap capacitor from BTST1 to SW1.                                                                                                |

DS9492-01

| Pin No. | Pin Name | I/O | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5       | REGN     | Р   | PWM low-side driver and internal supply output. Internally, REGN is connected to the anode of the bootstrap diode. Connect a $4.7\mu F$ capacitor from REGN to GND. The capacitor should be placed close to the IC. REGN must be used only for RT9492 relative functions.                                                                                                                                                                                                                                                      |

| 6       | D+       | AIO | Positive line of the USB data line pair. D+/D- based USB host/charging port detection. The detection includes data contact detection (DCD), primary, secondary detection in BC1.2 and manual control mode.                                                                                                                                                                                                                                                                                                                     |

| 7       | D-       | AIO | Negative line of the USB data line pair. D+/D- based USB host/charging port detection. The detection includes data contact detection (DCD), primary, secondary detection in BC1.2 and manual control mode.                                                                                                                                                                                                                                                                                                                     |

| 8       | VAC2     | AI  | VAC2 voltage sensing. When a voltage on VAC2 is above VAC2_UVLO, it represents input source plug in on port2. When there is no external AC-RBFET2, the VAC2 must connect to VBUS                                                                                                                                                                                                                                                                                                                                               |

| 9       | VAC1     | AI  | VAC1 voltage sensing. When a voltage on VAC1 is above VAC1_UVLO, it represents input source plug in on port1. When there is no external AC-RBFET1, the VAC1 must connect to VBUS                                                                                                                                                                                                                                                                                                                                               |

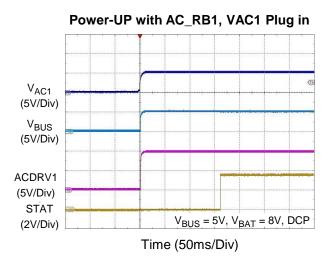

| 10      | ACDRV2   | Р   | External AC-RB N-channel FET gate driver output. The ACDRV2 is connected to external AC-RBFET2, the charger turns on AC-RBFET2 by increasing ACDRV2 voltage 5V above the AC-RBFET2 drain when the turn on condition is valid. When there is no external AC-RBFET2, the ACDRV2 must connect to GND.                                                                                                                                                                                                                             |

| 11      | ACDRV1   | Р   | External AC-RB N-channel FET gate driver output. The ACDRV1 is connected to external AC-RBFET1, the charger turns on AC-RBFET1 by increasing ACDRV1 voltage 5V above the AC-RBFET1 drain when the turn on condition is valid. When there is no external AC-RBFET1, the ACDRV1 must connect to GND.                                                                                                                                                                                                                             |

| 12      | QON      | DI  | Ship FET control input. When the device is in ship mode, a logic low duration with tQON_EXIT_SHIP_DLY turns on Ship FET to exit ship mode. A logic low duration with tQON_RST turns off the ship FET and stop converter switching for tsys_RST and resume to provide system reset. Pull-High to internal bias circuit via $200 \text{k}\Omega$ resistor.                                                                                                                                                                       |

| 13      | CE       | DI  | Charge enable pin. Active low. When this pin is driven low and REG_CHG_EN = 1, battery charging is enabled. Do NOT leave this pin floating.                                                                                                                                                                                                                                                                                                                                                                                    |

| 14      | SCL      | DI  | $I^2$ C interface clock. Connect SCL to the logic rail through a 10kΩ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15      | SDA      | DIO | $I^2C$ interface clock. Connect SDA to the logic rail through a $10k\Omega$ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

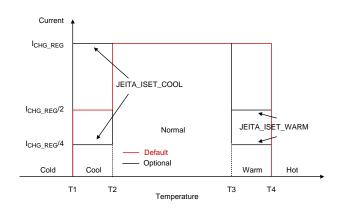

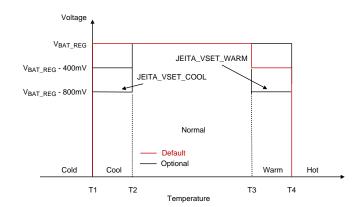

| 16      | TS       | AI  | Temperature qualification voltage input to support JEITA profile. Connect a negative temperature coefficient thermistor (103AT). Program temperature window with a resistor divider from REGN to TS to GND. The resistors used for resistor divider recommend 1% resistance tolerance. Charge suspends when TS pin voltage is out of range. When TS pin is not used, connect a $10 k\Omega$ resistor from REGN to TS and a $10 k\Omega$ resistor from TS to GND.                                                               |

| 17      | ILIM_HZ  | AI  | Input current limit setting and HZ mode control. A resistor divider is connected to ILIM_HZ pin by pull up resistors from REGN to GND. The pin voltage is calculated as VILIM_HZ = 1V + $800 \text{m}\Omega$ x ILIM, where ILIM is target input current limit. The input current limit for charger is the lower setting between ILIM_HZ and AICR register. When the pin voltage is below 0.75V, the buck-boost converter stops switching and REGN on. When the pin voltage is higher than 1V, the converter resumes switching. |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9492-01 July 2023 www.richtek.com

| Pin No. | Pin Name | I/O | Pin Function                                                                                                                                                                                                                                                       |

|---------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18      | ВАТР     | Al  | Positive battery voltage sensing. Connect to the positive terminal of battery pack. It is recommended to place $100\Omega$ series resistor between BATP and the positive terminal of battery pack.                                                                 |

| 19      | BTST2    | Р   | The high-side switching MOSFET (Q4) driver positive supply. Internally, the BTST2 is connected to the cathode of the bootstrap diode. Connect the 47nF bootstrap capacitor from BTST2 to SW2.                                                                      |

| 20      | PROG     | AI  | Charger POR default setting program. A resistor is connected from PROG to GND to set battery cells for default charging profile and switching frequency. The resistor connected to PROG is recommended to be 1% or 2% resistance tolerance.                        |

| 21      | INT      | DO  | Open-drain interrupt output. Active low. Connect the $\overline{\text{INT}}$ to a logic rail through $10\text{k}\Omega$ resistor. The $\overline{\text{INT}}$ pin sends active low pulse to host to report charger device status and fault.                        |

| 22, 23  | BAT      | Р   | Battery connection point to the positive terminal of the battery pack. The internal current sensing circuit is connected between SYS and BAT. Connect two $10\mu F$ capacitors from BAT to GND and place as close as possible to BAT.                              |

| 24      | SDRV     | Р   | External Ship N-channel FET gate driver output. The SDRV is connected to external ship FET, the SDRV is always turned off when in ship or shutdown mode. Without using ship FET, must connect a 1nF/50V capacitor from SDRV to GND.                                |

| 25      | SYS      | Р   | Charger output connection point. Connected to the drain of high-side switching MOSFET (Q4) and the internal current sensing circuit between SYS and BAT. Connect five $10\mu F$ and a $0.1\mu F$ capacitors from SYS to GND and place as close as possible to SYS. |

| 26      | SW2      | Р   | Switching node two connecting to output inductor. Internally SW2 is connected to the drain of the low-side switching MOSFET (Q3) and the source of the high-side switching MOSFET (Q4).                                                                            |

| 27      | GND      | Р   | Power Ground                                                                                                                                                                                                                                                       |

| 28      | SW1      | Р   | Switching node one connecting to output inductor. Internally SW1 is connected to the source of the high-side switching MOSFET (Q1) and the drain of the low-side switching MOSFET (Q2).                                                                            |

| 29      | PMID     | Р   | Connected to the drain of high-side switching MOSFET (Q1). Connect three $10\mu F$ and a $0.1\mu F$ capacitors from PMID to GND and place as close as possible to PMID.                                                                                            |

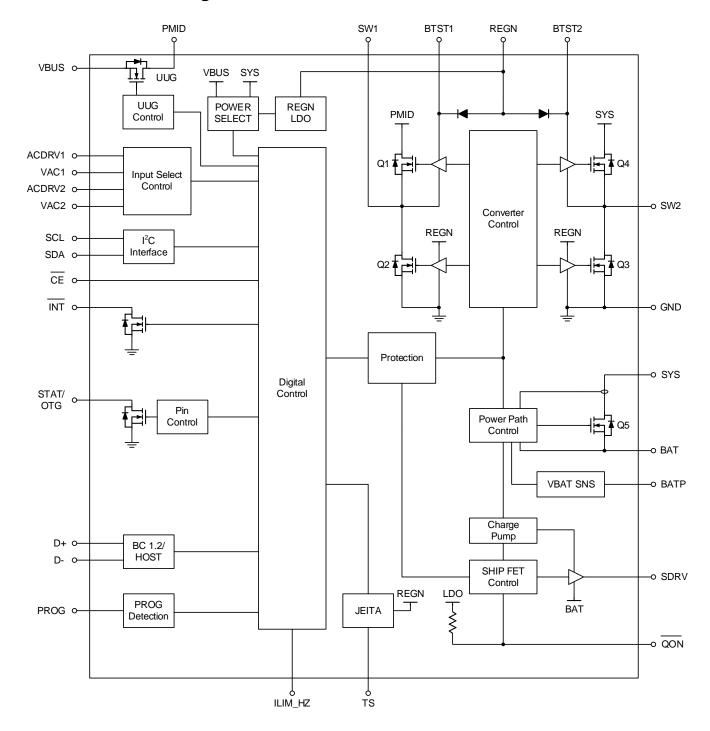

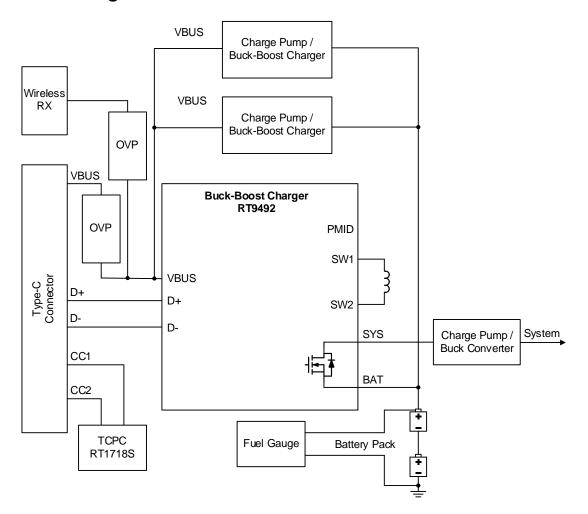

## **Functional Block Diagram**

# System Block Diagram

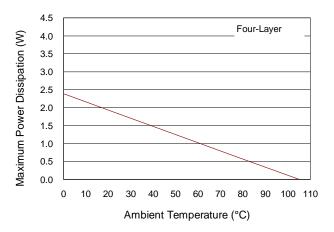

# **Absolute Maximum Ratings** (Note 1) • Supply Pin Voltage, VBUS ----- -2V to 30V • Terminal Pin Voltage, ACDRV1, ACDRV2, BTST1 ------ -0.3V to 32V • Voltage Sense Pin Voltage, BATP ----- -0.3V to 20V Power Dissipation, PD @ TA = 25°C VQFN-29TL 4x4 (FC) ------ 2.38W • Package Thermal Resistance (Note 2) VQFN-29TL 4x4 (FC), θJA ------ 44°C/W VQFN-29TL 4x4 (FC), θJC ----- 3.6°C/W • Lead Temperature (Soldering, 10 sec.)------ 260°C • Junction Temperature ------ 150°C • Storage Temperature Range ----- -55°C to 150°C ESD Susceptibility (Note 3) HBM (Human Body Model) ------ 2kV **Recommended Operating Conditions** (Note 4) • Voltage Sense Pin Voltage, VAC1, VAC2----- 3.6V to 24V • Supply Input Voltage Range, VBUS ----- 3.6V to 24V • Maximum Input Current, IBUS ------ 3.3A • Maximum Input Current, IOTG ----- 3.32A • Maximum Output Current (SW2), ISYS (Note 5)------ 5A • Maximum Battery Voltage, VBAT ----- 18.8V • Maximum Charge Current, IBAT ----- 5A • Maximum Discharge Current, IBAT------ 10A

July 2023

DS9492-01

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

## **Electrical Characteristics**

$(V_{BUS\_UVLO} < V_{BUS} < V_{BUS\_OVP}, T_A = 25^{\circ}C, unless otherwise specified)$  (Note 6)

| Parameter                                                                              | Symbol      | Test Conditions                                                                                          | Min  | Тур | Max  | Unit |

|----------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------|------|-----|------|------|

| Quiescent Current                                                                      |             |                                                                                                          |      | •   |      |      |

| Battery Discharge<br>Current (BATP) in Ship<br>Mode                                    | IQ_BAT_OFF  | BATP = 8V, No VBUS, I <sup>2</sup> C<br>enabled, SYS no load, in ship<br>mode, measure IBAT              |      | 2.5 | 6    | μА   |

| Battery Discharge<br>Current (BATP) in<br>Shutdown Mode                                | ISD_BAT_OFF | BATP = 8V, No VBUS, I <sup>2</sup> C disable, SYS no load, in shutdown mode, measure IBAT                |      | 0.6 | 0.7  | μА   |

| Battery Discharge<br>Current (BATP, BAT) in<br>the Battery Only Mode,<br>Q5 is Enabled | IQ_BAT_ON   | VBAT = 8V, No VBUS, Q5 is enabled, I <sup>2</sup> C enabled, SYS no load, measure IBAT                   |      | 18  | 23   | μΑ   |

| Input Supply Current (VAC) in HZ mode                                                  | IVAC_HZ     | VAC = 5V, HZ mode, no battery, ACDRV enable                                                              |      | 500 | 550  | μА   |

| Input Supply Current (VBUS) in HZ mode                                                 | IVBUS_HZ    | VBUS = 5V, HZ mode, no battery, ACDRV disable                                                            |      | 354 | 400  | μА   |

| Input Supply Current                                                                   | love ov     | VBUS = 15V, VBAT = 8V,<br>charge disabled, converter<br>switching, ISYS = 0A, OOA<br>disabled            |      | 3   |      | - mA |

| (VBUS)                                                                                 | IBUS_SW     | V <sub>BUS</sub> = 15V, VBAT = 8V,<br>charge disabled, converter<br>switching, ISYS = 0A, OOA<br>enable  |      | 5   |      | IIIA |

| Battery Discharge                                                                      | IBAT_OTG    | VBAT = 8V, VOTG = 5V, OTG<br>mode enabled, converter<br>switching, IBUS = 0A, OOA<br>disabled            |      | 2   |      |      |

| Current (BATP, BAT) in OTG Mode                                                        |             | V <sub>BAT</sub> = 8V, VOTG = 5V, OTG<br>mode enabled, converter<br>switching, IBUS = 0A, OOA<br>enabled |      | 5   |      | - mA |

| VAC, VBUS and BAT Pov                                                                  | wer         |                                                                                                          |      |     |      |      |

| VAC rising threshold to Turn On the ACDRV                                              | VVAC_RISE   | VAC rising until ACFET turn on,<br>measure VAC, VBUS,<br>ACDRV1 and ACDRV2                               |      | 3.4 | 3.5  | V    |

| VAC falling threshold to<br>Turn Off the ACDRV                                         | VVAC_FALL   | V <sub>AC</sub> falling until ACFET turn off,<br>measure VAC, VBUS,<br>ACDRV1 and ACDRV2                 | 3    | 3.2 |      | V    |

| VBUS Operating Range                                                                   | VBUS_OP     | VBUS rising                                                                                              | 3.6  |     | 24   | V    |

| VBUS Rising for Active I <sup>2</sup> C, No Battery                                    | Vp.10 157 0 | VBUS only, VBUS rising until I <sup>2</sup> C can communicate                                            | 3.45 | 3.6 | 3.75 | V    |

| VBUS Falling to Turn Off I <sup>2</sup> C, No Battery                                  | VBUS_UVLO   | VBUS only, VBUS falling until I <sup>2</sup> C can communicate                                           | 2.3  | 2.4 | 2.6  | V    |

| VBUS Rising Threshold to Start Switching                                               | VVBUS_RISE  | VBUS rising                                                                                              | 3.45 | 3.6 | 3.75 | V    |

DS9492-01

| Parameter                                                | Symbol        | Test Conditions                                                 | Min     | Тур              | Max  | Unit |

|----------------------------------------------------------|---------------|-----------------------------------------------------------------|---------|------------------|------|------|

| VBUS Falling Threshold to Turn off REGN                  | VBUS_FALL     | VBUS falling                                                    | 3.03    | 3.2              | 3.3  | V    |

| VAC 26V Overvoltage<br>Rising Threshold                  |               | VAC rising, VAC_OVP[1:0] = 00, for both VAC1 and VAC2           | 25.2    | 26               | 26.8 |      |

| VAC 26V Overvoltage Falling Threshold                    |               | VAC falling, VAC_OVP[1:0] = 00, for both VAC1 and VAC2          | 24.4    | 25.2             | 26   |      |

| VAC 18V Overvoltage rising threshold                     |               | VAC rising, VAC_OVP[1:0] = 01, for both VAC1 and VAC2           | 17.4    | 18               | 18.6 |      |

| VAC 18V Overvoltage falling threshold                    | V. 5. 5. 7    | VAC falling, VAC_OVP[1:0] = 01, for both VAC1 and VAC2          | 16.9    | 17.5             | 18.1 | .,   |

| VAC 12V Overvoltage<br>Rising Threshold                  | VAC_OVP       | VAC rising, VAC_OVP[1:0] = 10, for both VAC1 and VAC2           | 11.6    | 12               | 12.4 | V    |

| VAC 12V Overvoltage Falling Threshold                    |               | VAC falling, VAC_OVP[1:0] = 10, for both VAC1 and VAC2          | 11.2    | 11.6             | 12   |      |

| VAC 7V Overvoltage<br>Rising Threshold                   |               | VAC rising, VAC_OVP[1:0] = 11, for both VAC1 and VAC2           | 6.6     | 7                | 7.4  |      |

| VAC 7V Overvoltage Falling Threshold                     |               | VAC falling, VAC_OVP[1:0] = 11, for both VAC1 and VAC2          | 6.5     | 6.8              | 7.1  |      |

| VBUS Overvoltage<br>Rising Threshold                     | V             | VBUS rising                                                     | 24      | 25               | 26.2 |      |

| VBUS Overvoltage<br>Falling Threshold                    | VBUS_OVP      | VBUS falling                                                    | 23      | 24               | 24.8 | V    |

| IBUS Overcurrent Rising Threshold                        | IBUS_OCP      | IBUS rising                                                     |         | 8                |      | Α    |

| BAT for turn on Q5 and Active I <sup>2</sup> C           | V             | VBAT rising                                                     | 2.4     | 2.6              | 2.7  |      |

| BAT for turn off Q5 and I <sup>2</sup> C                 | VBAT_UVLO     | VBAT falling                                                    | 2.2     | 2.4              | 2.5  | V    |

| BATP for turn on Ship<br>FET and Active I <sup>2</sup> C | V             | VBATP rising                                                    | 3.3     | 3.4              | 3.5  |      |

| BATP for turn off I <sup>2</sup> C and Ship FET          | VBATP_UVLO    | VBATP falling                                                   | 2.2     | 2.4              | 2.5  | V    |

| Bad Adapter Detection Falling Threshold                  | VBUS_MIN      | V <sub>BUS</sub> falling                                        | 3.3     | 3.4              | 3.5  | V    |

| Bad Adapter Detection<br>Hysteresis                      | VBUS_MIN_HYS  | V <sub>B</sub> U <sub>S</sub> rising                            | 140     | 200              | 250  | mV   |

| Bad Adapter Detection<br>Sink Source                     | RBADSRC       | Sink source from V <sub>BUS</sub> to GND, V <sub>BUS</sub> = 5V |         | 1.1              |      | kΩ   |

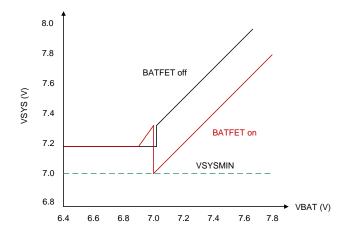

| Power Path                                               |               |                                                                 | ·       |                  |      |      |

| SYS Minimum<br>Regulation Voltage<br>Range               | Vsysmin_range | VSYSMIN regulation range, measured on SYS                       | 2.5     |                  | 16   | V    |

| SYS Minimum<br>Regulation Voltage Step                   | VSYSMIN_STEP  |                                                                 |         | 250              |      | mV   |

| SYS Minimum<br>Regulation Voltage                        | Vsysmin       | VBAT < VSYSMIN, Q5 disabled/<br>enable                          | Vsysmin | VSYSMIN<br>+ 0.2 |      | V    |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9492-01 July 2023 www.richtek.com

| Parameter                                     | Symbol         | Test Conditions                                                                                      | Min   | Тур  | Max   | Unit |

|-----------------------------------------------|----------------|------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| SYS Minimum<br>Regulation Voltage<br>Accuracy | Vsysmin_acc    |                                                                                                      | -2    |      | 2     | %    |

| SYS Regulation Voltage<br>Range               | Vsysreg_range  |                                                                                                      | 3.3   |      | 19.1  | ٧    |

|                                               |                | VBAT = 16.8V, VBAT > VSYSMIN,<br>Q5 disabled                                                         | 16.9  | 17.1 | 17.3  | ٧    |

| OVO Describitos Vallassa                      | Mariana        | V <sub>BA</sub> T =12.6V, V <sub>BAT</sub> > V <sub>SYSMIN</sub> , Q5 disabled                       | 12.72 | 12.9 | 13.14 | V    |

| SYS Regulation Voltage                        | Vsysreg        | VBAT = 8.4V, VBAT > VSYSMIN,<br>Q5 disabled                                                          | 8.53  | 8.7  | 8.87  | ٧    |

|                                               |                | VBAT = 4.2V, VBAT > VSYSMIN,<br>Q5 disabled                                                          | 4.36  | 4.5  | 4.65  | V    |

| VSYS Overvoltage<br>Rising Threshold          | Vsys_ovp       | As a percentage of the system regulation voltage, the converter stops switching when Vsys rises      | 105.5 | 110  | 112.5 | 0,   |

| VSYS Overvoltage<br>Falling Threshold         |                | As a percentage of the system regulation voltage, the converter re-start switching when Vsys falling | 95.5  | 100  | 102.5 | %    |

| VSYS Overvoltage Sink<br>Source               | Rsys_ovp       | Sink source from Vsys to GND                                                                         |       | 0.85 |       | kΩ   |

| VSYS Short Voltage<br>Falling Threshold       | Vsys_short     | VSYS falling                                                                                         | 2.1   | 2.2  | 2.3   | V    |

| Battery Charger                               |                |                                                                                                      |       |      |       |      |

| Charge Voltage Range                          | VBAT_REG_RANGE |                                                                                                      | 3     |      | 18.8  | V    |

| Charge Voltage Step                           | VBAT_REG_STEP  |                                                                                                      |       | 10   |       | mV   |

|                                               |                | VBAT_REG = 4.2V                                                                                      | -0.3  |      | 0.3   |      |

| Charge Voltage Setting                        |                | VBAT_REG = 8.4V                                                                                      | -0.3  |      | 0.3   | 0/   |

| Accuracy                                      | VBAT_REG_ACC   | VBAT_REG = 12.6V                                                                                     | -0.3  |      | 0.3   | %    |

|                                               |                | VBAT_REG = 16.8V                                                                                     | -0.5  |      | 0.5   |      |

| Charge Current<br>Regulation Range            | ICHG_REG_RANGE |                                                                                                      | 150   |      | 5000  | mA   |

| Charge Current<br>Regulation Step             | ICHG_REG_STEP  |                                                                                                      |       | 10   |       | mA   |

|                                               |                | ICHG_REG = 2A,<br>VSYS_MIN = 7V, VBAT = 8V                                                           | -3.5  |      | 3.5   | %    |

| Charge Current<br>Regulation Accuracy         | ICHG_REG_ACC   | ICHG_REG = 1A,<br>VSYS_MIN = 7V, VBAT = 8V                                                           | -4    |      | 4     |      |

|                                               |                | ICHG_REG = 0.5A,<br>VSYS_MIN = 7V, VBAT = 8V                                                         | -7.5  |      | 7.5   |      |

| Parameter                                 | Symbol                | Test Conditions                                                     | Min  | Тур  | Max  | Unit |

|-------------------------------------------|-----------------------|---------------------------------------------------------------------|------|------|------|------|

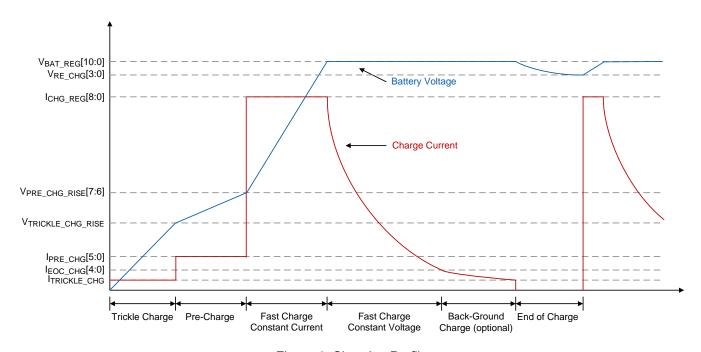

|                                           |                       | VPRE_CHG = 15% x VBAT_REG,<br>Pre-charge to Fast-charge             | 13   | 15   | 17   |      |

|                                           |                       | VPRE_CHG = 62% x VBAT_REG,<br>Pre-charge to Fast-charge             | 60.5 | 62   | 63.5 |      |

| Pre-Charge Rising<br>Threshold            | VPRE_CHG_RISE         | VPRE_CHG = 66.5% x VBAT_REG, Pre-charge to Fast-charge              | 65   | 66.5 | 68   | %    |

|                                           |                       | VPRE_CHG = 71.5% x<br>VBAT_REG, Pre-charge to Fast-<br>charge       | 70   | 71.5 | 73   |      |

| Pre-Charge Hysteresis                     | VPRE_CHG_HYS          | Fast-charge to Pre-charge                                           |      | 1.5  |      | %    |

| Pre-Charge Current<br>Range               | IPRE_CHG_RANGE        | Default = 120mA                                                     | 120  |      | 2000 | mA   |

| Pre-Charge Current Step                   | IPRE_CHG_STEP         |                                                                     |      | 40   |      | mA   |

|                                           |                       | IPRE_CHG = 480mA,<br>VSYS_MIN = 7V, VBAT = 6.5V                     | -7.5 |      | 7.5  |      |

| Pre-Charge Accuracy                       | IPRE_CHG_ACC          | IPRE_CHG = 200mA,<br>VSYS_MIN = 7V, VBAT = 6.5V                     | -15  |      | 15   | %    |

|                                           |                       | IPRE_CHG = 120mA,<br>VSYS_MIN = 7V, VBAT = 6.5V                     | -30  |      | 30   |      |

| End-Of-Charge Current Range               | IEOC_CHG_RANGE        | Default = 200mA                                                     | 120  |      | 1000 | mA   |

| End-Of-Charge Current<br>Step             | IEOC_CHG_STEP         |                                                                     |      | 40   |      | mA   |

|                                           |                       | IEOC_CHG = 200mA,<br>DIS_EOC_FCCM = 0<br>VBUS = 5V/15V, VBAT = 8.4V | -15  |      | 15   |      |

| End-Of-Charge Accuracy (Note 7)           | IEOC_CHG_ACC          | IEOC_CHG = 480mA,<br>DIS_EOC_FCCM = 0<br>VBUS = 5V/15V, VBAT = 8.4V | -13  |      | 13   | %    |

|                                           |                       | IEOC_CHG = 200mA,<br>DIS_EOC_FCCM = 1<br>VBUS = 5V/15V, VBAT = 8.4V |      |      | 5    |      |

| Trickle-Charge Falling<br>Threshold       | VTRICKLE_CHG_<br>FALL | VBAT falling                                                        | 1.8  | 2    | 2.2  | V    |

| Trickle-Charge Rising<br>Threshold        | VTRICKLE_CHG_<br>RISE | VBAT rising                                                         | 2.05 | 2.25 | 2.45 | ٧    |

| Trickle-Charge Current                    | ITRICKLE_CHG          | VBAT < VTRICKLE_CHG_RISE                                            | 80   | 100  | 120  | mA   |

| Re-Charge Threshold                       | Vpc cuc               | VBAT falling, VRECHG = 200mV,<br>VBUS = 15V, VBAT_REG = 8.4V        | 180  | 200  | 230  | - mV |

| Below VBAT_REG                            | VRE_CHG               | VBAT falling, VRECHG = 400mV<br>VBUS = 15V, VBAT_REG = 16.8V        | 360  | 400  | 460  |      |

| Input Voltage and Curre                   | nt Regulation         |                                                                     |      |      |      |      |

| Minimum Input Voltage<br>Regulation Range | VMIVR_RANGE           |                                                                     | 3.6  |      | 22   | V    |

DS9492-01 July 2023

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

| Parameter                                    | Symbol         | Test Conditions                         | Min  | Тур                                                                                                                    | Max  | Unit |

|----------------------------------------------|----------------|-----------------------------------------|------|------------------------------------------------------------------------------------------------------------------------|------|------|

| Minimum Input Voltage<br>Regulation Step     | VMIVR_STEP     |                                         |      | 100                                                                                                                    |      | mV   |

| Minimum Input Voltage<br>Regulation Accuracy | VMIVR_ACC      | VMIVR = 4.3V, 10.6V and 18.6V           | -1   |                                                                                                                        | 1    | %    |

| Average Input Current Regulation Range       | IAICR_RANGE    |                                         | 0.1  |                                                                                                                        | 3.3  | Α    |

| Average Input Current Regulation Step        | IAICR_STEP     |                                         |      | 10                                                                                                                     |      | mA   |

|                                              |                | VBUS = 15V, IAICR = 500mA               | 450  | 470                                                                                                                    | 500  |      |

| Average Input Current                        | 1              | VBUS = 15V, IAICR = 1000mA              | 900  | 950                                                                                                                    | 1000 | mA   |

| Regulation Accuracy                          | IAICR_ACC      | VBUS = 15V, IAICR = 2000mA              | 1800 | 1900                                                                                                                   | 2000 |      |

|                                              |                | VBUS = 15V, IAICR > 2000mA              | -9   |                                                                                                                        | 0    | %    |

| BAT Overvoltage Protec                       | tion           |                                         |      |                                                                                                                        |      |      |

| Battery Overvoltage<br>Rising                | V2.17.0V2      | VBAT rising, as percentage of VBAT_REG  | 103  | 104                                                                                                                    | 105  | %    |

| Battery Overvoltage<br>Falling               |                | VBAT falling, as percentage of VBAT_REG | 101  | 102                                                                                                                    | 103  | %    |

| Battery Overvoltage Sink<br>Source           | RBAT_OVP       | Sink source from VBAT to GND            |      | 1.1                                                                                                                    |      | kΩ   |

| Thermal Regulation and                       | Shutdown       |                                         |      |                                                                                                                        |      | •    |

| Junction Thermal<br>Regulation Range         | TJ_THREG_RANGE | Default = 120°C                         | 60   |                                                                                                                        | 120  | °C   |

| Junction Thermal<br>Regulation Step          | TJ_THREG_STEP  |                                         |      | 20                                                                                                                     |      | °C   |

|                                              |                | TJ_THREG = 120°C                        |      | 120                                                                                                                    |      |      |

| Junction Thermal                             | T              | T <sub>J_</sub> THREG = 100°C           |      | 100                                                                                                                    |      |      |

| Regulation Accuracy                          | TJ_THREG_ACC   | TJ_THREG = 80°C                         |      | 80                                                                                                                     |      | °C   |

|                                              |                | TJ_THREG = 60°C                         |      | 1 3.3 3.3 470 500 950 1000 0 0 104 105 0 103 120 120 120 120 120 150 150 150 170 130 150 150 170 130 150 140 85 105 30 |      |      |

|                                              |                | TJ_THREG = 150°C,<br>Temperature rising | 130  | 150                                                                                                                    | 170  |      |

| Thermal Shutdown                             | Torra          | TJ_THREG = 130°C,<br>Temperature rising | 110  | 130                                                                                                                    | 150  | °C   |

| Rising                                       | Тотр           | TJ_THREG = 120°C,<br>Temperature rising | 100  | 120                                                                                                                    | 140  |      |

|                                              |                | TJ_THREG = 85°C, Temperature rising     | 65   | 85                                                                                                                     | 105  |      |

| Thermal Shutdown<br>Hysteresis               | Totp_HYS       | Temperature falling                     |      | 30                                                                                                                     |      | °C   |

| NTC Monitor (Charger M                       | ode)           |                                         |      |                                                                                                                        |      | 1    |

| Battery Temperature                          | \\             | VTS rising, the ratio of VREGN          | 72.3 | 73.5                                                                                                                   | 74.7 | 0,1  |

| COLD Threshold (0°C)                         | VVTS_COLD      | VTS falling, the ratio of VREGN         | 70.8 | 72                                                                                                                     | 73.2 | %    |

| Parameter                                 | Symbol            | Test Conditions                                           | Min  | Тур  | Max  | Unit |

|-------------------------------------------|-------------------|-----------------------------------------------------------|------|------|------|------|

|                                           |                   | VVTS_COOL = 5°C, VTS rising, the ratio of VREGN           | 70.6 | 71.1 | 71.6 |      |

| Battery Temperature                       | V(170, 000), D(07 | VVTS_COOL = 10°C, VTS rising, the ratio of VREGN          | 67.4 | 68.5 | 69.6 | %    |

| COOL Rising Threshold                     | VVTS_COOL_RISE    | VVTS_COOL = 15°C, VTS rising, the ratio of VREGN          | 65   | 65.5 | 66   | 70   |

|                                           |                   | VVTS_COOL = 20°C, VTS rising, the ratio of VREGN          | 61.9 | 62.4 | 62.9 |      |

|                                           |                   | VVTS_COOL = 5°C, VTS falling, the ratio of VREGN          | 69.3 | 69.8 | 70.3 | %    |

| Battery Temperature                       | V                 | VvTs_cool = 10°C, VTs falling, the ratio of VREGN         | 65.9 | 67   | 68.1 | %    |

| COOL Falling Threshold                    | VVTS_COOL_FALL    | VVTS_COOL = 15°C, VTS falling, the ratio of VREGN         | 63.7 | 64.2 | 64.7 | 0/   |

|                                           |                   | VVTS_COOL = 20°C, VTS falling, the ratio of VREGN         | 60.6 | 61.1 | 61.6 | - %  |

|                                           |                   | VVTS_WARM = 40°C, VTS falling, the ratio of VREGN         | 47.9 | 48.4 | 48.9 |      |

| Battery Temperature                       | Vvts_warm_fall    | VVTS_WARM = 45°C, VTS falling, the ratio of VREGN         | 44.2 | 45   | 45.8 | - %  |

| WARM Falling Threshold                    |                   | VVTS_WARM = 50°C, VTS falling, the ratio of VREGN         | 40.7 | 41.2 | 41.7 |      |

|                                           |                   | VVTS_WARM = 55°C, VTS falling, the ratio of VREGN         | 37.2 | 37.7 | 38.2 |      |

|                                           |                   | VVTS_WARM = 40°C, VTS rising, the ratio of VREGN          | 49.2 | 49.7 | 50.2 |      |

| Battery Temperature                       |                   | VVTS_WARM = 45°C, VTS rising, the ratio of VREGN          | 45.2 | 46   | 46.8 | - %  |

| WARM Rising Threshold                     | Vvts_warm_rise    | VVTS_WARM = 50°C, VTS rising, the ratio of VREGN          | 42   | 42.5 | 43   |      |

|                                           |                   | VVTS_WARM = 55°C, VTS rising, the ratio of VREGN          | 38.5 | 39   | 39.5 |      |

| Battery Temperature                       | \\                | VTS falling, the ratio of VREGN                           | 33.4 | 34   | 34.7 | 0/   |

| HOT Threshold (60°C)                      | Vvts_hot          | VTS rising, the ratio of VREGN                            | 34.9 | 35.5 | 36.1 | %    |

| NTC Monitor (OTG Mode                     | <del>e</del> )    |                                                           |      |      |      |      |

| Battery Temperature COLD Rising Threshold | VVTS_COLD_OTG_    | VVTS_COLD_OTG = -20°C,<br>VTS rising, the ratio of VREGN  | 78.7 | 80   | 81.3 | - %  |

| OTG mode                                  | RISE              | VVTS_COLD_OTG = -10°C,<br>VTS rising, the ratio of VREGN  | 75.7 | 77   | 78.3 | /0   |

| Battery Temperature                       | VVTS_COLD_OTG_    | VVTS_COLD_OTG = -20°C,<br>VTS falling, the ratio of VREGN | 78.2 | 78.7 | 79.2 |      |

| COLD Falling Threshold OTG mode           | FALL              | VVTS_COLD_OTG = -10°C,<br>VTS falling, the ratio of VREGN | 74.8 | 76   | 77.2 | %    |

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

DS9492-01 July 2023 www.richtek.com

| Parameter                                                                        | Symbol                | Test Conditions                                      | Min  | Тур  | Max   | Unit |

|----------------------------------------------------------------------------------|-----------------------|------------------------------------------------------|------|------|-------|------|

|                                                                                  |                       | VVTS_HOT_OTG = 55°C, VTS falling, the ratio of VREGN | 37.2 | 37.7 | 38.2  |      |

| Battery Temperature HOT Falling Threshold OTG mode                               | VVTS_HOT_OTG_<br>FALL | VVTS_HOT_OTG = 60°C, VTS falling, the ratio of VREGN | 33.9 | 34.5 | 35.1  | %    |

|                                                                                  |                       | VVTS_HOT_OTG = 65°C, VTS falling, the ratio of VREGN | 32   | 32.5 | 33    |      |

| Battery Temperature                                                              |                       | VVTS_HOT_OTG = 55°C, VTS rising, the ratio of VREGN  | 38.8 | 39.3 | 39.8  | %    |

| HOT Rising Threshold OTG Mode                                                    | VVTS_HOT_OTG_<br>RISE | VVTS_HOT_OTG = 60°C, VTS rising, the ratio of VREGN  | 34.9 | 35.5 | 36.2  | %    |

|                                                                                  |                       | VVTS_HOT_OTG = 65°C, VTS rising, the ratio of VREGN  | 32   | 32.5 | 33    | %    |

| Overcurrent Threshold                                                            |                       |                                                      |      |      |       |      |

| Q1 Cycle-by-Cycle<br>Overcurrent Threshold                                       | IOCP_Q1               |                                                      | 8.55 | 10.5 | 12.25 | Α    |

| Q2 Cycle-by-Cycle<br>Overcurrent Threshold                                       | IOCP_Q2               |                                                      | 6.8  | 7.5  | 8.25  | Α    |

| Q3 Cycle-by-Cycle<br>Overcurrent Threshold                                       | IOCP_Q3               |                                                      | 6.8  | 7.5  | 8.25  | Α    |

| Q4 Cycle-by-Cycle<br>Overcurrent Threshold                                       | IOCP_Q4               |                                                      | 8.55 | 10.5 | 12.25 | Α    |

| System Over-Load<br>Threshold                                                    | IOCP_BATFET           |                                                      | 11   |      |       | Α    |

| Internal Sense Resistan                                                          | ce and MOSFET R       | dson                                                 | •    |      | '     |      |

| Input Sense Resistance                                                           | Rsns                  | Internal sense resistance between VBUS and PMID      |      | 9    |       | mΩ   |

| High-Side Switching<br>MOSFET (Q1) Turn on<br>Resistance between<br>PMID and SW1 | Ron_Q1                | VREGN = 4.9V                                         |      | 25   |       | mΩ   |

| Low-Side Switching<br>MOSFET (Q2) Turn on<br>Resistance between<br>SW1 and PGND  | RON_Q2                | VREGN = 4.9V                                         |      | 34   |       | mΩ   |

| Low-Side Switching<br>MOSFET(Q3) Turn on<br>Resistance between<br>SW2 and PGND   | Ron_q3                | VREGN = 4.9V                                         |      | 28   |       | mΩ   |

| High-Side Switching<br>MOSFET(Q4) Turn on<br>Resistance between<br>SW2 and SYS   | Ron_Q4                | VREGN = 4.9V                                         |      | 17   |       | mΩ   |

| BATFET (Q5) Turn on<br>Resistance between<br>SYS and BAT                         | RON_Q5                |                                                      |      | 11   |       | mΩ   |

| Parameter                                 | Symbol        | Test Conditions                                                       | Min  | Тур | Max  | Unit |

|-------------------------------------------|---------------|-----------------------------------------------------------------------|------|-----|------|------|

| USB On-The-Go (OTG)                       |               |                                                                       | •    |     |      | •    |

| OTG Low Battery                           | Vote LDD      | VBAT falling                                                          | 2.3  | 2.5 | 2.6  | V    |

| Protection                                | VOTG_LBP      | V <sub>BAT</sub> rising                                               | 2.5  | 2.7 | 2.9  | V    |

| OTG Voltage Limit<br>Regulation Range     | VOTG_CV_RANGE | Default = 5V                                                          | 2.8  |     | 22   | V    |

| OTG Voltage Limit<br>Regulation Step      | VOTG_CV_STEP  |                                                                       |      | 10  |      | mV   |

| OTG Voltage Limit<br>Regulation Accuracy  | Votg_cv_acc   | I <sub>VBUS</sub> = 0A, V <sub>OTG_REG</sub> = 5V, 12V, 20V           | -1.5 |     | 1.5  | %    |

| OTG Current Limit<br>Regulation Range     | IOTG_CC_RANGE | Default = 3A                                                          | 0.12 |     | 3.32 | Α    |

| OTG Current Limit<br>Regulation Step      | IOTG_CC_STEP  |                                                                       |      | 40  |      | mA   |

|                                           |               | IOTG_CC = 3A, VBAT = 8V,<br>VOTG_CV = 5V                              | -2.2 |     | 2.2  |      |

| OTG Current Limit<br>Regulation Accuracy  | IOTG_CC       | IOTG_CC = 1A, VBAT = 8V,<br>VOTG_CV = 5V                              | -5   |     | 3    | %    |

|                                           |               | IOTG_CC = 0.52A, VBAT = 8V,<br>VOTG_CV = 5V                           | -10  |     | 10   |      |

|                                           | IOTG_BAT      | IBAT_REG = 3A, VBAT = 8V,<br>VOTG_CV = 5V                             | 2.8  | 3   | 3.2  | A    |

| Battery Current<br>Regulation in OTG Mode |               | IBAT_REG = 4A, VBAT = 8V,<br>VOTG_CV = 5V                             | 3.8  | 4   | 4.2  |      |

|                                           |               | IBAT_REG = 5A, VBAT = 8V,<br>VOTG_CV = 5V                             | 4.8  | 5   | 5.2  |      |

| OTG Overvoltage                           |               | As percentage of Votg_cv,<br>OTG mode, OOA disabled,<br>VBus rising   | 104  | 113 | 120  | 0/   |

| Threshold                                 | VOTG_OVP      | As percentage of Votg_cv,<br>OTG mode, OOA disabled,<br>VBus falling  | 90   | 98  | 104  | - %  |

| OTG Undervoltage<br>Falling Threshold     | VOTG_UVP      | V <sub>BUS</sub> falling                                              | 2.1  | 2.2 | 2.3  | V    |

| PWM                                       |               |                                                                       |      |     |      |      |

| PWM Switching                             | farr          | Oscillator frequency,<br>fsw = 1.5MHz                                 |      | 1.5 |      | MHz  |

| Frequency                                 | fsw           | Oscillator frequency,<br>fsw = 750kHz                                 |      | 750 |      | kHz  |

| REGN                                      | •             | •                                                                     | •    |     | •    | •    |

| REGN LDO Output                           | Vocas         | VBUS = 5V, VBAT = 8V,<br>IREGN = 20mA, charge<br>disabled, ISYS = 0A  | 4.5  | 4.9 | 5.1  |      |

| Voltage                                   | VREGN         | VBUS = 15V, VBAT = 8V,<br>IREGN = 20mA, charge<br>disabled, ISYS = 0A | 4.5  | 4.9 | 5.2  | V    |

Copyright © 2023 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9492-01 July 2023 www.richtek.com

| Parameter                               | Symbol       | Test Conditions                       | Min  | Тур | Max  | Unit |

|-----------------------------------------|--------------|---------------------------------------|------|-----|------|------|

| REGN LDO Current<br>Limit               | IREGN        | VBUS = 5V, VBAT = 8V,<br>VREGN = 4.5V | 30   |     |      | mA   |

| Current Sink                            |              |                                       |      |     |      |      |

| VAC1 Discharge<br>Resistance            | RVAC1_DISCHG | VAC1_PD_EN = 1, VAC1 = 5V             |      | 1.1 |      | kΩ   |

| VAC2 Discharge<br>Resistance            | RVAC2_DISCHG | VAC2_PD_EN = 1, VAC2 = 5V             |      | 1.1 |      | kΩ   |

| VBUS Discharge<br>Resistance            | RVBUS_DISCHG | VBUS_PD_EN = 1, VBUS = 5V             |      | 1.1 |      | kΩ   |

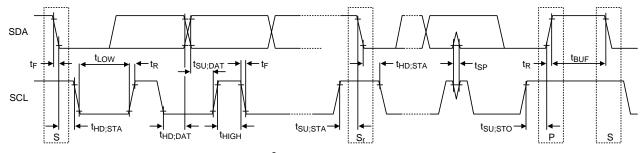

| I <sup>2</sup> C Interface (SCL and S   | DA)          |                                       |      |     |      |      |

| Input SDA High<br>Threshold Voltage     | VIH_SDA      | Pull high to 1.8V/1.2V                | 0.84 |     |      | V    |

| Input SDA Low<br>Threshold Voltage      | VIL_SDA      | Pull high to 1.8V/1.2V                |      |     | 0.4  | V    |

| Output SDA Low<br>Threshold Voltage     | VOL_SDA      | Sink current = 5mA                    |      |     | 0.4  | ٧    |

| High Level SDA Leakage<br>Current       | IBIAS_SDA    | Pull high to 1.8V                     |      |     | 1    | μА   |

| Input SCL High<br>Threshold Voltage     | VIH_SCL      | Pull high to 1.8V/1.2V                | 0.84 |     |      | V    |

| Input SCL Low<br>Threshold Voltage      | VIL_SCL      | Pull high to 1.8V/1.2V                |      |     | 0.4  | V    |

| High Level SCL Leakage<br>Current       | IBIAS_SCL    | Pull high to 1.8V                     |      |     | 1    | μА   |

| SCI Clask Fraguency                     | foot         | CB ≤ 100pF                            |      |     | 3400 | kHz  |

| SCL Clock Frequency                     | fscl         | 100pF < CB ≤ 400pF                    |      |     | 1700 | KIIZ |

| Control I/O Pin (CE, QON                | and ILIM_HZ) |                                       |      |     |      |      |

| Input CE High Threshold Voltage         | VIH_CE       |                                       | 1.3  |     |      | V    |

| Input CE LOW Threshold Voltage          | VIL_CE       |                                       |      |     | 0.4  | V    |

| High Level CE Leakage<br>Current        | IBIAS_CE     | Pull high to 1.8V                     |      |     | 1    | μА   |

| Input QON High<br>Threshold Voltage     | VIH_QON      |                                       | 1.3  |     |      | V    |

| Input QON LOW Threshold Voltage         | VIL_QON      |                                       |      |     | 0.4  | V    |

| Internal QON Pull Up<br>Voltage         | VQON         |                                       | 2.8  | 3.1 | 3.4  | V    |

| Internal QON Pull Up<br>Resistance      | RQON         |                                       | 185  | 200 | 230  | kΩ   |

| Input ILIM_HZ High<br>Threshold Voltage | VIH_ILIM_HZ  |                                       | 1    |     |      | V    |

| Input ILIM_HZ Low<br>Threshold Voltage  | VIL_ILIM_HZ  |                                       |      |     | 0.75 | V    |

| Parameter                                          | Symbol               | Test Conditions                        | Min  | Тур | Max  | Unit |

|----------------------------------------------------|----------------------|----------------------------------------|------|-----|------|------|

| Input ILIM_HZ Voltage<br>Range                     | VILIM_RANGE          | ILIM_HZ voltage range for setting ILIM | 1    |     | 4    | V    |

| High Level LIMI_HZ<br>Leakage Current              | IBIAS_ILIM_HZ        | VILIM_HIZ = 4V                         | -1.5 |     | 1.5  | μА   |

| Control I/O Pin (INT and                           | STAT/OTG)            |                                        |      |     | •    | •    |

| Output INT Low<br>Threshold Voltage                | VOL_INT              | Sink current = 5mA                     |      |     | 0.4  | V    |

| High Level INT Leakage<br>Current                  | IBIAS_INT            | Pull high to 1.8V                      |      |     | 1    | μА   |

| INT Pull Low Time                                  | tINT_PULL_LOW        | INT pull low time                      |      | 256 |      | μS   |

| Output STAT/OTG Low Threshold Voltage              | Vol_stat             | Sink current = 5mA                     |      |     | 0.4  | V    |

| High Level STAT/OTG<br>Leakage Current             | IBIAS_STAT           | Pull high to 1.8V                      |      |     | 1    | μА   |

| Input STAT/OTG High<br>Threshold Voltage           | VIH_OTG              | STAT configure to OTG pin              | 1.3  |     |      | V    |

| Input STAT/OTG LOW<br>Threshold Voltage            | VIL_OTG              | STAT configure to OTG pin              |      |     | 0.4  | V    |

| D+/D- Detection                                    |                      |                                        |      |     |      |      |

| Data Detect Voltage                                | VDAT_REF             | For primary/secondary detection        | 340  | 375 | 400  | mV   |

| D+ Current Sink                                    | ID+_ISNK             | V <sub>D+</sub> = 500mV                | 25   | 45  | 65   | μΑ   |

| D- Current Sink                                    | I <sub>D</sub> ISNK  | V <sub>D</sub> - = 500mV               | 25   | 45  | 65   | μΑ   |

| D+/ D- Leakage Current                             | ID+DLKG              | HIZ mode                               | -1   |     | 1    | μΑ   |

| D+ Logic Threshold                                 | VLGC                 | V <sub>D+</sub> rising                 | 800  | 900 | 1000 | mV   |

| D+ Current Source                                  | ID+_SRC              | V <sub>D+</sub> = 200mV                | 7    | 10  | 13   | μΑ   |

| D+ Voltage Source                                  | V <sub>D+_</sub> SRC |                                        | 600  | 650 | 700  | mV   |

| D- Voltage Source                                  | VDSRC                |                                        | 600  | 650 | 700  | mV   |

| D+ Pulldown for Connection Check                   | RD+_19K              |                                        | 16   | 20  | 24   | kΩ   |

| D- Pulldown for<br>Connection Check                | RD19K                |                                        | 16   | 20  | 24   | kΩ   |

| D+D- Threshold for Non-<br>Standard Adapter (0.9V) | VD+D0P9              |                                        | 0.81 | 0.9 | 0.99 | ٧    |

| D+D- Threshold for Non-<br>Standard Adapter (1.5V) | VD+D1P5              |                                        | 1.4  | 1.5 | 1.6  | V    |

| D+D- Threshold for Non-<br>Standard Adapter (2.3V) | VD+D2P3              |                                        | 2.2  | 2.3 | 2.4  | V    |

| D+D- Threshold for CDP                             | VD+DCDP              | For host mode, CDP                     | 1.8  | 2   | 2.2  | V    |

| Across D+/D-<br>Resistance in DCP                  | RDCP                 | For host mode, DCP                     |      | 50  | 150  | Ω    |

| Parameter                            | Symbol        | Test Conditions    | Min  | Тур | Max  | Unit |  |

|--------------------------------------|---------------|--------------------|------|-----|------|------|--|

| Timing Requirements                  |               |                    |      |     |      |      |  |

| Charge Safe Timer for Trickle Charge | ttri_safe_tmr |                    | 0.9  | 1   | 1.1  | hr   |  |

| Charge Safe Timer for<br>Pre-Charge  | tpre_safe_tmr | PRECHG_TMR = 2hr   | 1.8  | 2   | 2.2  | hr   |  |

|                                      | tCHG_SAFE_TMR | FASTCHG_TMR = 5hr  | 4.5  | 5   | 5.5  |      |  |

| Charge Safe Timer for                |               | FASTCHG_TMR = 8hr  | 7.2  | 8   | 8.8  | hr   |  |

| Fast Charge                          |               | FASTCHG_TMR = 12hr | 10.8 | 12  | 13.2 |      |  |

|                                      |               | FASTCHG_TMR = 24hr | 21.6 | 24  | 26.4 |      |  |

|                                      |               | BG_CHG_TMR = 15min | 12   | 15  | 18   |      |  |

| Back-Ground Charge Timer             | tbg_chg_tmr   | BG_CHG_TMR = 30min | 24   | 30  | 36   | min  |  |

| Timo                                 |               | BG_CHG_TMR = 45min | 36   | 45  | 54   |      |  |

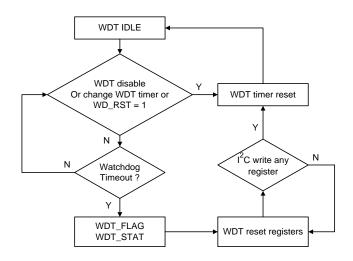

| Watchdog Timer                       |               |                    |      |     |      |      |  |

| Watchdog Timer                       | twdt          | WATCHDOG = 160s    | 144  | 160 | 176  | s    |  |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A$  = 25°C with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precautions are recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. Maximum output current for ISYS recommend to set switching frequency on 1MHz.

- Note 6. Specification is guaranteed by design and/or correlation with statistical process control.

- Note 7. Refer to MIVR section in the Application Information for detailed descriptions.

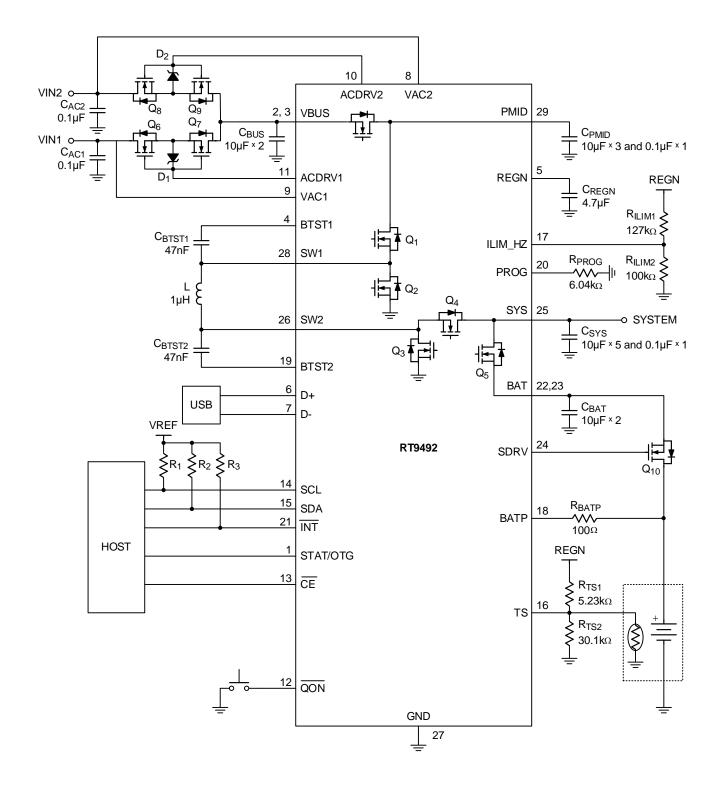

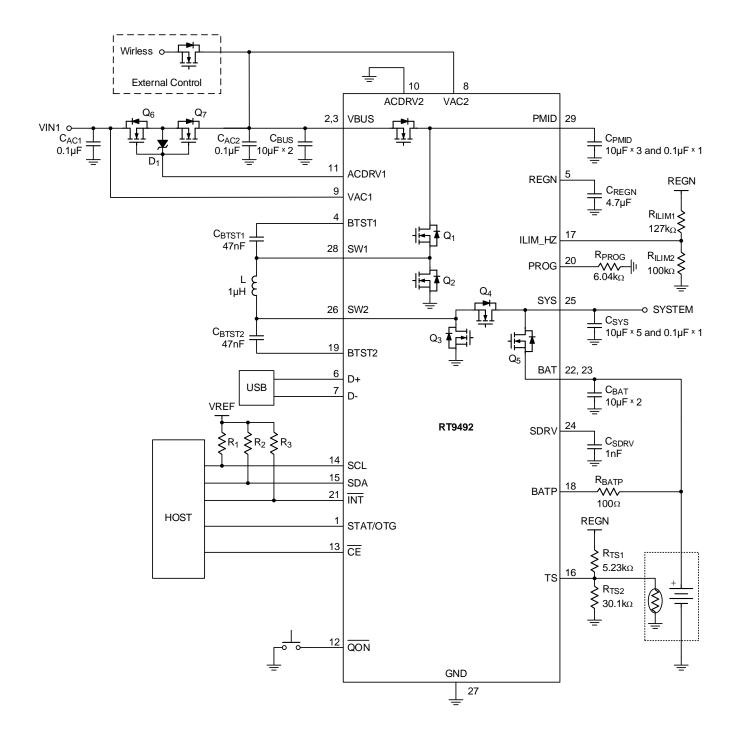

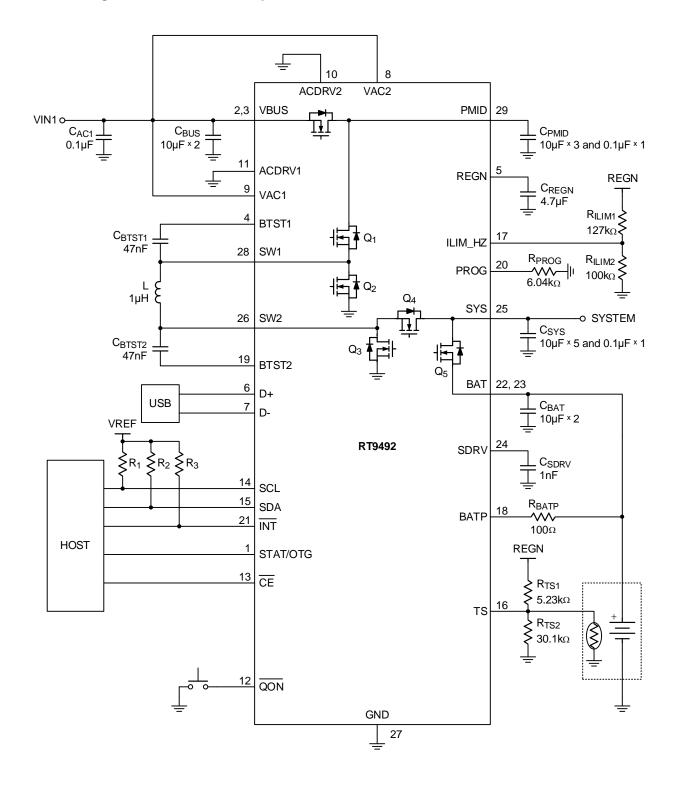

## **Typical Application Circuit**

### RT9492 with Dual input and Ship FET

**RICHTEK** is a registered trademark of Richtek Technology Corporation.

19

### RT9492 with Single input and no Ship FET

### RT9492 with Single ACRBFET and No Ship FET

### Below are recommended components information

| Name              | Part Number        | Description           | Package        | Manufacturer    |

|-------------------|--------------------|-----------------------|----------------|-----------------|

| CAC1              | 0402B104K500CT     | 0.1μF/50V/X7R         | 0402           | WALSIN          |

| CAC2              | 0402B104K500CT     | 0.1μF/50V/X7R         | 0402           | WALSIN          |

| CBUS              | GRM188R6YA106MA73  | 10μF/35V/X5R          | 0603           | MURATA          |

| СРМІД             | GRM188R6YA106MA73  | 10μF/35V/X5R          | 0603           | MURATA          |

| СРМІД             | 0402B104K500CT     | 0.1μF/50V/X7R         | 0402           | WALSIN          |

| Свтѕт1            | GRM033R61C473KE84  | 47nF/16V/X5R          | 0201           | MURATA          |

| Свтѕт2            | GRM033R61C473KE84  | 47nF/16V/X5R          | 0201           | MURATA          |

| Csys              | GRM188R61E106MA73  | 10μF/25V/X5R          | 0603           | MURATA          |

| Csys              | 0402B104K500CT     | 0.1μF/50V/X7R         | 0402           | WALSIN          |

| Сват              | GRM188R61E106MA73  | 10μF/25V/X5R          | 0603           | MURATA          |

| CREGN             | GRM155R60J475ME47D | 4.7μF/6.3V/X5R        | 0402           | MURATA          |

|                   | PIMB063T-1R0MS-68  | 1μH/20%/6.7m $\Omega$ | 6.8x7.3x3.0mm  | CYNTEC          |

| L                 | PIMB063T-2R2MS-68  | 2.2μH/20%/<br>13.5mΩ  | 6.8x7.3x3.0mm  | CYNTEC          |

| Q6, Q7,<br>Q8, Q9 | AONR36366          | N-MOSFET              | DFN 3x3 EP     | ALPHA and OMEGA |

| Q10               | AON7528            | N-MOSFET              | DFN 3.3x3.3 EP | ALPHA and OMEGA |

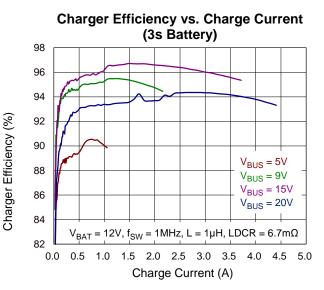

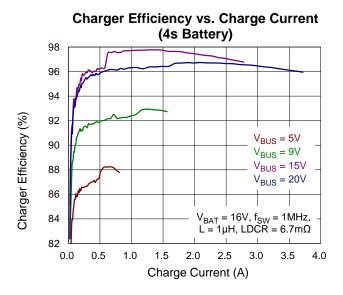

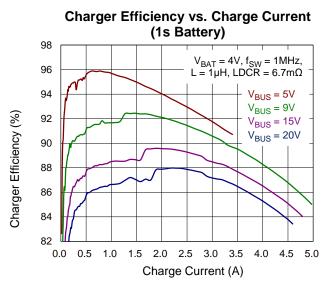

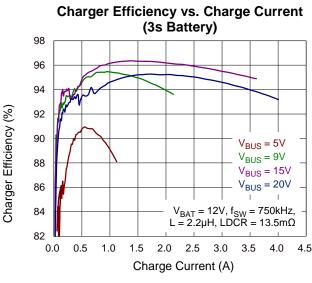

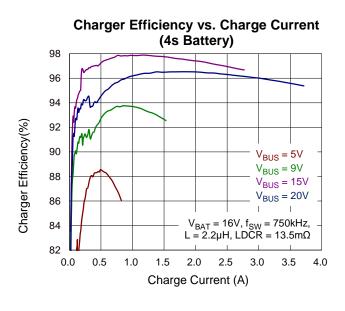

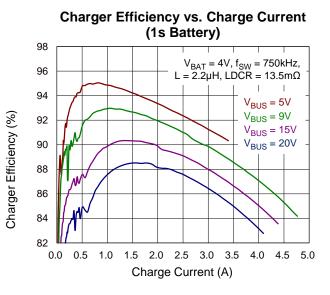

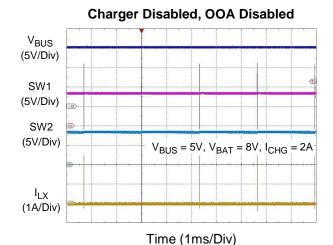

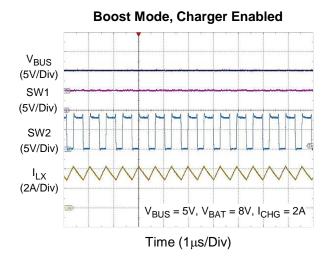

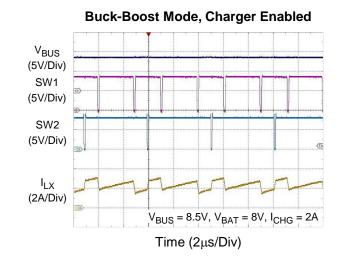

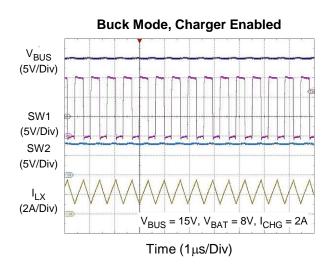

# **Typical Operating Characteristics**

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

2023

July

DS9492-01

RICHTEK is a registered trade

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

DS9492-01

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9492-01 July 2023 www.richtek.com

**RICHTEK** Copyright © 2023 Richtek Technology Corporation. All rights reserved. is a registered trademark of Richtek Technology Corporation.

DS9492-01 July 2023 www.richtek.com 27

# **Register Description**

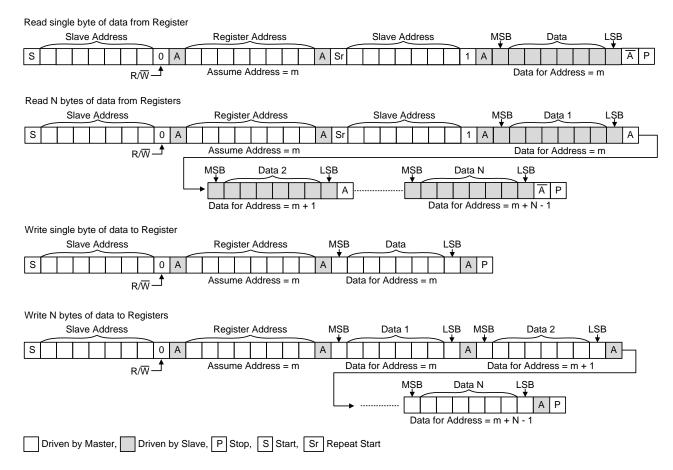

I<sup>2</sup>C Slave Address: 1010011 (53H)

R: Read only

R/W: Read and write

RWS: Read and write, also automatically set by particular condition

RWC: Read and write, also automatically cleared by particular condition

RWSC: Read and write, also automatically set/cleared by particular condition

Register Address: 0x00, Register Name: SYS\_MIN REGU

| Bit | Bit Name | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                                                                                                                                                                                                             |

|-----|----------|---------|------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | RESERVED | 00      | N          | N          | R    | Reserved                                                                                                                                                                                                                                                                                                                |

| 5:0 | VSYSMIN  | NA      | N          | Y          | RWSC | During POR, the device reads the resistance on PROG pin, to identify the default battery cell count and determine the default VSYSMIN, change REG0x0A[7:6] also change default value 000000: 2.5V 000001: 2.75V 000100: 3.5V (1s) 010010: 7V (2s) 011010: 9V (3s) 100110: 12V (4s) 110101: 15.75V 110110 to 111111: 16V |

Register Address: 0x01, Register Name: VCHG\_CTRL

| Bit   | Bit Name | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|----------|---------|------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:11 | RESERVED | 00000   | N          | N          | R    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10:0  | VBAT_REG | NA      | N          | Y          | RWSC | During POR, the device reads the resistance on PROG pin, to identify the default battery cell count and determine the default power-on battery voltage, change REG0x0A[7:6] also change default value 0000000000000 to 00100101100: 3.00V 00100101101: 3.01V 00100101110: 3.02V  00110100100: 4.2V (1s)  11010101000: 12.6V (3s)  11010010000: 16.8V (4s)  11101010111: 18.79V 11101011000 to 11111111111: 18.8V |

Register Address: 0x03, Register Name: ICHG\_CTRL

| Bit  | Bit Name  | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                                                                                                                                                                                                                                                   |

|------|-----------|---------|------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:9 | RESERVED  | 0000000 | N          | N          | R    | Reserved                                                                                                                                                                                                                                                                                                                                                      |

| 8:0  | ICHG_CTRL | NA      | Y          | Y          | RWSC | During POR, the device reads the resistance on PROG pin, to identify the default battery cell count and determine the default power-on battery charging current, change REG0x0A[7:6] also change default value 00000000000 to 0000001110: Reserved 000001111: 0.15A 001100100: 1A (3s, 4s) 011001000: 2A (1s, 2s) 111110011: 4.99A 111110100 to 111111111: 5A |

Register Address: 0x05, Register Name: MIVR\_CTRL

| Bit | Bit Name | Default  | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                                                                                                       |

|-----|----------|----------|------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | VMIVR    | 00100100 | N          | N          | RWS  | MIVR is set to the value based on the VBUS measurement when the adapter plugs in and AUTO_MIVR = 1 000000000 to 00100100: 3.6V (Default) 00100101: 3.7V 01101010: 10.6V 11011011: 21.9V 11011100 to 11111111: 22V |

Register Address: 0x06, Register Name: AICR\_CTRL

| Bit  | Bit Name | Default       | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                                                                    |

|------|----------|---------------|------------|------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:9 | RESERVED | 0000000       | N          | N          | R    | Reserved                                                                                                                                                                       |

| 8:0  | IAICR    | 10010<br>1100 | N          | Y          | RWSC | Based on D+/D- detection results, if AUTO_AICR = 1 0000000000 to 000001010: 100mA 000001011: 110mA 000110010: 500mA 100101100: 3000mA (Default) 101001010 to 111111111: 3300mA |

Register Address: 0x08, Register Name: PRE\_CHG

| Bit | Bit Name | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                     |

|-----|----------|---------|------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | VPRE_CHG | 11      | N          | Y          | R/W  | Pre-charge voltage threshold from<br>00: 15%*VBAT_REG<br>01: 62%*VBAT_REG<br>10: 66.5%*VBAT_REG<br>11: 71.5%*VBAT_REG (Default) |

| 5:0 | IPRE_CHG | 000011  | Y          | Y          | R/W  | Pre-charge current<br>000000 to 000010: Reserved<br>000011: 0.12A (Default)<br><br>110001: 1.96A<br>110010 to 111111: 2A        |

DS9492-01 July 2023 www.richtek.com

Register Address: 0x09, Register Name: EOC\_CTRL

| Bit | Bit Name | Default | WDT<br>RST | REG<br>RST | Туре | Description                                                                                                                                          |

|-----|----------|---------|------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|