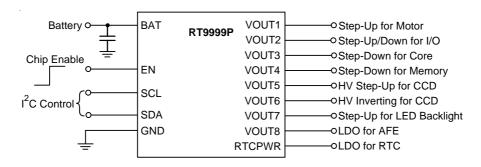

# 7+2 Channel DC/DC Converters with RTC and I<sup>2</sup>C Interface

# **General Description**

The RT9999P is a highly integrated power management IC that contains 7-CH switching DC/DC converters, one generic LDO, one Keep Alive low quiescent LDO, a switch with reverse leakage prevention from backup battery, and a Real-Time Clock (RTC) that includes a time counter and a 32768Hz oscillator for DSC applications.

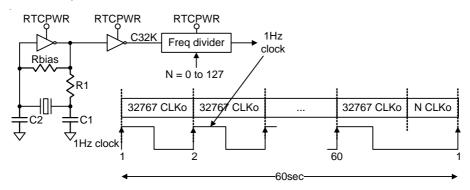

The DC/DC converters include one low voltage step-up operated in either asynchronous PFM or synchronous PWM, one current mode synchronous step-up/down (buck boost), two synchronous step-downs, one high voltage synchronous step-up for CCD+ with load disconnect, one asynchronous inverter for CCD-, and one WLED driver operated in either synchronous step-up mode or constant current source mode. All power MOSFETs are integrated and compensation networks are built in.

The RT9999P uses  $I^2C$  interface to set power on timing, output voltage, and WLED current and dimming level. The  $I^2C$  is also used to access RTC time counters and oscillator fine tuning.

The RT999P provides comprehensive protection functions, including over current, under voltage, over voltage, over temperature, and over load.

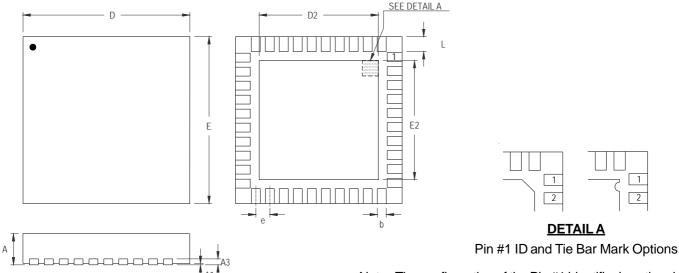

The RT9999P is available in a WQFN-40L 5x5 package.

# **Features**

- CH1 Sync Step-Up in PWM mode or Async Step-Up in Pulse Frequency Mode

- CH2 LV Sync Step-Up/Down

- CH3/4 LV Sync Step-Down with 100% Maximum Duty Cycle

- CH5 HV Sync Step-Up for CCD+ Power with Load Disconnect Function

- CH6 HV Async Inverter for CCD- Power

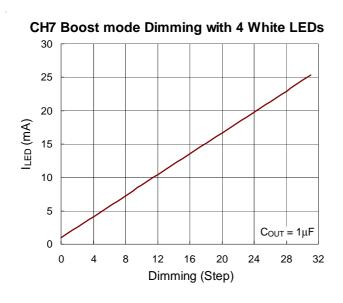

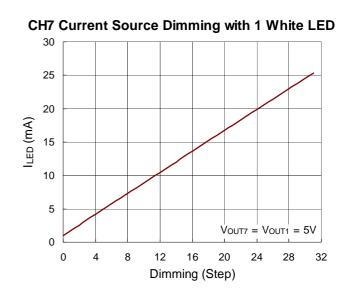

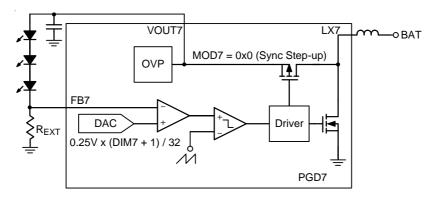

- CH7 WLED Driver in Sync Step-Up Mode or Constant Current Source Mode

- **▶** Open LED Protection

- 32 Dimming Levels

- CH8 Generic Low Voltage LDO for Multiple Purpose Power Supply

- CH9 Keep Alive Low Quiescent LDO

- I<sup>2</sup>C Interface to Program :

- ► Enable, Power On Delay Time, Output Regulated Voltage, WLED Dimming Current

- RTC Timer and Oscillator

- CH3/4 Fixed 2MHz Frequency

- CH1/2/5/6/7 Fixed 1MHz Frequency

- CH1/3/4/7/8 Support Dynamic Voltage Scaling (DVS)

- High Efficiency Up to 95%

- RoHS Compliant and Halogen Free

# **Applications**

- Digital Cameras

- Portable Instruments

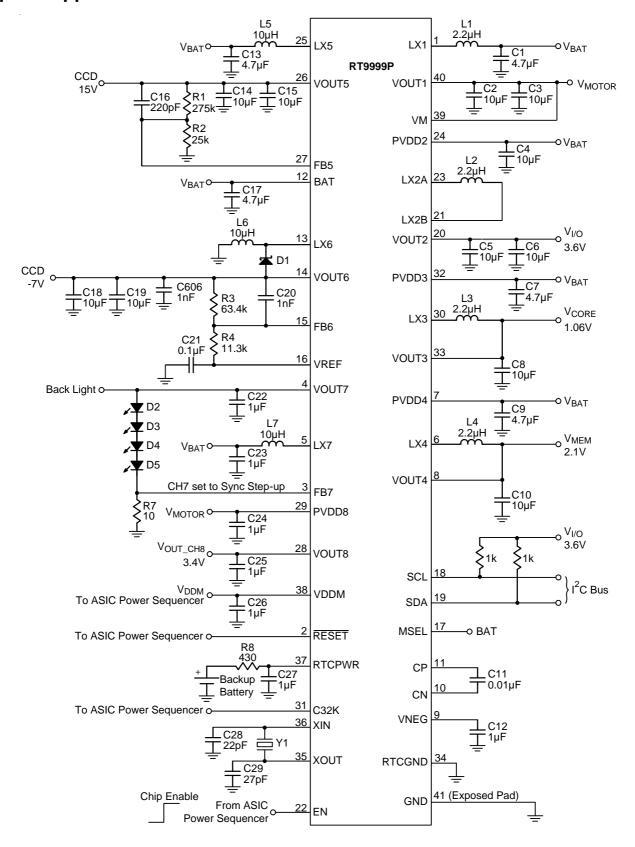

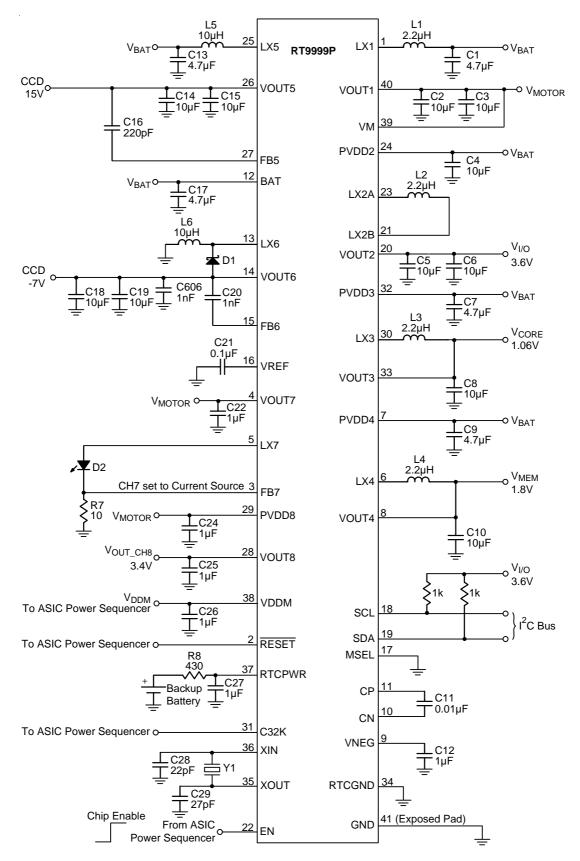

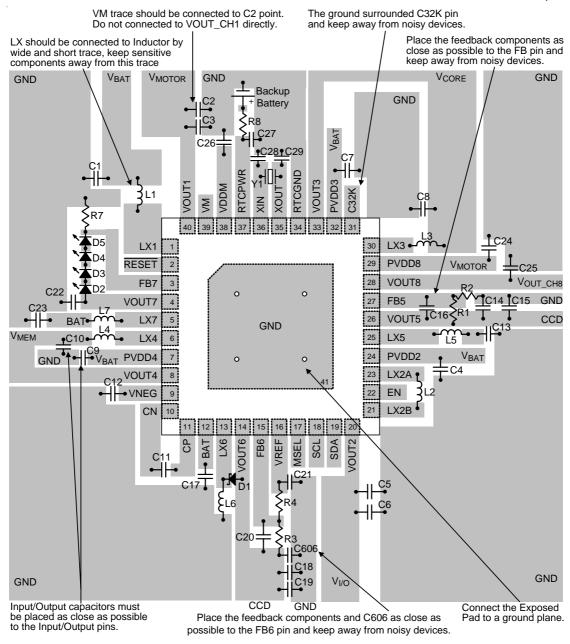

# Simplified Application Circuit

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

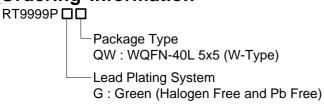

# **Ordering Information**

#### Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

# **Marking Information**

RT9999PGQW: Product Number

YMDNN: Date Code

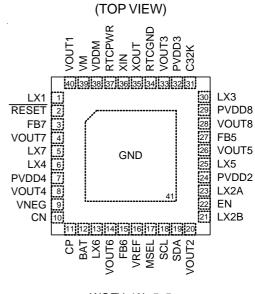

# **Pin Configuration**

WQFN-40L 5x5

## **Part Status**

| Part No    | Status  | Package Type |

|------------|---------|--------------|

| RT9999PGQW | Lifebuy | WQFN-40L 5x5 |

The part status values are defined as below:

Active: Device is in production and is recommended for new designs.

Lifebuy: The device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs.

**Preview**: Device has been announced but is not in production. **Obsolete**: Richtek has discontinued the production of the device.

# **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                        |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | LX1      | Switch Node of CH1. This pin is in high impedance during shutdown.                                                                                                                                                                                                                                                                  |

| 2       | RESET    | Push Pull Output. This pin asserts the status of monitored VDDM voltage.                                                                                                                                                                                                                                                            |

| 3       | FB7      | Feedback Input for CH7. This pin is in high impedance during shutdown.                                                                                                                                                                                                                                                              |

| 4       | VOUT7    | Power Output of CH7 in Step-Up Mode and Power Input of CH7 in Current Source Mode. When turning off in step-up mode, the IC discharges CH7 output capacitors internally. This pin is in high impedance during shutdown. In current source mode, it is recommended to connect VOUT7 to CH1 output node, VOUT1.                       |

| 5       | LX7      | Switch Node of CH7 in Step-Up Mode. This pin is in high impedance during shutdown. Connect this pin to the LED anode terminal when CH7 works in current source mode.                                                                                                                                                                |

| 6       | LX4      | Switch Node of CH4. This pin is in high impedance during shutdown.                                                                                                                                                                                                                                                                  |

| 7       | PVDD4    | Power Input of CH4. This pin is in high impedance during shutdown.                                                                                                                                                                                                                                                                  |

| 8       | VOUT4    | Sense Pin for CH4 Output Voltage. The IC can choose whether CH4 would discharge output capacitors internally when turning off. If the IC is set to discharge CH4 output capacitors internally, the IC would not start to turn off CH3 till VOUT4 < 0.1V. This pin is high impedance in shut down.                                   |

| 9       | VNEG     | Output of Negative Charge Pump to Enhance CH2 (PVDD2 – LX2A), CH3, CH4, CH6 P-MOSFET Driving. The regulated voltage is the higher one between (BAT – 4.5V) and (–BAT). When the negative charge pump is off, VNEG is internally connected to GND. Connect this pin to an external 1µF capacitor.                                    |

| 10      | CN       | Negative Switch Node of Charge Pump. A fly capacitor is needed between pins CP and CN.                                                                                                                                                                                                                                              |

| 11      | СР       | Positive Switch Node of Charge Pump.                                                                                                                                                                                                                                                                                                |

| 12      | BAT      | Power Input of CH6, Battery Power Input, and Sense Pin. It is recommended to place input bypass capacitors as close to the IC as possible. The IC senses the voltage of this pin for UVLO and body diode direction control of CH5 and CH7 P-MOSFET switches. This pin is also the input power for the negative charge pump circuit. |

| 13      | LX6      | Switch Node of CH6. This pin is in high impedance during shutdown.                                                                                                                                                                                                                                                                  |

| 14      | VOUT6    | Sense Pin for CH6 Output Voltage. When turning off, the IC internally discharges CH6 output capacitors to ground.                                                                                                                                                                                                                   |

| 15      | FB6      | Feedback Input of CH6. This pin is in high impedance during shutdown.                                                                                                                                                                                                                                                               |

| 16      | VREF     | Reference Voltage Buffer Output for CH6. This pin is in high impedance during shutdown.                                                                                                                                                                                                                                             |

| 17      | MSEL     | Selection Input for CH4 Default Output Voltage. This pin is sensed at the moment when RESET goes high to determine the CH4 default output voltage. MSEL = High means CH4 default = 1.8V; MSEL = Low means CH4 default = 1.5V.                                                                                                       |

| 18      | SCL      | Clock Input for I <sup>2</sup> C Serial Port.                                                                                                                                                                                                                                                                                       |

| 19      | SDA      | Data Input and Output for I <sup>2</sup> C Serial Port.                                                                                                                                                                                                                                                                             |

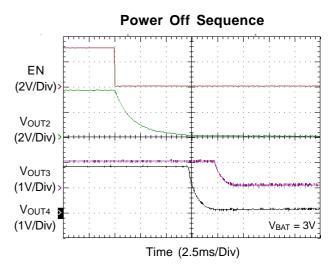

| 20      | VOUT2    | Power Output for CH2 Output Voltage. When turning off, the IC discharges CH2 output capacitors internally until VOUT2 < 0.1V. CH3 can only start turning off after VOUT2 < 0.1V. This pin is in high impedance during shutdown. I <sup>2</sup> C interface power level must be equal to CH2 output voltage.                         |

| 21      | LX2B     | Switch Node B of CH2. This pin is in high impedance during shutdown.                                                                                                                                                                                                                                                                |

Copyright ©2019 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

| Pin No.          | Pin Name | Pin Function                                                                                                                                                                                                                                              |

|------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22               | EN       | Enable Input. This pin is used to activate/deactivate the IC. An internal pull low is included.                                                                                                                                                           |

| 23               | LX2A     | Switch Node A of CH2. This pin is in high impedance during shutdown.                                                                                                                                                                                      |

| 24               | PVDD2    | Power Input of CH2. It must be connected to the same node as BAT. This pin is in high impedance during shutdown.                                                                                                                                          |

| 25               | LX5      | Switch Node of CH5. This pin is in high impedance during shutdown.                                                                                                                                                                                        |

| 26               | VOUT5    | Power Output and Sense Pin of CH5. When turning off, the IC discharges CH5 output capacitors internally until VOUT5 < 0.1V. It is recommended to place output capacitors as close to the chip as possible. This pin is in high impedance during shutdown. |

| 27               | FB5      | Feedback Input of CH5. This pin is in high impedance during shutdown.                                                                                                                                                                                     |

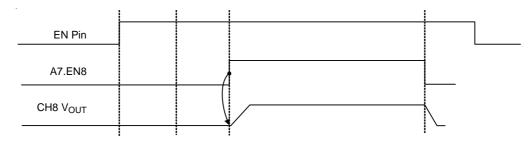

| 28               | VOUT8    | Regulated Output Node of CH8 Generic LDO. When turning off, the IC discharges CH8 output capacitors internally until VOUT8 < 0.1V. This pin is in high impedance during shutdown.                                                                         |

| 29               | PVDD8    | Power Input of CH8 Generic LDO. This pin is in high impedance during shutdown.                                                                                                                                                                            |

| 30               | LX3      | Switch Node of CH3. This pin is in high impedance during shutdown.                                                                                                                                                                                        |

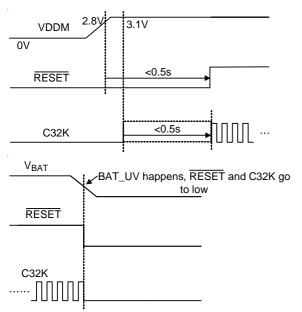

| 31               | C32K     | RTC 32768Hz Clock Output. Its rails are VDDM and GND. When RESET goes low, C32K outputs low.                                                                                                                                                              |

| 32               | PVDD3    | Power Input of CH3. It must be connected to the same node as BAT. This pin is in high impedance during shutdown.                                                                                                                                          |

| 33               | VOUT3    | Sense Pin for CH3 Output Voltage. When turning off, the IC discharges CH3 output capacitors internally until VOUT3 < 0.1V. This pin is in high impedance during shutdown.                                                                                 |

| 34               | RTCGND   | Ground for RTC Timer Counter and Oscillator.                                                                                                                                                                                                              |

| 35               | XOUT     | Crystal Output. This pin's parasitic capacitance should be kept as low as possible. Noise interference should also be avoided.                                                                                                                            |

| 36               | XIN      | Crystal Input. This pin's parasitic capacitance should be kept as low as possible. Noise interference should also be avoided.                                                                                                                             |

| 37               | RTCPWR   | RTCLDO Power Output Pin. Connect this pin to a backup battery.                                                                                                                                                                                            |

| 38               | VDDM     | Regulation Voltage Output of CH9. This pin also provides power for all IC control circuit. When VDDM is lower than RESET threshold, the IC asserts RESET = 0V. When BAT UVLO occurs, the IC discharges CH9 output capacitors internally.                  |

| 39               | VM       | Output Sense Pin of CH1 and Power Input of CH9.                                                                                                                                                                                                           |

| 40               | VOUT1    | Power Output and Sense Pin for CH1 Output Voltage. This pin is in high impedance during shutdown. It is recommended to place the output capacitors as close to the IC as possible.                                                                        |

| 41 (Exposed Pad) | GND      | Power Ground and Control Circuit Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum thermal dissipation.                                                                                                            |

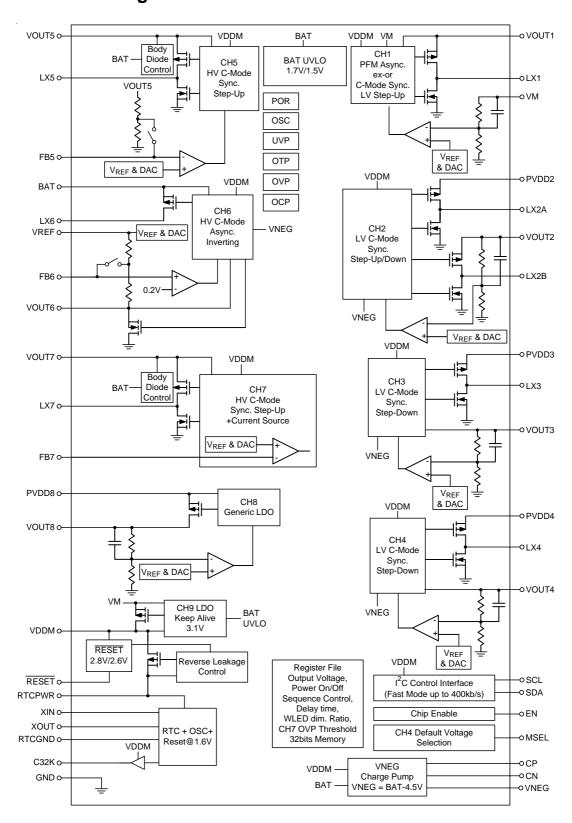

# **Functional Block Diagram**

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# Operation

The RT9999P is a highly integrated power management IC that contains 7-CH switching DC/DC converters, one generic LDO, one Keep Alive low quiescent LDO, a switch with reverse leakage prevention from backup battery, and a Real-Time Clock (RTC) that includes a time counter and 32768Hz oscillator.

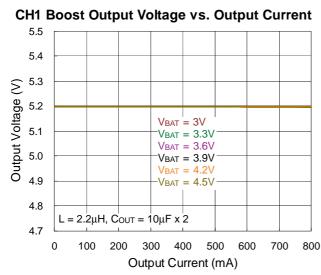

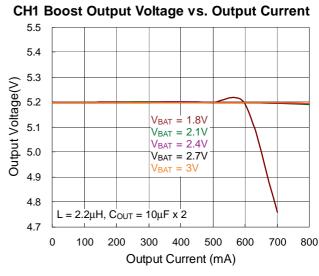

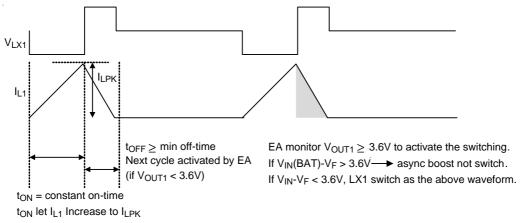

### CH1: Step-Up DC/DC Converter

CH1 is a step-up converter for motor driver power in DSC system. The converter operates at asynchronous PFM or fixed frequency PWM current mode which can be set by I<sup>2</sup>C.

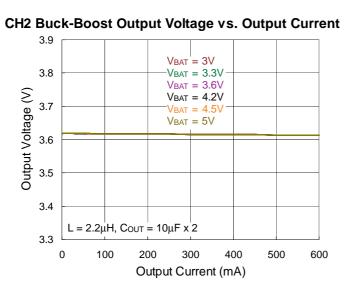

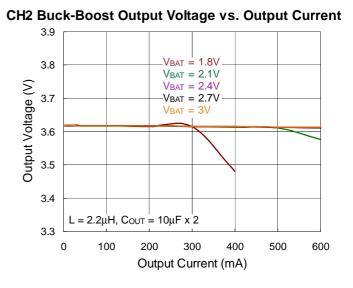

# CH2: Synchronous Step-Up/Down DC/DC Converter

CH2 is a synchronous step-up / down converter for system I/O power. The converter operates at fixed frequency PWM Current Mode.

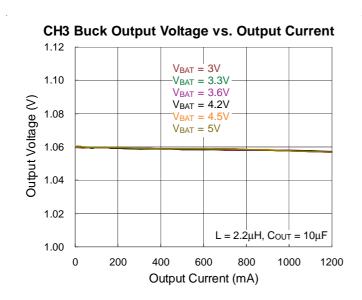

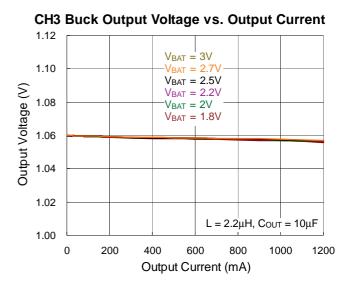

## CH3: Synchronous Step-Down DC/DC Converter

CH3 is suitable for core power in DSC system. The converter operates in fixed frequency PWM mode with integrated internal MOSFETs, FB resistors and compensation network.

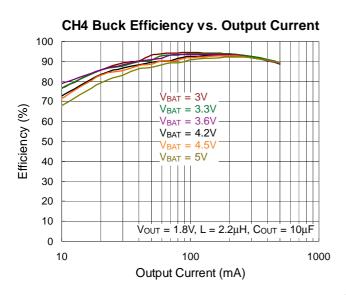

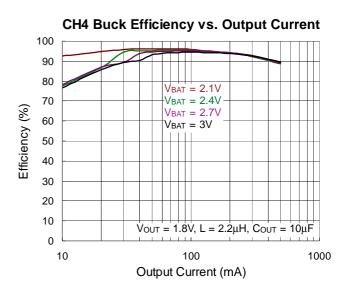

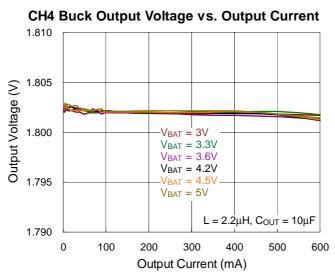

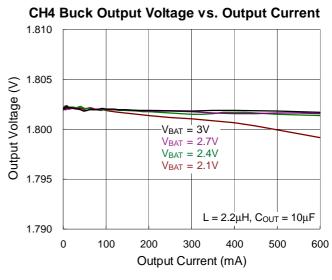

#### CH4: Synchronous Step-Down DC/DC Converter

CH4 is suitable for memory power in DSC system. The converter operates in fixed frequency PWM mode with integrated internal MOSFETs, FB resistors and compensation network.

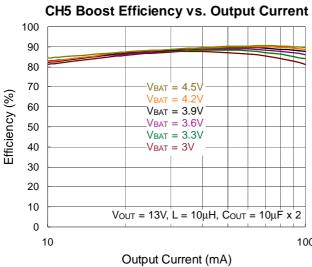

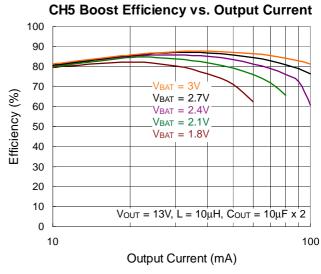

## CH5: Synchronous Step-Up DC/DC Converter

CH5 is a high voltage synchronous step-up converter for CCD positive power. The converter operates at fixed frequency PWM mode, and CCM with integrated internal MOSFETs, compensation network and load disconnect function.

#### CH6: INV DC/DC Converter

This converter integrates an internal P-MOSFET with internal compensation and needs an external Schottky diode to provide CCD negative power supply.

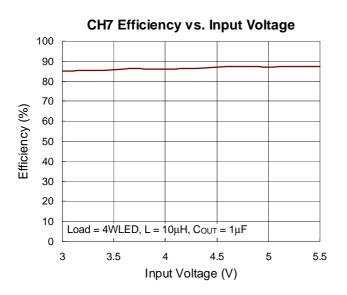

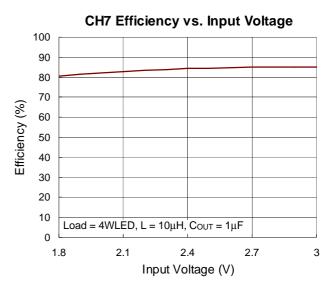

#### **CH7: WLED Driver**

CH7 is a WLED driver that can operate in either current source mode or synchronous step-up mode, as determined by I<sup>2</sup>C interface.

#### CH8: Generic LDO

CH8 is a generic low voltage LDO for multiple purpose power.

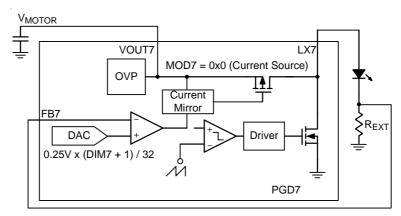

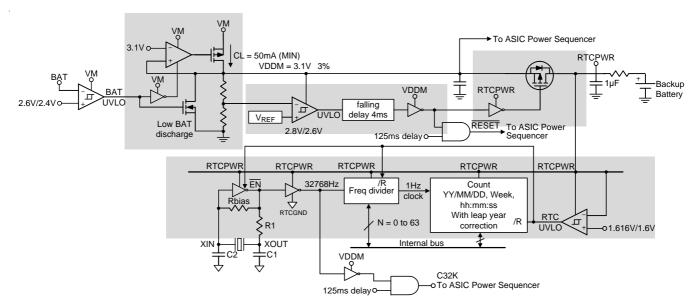

# CH9: Keep Alive LDO and RTC Related Function

The RT9999P provides a 3.1V output LDO for all IC control circuits and real time clock.

### **VNEG Charge Pump**

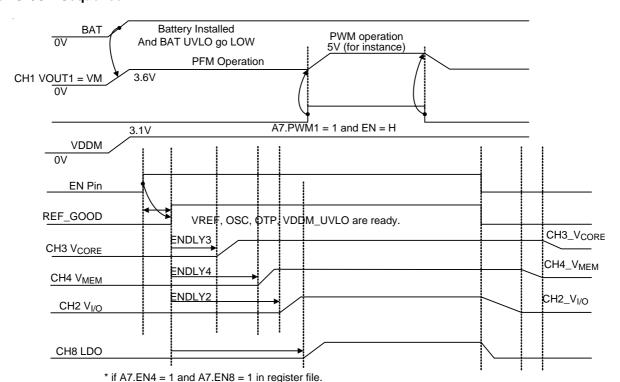

The Charge pump is to increase the Vgs driving of big PMOSFET in Ch2/3/4/6. When BAT < 3.6V and one of Ch2/3/4/6 turns on, VNEG charge pump will turn on and start to pump. As long as BAT doesn't trigger UVLO, CH1 remains active without EN pin = H. However, when A7.PWM1 = 1, EN pin = H and no VDDM UVLO, CH1 will switch from PFM mode to PWM mode. Otherwise, it works in PFM mode. CH2 and CH3 are both enabled by the EN pin and have turn-on delay time as defined in I<sup>2</sup>C register A5. ENDLY2/3. To enable CH4 and CH8, the bits A7.EN4 and A7.EN8 must be set to "1" and EN pin must be high. When the enable bits are set to "1", CH8 will turn on immediately, and CH4 will turn on after a delay time defined by ENDLY4.

# Absolute Maximum Ratings (Note 1)

| • Supply Input Voltage, BAT, VM, PVDD2, PVDD3, PVDD4, PVDD8                 | –0.3V to 6V                 |

|-----------------------------------------------------------------------------|-----------------------------|

| • LX1, LX2A, LX2B, LX3, LX4, CP                                             | –0.3V to 6V                 |

| • LX5, LX7, VOUT5, VOUT7                                                    | –0.3V to 24V                |

| • LX6                                                                       | (BAT – 16V) to (BAT + 0.3V) |

| • VOUT1, VOUT2, VOUT3, VOUT4, VOUT8, RTCPWR, VDDM                           | –0.3V to 6V                 |

| • CN                                                                        | (BAT – 6V) to (BAT + 0.3V)  |

| • VNEG                                                                      | (BAT – 6V) to 0.3V          |

| • VOUT6                                                                     | (BAT – 16V) to 0.3V         |

| • Other Pins                                                                | –0.3V to 6V                 |

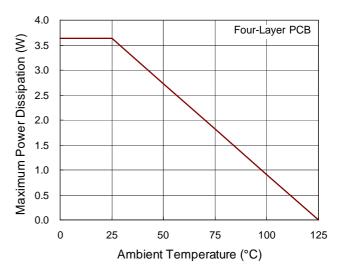

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                             |

| WQFN-40L 5x5                                                                | 3.64W                       |

| Package Thermal Resistance (Note 2)                                         |                             |

| WQFN-40L 5x5, $\theta_{JA}$                                                 | 27.5°C/W                    |

| WQFN-40L 5x5, $\theta_{JC}$                                                 | 6°C/W                       |

| Junction Temperature                                                        | 150°C                       |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C                       |

| Storage Temperature Range                                                   | –65°C to 125°C              |

| ESD Susceptibility (Note 3)                                                 |                             |

| HBM (Human Body Model)                                                      | 2kV                         |

| MM (Machine Model)                                                          | 200V                        |

|                                                                             |                             |

# Recommended Operating Conditions (Note 4)

| • Supply Input Voltage, BAT | 1.8V to 5.5V                                   |

|-----------------------------|------------------------------------------------|

| Junction Temperature Range  | $-40^{\circ}\text{C}$ to $125^{\circ}\text{C}$ |

| Ambient Temperature Range   | –40°C to 85°C                                  |

# **Electrical Characteristics**

( $V_{DDM} = 3.1V$ ,  $T_A = 25$ °C, unless otherwise specified)

| Parameter                                                              | Symbol              | Test Conditions                                                                   | Min | Тур         | Max | Unit |  |  |

|------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------|-----|-------------|-----|------|--|--|

| Supply Voltage                                                         |                     |                                                                                   |     |             |     |      |  |  |

| VM UVLO Threshold Voltage                                              |                     | VM Rising to turn on CH9                                                          |     | BAT<br>-1.1 |     | V    |  |  |

| VDDM Over Voltage Protection                                           |                     |                                                                                   | 5.8 | 6           | 6.2 | V    |  |  |

| VDDM Over Voltage Protection<br>Hysteresis                             |                     |                                                                                   |     | -0.25       | -   | V    |  |  |

| BAT UVLO Threshold Voltage                                             |                     | Rising                                                                            |     | 1.7         | 1.8 | ٧    |  |  |

| BAT UVLO Hysteresis                                                    |                     |                                                                                   |     | 0.2         |     | V    |  |  |

| Supply Current                                                         | Supply Current      |                                                                                   |     |             |     |      |  |  |

| Shutdown Supply Current into VM (including CH9 Keep Alive LDO and RTC) | I <sub>OFF,VM</sub> | $V_{EN}$ = 0V, CH1 No Switching and $V_{M}$ = $V_{OUT1}$ = 4.2V, $V_{BAT}$ = 3.3V |     | 50          | 75  | μА   |  |  |

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

| Parameter                                                                                                                        | Symbol               | Test Conditions                                                                         | Min  | Тур  | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------|------|------|------|------|

| Shutdown Supply Current into BAT                                                                                                 | I <sub>OFF,BAT</sub> | $V_{EN}$ = 0V, CH1 no switching and $V_{M}$ = $V_{OUT1}$ = 4.2V, $V_{BAT}$ = 3.3V       |      | 8    | 15   | μА   |

| CH1 (Async Step-Up PFM) Supply<br>Current into VOUT1                                                                             | I <sub>Q1</sub>      | $V_{EN}$ = 0V, CH1 No Switching<br>and $V_{M}$ = $V_{OUT1}$ = 4.2V,<br>$V_{BAT}$ = 3.3V |      |      | 10   | μΑ   |

| CH2 (Sync Step-Up/Down) + CH3<br>(Syn Step-Down) Supply Current into<br>VDDM                                                     | I <sub>Q23</sub>     | No Switching, V <sub>EN</sub> = 3.3V                                                    |      |      | 1200 | μΑ   |

| CH1 (Sync Step-Up PWM) + CH2<br>(Sync Step-Up/Down) + CH3 (Sync<br>Step-Down) + CH4 (Sync Step-Down)<br>Supply Current into VDDM | I <sub>Q1234</sub>   | No Switching, V <sub>EN</sub> = 3.3V                                                    | 1-   |      | 1600 | μΑ   |

| CH2 (Sync Step-Up/Down) + CH3<br>(Sync Step-Down) + CH4 (Sync<br>Step-Down)<br>Supply Current into VDDM                          | I <sub>Q234</sub>    | No Switching, V <sub>EN</sub> =3.3V                                                     |      |      | 1600 | μА   |

| CH5 (sync Step-Up) Supply Current into VDDM                                                                                      | $I_{Q5}$             | No Switching, V <sub>EN</sub> = 3.3V                                                    |      |      | 400  | μΑ   |

| CH6 (Inverting) Supply Current into VDDM                                                                                         | I <sub>Q6</sub>      | No Switching, V <sub>EN</sub> = 3.3V                                                    |      |      | 400  | μΑ   |

| CH7 (WLED) in Current Source Mode Supply Current into VDDM                                                                       | I <sub>Q7cs</sub>    | V <sub>EN</sub> = 3.3V                                                                  |      |      | 200  | μΑ   |

| CH7 (WLED) in Sync Step-Up Mode<br>Supply Current into VDDM                                                                      | I <sub>Q7bo</sub>    | No Switching, V <sub>EN</sub> = 3.3V                                                    |      |      | 400  | μΑ   |

| CH8 (LDO) Supply Current into VDDM                                                                                               | I <sub>Q8</sub>      | No Load, V <sub>EN</sub> = 3.3V                                                         |      |      | 100  | μА   |

| Oscillator                                                                                                                       |                      |                                                                                         |      |      |      |      |

| CH3, 4 Operation Frequency                                                                                                       | fosc                 |                                                                                         | 1800 | 2000 | 2200 | kHz  |

| CH1, 2, 5, 6, 7 Operation Frequency                                                                                              |                      | CH1 in PWM mode                                                                         | 900  | 1000 | 1100 | kHz  |

| CH1 Maximum Duty Cycle (Step-Up)                                                                                                 |                      |                                                                                         | 91   | 93   | 97   | %    |

| CH2 Maximum Duty Cycle at LX2B                                                                                                   |                      | V <sub>BAT</sub> = 4.2V                                                                 |      | 55   |      | %    |

| CH2 Maximum Duty Cycle at LX2A                                                                                                   |                      |                                                                                         |      |      | 100  | %    |

| CH3 Maximum Duty Cycle (Step-Down)                                                                                               |                      |                                                                                         | -    |      | 100  | %    |

| CH4 Maximum Duty Cycle (Step-Down)                                                                                               |                      |                                                                                         | -    |      | 100  | %    |

| CH5 Maximum Duty Cycle (Step-Up)                                                                                                 |                      |                                                                                         | 91   | 93   | 97   | %    |

| CH6 Maximum Duty Cycle (Inverting)                                                                                               |                      |                                                                                         | 91   | 93   | 97   | %    |

| CH7 Maximum Duty Cycle (WLED)                                                                                                    |                      | Step-up mode                                                                            | 91   | 93   | 97   | %    |

| Parameter                                    | Symbol               | Test Conditions                                                          | Min   | Тур  | Max   | Unit           |

|----------------------------------------------|----------------------|--------------------------------------------------------------------------|-------|------|-------|----------------|

| Feedback and Output Regulation V             | oltage               |                                                                          |       |      |       |                |

| VOUT2, 3, 5, 6 Accuracy                      |                      | VOUTx typical values are listed next.                                    | -1.5  |      | 1.5   | %              |

| VOUT8 Accuracy                               |                      | A3.VOUT8 = 0 to 3                                                        | -1.5  |      | 1.5   | %              |

| VOOTO Accuracy                               |                      | A3.VOUT8 = 4 to 7                                                        | -2    |      | 2     | /0             |

| VOLT4 Acquire ov                             |                      | A1.VOUT4 = 0 to 3                                                        | -1.5  |      | 1.5   | %              |

| VOUT4 Accuracy                               |                      | A1.VOUT4 = 4 to 7                                                        | -2    |      | 2     | <del>7</del> 0 |

| VOLITA Appurpay                              |                      | A0.VOUT1 = 0 to 7                                                        | -1.5  |      | 1.5   | %              |

| VOUT1 Accuracy                               |                      | A0.VOUT1 = 8 to 15                                                       | -2    |      | 2     | <b>%</b>       |

| Feedback Regulation Voltage @ FB6            |                      |                                                                          | 170   | 200  | 230   | mV             |

| (VREF – VFB6) Regulation Voltage             |                      | A2.VOUT6 = 0x7 (for CH6 external feedback)                               | 1.222 | 1.24 | 1.258 | V              |

| VREF Load Regulation                         |                      | VREF = -200μA                                                            |       |      | -10   | mV             |

| Feedback Regulation Voltage @ FB5            |                      | A2.VOUT5 = 0x7 (for CH5 external feedback)                               | 1.232 | 1.25 | 1.268 | V              |

| Feedback Regulation Voltage @ FB7            |                      |                                                                          | 0.237 | 0.25 | 0.263 | V              |

| VDDM Voltage (CH9 Output Regulation)         |                      |                                                                          | 3.01  | 3.1  | 3.19  | <b>V</b>       |

| Power Switch R <sub>ON</sub> and Current Lim | it                   |                                                                          |       |      |       |                |

| CU1 On Decistores of MOSEET                  | В                    | P-MOSFET, V <sub>OUT1</sub> = 3.3V                                       |       | 200  | 250   |                |

| CH1 On Resistance of MOSFET                  | R <sub>DS(ON)</sub>  | N-MOSFET, V <sub>OUT1</sub> = 3.3V                                       |       | 150  | 200   | mΩ             |

| CH1 Current Limitation (Step-Up)             |                      |                                                                          | 2.5   | 3    | 3.5   | Α              |

| CH2 On Resistance of MOSFET                  | Provoul              | P-MOSFET(PVDD2 – LX2A),<br>V <sub>PVDD2</sub> = V <sub>OUT2</sub> = 3.3V | -1    | 150  | 200   | mΩ             |

| CH2 Off Resistance of MOSFET                 | R <sub>DS(ON</sub> ) | N-MOSFET(LX2A – GND),<br>$V_{PVDD2} = V_{OUT2} = 3.3V$                   | 1     | 250  | 350   | 1115.2         |

| CH2 On Begintanes of MOSEET                  | В                    | P-MOSFET (LX2B $-$ VOUT2),<br>$V_{PVDD2} = V_{OUT2} = 3.3V$              | -1    | 200  | 280   | <b></b> 0      |

| CH2 On Resistance of MOSFET                  | R <sub>DS(ON)</sub>  | N-MOSFET (LX2B – GND),<br>V <sub>PVDD2</sub> = V <sub>OUT2</sub> = 3.3V  |       | 150  | 200   | mΩ             |

| CH2 Current Limitation                       |                      | Both P-MOSFET (PVDD2 – LX2A) and N-MOSFET (LX2B – GND)                   | 1.5   | 2    | 2.5   | Α              |

| OHO On Desistant of MOOFFT                   | Б                    | P-MOSFET, V <sub>PVDD3</sub> = 3.3V                                      |       | 200  | 300   | mΩ             |

| CH3 On Resistance of MOSFET                  | R <sub>DS(ON)</sub>  | N-MOSFET, V <sub>PVDD3</sub> = 3.3V                                      |       | 150  | 220   |                |

| CH3 Current Limitation (Step-Down)           |                      |                                                                          | 1.5   | 2    | 2.5   | А              |

| Paramete                            | er             | Symbol              | Test Conditions                                                                       | Min | Тур | Max | Unit |

|-------------------------------------|----------------|---------------------|---------------------------------------------------------------------------------------|-----|-----|-----|------|

| CH4 On Resistance of MOSFET         |                | Б                   | P-MOSFET, V <sub>PVDD4</sub> = 3.3V                                                   |     | 350 | 400 | 0    |

|                                     |                | R <sub>DS(ON)</sub> | N-MOSFET, V <sub>PVDD4</sub> = 3.3V                                                   |     | 350 | 400 | mΩ   |

| CH4 Current Limitati<br>(Step-Down) | on             |                     |                                                                                       | 1   | 1.5 | 2   | Α    |

|                                     | ~{ MOCEET      |                     | P-MOSFET, V <sub>OUT5</sub> = 3.3V                                                    |     | 1.2 | 1.5 |      |

| CH5 On Resistance                   | OI WOSFET      |                     | N-MOSFET, V <sub>DDM</sub> = 3.1V                                                     |     | 0.6 | 0.8 | Ω    |

| CH5 Current Limitati                | on             |                     | N-MOSFET                                                                              | 0.9 | 1.2 | 1.5 | Α    |

| CH6 On Resistance                   | of MOSFET      |                     | P-MOSFET, V <sub>BAT</sub> = 3.3V                                                     |     | 0.6 | 0.8 | Ω    |

| CH6 Current Limitati                | on             |                     | P-MOSFET, V <sub>BAT</sub> = 3.3V                                                     | 1   | 1.5 | 2   | Α    |

| CLIZ On Desintance                  | ~{ MOCEET      |                     | N-MOSFET                                                                              |     | 0.9 | 1.1 |      |

| CH7 On Resistance                   | OI WOSFET      |                     | P-MOSFET                                                                              |     | 2.0 | 3.0 | Ω    |

| CH7 Current Limitati                | on             |                     | N-MOSFET                                                                              | 0.6 | 0.8 | 1   | Α    |

| Control                             |                |                     |                                                                                       | •   |     |     |      |

| MSEL Input                          | Logic-High     |                     |                                                                                       | 1.3 |     |     | V    |

| Threshold Voltage                   | Logic-Low      |                     |                                                                                       |     |     | 0.4 | \ \  |

| MCEL Cink Current                   |                |                     | EN = High                                                                             |     | 1   | 3   | _    |

| MSEL Sink Current                   |                |                     | EN = Low                                                                              |     |     | 0.5 | μΑ   |

| EN Input Threshold                  | Logic-High     |                     |                                                                                       | 1.3 |     |     | V    |

| Voltage                             | Logic-Low      |                     |                                                                                       |     |     | 0.4 | V    |

| EN Sink Current                     |                |                     |                                                                                       |     | 1   | 3   | μА   |

| Thermal Protection                  | 1              |                     |                                                                                       |     |     |     |      |

| Thermal Shutdown                    |                | T <sub>SD</sub>     |                                                                                       | 125 | 160 |     | °C   |

| Thermal Shutdown F                  | Hysteresis     | $\Delta T_{SD}$     |                                                                                       |     | 20  |     | °C   |

| VNEG Charge Pum                     | p              |                     |                                                                                       | •   |     |     |      |

| Charge Pump Low T<br>Start          | hreshold to    | NV <sub>ST</sub>    | Monitor BAT Falling                                                                   | 3.4 | 3.6 | 3.8 | V    |

| Charge Pump Hyste                   | resis Gap to   | 4 NIV/              |                                                                                       | 0.1 | 0.2 | 0.3 |      |

| Stop (BAT-VNEG) Clamp Level         |                | ΔNV <sub>ST</sub>   |                                                                                       | 4.1 | 4.5 | 4.9 | V    |

| CH8 LDO                             |                |                     |                                                                                       |     |     |     |      |

| Supply Voltage of Cl                | <del>1</del> 8 | V <sub>PVDD8</sub>  |                                                                                       | 2.7 |     | 5.5 | ٧    |

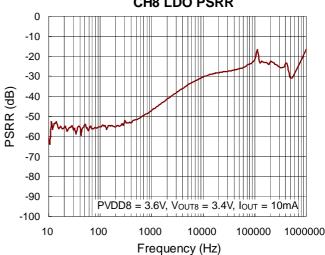

| PSRR+ of CH8                        |                |                     | 1kHz, I <sub>OUT</sub> = 10mA,<br>V <sub>PVDD8</sub> = 3.6V, V <sub>OUT8</sub> = 3.4V |     | -40 |     | dB   |

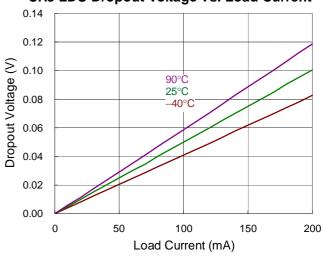

| CH8 Dropout Voltage                 | е              |                     | V <sub>OUT8</sub> = 3.4V, I <sub>OUT</sub> = 100mA                                    |     | 40  | 60  | mV   |

| CH8 Current Limitati                | on             |                     | V <sub>OUT8</sub> = 3.4V                                                              | 220 | 300 | 380 | mA   |

|                                     |                |                     | •                                                                                     | •   | •   |     |      |

| Parameter                                | Symbol             | Test Conditions                                            | Min                         | Тур    | Max          | Unit |

|------------------------------------------|--------------------|------------------------------------------------------------|-----------------------------|--------|--------------|------|

| CH9 Keep Alive LDO                       |                    |                                                            |                             |        |              |      |

| Supply Voltage of CH9 at VM Pin          |                    |                                                            | 2.4                         |        | 5.5          | V    |

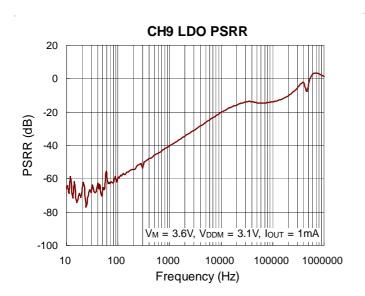

| PSRR+ of CH9                             |                    | 1kHz, $I_{OUT} = 1$ mA, $V_{M} = 3.6$ V, $V_{DDM} = 3.1$ V |                             | -40    |              | dB   |

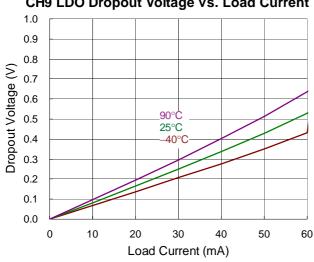

| CH9 Dropout Voltage                      |                    | $V_{DDM} = 3.1V$ , $I_{OUT} = 20$ mA                       |                             | 170    | 200          | mV   |

| Current Limit of CH9                     |                    | V <sub>DDM</sub> = 3.1V                                    | 50                          | 100    |              | mA   |

| RESET Hysteresis Low                     |                    | RESET Falling                                              | 2.55                        | 2.6    |              | V    |

| RESET Hysteresis High                    |                    | RESET Rising                                               |                             | 2.8    | 2.86         | V    |

| RESET Rising Delay Time                  |                    |                                                            |                             |        | 0.5          | S    |

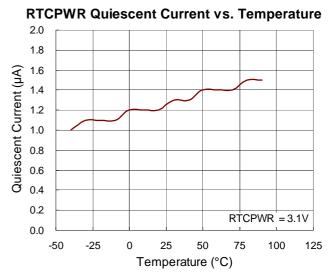

| CH9 Quiescent Current                    |                    | Excluding RTC Quiescent Current                            |                             | 4      | 8            | μΑ   |

| RTC                                      |                    |                                                            |                             |        |              |      |

| RTC Operation Voltage                    |                    |                                                            | 1.6                         |        | 3.3          | V    |

| RTC Quiescent Current                    |                    | Including RTC_UVLO, RTC_OSC, and Time Counter              |                             |        | 2            | μΑ   |

| RTC Off Quiescent Current                |                    | When RTC RESET (UVLO) occurred                             |                             |        | 0.2          | μΑ   |

| RTC Clock                                |                    |                                                            |                             | 32.768 |              | kHz  |

| RTC Clock Accuracy                       |                    | V <sub>RTCPWR</sub> = 1.6V to 3.3V                         | -10                         |        | 10           | ppm  |

| RTC Clock Output High                    |                    | C32K pin source out 0.1mA                                  | V <sub>DDM</sub><br>- 0.3   |        |              | V    |

| RTC Clock Output Low                     |                    | C32K pin sink 0.1mA                                        |                             |        | 0.3          | V    |

| RTC RESET (UVLO)                         | V <sub>RTC_F</sub> | RTCPWR Falling                                             | 1.5                         | 1.6    | 1.7          | V    |

| RTC RESET POR                            | V <sub>RTC_R</sub> | RTCPWR Rising                                              | V <sub>RTC_F</sub><br>+ 20m | 1.9    | 2            | V    |

| RTC Osc Startup Time                     |                    |                                                            |                             |        | 1            | s    |

| Switch On Resistance from VDDM to RTCPWR |                    | P-MOSFET, V <sub>DDM</sub> = 3.1V                          |                             | 30     | -            | Ω    |

| Under Voltage and Over Voltage           | Protectio          | n                                                          |                             |        |              |      |

| CH1 OVP Threshold @ VOUT1                |                    |                                                            | 5.8                         | 6      | 6.2          | V    |

| CH2 OVP Threshold @ VOUT2                |                    |                                                            | 5.8                         | 6      | 6.2          | V    |

| CH5 OVP Threshold @ VOUT5                |                    |                                                            | 20                          | 21     | 22           | V    |

| CH6 OVP Threshold @ VOUT6                |                    |                                                            |                             | -13    |              | V    |

| CH7 OVP Threshold Accuracy @ VOUT7       |                    | Target voltage is the one chosen in A4.OVP7                | Target<br>-1                | Target | Target<br>+1 | V    |

| CH1 UVP Threshold @ VOUT1                |                    | For PWM Mode                                               | 1.95                        | 2.25   | 2.55         | V    |

| CH2 UVP Threshold @ VOUT2                |                    |                                                            | 1.4                         | 1.6    | 1.8          | V    |

| Paramet                                                               | er                    | Symbol              | Test Conditions                                        | Min                        | Тур              | Max                        | Unit                                  |

|-----------------------------------------------------------------------|-----------------------|---------------------|--------------------------------------------------------|----------------------------|------------------|----------------------------|---------------------------------------|

| CH3 UVP Threshold                                                     | d @ VOUT3             |                     |                                                        | 0.525                      | 0.6              | 0.675                      | V                                     |

| CH4 UVP Threshold                                                     | d @ VOUT4             |                     |                                                        | 0.7                        | 0.8              | 0.9                        | V                                     |

| CH5 UVP Threshold                                                     | d @ FB5               |                     |                                                        | 0.5                        | 0.6              | 0.7                        | V                                     |

| CH6 UVP Threshold                                                     | d @ FB6               |                     |                                                        | 0.4                        | 0.5              | 0.6                        | V                                     |

| CH8 UVP Threshold                                                     | 8TUOV ® b             |                     | Target voltage is the one chosen in A3.VOUT8           |                            | 0.5 x<br>Target  |                            | V                                     |

| CH1 Over Load P T (OLP) @ VOUT1                                       | hreshold              |                     | Target voltage is the one chosen in A0.VOUT1           |                            | Target –<br>0.6  |                            | V                                     |

| CH2 OLP Threshold                                                     | d @ VOUT2             |                     | Target voltage is the one chosen in A0.VOUT2           |                            | Target –<br>0.4  |                            | V                                     |

| CH3 OLP Threshold                                                     | d @ VOUT3             |                     | Target voltage is the one chosen in A1.VOUT3           |                            | Target –<br>0.15 |                            | V                                     |

| CH4 OLP Threshold                                                     | d @ VOUT4             |                     | Target voltage is the one chosen in A1.VOUT4           |                            | Target –<br>0.2  |                            | V                                     |

| CH5 OLP Threshold                                                     | d @ VOUT5             |                     | Target voltage is the one chosen in A2.VOUT5           |                            | Target –<br>1.8  |                            | V                                     |

| CH6 OLP Threshold                                                     | d @ FB6               |                     | A2.VOUT6 = 0x7                                         | 0.3                        | 0.35             | 0.4                        | V                                     |

| Protection Delay Tir                                                  | Protection Delay Time |                     | For OCP and OLP, except OCP of CH2                     |                            | 100              | -                          | ms                                    |

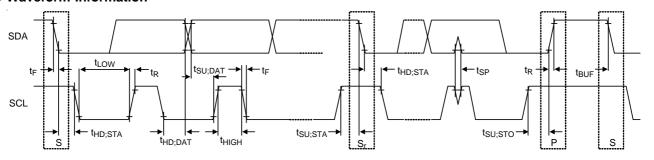

| I <sup>2</sup> C Interface                                            |                       |                     |                                                        |                            |                  |                            |                                       |

| SDA, SCLK Input                                                       | Logic-High            |                     | V <sub>OUT2</sub> = 3.3V                               | 0.7 x<br>V <sub>OUT2</sub> |                  |                            | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| Threshold Voltage                                                     | Logic-Low             |                     | V <sub>OUT2</sub> = 3.3V                               |                            |                  | 0.3 x<br>V <sub>OUT2</sub> | V                                     |

| SCLK Clock Rate                                                       |                       | f <sub>SCL</sub>    | V <sub>OUT2</sub> = 3.3V                               |                            |                  | 400                        | kHz                                   |

| Hold Time for Repe<br>Condition (After this<br>first clock pulse is g | period, the           | t <sub>HD;STA</sub> | V <sub>OUT2</sub> = 3.3V                               | 0.6                        |                  |                            | μS                                    |

| LOW Period of SCL                                                     | . Clock               | t <sub>LOW</sub>    | V <sub>OUT2</sub> = 3.3V                               | 1.3                        |                  |                            | μS                                    |

| HIGH Period of SCI                                                    | _ Clock               | tHIGH               | V <sub>OUT2</sub> = 3.3V                               | 0.6                        |                  |                            | μS                                    |

| Set-up Time for Rep<br>START<br>Condition                             | peated                | t <sub>SU;STA</sub> | V <sub>OUT2</sub> = 3.3V                               | 0.6                        | 1                | -1                         | μS                                    |

| Data Hold Time                                                        |                       | t <sub>HD;DAT</sub> | V <sub>OUT2</sub> = 3.3V                               | 0                          |                  | 0.9                        | μS                                    |

| Data Set-up Time                                                      |                       | t <sub>SU;DAT</sub> | V <sub>OUT2</sub> = 3.3V                               | 100                        |                  |                            | ns                                    |

| Set-up Time for STO                                                   | OP Condition          | tsu;sto             | V <sub>OUT2</sub> = 3.3V                               | 0.6                        |                  |                            | μS                                    |

| Bus Free Time betwand START Condition                                 |                       | t <sub>BUF</sub>    | V <sub>OUT2</sub> = 3.3V                               | 1.3                        | 1                | -                          | μS                                    |

| Rise Time of Both S<br>Signals                                        | DA and SCL            | t <sub>R</sub>      | V <sub>OUT2</sub> = 3.3V                               | 20                         |                  | 300                        | ns                                    |

| Fall Time of Both SI Signals                                          | DA and SCL            | t <sub>F</sub>      | V <sub>OUT2</sub> = 3.3V                               | 20                         | -1               | 300                        | ns                                    |

| SDA and SCL Outp<br>Current                                           | ut Low Sink           | I <sub>OL</sub>     | SDA or SCL voltage = 0.4V,<br>V <sub>OUT2</sub> = 3.3V | 2                          |                  |                            | mA                                    |

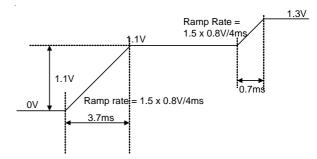

| Parameter                                                   | Symbol | Test Conditions                                                | Min  | Тур   | Max  | Unit |

|-------------------------------------------------------------|--------|----------------------------------------------------------------|------|-------|------|------|

| Output Voltage Ramp Rate                                    |        |                                                                |      |       | •    | •    |

| VOUT1 Ramp Rate                                             |        | V <sub>OUT1</sub> = 3.6V to 5.3V                               |      | 1.24  |      | V/ms |

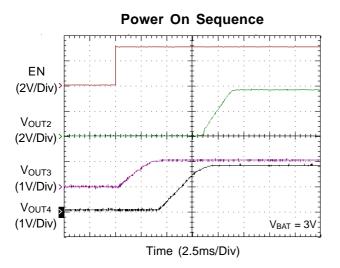

| VOUT2 Ramp Rate                                             |        | V <sub>OUT2</sub> = 0V to 3.25V                                |      | 0.82  |      | V/ms |

| VOUT3 Ramp Rate                                             |        | V <sub>OUT3</sub> = 0V to 1.1V                                 |      | 0.33  |      | V/ms |

| VOUT4 Ramp Rate                                             |        | V <sub>OUT4</sub> = 0V to 1.8V                                 |      | 0.44  |      | V/ms |

| VOUT5 Ramp Rate                                             |        | V <sub>OUT5</sub> = 0V to 13V,<br>A2.VOUT5 [2:0] is not 0x7.   |      | 1.6   |      | V/ms |

| FB5 Reference Ramp Rate (CH5 external feedback)             |        | V <sub>FB5</sub> = 0V to 1.25V,<br>A2.VOUT5 [2:0] = 0x7        |      | 0.133 |      | V/ms |

| VOUT6 Ramp Rate                                             |        | V <sub>OUT6</sub> = 0V to -7.5V,<br>A2.VOUT6 [2:0] is not 0x7. |      | 0.8   |      | V/ms |

| VREF Ramp Rate (CH6 external feedback)                      |        | V <sub>REF</sub> = 0V to 1.24V,<br>A2.VOUT6 [2:0] = 0x7        |      | 0.125 |      | V/ms |

| VOUT8 Ramp Rate                                             |        | V <sub>OUT8</sub> = 0V to 3.4V                                 | 1    | 0.84  | -    | V/ms |

| Ramp Rate Accuracy                                          |        | (For all ramp rates listed above)                              | -40  |       | 40   | %    |

| <b>Enabling Delay Time</b>                                  |        |                                                                |      |       |      |      |

| Delay Time Step Resolution                                  |        | For ENDLY2, 3, 4 at A5, A6                                     |      | 2     |      | ms   |

| Off Discharge                                               |        |                                                                |      |       |      |      |

| VOUT2, 3, 4, 5, 7 Discharge<br>Equivalent Resistance        |        | V <sub>OUTx</sub> = 1V                                         | 50   |       |      | Ω    |

| VOUT6 Discharge Equivalent Resistance                       |        | V <sub>OUT6</sub> = -1V                                        | 100  |       |      | Ω    |

| VOUT8 Discharge Equivalent Resistance                       |        | V <sub>OUT8</sub> = 1V                                         | 200  |       |      | Ω    |

| VDDM Discharge Equivalent Resistance                        |        | $V_M = 4.2V$ and $V_{DDM} = 1V$                                | 200  |       |      | Ω    |

| CH2 Discharge Finish Threshold for CH3 Starting to Turn Off |        |                                                                | 0.05 | 0.1   | 0.15 | V    |

| CH4 Discharge Finish Threshold for CH3 Starting to Turn Off |        | CH3 will wait for CH4 to discharge only when A1.DIS4 = 1       | 0.05 | 0.1   | 0.15 | V    |

| CH1 Asynchronous PFM                                        |        |                                                                |      |       |      |      |

| N-MOSFET On-Time                                            |        | V <sub>M</sub> = 3.6V                                          |      | 0.5   |      | μS   |

| Minimum Off-Time                                            |        | V <sub>M</sub> = 3.6V                                          |      | 0.5   |      | μS   |

| N-MOSFET Current Limit                                      |        | V <sub>M</sub> = 3.6V                                          |      | 0.8   |      | Α    |

| N-MOSFET On Resistance                                      |        | V <sub>M</sub> = 3.6V, (the same as PWM mode)                  | -    | 150   | 200  | mΩ   |

| VOUT1 Regulation Voltage                                    |        | V <sub>M</sub> = 3.6V                                          | 3.5  | 3.6   | 3.7  | V    |

# **RT9999P**

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

# **Typical Application Circuit**

Figure 1. Application for  $V_{MEM} = 2.1V$

Copyright © 2019 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

Figure 2. Application for  $V_{MEM} = 1.8V$

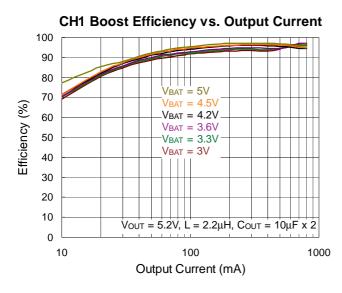

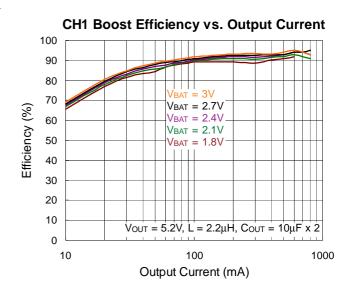

# **Typical Operating Characteristics**

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

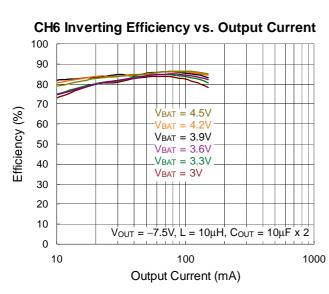

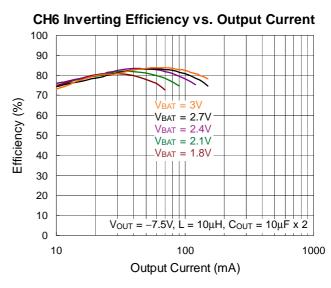

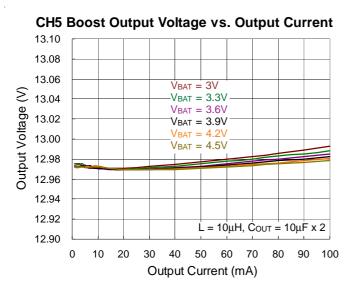

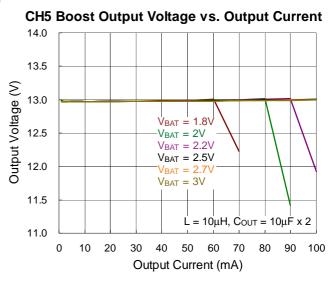

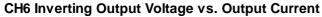

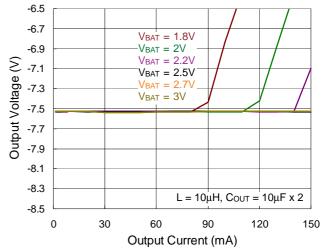

## CH6 Inverting Output Voltage vs. Output Current

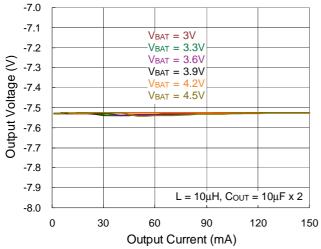

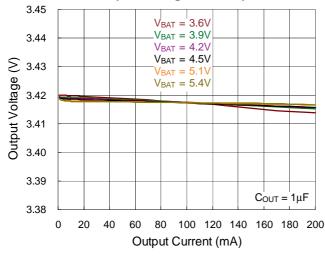

## CH8 LDO Output Voltage vs. Output Current

#### CH8 LDO Dropout Voltage vs. Load Current

## CH9 LDO Dropout Voltage vs. Load Current

**CH8 LDO PSRR**

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **Application Information**

The RT9999P is a highly-integrated DSC Power Management IC that contains 7CH switching DC/DC converters and one generic LDO, one keep-alive low-quiescent LDO, a switch with reverse leakage prevention from backup battery, and a Real-Time-Clock (RTC) including time counter and 32768Hz oscillator.

CH1: Step-up operated in either Async PFM or Sync PWM current mode DC/DC converter. It includes internal power MOSFETs, compensation network and FB resistors. The P-MOSFET body can be controlled to disconnect the load. This is suitable for power of DSC Motor.

CH2: Step-up/down (Buck-Boost) synchronous current mode DC/DC converter with internal power MOSFETs, compensation network and FB resistors. This channel supplies the power for I/O. This channel is always operated at CCM.

CH3: Step-down synchronous current mode DC/DC converter with internal power MOSFETs, compensation network and FB resistors. This channel supplies the power for core. It can be operated at 100% maximum duty cycle to extend battery operating voltage range.

CH4: Step-down synchronous current mode DC/DC converter with internal power MOSFETs, compensation network and FB resistors. This channel supplies the power for Memory. It can be operated at 100% maximum duty cycle to extend battery operating voltage range.

CH5: High voltage step-up synchronous current mode DC/DC converter with internal power MOSFETs, compensation network and FB resistors. The P-MOSFET

body can be controlled to disconnect the load. This channel supplies the CCD+ bias.

CH6: Asynchronous inverting current mode DC/DC converter with internal power MOSFET, compensation network and FB resistors. It needs an external Schottky diode. This channel supplies the CCD- bias.

CH7: A WLED driver operating in either current source mode or synchronous step-up mode with internal P-MOSFET and compensation network. WLED current and dimming level is determined by I<sup>2</sup>C interface. The P-MOSFET body in step-up mode can be controlled to disconnect the load.

CH3 and CH4 operate in PWM mode with 2MHz, while CH1, CH2, CH5, CH6 and CH7 operate in PWM mode with 1MHz switching frequency.

CH8 : A generic LDO output voltage is controlled by I<sup>2</sup>C interface. This supplies the multiple purpose power.

CH9 : A keep-alive LDO supplies the power for backup battery.

## CH1: Step-Up DC/DC Converter

CH1 is a step-up converter for motor driver power in DSC system. The converter operates at async PFM or fixed frequency PWM current mode which can be set by I<sup>2</sup>C. The converter integrates internal MOSFETs, FB resistors, compensation network and synchronous rectifier for up to 95% efficiency. The output voltage of CH1 is adjustable by the I<sup>2</sup>C interface in the range of 3.6V to 5.3V.

CH1 operates at async PFM mode, LX1 switch as below waveform:

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

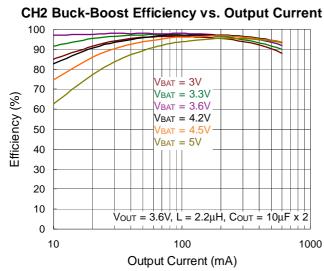

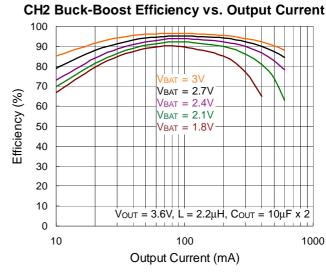

# CH2 : Synchronous Step-Up / down DC/DC Converter

CH2 is a synchronous step-up / down converter for system I/O power. The converter operates at fixed frequency PWM Current Mode. The converter integrates internal MOSFETs, FB resistors, compensation network and synchronous rectifier for up to 95% efficiency.

The output voltage of CH2 can be adjusted by the I<sup>2</sup>C interface.

### **VNEG Charge Pump**

The Charge pump is to increase the Vgs driving of big P-MOSFET in CH2/3/4/6.

When BAT < 3.6V and one of CH2/3/4/6 turns on, VNEG charge pump would turn on and start to pump. But when pumping, the BAT threshold to turn off and stop charge pump becomes 3.9V.

When pumping, the (BAT - VNEG) voltage would be clamped at 4.5V. But because of charge pumping architecture limitation, most negative level of the VNEG is only (-BAT).

Hence, if BAT < 4.5 / 2 = 2.25V, VNEG is limited to (–BAT).

When VNEG charge pump is off, VNEG is connected internally to GND.

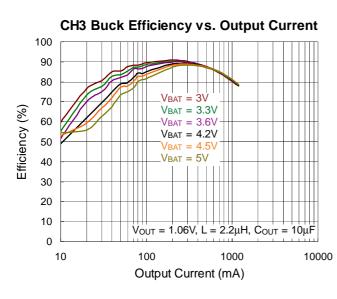

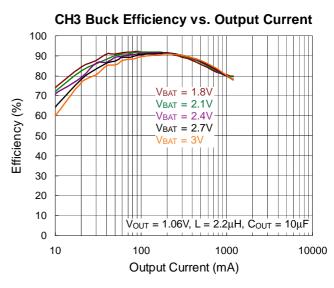

#### CH3: Synchronous Step-Down DC/DC Converter

CH3 is suitable for core power in DSC system. The converter operates in fixed frequency PWM mode with integrated internal MOSFETs, FB resistors and compensation network. The CH3 step-down converter can be operated at 100% maximum duty cycle to extend battery operating voltage range.

The output voltage of CH3 is adjustable by the I<sup>2</sup>C interface in the range of 1.3V to 1V.

## CH4: Synchronous Step-Down DC/DC Converter

CH4 is suitable for memory power in DSC system. The converter operates in fixed frequency PWM mode with integrated internal MOSFETs, FB resistors and compensation network. The CH4 step-down converter can be operated at 100% maximum duty cycle to extend battery operating voltage range.

The output voltage of CH4 is adjustable by the I<sup>2</sup>C interface.

## CH5: Synchronous Step-Up DC/DC Converter

CH5 is a high voltage synchronous step-up converter for CCD positive power. The converter operates at fixed frequency PWM mode, and CCM with integrated internal MOSFETs, compensation network and load disconnect function.

The output voltage of CH5 is adjustable by the I<sup>2</sup>C interface in the range of 15V to 12V or set by external feedback resistors.

The equation is as follows:

$V_{OUT\_CH5} = (1 + R1 / R2) \times V_{FB5}$

V<sub>FB5</sub> is 1.25V typically.

#### CH6: INV DC/DC Converter

This converter integrates an internal P-MOSFET with internal compensation and needs an external Schottky diode to provide CCD negative power supply.

The output voltage of CH6 is adjustable by the  $I^2C$  interface in the range of -5V to -8V or set by external feedback resistors.

The equations are as follows:

$V_{OUT\ CH6} = 0.2 - (R3 / R4) \times 1.24 V$

Where R3 and R4 feedback resistors are connected to FB6, 1.24V equals to  $(V_{REF} - V_{FB6})$ .

## Reference Voltage

The RT9999P provides a precise 1.24V to 1.84V reference voltage, VREF, with souring capability of  $200\mu A$ . Connect a  $0.1\mu F$  ceramic capacitor from the VREF pin to GND. Reference voltage is enabled by I<sup>2</sup>C interface. Furthermore, this reference voltage is internally pulled to GND at shutdown.

## **CH7: WLED Driver**

CH7 is a WLED driver that can operate in either current source mode or synchronous step-up mode, as determined by I<sup>2</sup>C interface. When CH7 works in current source mode, it sources an LED current out of LX7 pin and regulates the current by FB7 voltage. The LED current is defined by FB7 voltage and the external resistor between FB7 and

GND. The FB7 regulation voltage can be set in 32 steps from 7.8mV to 250mV, typically, via I<sup>2</sup>C interface. If CH7 works in synchronous step-up mode, it integrates synchronous step-up mode with an internal MOSFET and

internal compensation. The LED current is also set via an external resistor and FB7 regulation voltage.

#### **CH7 WLED Current Dimming Control**

If CH7 is in synchronous step-up mode or current source mode, the WLED current is set by an external resistor. Regardless of the mode, dimming is always controlled by I<sup>2</sup>C interface.

The WLED current can be set by the following equation:

$$I_{LED}$$

(mA) = [250mV / R (W)] x (DIM7 + 1) / 32

R is the current sense resistor from FB7 to GND and (DIM + 1) / 32 ratio refers to I<sup>2</sup>C control register file.

\* Register DIM7 defines dimming FB7 regulation voltage for Both Sync Step-Up mode and Current Source mode. The regulation voltage = 0.25V x (DIM7 + 1) / 32, where (DIM7 + 1) / 32 = 1/32 to 32/32.

0.25V voltage with accuracy  $\pm 5\%.$   $I_{LED}$  max is defined by the 0.25V/Rext.

#### CH8: Generic LDO

CH8 is a generic low voltage LDO for multiple purpose power.

The CH8 is a linear regulator, designed to be stable over the entire operating load range with the use of external ceramic capacitors. CH8 have an ON/OFF control which can be set by  $I^2C$  commands. The output voltage of CH8 is adjustable by the  $I^2C$  interface in the range of 3.5V to 1.5V.

# CH9 : Keep Alive LDO and RTC Related Function Block

The RT9999P provides a 3.1V output LDO for all IC control circuits and real time clock. The LDO features low quiescent current (4 $\mu$ A) and high output voltage accuracy. This LDO is always on, even when the system is shut down. For better stability, it is recommended to connect a 1 $\mu$ F to the VDDM pin. The RTCPWR switch avoids backcharging from the RTCPWR node into the input node VDDM.

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

The Frequency Divider from 32768Hz to 1Hz would generate the below 1Hz wave that has a little jitter but the 1Hz average frequency can be finely tuned.

Fine tune 1Hz by digital divider can create tuning range =  $(-60 \text{ to } 67) / (32768\text{Hz} \times 60\text{s}) = -30 \text{ to } 33 \text{ ppm}$  each tune step size = 0.5 ppm.

But the 1Hz would include jitter and the C32K still is not tuned.

## **RTC Time Read/Write Method**

When reading RTC time via I<sup>2</sup>C interface, suggest reading 6 bytes (address A11 to A16) together and finish reading within 0.5 second to avoid the second carry issue. A16. RTCT\_SEC [0] can be used for checking whether second is carried during reading time.

When writing RTC time via I<sup>2</sup>C interface, suggest writing 6 bytes (address A11 to A16) together. A11 is first and then A12, A13, A14, A15, A16. Suggest finishing writing within 0.5 second to avoid second carry issue during writing.

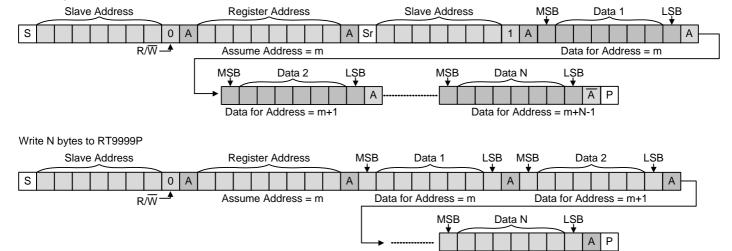

## I<sup>2</sup>C Register Information

The RT9999P I<sup>2</sup>C interface power must be supplied by either VOUT2 or an equal potential node. If  $\overline{RESET}$  = Low, I<sup>2</sup>C read/write can not function.

Driven by Slave (RT9999P),

The RT9999P I<sup>2</sup>C slave address = 0011000 (7bits). I<sup>2</sup>C interface supports fast mode (bit rate up to 400kb/s). The write or read bit stream (N  $\geq$  1) is shown below :

Data for Address = m+N-1

Read N bytes from RT9999P

P Stop, S Start, Sr Repeat Start

#### I<sup>2</sup>C Waveform Information

Driven by Master,

## I<sup>2</sup>C Register File

| Address | Register | (MSB)    |       | Bit Map, | Read/Wri | te, Default va | alue |       | (LSB) |

|---------|----------|----------|-------|----------|----------|----------------|------|-------|-------|

| Name    | Address  | b[7]     | b[6]  | b[5]     | b[4]     | b[3]           | b[2] | b[1]  | b[0]  |

|         |          |          | VOU   | Γ1       |          | Reserved       |      | VOUT2 |       |

| A0      | 0x00     |          | R/W   | 1        |          |                |      | R/W   |       |

|         |          | 0        | 0     | 0        | 1        | х              | 0    | 0     | 1     |

|         |          |          | VOUT  | Γ3       |          | DIS4           |      | VOUT4 |       |

| A1      | 0x01     |          | R/W   | 1        |          | R/W            |      | R/W   |       |

|         |          | 1        | 1     | 0        | 0        | 1              | MSEL | 0     | 1     |

|         |          | Reserved |       | VOUT5    |          | Reserved       |      | VOUT6 |       |

| A2      | 0x02     |          |       | RW       |          |                |      | R/W   |       |

|         |          | х        | 1     | 0        | 0        | х              | 1    | 0     | 1     |

|         |          |          | VOUT8 |          |          |                | DIM7 |       |       |

| A3      | 0x03     |          | RW    |          |          |                | R/W  |       |       |

|         |          | 0        | 0     | 1        | 1        | 1              | 1    | 1     | 1     |

Copyright ©2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

| Address | Register | (MSB)           |          | Bit Map,              | Read/Wri | te, Default va | alue     |         | (LSB) |

|---------|----------|-----------------|----------|-----------------------|----------|----------------|----------|---------|-------|

| Name    | Address  | b[7]            | b[6]     | b[5]                  | b[4]     | b[3]           | b[2]     | b[1]    | b[0]  |

|         |          |                 | Reserv   | /ed                   | •        | MOD7           |          | OVP7    |       |

| A4      | 0x04     |                 |          |                       |          | R/W            |          | R/W     |       |

|         |          | Х               | Х        | х                     | х        | 0              | 1        | 1       | 0     |

|         |          |                 | ENDL     | Y3                    |          |                | ENDL     | Y2      |       |

| A5 0x05 |          |                 | R/W      | 1                     |          |                | R/V      | V       |       |

|         |          | 0               | 0        | 0                     | 0        | 0              | 1        | 0       | 0     |