# 2.1MHz, 20A Multi-Phase Step-Down Converter with I<sup>2</sup>C Interface

#### **General Description**

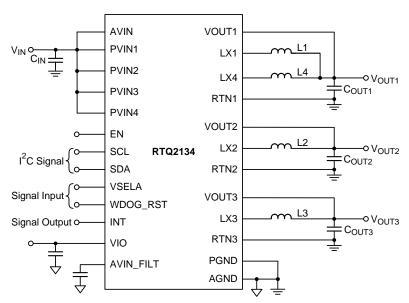

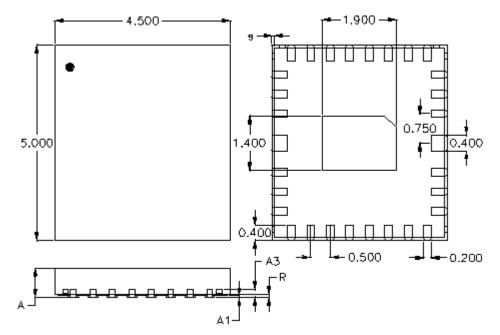

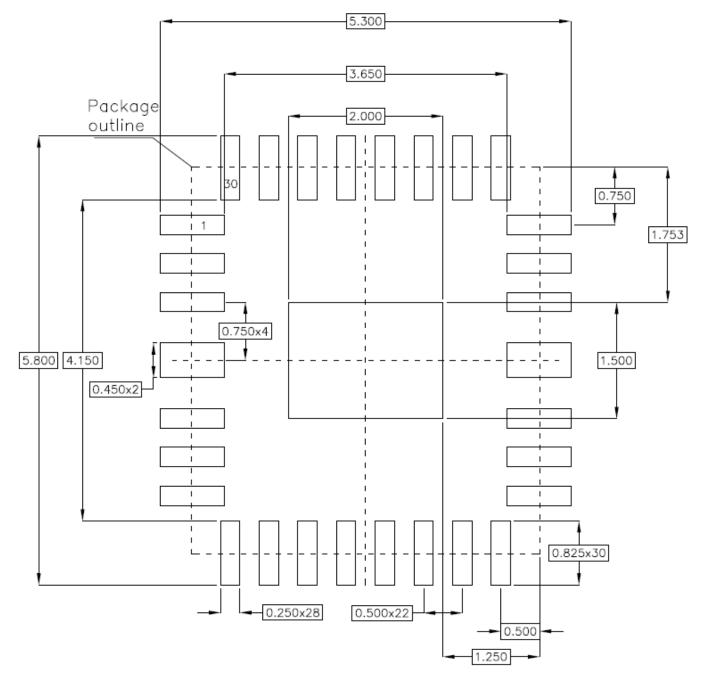

The RTQ2134 is a multi-phase, programmable power management IC that integrates with four high efficient, synchronous step-down converter cores. The RTQ2134 can be 2 + 2 and 2 + 1 + 1 output by OTP. It also features wide output voltage range and the capability to configure the corresponding power stages, which make the device optimized to meet power management requirements for low-power processors, such as core power for CPUs and GPUs. The RTQ2134 supports many programmable functions including voltage level, slew rate of voltage change, and slew rate of soft-start via an I2C interface capable of operating up to 3.4MHz. The RTQ2134 also supports remote-sense function to get accurate output voltage at large loading. Moreover, the device has interrupt and fault-detection function to report error status. The RTQ2134 is available in a WET-WQFN-30L 4.5x5 (FC) package.

#### **Applications**

Automotive Systems

#### Features

- FMEA Compliant PinOut

- AEC-Q100 Grade1 Qualified

- 2 + 2/2 + 1 + 1 Phase Output

- I<sup>2</sup>C Programmable Output Voltage: 0.3V to 1.85V

- Maximum Output Current: Total 20A, 5.5A per Phase

- Output Remote Sense

- Fast Transient Response

- Input Supply Voltage Range: 3V to 6V

- Selectable Automatic Phase Shielding and Power Saving Mode Enables Higher Light Load Efficiency

- Dynamic Voltage Scaling (DVS) with Programmable Slew Rate for Each Output

- Programmable Soft-Start Function

- Interrupt Function and Fault Detection

- Watchdog Function

- Input Undervoltage Lockout (UVLO)

- Cycle by Cycle Current Limit

- Output Undervoltage Protection

- Over-Temperature Protection

- WET-WQFN-30L 4.5x5 (FC)

- Junction Temperature Range: –40°C to 150°C

#### **Simplified Application Circuit**

#### **Ordering Information**

| Part Number                   | l <sup>2</sup> C<br>Address | Default VOUT and Delay Time                                                                                                                                    | Lead Plating<br>System                  | Package Type                        | Grade                                        |  |

|-------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------|----------------------------------------------|--|

| Program to 2 + 1 + 1 phase of | operation                   |                                                                                                                                                                |                                         |                                     |                                              |  |

| RTQ2134GQWTF-21-QA-00         | 0x18                        | <ul><li>(1) VOUTx = 1V</li><li>(2) No Enable/Disable delay time</li></ul>                                                                                      |                                         |                                     |                                              |  |

| RTQ2134GQWTF-21-QA-01         | 0x18                        | <ul> <li>(1) VOUTx = 1V</li> <li>(2) Enable delay time: VOUT1/2/3 = 0/4/4ms</li> <li>(3) Disable delay time: VOUT1/2/3 = 4/0/0ms</li> </ul>                    |                                         | QWTF:                               | QA: AEC-Q100                                 |  |

| RTQ2134GQWTF-21-QA-02         | 0x19                        | <ul><li>(1) VOUTx = 1V</li><li>(2) No Enable/Disable delay time</li></ul>                                                                                      | G: Richtek<br>Green Policy<br>Compliant | WET-WQFN-30L<br>4.5x5 (FC)          | Qualified and<br>Screened by<br>High         |  |

| RTQ2134GQWTF-21-QA-03         | 0x18                        | <ul> <li>(1) VOUT1/2/3 = 0.75V/1.125V/0.6V</li> <li>(2) Enable delay time: VOUT1/2/3 = 3/2/8ms</li> <li>(3) Disable delay time: VOUT1/2/3 = 4/8/0ms</li> </ul> | Compilant                               | (W-Type)                            | Temperature                                  |  |

| RTQ2134GQWTF-21-QA-04         | 0x18                        | <ul><li>(1) VOUTx = Disable</li><li>(2) No Enable/Disable delay time</li></ul>                                                                                 |                                         |                                     |                                              |  |

| Program to 2 + 2 phase oper   | ation                       |                                                                                                                                                                |                                         |                                     |                                              |  |

| RTQ2134GQWTF-22-QA-00         | 0x18                        | <ul><li>(1) VOUTx = 1V</li><li>(2) No Enable/Disable delay time</li></ul>                                                                                      |                                         |                                     |                                              |  |

| RTQ2134GQWTF-22-QA-01         | 0x18                        | <ul> <li>(1) VOUTx = 1V</li> <li>(2) Enable delay time: VOUT1/2 = 4/0ms</li> <li>(3) Disable delay time: VOUT1/2 = 0/4ms</li> </ul>                            |                                         |                                     |                                              |  |

| RTQ2134GQWTF-22-QA-02         | 0x18                        | <ul> <li>(1) VOUTx = 1V</li> <li>(2) Enable delay time: VOUT1/2 = 3/0ms</li> <li>(3) Disable delay time: VOUT1/2 = 0/3ms</li> </ul>                            | G: Richtek<br>Green Policy              | QWTF:<br>WET-WQFN-30L<br>4.5x5 (FC) | QA: AEC-Q100<br>Qualified and<br>Screened by |  |

| RTQ2134GQWTF-22-QA-03         | 0x18                        | <ul><li>(1) VOUT1/2 = 1.15V/1.06V</li><li>(2) No Enable/Disable delay time</li></ul>                                                                           | Compliant                               | (W-Type)                            | High<br>Temperature                          |  |

| RTQ2134GQWTF-22-QA-N0         | 0x18                        | <ul><li>(1) VOUT1 = 1V, VOUT2 = Disable</li><li>(2) No Enable/Disable delay time</li></ul>                                                                     |                                         |                                     |                                              |  |

| RTQ2134GQWTF-22-QA-N1         | 0x19                        | <ul><li>(1) VOUTx = 1V</li><li>(2) No Enable/Disable delay time</li></ul>                                                                                      |                                         |                                     |                                              |  |

Note:

Richtek products are Richtek Green Policy compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

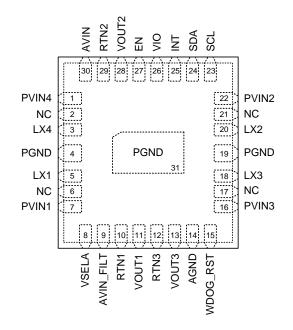

### **Pin Configuration**

(TOP VIEW)

WET-WQFN-30L 4.5x5 (FC)

#### **Marking Information**

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

#### **Functional Pin Description**

| Pin No.      | Pin Name  | Pin Function                                                                                                         |

|--------------|-----------|----------------------------------------------------------------------------------------------------------------------|

| 1            | PVIN4     | Power input for power stage 4. It is recommended to use a 10- $\mu\text{F},$ X7R capacitor.                          |

| 2, 6, 17, 21 | NC        | No internal connection.                                                                                              |

| 3            | LX4       | Switching node for power stage 4.                                                                                    |

| 4, 19        | PGND      | Power ground for power stage.                                                                                        |

| 5            | LX1       | Switching node for power stage 1.                                                                                    |

| 7            | PVIN1     | Power input for power stage 1. It is recommended to use a 10- $\mu\text{F},$ X7R capacitor.                          |

| 8            | VSELA     | VSEL input pin for all channels. Using corresponding register to define action.<br>"Do Not" leave this pin floating. |

| 9            | AVIN_FILT | Filtered analog supply voltage. It is recommended to use a 1- $\mu\text{F},$ X7R capacitor.                          |

| 10           | RTN1      | Remote ground sense for Buck1.                                                                                       |

| 11           | VOUT1     | Output voltage sense for Buck1.                                                                                      |

| 12           | RTN3      | Remote ground sense for Buck3.                                                                                       |

| 13           | VOUT3     | Output voltage sense for Buck3.                                                                                      |

| 14           | AGND      | Analog GND.                                                                                                          |

### RICHTEK

| Pin No.         | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15              | WDOG_RST | Control input for output voltage reset. Reset each Buck output voltage, DVSx, and ENDVSx registers to factory default setting value when this pin is pulled low. Connect this pin to be higher than 70% of VIO pin voltage if this pin is not used. "Do Not" leave this pin floating. The minimum watchdog debounce time is $100\mu$ s.<br>Note that the factory default setting value in watchdog register (0x25) is 0x00h (Disabled). |

| 16              | PVIN3    | Power input for power stage 3. It is recommended to use a 10- $\mu\text{F},$ X7R capacitor.                                                                                                                                                                                                                                                                                                                                             |

| 18              | LX3      | Switching node for power stage 3.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 20              | LX2      | Switching node for power stage 2.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 22              | PVIN2    | Power input for power stage 2. It is recommended to use a 10- $\mu\text{F},$ X7R capacitor.                                                                                                                                                                                                                                                                                                                                             |

| 23              | SCL      | Clock input for I <sup>2</sup> C interface. The pull-up voltage supply must be the same as VIO voltage for correct operation. Connect this pin to AGND if I <sup>2</sup> C interface is not used. "Do Not" leave this pin floating.                                                                                                                                                                                                     |

| 24              | SDA      | Data line for I <sup>2</sup> C interface. The pull-up voltage supply must be the same as VIO voltage for correct operation. Connect this pin to AGND if I <sup>2</sup> C interface is not used. "Do Not" leave this pin floating.                                                                                                                                                                                                       |

| 25              | INT      | Interrupt indicator. When INT function is used, set $0x33[6] = 1$ , $0x34[6] = 1$ and $0x35[6] = 1$ .                                                                                                                                                                                                                                                                                                                                   |

| 26              | VIO      | I/O supply voltage for digital communications. Connect this pin to 1.8V for normal operation. "Do Not" leave this pin floating.                                                                                                                                                                                                                                                                                                         |

| 27              | EN       | Master chip enable. A logic-high enables the converter; a logic-low forces the device into shutdown mode. "Do Not" leave this pin floating.                                                                                                                                                                                                                                                                                             |

| 28              | VOUT2    | Output voltage sense for Buck2.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 29              | RTN2     | Remote ground sense for Buck2.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 30              | AVIN     | Analog input voltage.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 31(Exposed PAD) | PGND     | Exposed pad. The exposed pad is connected to PGND and must be soldered to a large PCB copper area for maximum power dissipation.                                                                                                                                                                                                                                                                                                        |

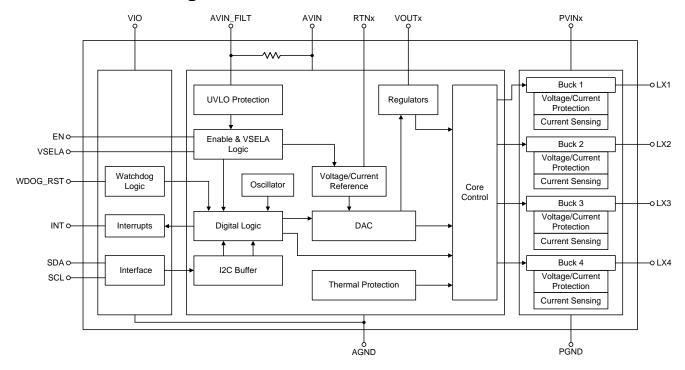

#### **Functional Block Diagram**

#### Operation

The RTQ2134 is a power management IC that integrates four high efficiency Buck converters, and is capable of providing multiphase or single phase operation. Each of the four converters provides up to 5.5A of maximum output current over an input supply voltage range of 3.3V to 6V.

The RTQ2134 utilizes the proprietary Advanced Constant On-Time (ACOT<sup>®</sup>) control architecture. The ultrafast  $ACOT^{®}$  control enables the use of small ceramic capacitors (MLCC) to save the PCB size.

During normal operation, the internal high-side power switch (HSFET) is turned on for a fixed interval determined by a one-shot timer at the beginning of each clock cycle. When the HSFET is turned off, the internal low-side power switch (LSFET) is turned on. The output voltage is sensed remotely at VOUTx and RTNx for high accuracy and is compared to an internal reference voltage. Hence, the error signal is obtained and internally compensated. The compensated error signal is then compared to an internal ramp signal. When the minimum off-time one-shot (100ns, max.) has timed out and the inductor current is below the current-limit threshold, the one-shot is triggered again if the internal ramp signal falls below the compensated error signal. The ACOT<sup>®</sup> control architecture features ultrafast transient response. When a load is suddenly increased, the output voltage drops quickly, and triggers a new on-time to rise inductor current again.

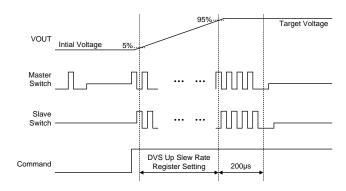

#### **Dynamic Voltage Scaling (DVS)**

The RTQ2134 provides wide output voltage range with 8-bit resolution and each Buck converter has two independently programmable voltage setting. They are called DVS0 and DVS1. Take Buck1 as two-phase configuration for example, register 0x48[8:0] can set voltage of DVS0 while 0x4A[8:0] is used to set voltage of DVS1. There are two methods to select the DVS. For the first method, it can be changed by software from register 0x52[1:0]. Control DVS0 by setting 0x52[1:0]=00 and DVS1 by setting 0x52[1:0]=01. For the second method, selecting the DVS can be from external hardware pin when setting 0x52[1:0]=10. VSELA pin can be this role and its polarity is defined by 0x52[2]. When setting 0x52[2]=0, pull VSELA high to

put DVS0 in use and pull VSELA low to put DVS1 in use. Conversely, when setting 0x52[2]=1, pull VSELA high to put DVS1 in use and pull VSELA low to put DVS0 in use.

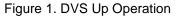

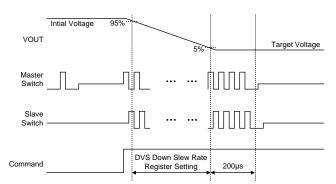

The RTQ2134 also supports DVS speed configuration, whether the slew rate of voltage changes in the same DVSx or between DVS0 and DVS1. Take Buck1 as two-phase configuration for example, when output voltage is set from low to high or high to low, register 0x54[6:4] defines slew rate of DVS up while 0x54[2:0] is used to define slew rate of DVS down. In order to have better performance during voltage changing operation, the master/slave enters PWM operation and keeps  $200\mu$ s after the voltage achieves target even when IC is set to Auto mode. Figure 1 and Figure 2 show the DVS up and down operation.

Figure 2. DVS Down Operation

## **RTQ2134-QA**

#### **MODE Selection**

Whether it is DVS0 or DVS1, there are two modes of operation: forced continuous conduction mode (FCCM) and automatic power saving mode (Auto mode). It is set in the following registers: 0x49[5], 0x4B[5], 0x63[5], 0x65[5], 0x7D[5] and 0x7F[5]. For example, to set DVS0 of Buck1 to FCCM, just write "1" at 0x49[5].

#### Auto Mode with Automatic Phase Adding/Shedding

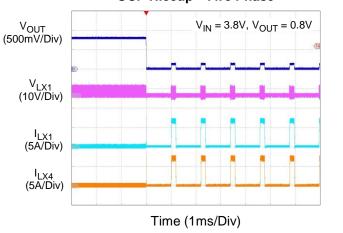

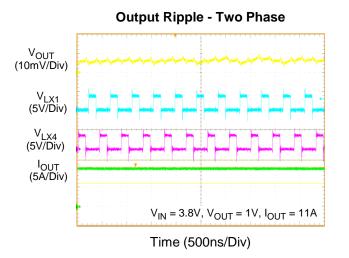

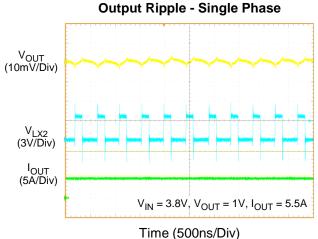

Auto mode enables high efficiency at light load. At low load current, the inductor current can drop to zero and become negative. This is detected by internal zero current-detect circuitry utilizing the LSFET RDS(ON) to sense the inductor current. The LSFET is turned off when the inductor current drops to zero, resulting in discontinuous operation (DCM). Both HSFET and LSFET remain off with the output capacitor supplying the load current until the feedback voltage falls below the feedback reference voltage. DCM operation maintains high efficiency at light load, while setting MODE to Forced PWM (FCCM) operation helps meet tight voltage regulation accuracy requirements. For multiphase outputs, the RTQ2134 automatically increases the number of operating phases as the load continues to increase above 3A (typ). The two phases are interleaved with 180 degrees apart. Interleaving reduces ripple current at the input and output. Therefore, the input and output capacitors are also reduced. Conversely, when the load current per phase drops below 2.6A (typ), the RTQ2134 automatically sheds the number of phases.

#### FCCM Mode

Setting MODE to Forced PWM (FCCM) operation helps meet stringent voltage regulation accuracy requirements. Users must enable all the set outputs before setting into the FCCM.

#### UVLO, Enable Control and Soft-Start

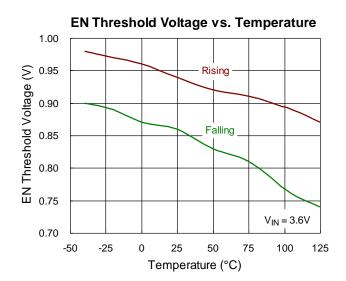

The RTQ2134 implements undervoltage lockout protection (UVLO) to prevent operation without fully turn on the internal HSFET and LSFET. The UVLO monitors the voltage of AVIN. When the AVIN voltage is lower than UVLO threshold, IC stops switching and resets all digital functions.

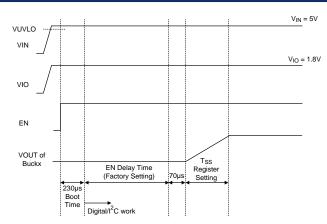

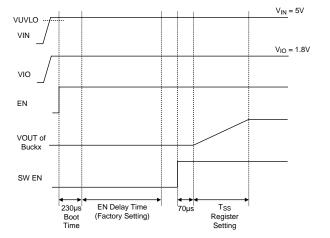

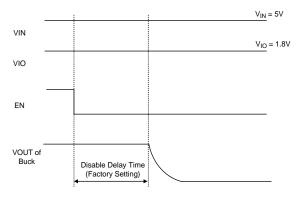

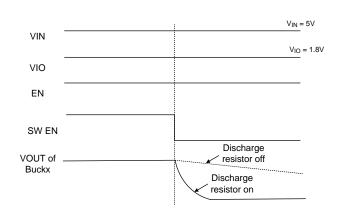

enable control, to enable or disable the device. If VEN is held below a logic-low threshold voltage (VENL) of the enable input (EN), the converter will enter into shutdown mode and reset all digital function (I<sup>2</sup>C); that is, the converter is disabled even if the VIN voltage is above VIN undervoltage lockout threshold (VUVLO). During shutdown mode, the supply current can be reduced to ISHDN (20µA or below). If the EN voltage rises above the logic-high threshold voltage (VENH), the device starts switching. When appropriate voltages are present on the VIN, AVIN, VIO and EN pins, the RTQ2134 will begin digital function, switching and initiate a soft-start ramp of the output voltage. After the device is turned on and VIO is ready, all digital functions including I<sup>2</sup>C communication start to work in a boot time with 230µs (typ.). The voltage of VIO can be used to supply power to digital function and it is recommended that enable the device after VIO voltage is ready. The RTQ2134 supports enable delay time setting (factory setting) and soft-start slew rate setting for each Buck. The soft-start function is used to prevent large inrush current while the converter is powered up. Register 0x55[5:4], 0x6F[5:4] and 0x89[5:4] let soft-start time of each be programmable. The start-up sequence is shown in Figure 3. IC also implements enable control by software, it can be set in the registers: 0x49[0], 0x4B[0], 0x63[0], 0x65[0], 0x7D[0] and 0x7F[0]. If the output voltage of Buck is default disable which is only set by factory, the output voltage starts to ramp up by software and the Figure 4 shows the start-up sequence. For disable function, the device supports disable delay time setting (factory setting) by external EN pin and the output voltage ramps down with default discharge resistor. The discharge resistor can be controlled to on or off by register 0x42[0], 0x5F[0] and 0x79[0] when the converter is disabled by software. The power-off sequence is shown in Figure 5 and Figure 6.

The RTQ2134 provides an EN pin, as an external chip

#### Figure 4. Start-up Sequence by Software

Figure 5. Power-off Sequence

RICHTEK

#### Power Good Indication

The RTQ2134 provides a power good indication and this function shows the status of output voltage. When output voltage is between 110% and 90% of setting voltage for each Buck, the PG indication bit goes high. The relative registers are 0x14[7], 0x15[7] and 0x16[7]. Fault Detection and Interrupt Pin

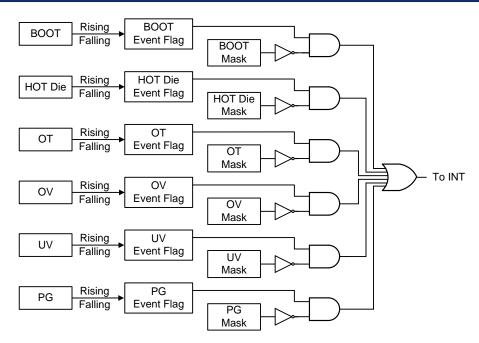

The RTQ2134 alerts the host when a warning, like Boot and Hot Die, or fault events, like overvoltage, undervoltage and over-temperature conditions have occurred. Registers 0x13, 0x14, 0x15 and 0x16 can help host to know if the fault or waning event happens. These bits relative to events can be read and cleared. Moreover, the RTQ2134 provides an interrupt pin with the push-pull output capability and this pin shows these events by using active low. When INT function is used, set 0x33[6] = 1, 0x34[6] = 1 and 0x35[6] = 1. The pull high output voltage of INT pin will be VIO voltage. Register 0x32, 0x33, 0x34 and 0x35 can also set the mask function to mask or pass the event flag output to external interrupt pin. The overall detection function is shown in Figure 7.

Figure 7. Overall Detection Function

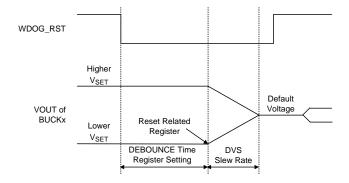

#### Watchdog Function

The RTQ2134 implements a watchdog function which resets each Buck output voltage, DVSx, and ENDVSx registers to factory default setting value. Register 0x25 can enable or disable watchdog function of each Buck and provide the debounce time for selection. The minimum watchdog debounce time is  $100\mu$ s when 0x25[2:0] is set to 000. The operation of watchdog reset is shown in Figure 8. Table 1 shows the registers will be reset when WDOG\_RST pin is pulled low. The I<sup>2</sup>C command needs to be after the WDOG\_RST is pulled high.

Figure 8. Watchdog Reset Operation

| Table 1 | Watchdog | Reset | Register |

|---------|----------|-------|----------|

|---------|----------|-------|----------|

**RTQ2134-QA**

|           | <u> </u>  | <u> </u>  |

|-----------|-----------|-----------|

| BUCK1_WDT | BUCK2_WDT | BUCK3_WDT |

| 0x48      | 0x62      | 0x7C      |

| 0x49[0]   | 0x63[0]   | 0x7D[0]   |

| 0x4A      | 0x64      | 0x7E      |

| 0x4B[0]   | 0x65[0]   | 0x7F[0]   |

| 0x52      | 0x6C      | 0x86      |

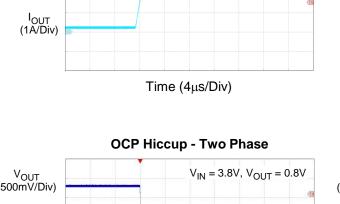

#### **Overcurrent Protection**

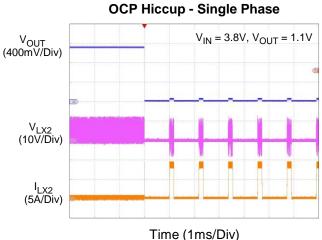

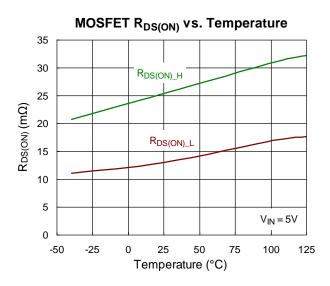

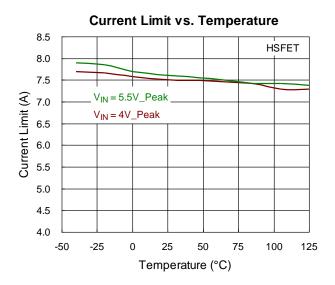

The RTQ2134 features cycle-by-cycle current-limit protection on both HSFET and LSFET to prevent the device from the catastrophic damage in output short-circuit, overcurrent or inductor saturation conditions.

The HSFET overcurrent protection is achieved by an internal current comparator that monitors the current in the HSFET during each on-time. The switch current is compared with the HSFET peak-current limit (I<sub>LIM\_H</sub>) after a certain amount of delay when the HSFET is turned on each cycle. If an overcurrent condition occurs, the converter will immediately turn off the HSFET and turn on the LSFET to prevent the inductor current from exceeding the HSFET current limit.

The LSFET overcurrent protection is achieved by measuring the inductor current through the LSFET

RICHTEK

during the LSFET on-time. Once the current rises above the LSFET valley current limit (ILIM\_L), the on-time one-shot will be inhibited until the inductor current ramps down to the current limit level (ILIM\_L), that is, another on-time can only be triggered when the inductor current goes below the LSFET current limit. If the output load current exceeds the available inductor current (clamped by the LSFET current limit), the output capacitor needs to supply the extra current so that the output voltage will begin to drop. If it drops below the output undervoltage protection trip threshold, the IC will stop switching to avoid excessive heat.

#### **Output Undervoltage Protection**

The RTQ2134 includes output undervoltage protection (UVP) against over-load or short-circuited condition by constantly monitoring the output voltage VOUT. If VOUT drops below the undervoltage protection trip threshold (typically 50% of the internal reference voltage), both HSFET and LSFET will stop switching. Register 0x37[3], 0x38[3] and 0x39[3] can select hiccup or latch protection behavior of each Buck converter when converter is in UV condition. For hiccup behavior, both HSFET and LSFET keep low state in a 1ms and then IC starts to switch. If the output voltage is not greater than UV threshold after internal soft-start end signal is

triggered, both HSFET and LSFET will still keep low state again for next cycle. When each Buck is set to latch mode, UVP will let converter enter shutdown mode unless resetting IC by external EN pin or falling to UVLO low threshold.

#### **Over-Temperature Protection**

The RTQ2134 includes an over-temperature protection (OTP) circuitry to prevent overheating due to excessive power dissipation. The OTP shuts down switching operation when junction temperature exceeds a thermal shutdown threshold Tsp. Once the junction temperature cools down by a thermal shutdown hysteresis ( $\Delta$ Tsp), the IC resumes normal operation with a complete soft-start. It can select not to shut down IC when OTP happens by using register 0x30[3].

Note that the over-temperature protection is intended to protect the device during momentary overload conditions. The protection is activated outside of the absolute maximum range of operation as a secondary fail-safe and therefore should not be relied upon operationally. Continuous operation above the specified absolute maximum operating junction temperature reliability may impair device or permanently damage the device.

#### Absolute Maximum Ratings (Note 1)

| Supply Input Voltage                                  | –0.3V to 6.5V  |

|-------------------------------------------------------|----------------|

| LX Pin Switch Voltage                                 | –0.3V to 7.3V  |

| < 100ns                                               | –5V to 9V      |

| Other I/O Pin Voltages                                | –0.3V to 7.3V  |

| <ul> <li>Power Dissipation, PD @ TA = 25°C</li> </ul> |                |

| WET-WQFN-30L 4.5x5 (FC)                               | 2.87W          |

| Package Thermal Resistance (Note 2)                   |                |

| WET-WQFN-30L 4.5x5 (FC), θJA                          | 34.8°C/W       |

| WET-WQFN-30L 4.5x5 (FC), θJC(Top)                     | 18.2°C/W       |

| WET-WQFN-30L 4.5x5 (FC), θJB                          | 13.2°C/W       |

| Lead Temperature (Soldering, 10 sec.)                 | 260°C          |

| Junction Temperature                                  | 150°C          |

| Storage Temperature Range                             | –65°C to 150°C |

| ESD Susceptibility (Note 3)                           |                |

| HBM (Human Body Model)                                | 2kV            |

#### Recommended Operating Conditions (Note 4)

| Supply Input Voltage (for 2 + 2 application)     | 3.3V to 6V                       |

|--------------------------------------------------|----------------------------------|

| Supply Input Voltage (for 2 + 1 + 1 application) | 3V to 6V                         |

| VIO Input Voltage                                | 1.7V to VIN                      |

| Junction Temperature Range                       | $-40^{\circ}C$ to $150^{\circ}C$ |

#### **Electrical Characteristics**

(V<sub>IN</sub> = 3.7V, T<sub>J</sub> =  $-40^{\circ}$ C to 125°C, unless otherwise specified)

| Parameter                          | Symbol    | Test Conditions                               | Min | Тур  | Max  | Unit |

|------------------------------------|-----------|-----------------------------------------------|-----|------|------|------|

| Analog Input Voltage               | VAVIN     | For 2 + 2 application                         | 3.3 |      | 6    | V    |

| Power Input Voltage                | Vpvin     | For 2 + 2 application                         | 3.3 |      | 6    | V    |

| Shutdown Current                   | ISHDN     | EN = 0V, Digital circuit does not work        |     | 1    | 20   | μA   |

| Buck Off Current                   | ISDBO     | EN = VIO = 1.8V, disable all Buck by software |     | 20   | 80   | μA   |

| 1Phase no Switching<br>Current     | ISLP      | Vout = 1.2 x Vout_setting                     |     | 70   | 120  | μA   |

| Undervoltage Lockout<br>Threshold  | Vuvlo     | V <sub>IN</sub> rising                        | 2.1 | 2.32 | 2.45 | V    |

| Undervoltage Lockout<br>Hysteresis | Δνυνίο    |                                               |     | 300  |      | mV   |

| High-Side Switch<br>On-Resistance  | Rds(on)_H | VIN = 5V                                      | 18  | 25   | 45   | mΩ   |

| Low-Side Switch<br>On-Resistance   | Rds(on)_L | VIN = 5V                                      | 8   | 15   | 25   | mΩ   |

| Parame                             | eter        | Symbol          | Test Conditions                                                                                            | Min          | Тур   | Max          | Unit |

|------------------------------------|-------------|-----------------|------------------------------------------------------------------------------------------------------------|--------------|-------|--------------|------|

| SDA, SCL,                          | Logic-High  | Viн             | $3V \le VIN \le 6V$                                                                                        | 0.7 x<br>VIO |       |              |      |

| VSELA,<br>WDOG_RST                 | Logic-Low   | VIL             | $3V \le V_{IN} \le 6V$                                                                                     |              |       | 0.3 x<br>VIO | V    |

| EN Threshold                       | Logic-High  | Venh            |                                                                                                            | 1.2          |       |              | v    |

|                                    | Logic-Low   | Venl            |                                                                                                            |              |       | 0.4          | v    |

| External Supply<br>I/O Pin         | Voltage for | Vin_i/o         |                                                                                                            | 1.7          | 1.8   | Vin          | V    |

|                                    | 2014        |                 | Auto PFM/PWM, V <sub>OUT</sub> = 1V (Note 5)                                                               | -2.5         |       | 2.5          | %    |

| VOUT DC Accur                      | acy         |                 | Forced PWM, $0.6V \le V_{OUT} \le 1.85V$                                                                   | -1.5         |       | 1.5          | %    |

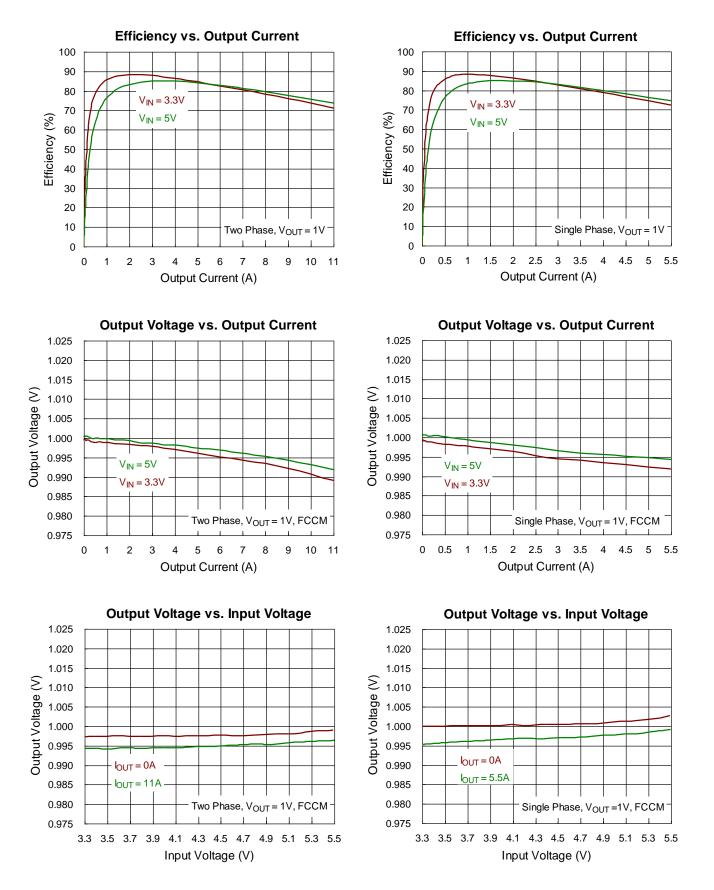

| Load Regulation                    | า           | $\Delta V$ LOAD | IOUT(DC) = 1  to  5A  (Note 5)                                                                             |              | -0.08 |              | %/A  |

| Line Regulation                    |             | $\Delta VLINE$  | $3V \le V_{IN} \le 6V$ , $I_{OUT(DC)} = 1.5A$ (Note 5)                                                     |              | 0.2   |              | %/V  |

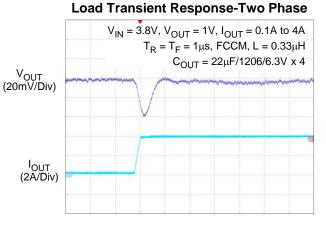

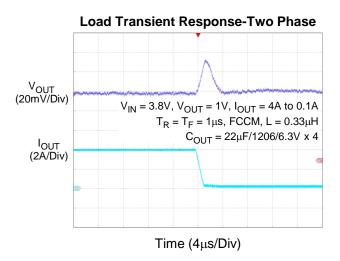

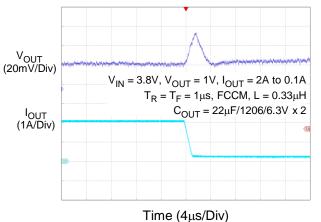

| Load Transient                     | Response    |                 | 2phase operation, 0.1 to 4A, tR = tF = 1 $\mu$ s,<br>L = 0.33 $\mu$ H, COUT = 44 $\mu$ F/phase<br>(Note 5) |              | ±40   |              | mV   |

|                                    | ·           |                 | 1phase operation, 0.1 to 2A, $t_R = t_F = 1\mu s$ ,<br>L= 0.33 $\mu$ H, COUT = 44 $\mu$ F/phase (Note 5)   |              | ±40   |              | mV   |

| Line Transient F                   | Response    |                 | $4V \text{ to } 5V, t_R = t_F = 10 \mu s$ (Note 5)                                                         |              | ±40   |              | mV   |

| Current Balance                    | Э           |                 | Load = 10A,  I <sub>Avg</sub> - I <sub>LX_1 or 4</sub>                                                     |              |       | 0.5          | А    |

| Phase Adding L                     | .evel       |                 | From 1phase to 2phase (Note 5)                                                                             |              | 3     |              | А    |

| Phase Shedding                     | g Level     |                 | From 2phase to 1phase (Note 5)                                                                             |              | 2.6   |              | А    |

| Soft-Start Time                    |             | Tstart          | Slew Rate = 10mV/µs                                                                                        | -20          |       | 20           | %    |

| High-Side Switc<br>Limit per Chann |             | ILIM_H          |                                                                                                            | 5.8          | 8     | 11           | A    |

| Low-Side Switc<br>Limit per Chann  |             | ILIM_L          |                                                                                                            | 5.1          | 7     | 9            | A    |

| Thermal Shutdo                     | own         | Tsd             |                                                                                                            |              | 160   |              | °C   |

| Thermal Shutdo<br>Hysteresis       | own         | ΔTsd            |                                                                                                            |              | 30    |              | °C   |

| HOT Die Warni                      | ng          |                 | 0xAA = 0x02 (Note 5)                                                                                       |              | 109   |              | °C   |

| HOT Die Hyster                     | resis       | THYSHD          | (Note 5)                                                                                                   |              | 15    |              | °C   |

| Discharge Resis                    | stor        |                 |                                                                                                            | 70           | 115   | 180          | Ω    |

| Output UVP Flag                    |             | VUVP_T          | Trigger Level                                                                                              | 40           | 50    | 60           | %    |

|                                    |             | VUVP_R          | Recovery Level                                                                                             |              | 57    |              | %    |

|                                    | ~           | Vovp_t          | Trigger Level                                                                                              | 123          | 133   | 143          | %    |

| Output OVP Fla                     | iy.         | Vovp_r          | Recovery Level                                                                                             |              | 125   |              | %    |

| Switching Frequ                    | lency       | fsw             | Vout = 1V                                                                                                  | 1850         | 2100  | 2500         | kHz  |

### **RTQ2134-QA**

| Parameter                                                                                            | Symbol         | Test Conditions                 | Min | Тур | Мах | Unit |

|------------------------------------------------------------------------------------------------------|----------------|---------------------------------|-----|-----|-----|------|

| Error Rate of DVS Slew<br>Rate                                                                       |                | VIN = 3.7V, VOUT = 0.6V to 1.2V | -20 |     | 20  | %    |

|                                                                                                      |                | Output low level, ISOURCE = 2mA |     |     | 0.4 | V    |

| Digital Output Pin: INT                                                                              |                | Push-pull, ISINK = 2mA          | 1.6 |     | VIO | V    |

| Digital Output Pin: SDA                                                                              |                | Output low level Resistor       |     |     | 40  | Ω    |

| I <sup>2</sup> C Speed                                                                               |                |                                 |     |     | 3.4 | MHz  |

| Hold Time (Repeated) Start<br>Condition. After this Period,<br>the First Clock Pulse is<br>Generated | thd;sta        | Fast mode (Note5)               | 0.6 |     |     | μS   |

| Low Period of the SCL<br>Clock                                                                       | tLOW           | Fast mode (Note5)               | 1.3 |     |     | μS   |

| High Period of the SCL<br>Clock                                                                      | tніgн          | Fast mode (Note5)               | 0.6 |     |     | μs   |

| Set-Up Time for a Repeated START Condition                                                           | tsu;sta        | Fast mode (Note5)               | 0.6 |     |     | μs   |

| Data Hold Time                                                                                       | thd;dat        | Fast mode (Note5)               | 0   |     | 0.9 | μS   |

| Data Set-Up Time                                                                                     | tsu;dat        | Fast mode (Note5)               | 100 |     |     | ns   |

| Set-Up Time for STOP<br>Condition                                                                    | tsu;sto        | Fast mode (Note5)               | 0.6 |     |     | μs   |

| Bus Free Time between a<br>STOP and START<br>Condition                                               | tBUF           | Fast mode (Note5)               | 1.3 |     |     | μs   |

| Rising Time of both SDA and SCL Signals                                                              | tR             | Fast mode (Note5)               | 20  |     | 300 | ns   |

| Falling Time of both SDA and SCL Signals                                                             | tF             | Fast mode (Note5)               | 20  |     | 300 | ns   |

| SDA Output Low Sink<br>Current                                                                       | Iol            | SDA Voltage = 0.4V (Note5)      | 2   |     |     | mA   |

| Detect SDA Low Timeout                                                                               | <b>TIMEOUT</b> | Fast/High speed mode (Note5)    |     | 30  |     | ms   |

**Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- **Note 2.**  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25^{\circ}C$  on a Four-layer Richtek Evaluation Board.  $\theta_{JC}$  is measured at the top of the package.

- Note 3. Devices are ESD sensitive. Handling precautions are recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. Guaranteed by design.

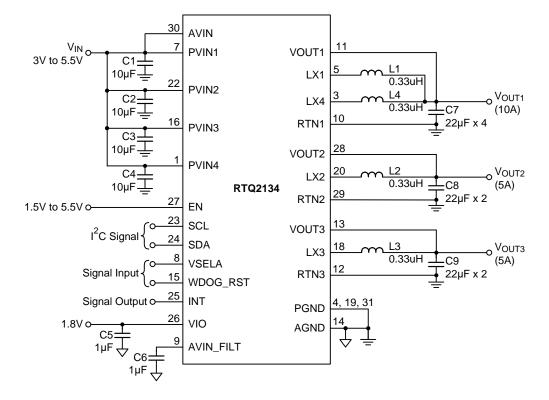

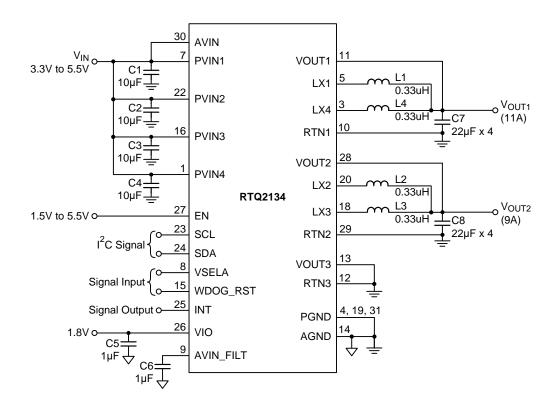

#### **Typical Application Circuit**

#### 2 + 1 + 1 Phase

#### 2+2Phase

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

| Table 2. Recommended BOM |     |                   |                    |                            |             |  |  |

|--------------------------|-----|-------------------|--------------------|----------------------------|-------------|--|--|

| Reference                | Qty | Part number       | Description        | Package                    | Manufacture |  |  |

| U1                       | 1   | RTQ2134           | DC-DC<br>Converter | WET-WQFN-30L<br>4.5x5 (FC) | RICHTEK     |  |  |

| C1, C2, C3, C4           | 4   | GRT188C81A106ME   | 10μF               | C-0603                     | Murata      |  |  |

| C5, C6                   | 2   | GRT188C8YA105KE   | 1μF                | C-0603                     | Murata      |  |  |

| C7, C8, C9               | 8   | GRT31CR70J226KE   | 22µF               | C-1206                     | Murata      |  |  |

| L1, L2, L3, L4           | 4   | VCTA25201B-R33MS6 | 0.33µH             | 2520                       | Cyntec      |  |  |

Table 2 Recommended BOM

Note:

1. COUT =  $44\mu$ F per-phase is min. value for the RTQ2134.

2. All the input and output capacitors are the suggested values, referring to the effective capacitances, subject to any de-rating effect, like a DC bias.

### **Typical Operating Characteristics**

Copyright © 2023 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

DSQ2134-QA-03

September 2023

Time (4µs/Div)

### **RTQ2134-QA**

Load Transient Response-Single Phase  $V_{IN} = 3.8V, V_{OUT} = 1V, I_{OUT} = 0.1A \text{ to } 2A$   $T_R = T_F = 1\mu s, FCCM, L = 0.33\mu H$   $C_{OUT} = 22\mu F/1206/6.3V \times 2$   $I_{OUT}$  (1A/Div)Time (4us/Div)

#### Load Transient Response-Single Phase

#### EN Pin Current vs. Temperature 0.8 0.7 0.1 $V_{EN} = 3.3V$ 0 -50 -25 0 25 50 75 100 125 Temperature (°C)

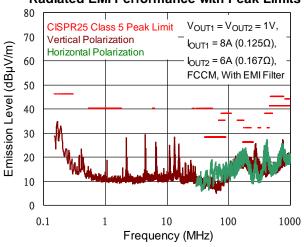

#### **Radiated EMI Performance with Peak Limits**

#### **Application Information**

Richtek's component specification does not include the following information in the Application Information section. Thereby no warranty is given regarding its validity and accuracy. Customers should take responsibility to verify their own designs and reserve suitable design margin to ensure the functional suitability of their components and systems.

The RTQ2134 is a power management IC that integrates four high efficiency Buck converters, and is capable of multiphase or single-phase operation. The RTQ2134 supports 2 + 1 + 1 and 2 + 2 configuration.

#### **Inductor Selection**

The inductor selection are trade-offs among size, cost, efficiency, and transient response requirements. Generally, three key inductor parameters are specified for operation with the device: inductance value (L), inductor saturation current (ISAT), and DC resistance (DCR).

A good compromise between size and loss is a 30% peak-to-peak ripple current to the IC rated current, but it still depends on size consideration. The inductor used in the Typical Application Circuit of this datasheet is recommended. The switching frequency, input voltage, output voltage, and selected inductor ripple current determine the inductor value as follows:

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times \Delta I_L}$$

To enhance the efficiency, choose a low-loss inductor having the lowest possible DCR that fits in the allotted dimensions. The selected inductor should have a saturation current rating greater than the peak current limit of the device. The core must be large enough not to saturate at the peak inductor current ( $I_{L-PEAK}$ ):

$$\Delta I_{L} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times L}$$

$$I_{L_{PEAK}} = I_{OUT_{MAX}} + \frac{1}{2} \Delta I_{L}$$

The current flowing through the inductor is the inductor ripple current plus the output current. During power-up, faults, or transient load conditions, the inductor current can increase the peak inductor current level calculated above. In transient conditions, the inductor current can increase up to the switch current limit of the device. For this reason, the most conservative approach is to specify an inductor with a saturation current rating equal to or greater than the switch current limit rather than the peak inductor current.

#### **Input Capacitor Selection**

Input capacitance, CIN, is needed to filter the pulsating current at the drain of the HSFET. The CIN should be sized to do this without causing a large variation in input voltage. Several capacitors may also be paralleled to meet size, height and thermal requirements in the design. For low input voltage applications, sufficient bulk input capacitance is needed to minimize transient effects during output load changes.

The input capacitor should be placed as close as possible to each VIN pin with a low inductance connection to the PGND of the IC. It is recommended to connect capacitors between the VIN pin and the PGND pin as shown in the Typical Application Circuit. The larger input capacitance is required when a lower switching frequency is used. The X7R capacitors are recommended for best performance across temperature and input voltage variations.

#### **Output Capacitor Selection**

The selection of COUT is determined by considering to satisfy the voltage ripple and the transient loads. The peak-to-peak output ripple,  $\Delta VOUT$ , is determined by:

$$\Delta V_{OUT} = \Delta I_{L} \left( ESR + \frac{1}{8 \times C_{OUT} \times F_{SW}} \right)$$

where the  $\Delta IL$  is the peak-to-peak inductor ripple current. The highest output ripple is at maximum input voltage since  $\Delta IL$  increases with input voltage. Multiple capacitors placed in parallel may be needed to meet the ESR and RMS current handling requirements.

Ceramic capacitors have very low equivalent series

## RICHTEK

resistance (ESR) and provide the best ripple performance. The X7R dielectric capacitor is recommended for the best performance across temperature and input voltage variations. The variation of the capacitance value with temperature, DC bias voltage and switching frequency needs to be taken into consideration. For example, the capacitance value of a capacitor decreases as the DC bias across the capacitor increases. Be careful to consider the voltage coefficient of ceramic capacitors when choosing the value and case size. Most ceramic capacitors lose 50% or more of their rated values when used near their rated voltage.

Transient performance can be improved with a higher value output capacitor. Increasing the output capacitance will also decrease the output voltage ripple.

The recommended output capacitors are shown in Typical Application Circuit section.

#### **Thermal Considerations**

In many applications, the RTQ2134 does not generate much heat due to its high efficiency and low thermal resistance of its WQFN- 30L 4.5x5 package. However, in applications where the RTQ2134 runs at a high ambient temperature and high input voltage or high switching frequency, the generated heat may exceed the maximum junction temperature of the part.

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. If the junction temperature reaches approximately 160°C, the RTQ2134 stops switching the power MOSFETs until the temperature cools down by 30°C.

The maximum power dissipation can be calculated by the following formula:

#### $PD(MAX) = (TJ(MAX) - TA) / \theta JA(EFFECTIVE)$ where

$T_{J(MAX)}$  is the maximum allowed junction temperature of the die. For recommended operating condition specifications, the maximum junction temperature is 125°C. TA is the ambient operating temperature,  $\theta_{JA(EFFECTIVE)}$  is the system-level junction to ambient thermal resistance. It can be estimated from thermal modeling or measurements in the system.

The thermal resistance of the device strongly depends on the surrounding PCB layout and can be improved by providing a heat sink of surrounding copper ground. The addition of backside copper with thermal vias, stiffeners, and other enhancements can also help reduce thermal resistance.

Experiments in the Richtek thermal lab show that simply set  $\theta_{JA}$ (EFFECTIVE) as 110% to 120% of the  $\theta_{JA}$  is reasonable to obtain the allowed PD(MAX).

The power loss of system can be found in the efficiency measurement and the formula below can be used to determine the power loss of IC by removing the loss of inductor including DC loss and AC loss.

Two-phase converter power loss:

$$P_{loss} = (V_{lN} \times I_{lN} - V_{OUT} \times I_{OUT}) - ((\frac{I_{OUT}}{2})^2 \times DCR) \times 2$$

$$-P_{core\_loss} \times 2 - (\frac{V_{OUT}^2 \times ACR}{12 \times L^2 \times f_{SW}^2} \times (1 - \frac{V_{OUT}}{V_{lN}})^2) \times 2$$

Single-phase converter power loss:

$$\begin{split} \mathsf{P}_{\mathsf{loss}} &= (\mathsf{V}_{\mathsf{IN}} \times \mathsf{I}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}} \times \mathsf{I}_{\mathsf{OUT}}) - \mathsf{I}_{\mathsf{OUT}}^2 \times \mathsf{DCR} - \mathsf{P}_{\mathsf{core\_loss}} \\ &- \frac{\mathsf{V}_{\mathsf{OUT}}^2 \times \mathsf{ACR}}{12 \times \mathsf{L}^2 \times \mathsf{f}_{\mathsf{SW}}^2} \times (1 - \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{IN}}})^2 \end{split}$$

#### Where

P<sub>core\_loss</sub> and ACR need to be obtained from inductor supplier.

Total loss of IC cannot be larger than maximum power loss. If the application requires a higher ambient temperature and/or higher switching frequency, care should be taken to reduce the temperature rise of the part by using a heat sink or air flow. Note that the over-temperature protection is intended to protect the device during momentary overload conditions. The protection is activated outside of the absolute maximum range of operation as a secondary fail-safe and therefore should not be relied upon operationally. Continuous operation above the specified absolute maximum operating junction temperature may impair device reliability or permanently damage the device.

## RICHTEK

#### Layout Guidelines

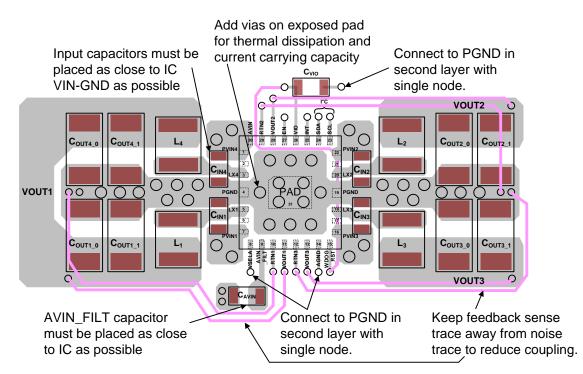

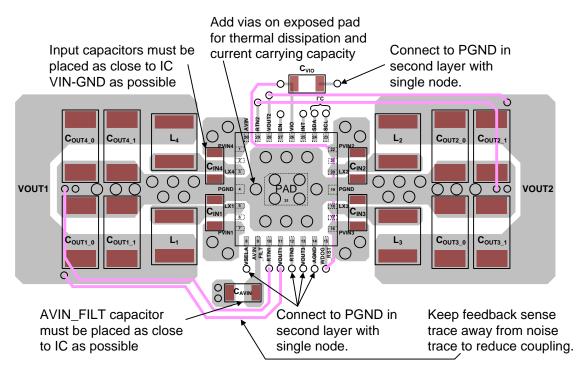

When laying out the printed circuit board, the following checklist should be used to ensure proper operation of the RTQ2134:

- Four-layer or six-layer PCB with maximum ground plane is strongly recommended for good thermal performance.

- Keep the traces of the main current paths wide and short.

- Place high frequency decoupling capacitor as close as possible to the IC to reduce the loop impedance and minimize switch node ringing.

- Place multiple vias under the device near PVIN and PGND and close to input capacitors to reduce parasitic inductance and improve thermal performance. To keep thermal resistance low, extend the ground plane as much as possible, and add twenty thermal vias under and near the RTQ2134 to additional ground planes within the circuit board and on the bottom side.

- The high frequency switching nodes, LX, should be as small as possible. Keep analog components away from the LX node.

- Reduce the area size of the LX exposed copper to reduce the electrically coupling from this voltage.

- Connect the feedback sense network behind via of output capacitor.

- Connect all analog grounds to common node and then connect the common node to the power ground with a single point.

Figure 9 and Figure 10 show the layout example which includes one two phase converter for Core and one single phase converter for Memory application.

Figure 9. Layout Guideline for 2 + 1 + 1 Application

| Copyright © 2023 Richtek Technology Corporation. All rights reserved. | RICHTEK is a registered trademark of Richtek Technology C | orporation. |      |

|-----------------------------------------------------------------------|-----------------------------------------------------------|-------------|------|

| www.richtek.com                                                       | DSQ2134-QA-03                                             | September   | 2023 |

Figure 10. Layout Guideline for 2 + 2 Application

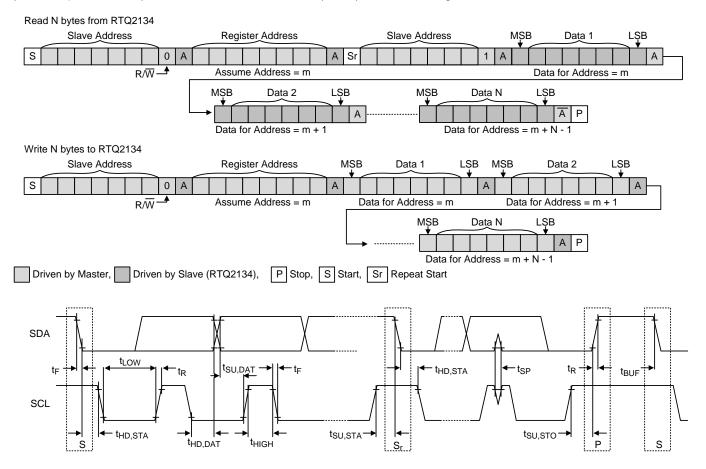

#### I<sup>2</sup>C Interface

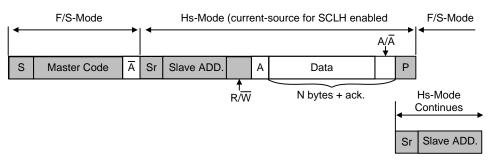

The RTQ2134 I<sup>2</sup>C slave address = 7'b0011000 (Changed by Factory Setting). The RTQ2134 supports fast mode (bit rate up to 400kb/s). The write or read bit stream (N  $\ge$  1) is shown in Figure 11.

Figure 11. I<sup>2</sup>C Read and Write Stream and Timing Diagram

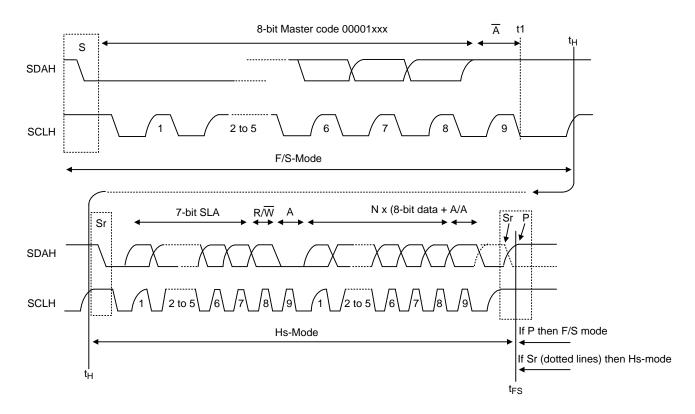

The RTQ2134 also supports High-speed mode (bit rate up to 3.4Mb/s) with access code 08H. Figure 12 and Figure 13 show detailed transfer format. Hs-mode can only start after the following conditions (all of which are in F/S-mode):

- START condition (S)

- ► 8-bit master code (00001xxx)

- ▶ not-acknowledge bit (Ā)

Figure 12. Data Transfer Format in Hs-mode

Figure 13. A Complete Hs-mode Transfer

#### Table 3. I<sup>2</sup>C Register Summary

| Register<br>Address | Register<br>Name    | Bit 7                   | Bit 6           | Bit 5                   | Bit 4                   | Bit 3                                | Bit 2          | Bit 1            | Bit 0                | Default |  |

|---------------------|---------------------|-------------------------|-----------------|-------------------------|-------------------------|--------------------------------------|----------------|------------------|----------------------|---------|--|

| 0x01                | IO_CHIPNA<br>ME     |                         |                 |                         | IO_CHI                  | PNAME                                |                |                  |                      | 0x01    |  |

| 0x02                | IO_CHIPVE<br>RSION  |                         |                 |                         | IO_CHIP                 | VERSION                              |                |                  |                      | 0x01    |  |

| 0x0A                | IO_DIEID3           |                         | IO_DIEID3       |                         |                         |                                      |                |                  |                      |         |  |

| 0x0B                | IO_DIEID2           |                         |                 |                         | IO_D                    | IEID2                                |                |                  |                      | 0xDC    |  |

| 0x0C                | IO_DIEID1           |                         |                 |                         | IO_D                    | IEID1                                |                |                  |                      | 0xBA    |  |

| 0x0D                | IO_DIEID0           |                         |                 |                         | IO_D                    | IEID0                                |                |                  |                      | 0x98    |  |

| 0x0F                | IO_SOFTR<br>ESET    |                         |                 |                         | Reserved                |                                      |                |                  | IO_SO<br>FTRES<br>ET | 0x00    |  |

| 0x13                | FLT_RECO<br>RDTEMP  | FLT_BO<br>OT            |                 | Res                     | erved                   | FLT_HO FLT_TE<br>TDIE MPSDR Reserved |                |                  |                      | 0x00    |  |

| 0x14                | FLT_RECO<br>RDBUCK1 | BUCK1_<br>PG            | Reserved        | FLT_BU<br>CK1_OV        | FLT_BU<br>CK1_UV        | Reserved                             |                |                  |                      | 0x00    |  |

| 0x15                | FLT_RECO<br>RDBUCK2 | BUCK2_<br>PG            | Reserved        | FLT_BU<br>CK2_OV        | FLT_BU<br>CK2_UV        |                                      | Rese           | erved            |                      | 0x00    |  |

| 0x16                | FLT_RECO<br>RDBUCK3 | BUCK3_<br>PG            | Reserved        | FLT_BU<br>CK3_OV        | FLT_BU<br>CK3_UV        |                                      | Rese           | erved            |                      | 0x00    |  |

| 0x22                | IO_I2CCFG           | Reserved                |                 |                         | ŀ                       | O_I2CADDR                            | R              |                  |                      | 0x18    |  |

| 0x25                | IO_RSTDV<br>S       | Reserved                | IO_F            | RSTDVS_C                | TRL                     | Reserved                             | Į              | O_DBNTIN         | 1E                   | 0x00    |  |

| 0x30                | FLT_OT_<br>CTRL     |                         | Rese            | erved                   |                         | FLT_CTR<br>LOT1                      |                | Reserved         |                      | 0x00    |  |

| 0x32                | FLT_MASK<br>TEMP    | FLT_MA<br>SKBOOT        |                 | Res                     | erved                   |                                      | FLT_MA<br>SKHD | FLT_MA<br>SKTSDR | Reserved             | 0x00    |  |

| 0x33                | FLT_MASK<br>BUCK1   | FLT_BU<br>CK1MAS<br>KPG | BUCK1<br>INTACT | FLT_BU<br>CK1MAS<br>KOV | FLT_BU<br>CK1MAS<br>KUV |                                      | Rese           | erved            |                      | 0x00    |  |

| 0x34                | FLT_MASK<br>BUCK2   | FLT_BU<br>CK2MAS<br>KPG | BUCK2<br>INTACT | FLT_BU<br>CK2MAS<br>KOV | FLT_BU<br>CK2MAS<br>KUV | Reserved                             |                |                  |                      | 0x00    |  |

| 0x35                | FLT_MASK<br>BUCK3   | FLT_BU<br>CK3MAS<br>KPG | BUCK3<br>INTACT | FLT_BU<br>CK3MAS<br>KOV | FLT_BU<br>CK3MAS<br>KUV | Reserved                             |                |                  |                      | 0x00    |  |

| 0x37                | FLT_BUCK<br>1_CTRL  |                         | Rese            | erved                   |                         | FLT_BUC<br>K1_CTRL Reserved<br>UV    |                |                  |                      | 0x0C    |  |

| Register<br>Address | Register<br>Name   | Bit 7    | Bit 6            | Bit 5                                                      | Bit 4    | Bit 3                    | Bit 2                           | Bit 1     | Bit 0            | Default |

|---------------------|--------------------|----------|------------------|------------------------------------------------------------|----------|--------------------------|---------------------------------|-----------|------------------|---------|

| 0x38                | FLT_BUCK<br>2_CTRL |          | Rese             | erved                                                      |          | FLT_BU<br>CK2_CT<br>RLUV |                                 | Reserved  |                  | 0x0C    |

| 0x39                | FLT_BUCK<br>3_CTRL |          | Rese             | erved                                                      |          | FLT_BU<br>CK3_CT<br>RLUV | Reserved                        |           |                  | 0x0C    |

| 0x3E                | BUCK1_<br>RAMP     | Reserved | BUCK1_<br>DVS_UP | Received                                                   |          |                          | BUCK1_<br>DVS_DO Reserved<br>WN |           | erved            | 0x44    |

| 0x42                | BUCK1_<br>CFG0     |          |                  |                                                            | Reserved |                          |                                 |           | BUCK1_<br>DIS    | 0x01    |

| 0x48                | BUCK1_<br>DVS0CFG1 |          |                  |                                                            | BUCK1    | _DVS0                    |                                 |           |                  | 0x8C    |

| 0x49                | BUCK1_<br>DVS0CFG0 | Rese     | erved            | BUCK1_<br>DVS0M<br>ODE                                     |          | Rese                     | erved                           |           | BUCK1_<br>ENDVS0 | 0x00    |

| 0x4A                | BUCK1_<br>DVS1CFG1 |          |                  | BUCK1_DVS1                                                 |          |                          |                                 |           |                  | 0x8C    |

| 0x4B                | BUCK1_<br>DVS1CFG0 | Rese     | erved            | BUCK1_<br>DVS1M Reserved BUCK1_<br>DDE BUCK1_              |          |                          |                                 |           | 0x00             |         |

| 0x52                | BUCK1_<br>DVSCFG   |          |                  | Reserved BUCK1_ DVSPINPOL                                  |          |                          |                                 |           | _DVS_<br>RL      | 0x00    |

| 0x54                | BUCK1_<br>RSPCFG   | Reserved | BL               | JCK1_RSPI                                                  | UP       | Reserved                 |                                 | ICK1_RSPI | DN               | 0x14    |

| 0x55                | BUCK1_<br>SLEWCTRL | Rese     | erved            | BUCK<br>SLI                                                |          |                          | Rese                            | erved     |                  | 0x00    |

| 0x5B                | BUCK2_<br>RAMP     | Reserved | BUCK2_<br>DVS_UP |                                                            | Reserved |                          | BUCK2_<br>DVS_DO<br>WN          | Rese      | erved            | 0x44    |

| 0x5F                | BUCK2_<br>CFG0     |          |                  |                                                            | Reserved |                          |                                 |           | BUCK2_<br>DIS    | 0x01    |

| 0x62                | BUCK2_<br>DVS0CFG1 |          |                  |                                                            | BUCK2    | 2_DVS0                   |                                 |           |                  | 0x8C    |

| 0x63                | BUCK2_<br>DVS0CFG0 | Rese     | erved            | BUCK2_<br>DVS0M<br>ODE                                     |          | Rese                     | erved                           |           | BUCK2_<br>ENDVS0 | 0x00    |

| 0x64                | BUCK2_<br>DVS1CFG1 |          |                  |                                                            | BUCK2    | 2_DVS1                   |                                 |           |                  | 0x8C    |

| 0x65                | BUCK2_<br>DVS1CFG0 | Rese     | erved            | ed BUCK2_<br>DVS1M Reserved BUCK2_<br>DDE BUCK2_<br>ENDVS1 |          |                          |                                 |           | 0x00             |         |

| 0x6C                | BUCK2_<br>DVSCFG   |          |                  | Reserved BUCK2_<br>DVSPIN _POL CTRL                        |          |                          |                                 | 0x00      |                  |         |

| 0x6E                | BUCK2_<br>RSPCFG   | Reserved | BL               | JCK2_RSPI                                                  | UP       | Reserved                 | BL                              | ICK2_RSPI | DN               | 0x14    |

| Register<br>Address | Register<br>Name   | Bit 7    | Bit 6                                               | Bit 5                            | Bit 4                                    | Bit 3  | Bit 2                    | Bit 1 | Bit 0            | Default |

|---------------------|--------------------|----------|-----------------------------------------------------|----------------------------------|------------------------------------------|--------|--------------------------|-------|------------------|---------|

| 0x6F                | BUCK2_<br>SLEWCTRL | Rese     | erved                                               | BUCK:<br>SLI                     |                                          |        | Rese                     | erved |                  | 0x00    |

| 0x75                | BUCK3_<br>RAMP     | Reserved | BUCK3_<br>DVS_UP                                    |                                  | Reserved BUCK3_<br>DVS_DO Reserved<br>WN |        |                          |       | erved            | 0x44    |

| 0x79                | BUCK3_<br>CFG0     |          |                                                     |                                  | Reserved BUCK3_<br>DIS                   |        |                          |       |                  |         |

| 0x7C                | BUCK3_<br>DVS0CFG1 |          |                                                     | BUCK3_DVS0                       |                                          |        |                          |       |                  | 0x8C    |

| 0x7D                | BUCK3_<br>DVS0CFG0 | Rese     | erved BUCK3_<br>DVS0M Reserved BUCK3_<br>DDE BUCK3_ |                                  |                                          |        |                          |       | 0x00             |         |

| 0x7E                | BUCK3_<br>DVS1CFG1 |          |                                                     |                                  | BUCK3                                    | B_DVS1 |                          |       |                  | 0x8C    |

| 0x7F                | BUCK3_<br>DVS1CFG0 | Rese     | erved                                               | BUCK3_<br>DVS1M<br>ODE           |                                          | Rese   | erved                    |       | BUCK3_<br>ENDVS1 | 0x00    |

| 0x86                | BUCK3_<br>DVSCFG   |          |                                                     | Reserved                         |                                          |        | BUCK3_<br>DVSPIN<br>_POL |       | B_DVS_<br>RL     | 0x00    |

| 0x88                | BUCK3_<br>RSPCFG   | Reserved | BL                                                  | BUCK3_RSPUP Reserved BUCK3_RSPDN |                                          |        |                          | 0x14  |                  |         |

| 0x89                | BUCK3_<br>SLEWCTR  | Rese     | erved                                               | BUCK:<br>SLE                     |                                          |        | Rese                     | erved |                  | 0x00    |

#### Table 4. I<sup>2</sup>C Register Map

| Register<br>Address | 0x     | 01          | Register<br>Name |       | IO_CHIPNAME |        |       |       |  |  |  |

|---------------------|--------|-------------|------------------|-------|-------------|--------|-------|-------|--|--|--|

| Bits                | Bit 7  | Bit 7 Bit 6 |                  | Bit 4 | Bit 3       | Bit 2  | Bit 1 | Bit 0 |  |  |  |

| Default             | 0      | 0           | 0                | 0     | 0           | 0      | 0     | 1     |  |  |  |

| Read/Write          | R      | R           | R                | R     | R           | R      | R     | R     |  |  |  |

| Bits                | Na     | me          |                  |       | Descr       | iption |       |       |  |  |  |

| Bit 7 to Bit 0      | IO_CHI | IO_CHIPNAME |                  |       | IO_CHIPNAME |        |       |       |  |  |  |

| Register<br>Address | 0x      | 02          | Register<br>Name | IO_CHIPVERSION |       |       |       |       |  |

|---------------------|---------|-------------|------------------|----------------|-------|-------|-------|-------|--|

| Bits                | Bit 7   | Bit 7 Bit 6 |                  | Bit 4          | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |

| Default             | 0       | 0           | 0                | 0              | 0     | 0     | 0     | 1     |  |

| Read/Write          | R       | R           | R                | R              | R     | R     | R     | R     |  |

| Bits                | Na      | me          |                  | Description    |       |       |       |       |  |

| Bit 7 to Bit 0      | IO_CHIP | VERSION     |                  | IO_CHIPVERSION |       |       |       |       |  |

| Register<br>Address | 0x0A  |             | Register<br>Name | IO_DIEID3   |       |       |       |       |  |  |

|---------------------|-------|-------------|------------------|-------------|-------|-------|-------|-------|--|--|

| Bits                | Bit 7 | Bit 7 Bit 6 |                  | Bit 4       | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

| Default             | 1     | 1           | 1                | 1           | 1     | 1     | 1     | 0     |  |  |

| Read/Write          | R     | R           | R                | R           | R     | R     | R     | R     |  |  |

| Bits                | Name  |             |                  | Description |       |       |       |       |  |  |

| Bit 7 to Bit 0      | IO_D  | IEID3       |                  | IO_DIEID3   |       |       |       |       |  |  |

| Register<br>Address | 0x    | 0B    | Register<br>Name | IO_DIEID2   |       |       |       |       |  |  |

|---------------------|-------|-------|------------------|-------------|-------|-------|-------|-------|--|--|

| Bits                | Bit 7 | Bit 6 | Bit 5            | Bit 4       | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

| Default             | 1     | 1     | 0                | 1           | 1     | 1     | 0     | 0     |  |  |

| Read/Write          | R     | R     | R                | R           | R     | R     | R     | R     |  |  |

| Bits                | Na    | me    |                  | Description |       |       |       |       |  |  |

| Bit 7 to Bit 0      | IO_D  | IEID2 |                  | IO_DIEID2   |       |       |       |       |  |  |

| Register<br>Address | 0x0C  |       | Register<br>Name |           | IO_DIEID1 |        |       |       |  |  |  |

|---------------------|-------|-------|------------------|-----------|-----------|--------|-------|-------|--|--|--|

| Bits                | Bit 7 | Bit 6 | Bit 5            | Bit 4     | Bit 3     | Bit 2  | Bit 1 | Bit 0 |  |  |  |

| Default             | 1     | 1 0   |                  | 1         | 1         | 0      | 1     | 0     |  |  |  |

| Read/Write          | R     | R     | R                | R         | R         | R      | R     | R     |  |  |  |

| Bits                | Na    | me    |                  |           | Descr     | iption |       |       |  |  |  |

| Bit 7 to Bit 0      | IO_D  | IEID1 |                  | IO_DIEID1 |           |        |       |       |  |  |  |

| Register<br>Address | 0x        | 0D    | Register<br>Name | IO_DIEID0                                                     |             |   |   |   |  |  |

|---------------------|-----------|-------|------------------|---------------------------------------------------------------|-------------|---|---|---|--|--|

| Bits                | Bit 7     | Bit 6 | Bit 5            | Bit 5         Bit 4         Bit 3         Bit 2         Bit 1 |             |   |   |   |  |  |

| Default             | 1         | 0     | 0                | 1                                                             | 1           | 0 | 0 | 0 |  |  |

| Read/Write          | R         | R     | R                | R                                                             | R           | R | R | R |  |  |

| Bits                | Na        | Name  |                  |                                                               | Description |   |   |   |  |  |

| Bit 7 to Bit 0      | IO_DIEID0 |       |                  | IO_DIEID0                                                     |             |   |   |   |  |  |

| Register<br>Address | 0x     | 0F     | Register<br>Name                                                                              | IO_SOFTRESET |       |       |       |       |  |  |

|---------------------|--------|--------|-----------------------------------------------------------------------------------------------|--------------|-------|-------|-------|-------|--|--|

| Bits                | Bit 7  | Bit 6  | Bit 5                                                                                         | Bit 4        | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |

| Default             | 0      | 0      | 0                                                                                             | 0            | 0     | 0     | 0     | 0     |  |  |

| Read/Write          | R      | R      | R                                                                                             | R            | R     | R     | R     | RW    |  |  |

| Bits                | Na     | me     |                                                                                               | Description  |       |       |       |       |  |  |

| Bit 7 to Bit 1      | Rese   | erved  | Reserved b                                                                                    | ved bits     |       |       |       |       |  |  |

| Bit 0               | IO_SOF | TRESET | Reset all digital functions to default setting.<br>0: Not changed<br>1: Reset and bit cleared |              |       |       |       |       |  |  |