## **RTQ2183-QA**

# 5.5V, 3A, 2.4MHz, Automotive Synchronous Buck Converter

### 1 General Description

The RTQ2183-QA is a synchronous buck converter designed to operate within an input voltage range of 2.5V to 5.5V. It delivers up to 3A output current and supports an adjustable output voltage ranging from 0.6V to 3.3V.

Utilizing Advanced Constant On-Time (ACOT®) control architecture, the RTQ2183-QA achieves fast and stable output voltage regulation, making it ideal for applications with dynamic load requirements. By minimizing the number of external components, The ACOT® architecture minimizes the number of required external components, simplifying design and reducing system cost for efficient power management.

Key features include an independent enable control input and a power-good indicator for easy sequence control. A programmable soft-start function, implemented via an external capacitor on the SS pin, ensures controlled inrush current and smooth power-up.

The RTQ2183-QA provides comprehensive protection functions, including input undervoltage-lockout, output undervoltage protection, output overvoltage protection, overcurrent protection, and over-temperature protection. Cycle-by-cycle current-limit protection safeguards against shorted outputs. The RTQ2183-QA is available in a compact WET-VDFN-8J2L 2x1.5 (FC) package, providing flexibility and space-saving advantages for various system designs.

The recommended junction temperature range is  $-40^{\circ}$ C to 150°C, and ambient temperature range is  $-40^{\circ}$ C to 125°C.

### 2 Features

- AEC-Q100 Grade 1 Qualified

- ±1.5% Output Accuracy from –40°C to 125°C

Junction Temperature Range

- Soft-Start Control with External Css

- Forced PWM Mode

- Input Voltage Range: 2.5V to 5.5V

- Output Voltage Range: 0.6V to 3.3V

- $65m\Omega$  and  $35m\Omega$  Integrated Power MOSFETs

- Fixed 2.4MHz Switching Frequency

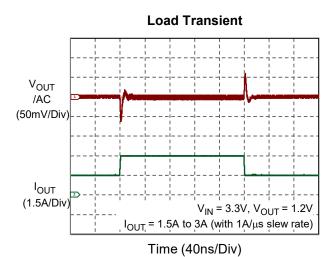

- Fast Load Transient Response with ACOT<sup>®</sup>

Control Topology

- Enable Pin and Soft-Start Pin for Sequence Control

- Power-Good Indicator

- Operate Up to 100% Duty Cycle

- Input Undervoltage-Lockout Protection (UVLO)

- Input Overvoltage-Lockout Protection (OVLO)

- Output Overvoltage Protection (OVP)

- Output Undervoltage Protection (UVP)

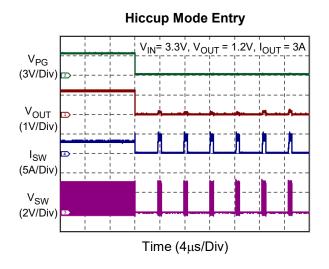

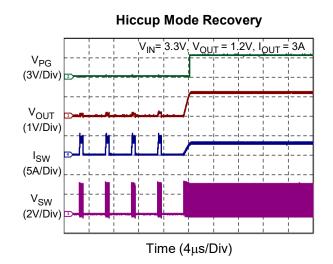

- Short Circuit Protection with Hiccup Mode

- Over-Temperature Protection

- Small Form Factor

- WET-VDFN-8J2L 2x1.5 (FC) Package with Compact BOM

- Ambient Temperature Range: -40°C to 125°C

- Junction Temperature Range: -40°C to 150°C

### 3 Applications

- ADAS

- Automotive IVI

- Automotive Clusters

RICHTEK

November

RTQ2183-QA DS-00

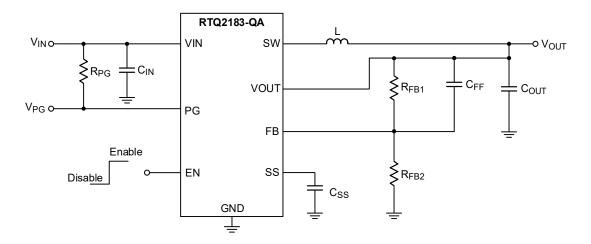

## 4 Simplified Application Circuit

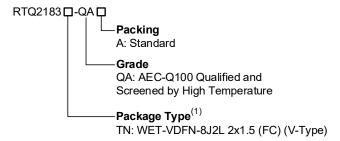

## **5 Ordering Information**

### Note 1.

Richtek products are Richtek Green Policy compliant and marked with <sup>(1)</sup> indicates compatible with the current requirements of IPC/JEDEC J-STD-020.

## **6 Marking Information**

### **Table of Contents**

| 1  | Gene  | eral Description 1                |    | 17.7  | Input Voltage Protection           | 16 |

|----|-------|-----------------------------------|----|-------|------------------------------------|----|

| 2  | Featu | ıres 1                            |    | 17.8  | Overcurrent Protection             | 17 |

| 3  | Appli | ications 1                        |    | 17.9  | Output Active Discharge            | 17 |

| 4  | Simp  | lified Application Circuit2       |    | 17.10 | Output Undervoltage Protection     | 17 |

| 5  | Orde  | ring Information2                 |    | 17.11 | Output Overvoltage Protection      | 18 |

| 6  |       | ing Information2                  |    | 17.12 | Over-Temperature Protection        | 18 |

| 7  | Pin C | Configuration 4                   | 18 | Appli | cation Information                 | 19 |

| 8  |       | tional Pin Description4           |    | 18.1  | Inductor Selection                 | 19 |

| 9  |       | tional Block Diagram5             |    | 18.2  | Input Capacitor Selection          | 19 |

| 10 |       | olute Maximum Ratings 6           |    | 18.3  | Output Capacitor Selection         | 20 |

| 11 | ESD   | Ratings 6                         |    | 18.4  | Output Ripple                      | 21 |

| 12 | Reco  | mmended Operating Conditions 6    |    | 18.5  | Feedback Voltage                   | 21 |

| 13 |       | mal Information6                  |    | 18.6  | EN Pin for Start-Up and Shutdown   |    |

| 14 |       | rical Characteristics7            |    |       | Operations                         | 21 |

| 15 |       | cal Application Circuit9          |    | 18.7  | Power-Good (PG)                    | 22 |

| 16 |       | cal Operating Characteristics10   |    | 18.8  | Thermal Considerations             | 22 |

| 17 | Oper  | ation15                           |    | 18.9  | Layout Considerations              |    |

|    | 17.1  | Advanced Constant On-Time Control | 19 |       | ne Dimension                       |    |

|    |       | and Switching Node Operation15    | 20 |       | orint Information                  |    |

|    | 17.2  | Forced PWM Mode Operation15       | 21 | Packi | ng Information                     |    |

|    | 17.3  | Enable Control15                  |    | 21.1  | Tape and Reel Data                 | 27 |

|    | 17.4  | Soft-Start (SS)15                 |    | 21.2  | Tape and Reel Packing              | 28 |

|    | 17.5  | Maximum Duty Cycle Operation16    |    | 21.3  | Packing Material Anti-ESD Property | 29 |

|    | 17.6  | Power-Good Indication (PG)16      | 22 | Datas | heet Revision History              | 30 |

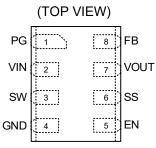

# 7 Pin Configuration

WET-VDFN-8J2L 2x1.5 (FC)

# **8 Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                             |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | PG       | Open-drain, power-good indicator pin for device output status. Connect a $300 k\Omega$ pull-up resistor to the I/O reference power source. The PG output is logic-high when V <sub>FB</sub> exceeds 90% of V <sub>REF</sub> , and is pulled low to ground when V <sub>FB</sub> falls below 85% of V <sub>REF</sub> . If unused, leave this pin floating. |

| 2       | VIN      | Power input. The input voltage range is from 2.5V to 5.5V. Connect at least a 10μF X7R or larger ceramic capacitor between this pin and GND.                                                                                                                                                                                                             |

| 3       | sw       | Switch node between the internal switch and the synchronous rectifier. Connect this pin to an inductor, with the other end connected to the output capacitor.                                                                                                                                                                                            |

| 4       | GND      | Power ground. Connect this pin to the PCB ground plane with multiple vias to optimize thermal performance.                                                                                                                                                                                                                                               |

| 5       | EN       | Enable control input. Pulling this pin high enables the device; pulling it low disables the device.                                                                                                                                                                                                                                                      |

| 6       | SS       | Soft-start capacitor connection. Connect an external capacitor between this pin and ground to set the soft-start time.                                                                                                                                                                                                                                   |

| 7       | VOUT     | Output voltage sense input. Connect this pin to the external output capacitors located near the critical load to maintain the desired output voltage.                                                                                                                                                                                                    |

| 8       | FB       | Feedback sense input pin. Connect this pin to the midpoint of the external feedback resistive divider between VOUT and GND to set the output voltage. The device regulates the FB voltage to a reference value, typically 0.6V.                                                                                                                          |

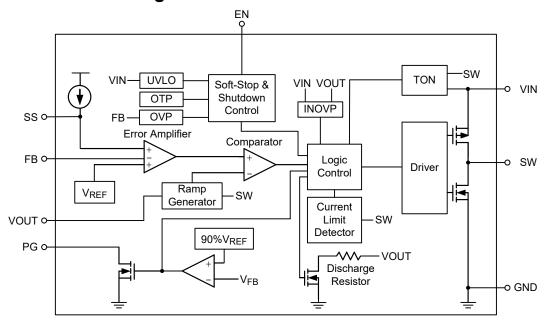

## 9 Functional Block Diagram

### 10 Absolute Maximum Ratings

(Note 2)

| • | Supply Input Voltage, VIN             | -0.3V to 6.5V   |

|---|---------------------------------------|-----------------|

| • | Output Voltage, VOUT                  | −0.3V to 4V     |

| • | VIN to SW                             | -0.3V to $6.5V$ |

| • | VIN to SW (t $\leq$ 10ns)             | -2.5V to 9V     |

| • | Switch Node Voltage, SW               | -0.3V to 6.5V   |

|   | <10ns                                 | −5V to 8V       |

| • | Other I/O Pins Voltages               | -0.3V to 6.5V   |

| • | Junction Temperature                  | 150°C           |

| • | Lead Temperature (Soldering, 10 sec.) | 260°C           |

| • | Storage Temperature Range             | –65°C to 150°C  |

Note 2. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

### 11 ESD Ratings

(Note 3)

ESD Susceptibility

HBM (Human Body Model) ------2kV

Note 3. Devices are ESD sensitive. Handling precautions are recommended.

## 12 Recommended Operating Conditions

(Note 4)

| • | Supply Input Voltage, VIN  | 2.5V to 5.5V   |

|---|----------------------------|----------------|

| • | Output Voltage, VOUT       | 0.6V to 3.3V   |

| • | Junction Temperature Range | -40°C to 150°C |

| • | Ambient Temperature Range  | -40°C to 125°C |

Note 4. The device is not guaranteed to function outside its operating conditions.

### 13 Thermal Information

(Note 5 and Note 6)

|             | Thermal Parameter                                       | WET-VDFN-<br>8J2L 2x1.5 (FC) | Unit |

|-------------|---------------------------------------------------------|------------------------------|------|

| θЈА         | Junction-to-ambient thermal resistance (JEDEC standard) | 99                           | °C/W |

| θJC(Top)    | Junction-to-case (top) thermal resistance               | 121                          | °C/W |

| θJC(Bottom) | Junction-to-case (bottom) thermal resistance            | 8                            | °C/W |

Note 5. For more information about thermal parameter, see the Application and Definition of Thermal Resistances report, AN061.

Note 6.  $\theta_{JA}$  is simulated under natural convection (still air) at  $T_A = 25^{\circ} C$  with the component mounted on a high effectivethermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.

### 14 Electrical Characteristics

( $V_{IN}$  = 3.6V,  $T_J$  = -40 to 150°C, unless otherwise specified.)

| Parameter                                 | Parameter Symbol Test Conditions |                                                          |       | Тур  | Max   | Unit     |

|-------------------------------------------|----------------------------------|----------------------------------------------------------|-------|------|-------|----------|

| Supply Voltage                            |                                  |                                                          |       |      |       |          |

| VIN Supply Input<br>Operating Voltage     | Vin                              | VEN = 2V                                                 | 2.5   |      | 5.5   | V        |

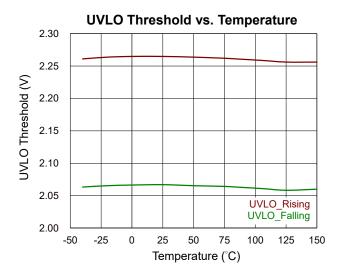

| Undervoltage-Lockout<br>Rising Threshold  | Vuvlo_r                          | VIN rising                                               | 2.15  | 2.3  | 2.45  | <b>V</b> |

| Undervoltage-Lockout<br>Falling Threshold | VUVLO_F                          | V <sub>IN</sub> falling                                  | 1.95  | 2.1  | 2.25  | V        |

| Supply Current                            |                                  | V <sub>EN</sub> = 0V, T <sub>J</sub> = 25°C              |       | 0.01 | 1     |          |

| (Shutdown)                                | ISHDN                            | V <sub>EN</sub> = 0V,<br>T <sub>J</sub> = -40°C to 125°C |       |      | 20    | μА       |

| Supply Current (Quiescent)                | IQ_FPWM                          | VFB = 0.63V                                              |       | 460  | 650   | μΑ       |

| Soft-Start                                |                                  |                                                          |       |      |       |          |

| Soft-Start Charge Current                 | Iss                              | 0%V <sub>FB</sub> to 95%V <sub>FB</sub>                  |       | 0.75 | 0.9   | μΑ       |

| Enable Voltage                            |                                  |                                                          |       |      |       |          |

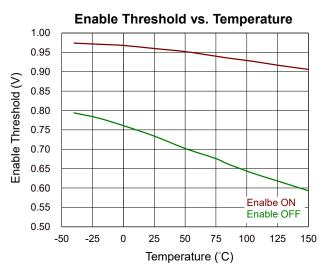

| EN Input Voltage Rising<br>Threshold      | V <sub>EN_R</sub>                | EN high-level input voltage                              | 1.1   |      |       | <        |

| EN Input Voltage Falling<br>Threshold     | V <sub>EN_F</sub>                | EN low-level input voltage                               |       |      | 0.4   | <        |

| Enable Input Current                      | IEN                              | EN = 2V                                                  |       | 1.2  |       | μΑ       |

| Enable Turn-On Delay<br>Time              | tdly_en_on                       | Time for EN on to start switching, SS pin = floating.    |       | 120  |       | μS       |

| Output Voltage                            |                                  |                                                          |       |      |       |          |

| Feedback Threshold                        | \/=p                             | T <sub>J</sub> = 25°C                                    | 0.594 | 0.6  | 0.606 | \/       |

| Voltage                                   | VFB                              | T <sub>J</sub> = -40°C to 125°C                          | 0.591 | 0.6  | 0.609 | V        |

| Feedback Current                          | IFB                              | V <sub>FB</sub> = 0.63V                                  |       | 50   | 100   | nA       |

| Internal MOSFET                           |                                  |                                                          |       |      |       |          |

| High-Side On-Resistance                   | RDSON_H                          | V <sub>IN</sub> = 5V                                     | -     | 65   |       | mΩ       |

| Low-Side On-Resistance                    | RDSON_L                          | VIN = 5V                                                 |       | 35   |       | 11122    |

| Current Limit                             |                                  |                                                          |       |      |       |          |

| High-Side Switch Peak<br>Current Limit    | Ішм_н                            |                                                          | 4     | 5    | 6     | А        |

| Low-Side Switch Valley<br>Current Limit   | ILIM_L                           |                                                          |       | 3    |       | τ        |

| Low-Side Switch Negative Current Limit    | ILIM_N                           | Current flow from SW to GND                              |       | 1.2  |       | Α        |

| Parameter                                    | Test Conditions      | Min                                                                                        | Тур | Max | Unit |          |

|----------------------------------------------|----------------------|--------------------------------------------------------------------------------------------|-----|-----|------|----------|

| Switching                                    |                      |                                                                                            |     | l   |      |          |

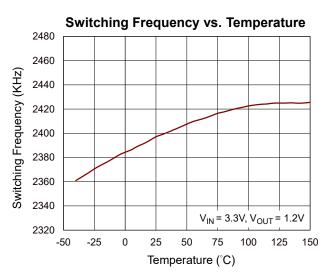

| Switching Frequency                          | fsw                  | VIN = 3.3V, VOUT = 1.2V, FCCM                                                              | 2   | 2.4 | 2.67 | MHz      |

| Minimum Off-Time                             | toff_min             | VIN = 5V                                                                                   | 1   | 80  |      | ns       |

| Maximum Duty Cycle                           | Dмах                 |                                                                                            |     |     | 100  | %        |

| Switch Pin Leakage<br>Current                | Isw_LK               | EN = 0V, V <sub>IN</sub> = 6V, V <sub>SW</sub> = 0V or 6V, T <sub>J</sub> = -40°C to 125°C | -   |     | 30   | μА       |

| Protection                                   |                      |                                                                                            |     |     |      |          |

| Input Overvoltage<br>Protection Threshold    | VIN_OVP              | After Vous exchied                                                                         |     | 6.1 |      | V        |

| Input Overvoltage<br>Protection Hysteresis   | VIN_OVP_HYS          | After Vout_ovp enabled                                                                     | 1   | 160 |      | mV       |

| Output Overvoltage<br>Protection Threshold   | VOUT_OVP             |                                                                                            | 110 | 115 | 120  | %        |

| Output Overvoltage<br>Protection Hysteresis  | Vout_ovp_hys         | Overvoltage protection release                                                             |     | 10  |      | %        |

| Output Undervoltage<br>Protection Threshold  | VOUT_UVP             |                                                                                            |     | 40  |      | %        |

| Output Undervoltage<br>Protection Hysteresis | Vout_uvp_hys         | Undervoltage protection release                                                            |     | 10  |      | %        |

| Over-Temperature Protect                     | tion                 |                                                                                            |     |     |      |          |

| Over-Temperature<br>Protection Threshold     | T <sub>OTP</sub>     |                                                                                            |     | 170 |      | °C       |

| Over-Temperature<br>Protection Hysteresis    | T <sub>OTP_HYS</sub> |                                                                                            |     | 20  |      | O        |

| Power-Good                                   |                      |                                                                                            |     |     |      |          |

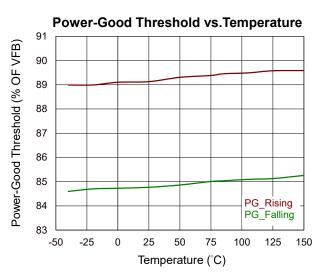

| Power-Good High<br>Threshold                 | VPG_H                | V <sub>OUT</sub> rising, PG from low to high                                               | 87  | 90  | 93   | %VFB     |

| Power-Good Low<br>Threshold                  | VPG_L                | V <sub>OUT</sub> falling, PG from high to low                                              | 82  | 85  | 88   | 70 V F B |

| Power-Good Delay Time                        | tDLY_PG              |                                                                                            | -   | 80  |      | μS       |

| Power-Good High-Level Voltage                | VPG_HL               | VIN = 5V, VFB = 0.6V                                                                       | 4.6 |     |      | V        |

| Power-Good Low-Level Voltage                 | VPG_LL               | Sink current = 1mA                                                                         | 0   |     | 250  | mV       |

| Power-Good Leakage<br>Current                | lpg_lk               | Pull-up voltage is 5V                                                                      |     |     | 100  | nA       |

| Self-Bias PG                                 |                      | When VIN = 0 & EN =0, PG pull-up voltage = 3.6V, pull-up resistor = $300k\Omega$ (Note 7)  |     |     | 0.7  | V        |

| Output Discharge Resisto                     | or                   |                                                                                            |     |     |      |          |

| Output Discharge Switch<br>On-Resistance     | RDISCHG              | VEN = 0V, VOUT = 1.2V                                                                      |     | 5   | 10   | Ω        |

Note 7. Guaranteed by design.

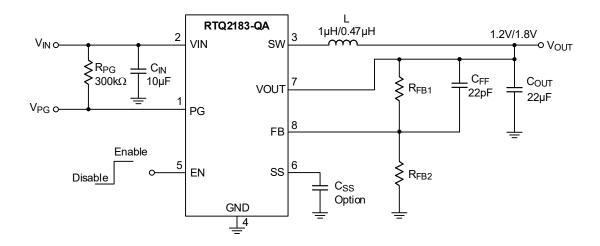

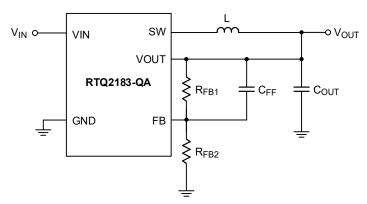

# 15 Typical Application Circuit

Table 1. Recommended External Components for 3A Maximum Load Current (Note 8)

| Component                   | Part Number       | Description           | Manufacturer |  |

|-----------------------------|-------------------|-----------------------|--------------|--|

| Cin                         | GCM21BC71C106KE36 | 10μF/16V/X7S/0805     | MURATA       |  |

| Соит                        | GCM21BD70J226ME36 | 22μF/6.3V/X7T/0805    | MURATA       |  |

| L (For 1.8V)                | DFE32CAHR47MR0    | 470nH/8.7A/14mΩ       | MURATA       |  |

| L (For 1.2V)                | XEL4020-102MEC    | 1μH/9A/14.6m $\Omega$ | COILCRAFT    |  |

| CFF                         | GCM1555C1H220JA16 | 22pF/50V/C0G/0402     | MURATA       |  |

| RFB1 (For 1.8V)             | MR04X1003FTL      | 100kΩ/1%/0402         | WALSIN       |  |

| RFB2 (For 1.8V)             | MR04X4992FTL      | 49.9kΩ/1%/0402        | WALSIN       |  |

| RFB1 (For 1.2V)             | MR04X1003FTL      | 100kΩ/1%/0402         | WALSIN       |  |

| R <sub>FB2</sub> (For 1.2V) | MR04X1003FTL      | 100kΩ/1%/0402         | WALSIN       |  |

| Rpg                         | MR04X3003FTL      | 300kΩ/1%/0402         | WALSIN       |  |

**Note 8**. All the input and output capacitors are the suggested values, referring to the effective capacitances, subject to any derating effect, like a DC bias.

November

RTQ2183-QA DS-00

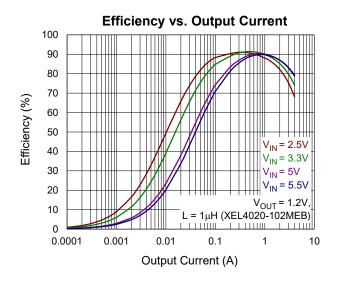

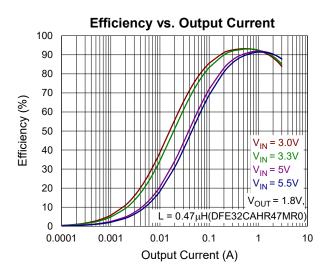

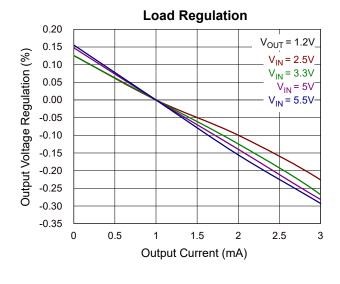

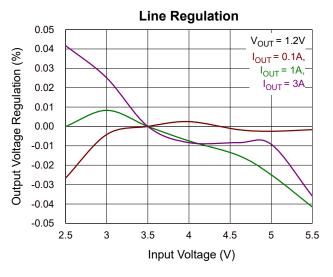

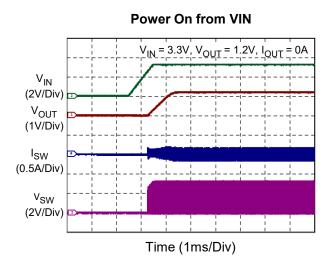

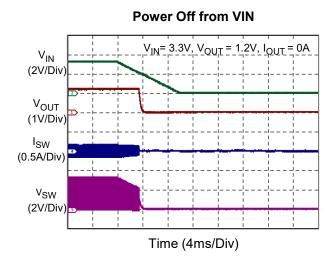

## 16 Typical Operating Characteristics

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

November

RTQ2183-QA DS-00

**RICHTEK** is a registered trademark of Richtek Technology Corporation.

2025

### 17 Operation

The RTQ2183-QA is a synchronous buck converter capable of delivering up to 3A output current from a 2.5V to 5.5V input supply.

#### Advanced Constant On-Time (ACOT®) Control and Switching Node Operation 17.1

The RTQ2183-QA utilizes ACOT® control to achieve ultrafast transient response, reduce external component count, and ensure stability with low ESR MLCC output capacitors. When the feedback voltage drops below the reference and the minimum off-time one-shot (80ns, typical) has expired with inductor current below the currentlimit threshold, the internal on-time one-shot circuitry is triggered, turning on the high-side switch. The short minimum off-time enables ultrafast transient response and allows for smaller output capacitance.

The on-time duration is inversely proportional to the input voltage and directly proportional to the output voltage, maintaining a pseudo-fixed switching frequency across the input range. After the on-time period, the high-side switch turns off, and the low-side switch turns on until the next on-time trigger. In the steady state, the error amplifier compares the feedback voltage (VFB) to the internal reference voltage. If the virtual inductor current ramp voltage is lower than the output of the error amplifier, a new fixed on-time is triggered.

#### 17.2 **Forced PWM Mode Operation**

The RTQ2183-QA operates in forced PWM mode (FCCM) for applications requiring exclusion of switching harmonics from the signal band. While FCCM mode reduces light load efficiency, it provides low output voltage ripple, precise output voltage regulation, fast transient response, and stable switching frequency.

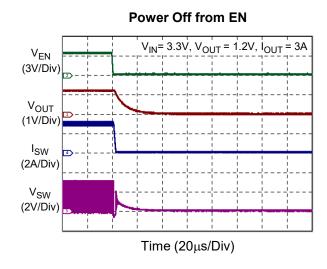

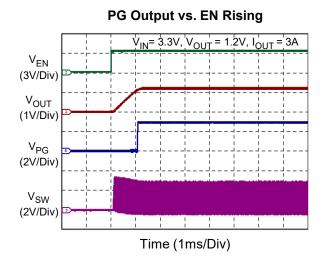

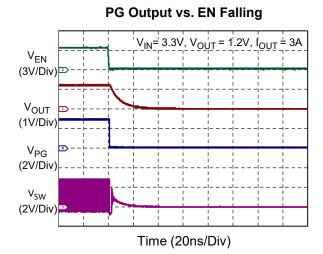

#### 17.3 **Enable Control**

The RTQ2183-QA features an EN pin for external enable control. If the EN pin voltage (VEN) is below the falling threshold (VEN F), the converter disables its output, regardless of VIN voltage being above the input undervoltagelockout rising threshold (V<sub>UVLO</sub> R). In shutdown mode, the supply current is reduced to I<sub>SHDN</sub> (μA). If the EN voltage exceeds the rising threshold (V<sub>EN R</sub>) and the VIN voltage is above the UVLO rising threshold (V<sub>UVLO R</sub>), the device is enabled and the soft-start sequence is initiated.

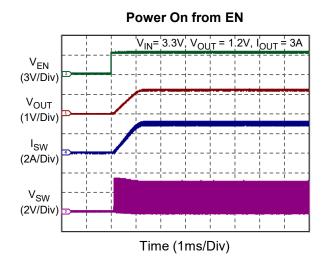

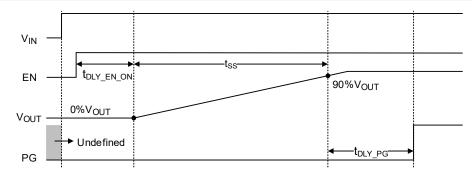

#### 17.4 Soft-Start (SS)

The RTQ2183-QA features an internal soft-start mechanism controlled by an external capacitor. Upon power-up, the external capacitor is charged by an internal current source, generating a soft-start ramp voltage as the reference for the PWM controller. The output voltage ramps smoothly to its target regulation voltage once this ramp voltage exceeds feedback voltage (VFB), ensuring smooth start-up from a pre-biased output. The soft-start time (tss) is determined by the external soft-start capacitor (Css) and the internal charge current (lss ≈ 0.75µA):

$$tss(ms) = \frac{Css(nF) \times 0.6}{Iss(uA)}$$

The minimum soft-start time is approximately 1ms, even if no external Css is connected or the calculated tss is less than 1ms.

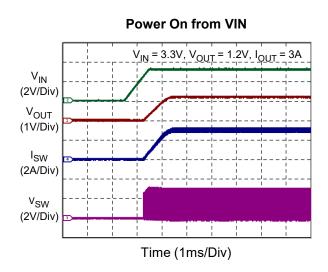

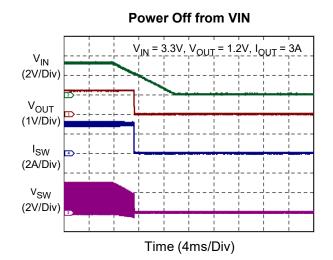

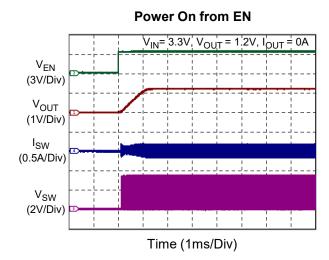

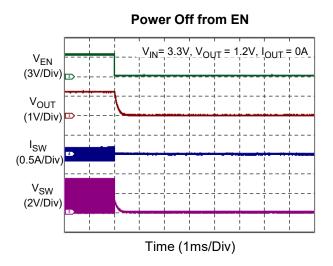

Figure 1. Start-Up Sequence

#### 17.5 Maximum Duty Cycle Operation

The RTQ2183-QA is designed to operate in dropout mode when the duty cycle approaches 100%. If the required off-time becomes less than the minimum off-time, the RTQ2183-QA activates the skip off-time function, allowing the high-side MOSFET to remain continuously on. This enables the converter to achieve a duty cycle close to 100%, so the maximum output voltage is nearly equal to the input supply voltage. The actual dropout voltage depends on several factors, including the input voltage, output voltage, switching frequency, load current, and overall efficiency.

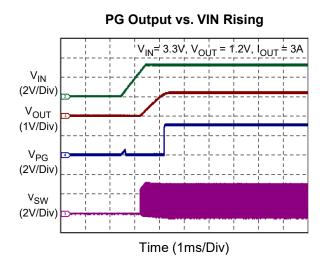

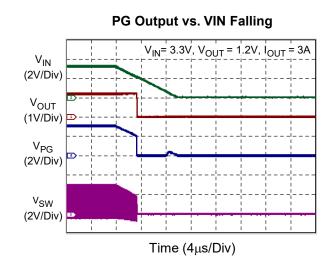

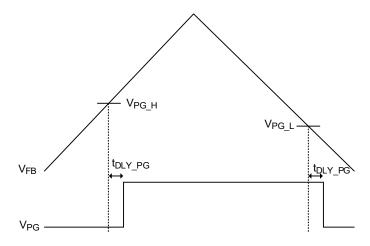

### 17.6 Power-Good Indication (PG)

The RTQ2183-QA features an open-drain power-good output (PG) that indicates the status of the output voltage. The PG pin should be connected to VIN or an external voltage source (not exceeding 5.5V) through a pull-up a resistor.

The power-good function is enabled after the soft-start process and is monitored by a comparator connected to the feedback signal (VFB). When VFB rises above the power-good high threshold (VPG\_H, typically 90% of the reference voltage), the PG pin enters a high-impedance state and the VPG remains high after a short delay. If VFB falls below the power-good low threshold (VPG\_L, typically 85% of the reference voltage), the PG pin is pulled low. Figure 2 illustrates the power-good indication profile.

Figure 2. The Logic of Power-Good Function

#### 17.7 Input Voltage Protection

The RTQ2183-QA is equipped with both input undervoltage-lockout protection (UVLO) and input overvoltage protection overvoltage-lockout protection (OVLO) (VIN\_OVP) to ensure proper operation. The device continuously monitors VIN and initiates soft-start to the regulated output voltage when the VIN voltage rises above the UVLO

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

high threshold (typically 2.3V). If VIN drops below the UVLO low threshold (typically 2.1V), the device shuts down immediately.

Additionally, during output OVP (and only then), if the voltage on the VIN pin exceeds the OVLO threshold (typically 6.1V), the device will immediately shut down to prevent potential damage.

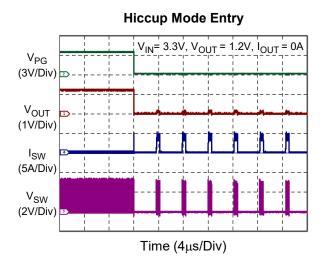

#### 17.8 Overcurrent Protection (OCP)

The RTQ2183-QA features cycle-by-cycle current-limit protection on both the high-side and low-side MOSFETs to prevent catastrophic damage during output short circuits, overcurrent conditions, or inductor saturation.

Overcurrent protection is implemented using an internal current comparator that monitors the current in the high-side MOSFET during each switching cycle. The switch current is compared to the high-side peak current limit (ILIM\_H) and the low-side valley current limit (ILIM\_L). If an overcurrent condition persists, the converter will shut down after a certain number of hiccup cycles.

Negative overcurrent protection is also provided in forced PWM (FPWM) mode by measuring the inductor current through the low-side switch during its on-time. If the current exceeds the low-side negative current limit (ILIM\_N), the low-side switch is turned off immediately.

#### 17.9 Output Active Discharge

When the RTQ2183-QA is disabled due to the EN pin being inactive, an undervoltage-lockout (UVLO), or an over-temperature protection (OTP) event, the device actively discharges the output capacitors through an internal  $5\Omega$  resistor connected to ground via the SW pins. This built-in discharge function prevents reverse current flow from the output to the input capacitors in the event of an input voltage drop. No external active discharge circuit is required. This discharge function ceases once the fault condition is cleared.

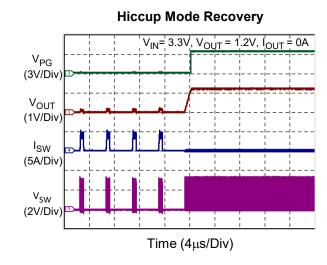

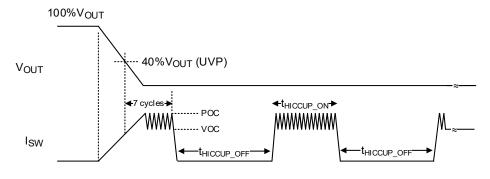

#### 17.10 Output Undervoltage Protection (UVP)

The RTQ2183-QA features output undervoltage protection (UVP) with hiccup mode to safeguard against overloads or short circuits. The IC consistently monitors the feedback voltage (VFB). If VFB drops below the UVP threshold, typically 40% of the reference voltage, the UV comparator is triggered. The IC responds by disabling the low-side and enabling the high-side MOSFET, causing the inductor current to ramp up to the peak current limit (POC) and then down to the valley current limit (VOC). If this condition is detected 7 consecutive cycles, the device enters hiccup mode, shutting down for a predetermined off-time (thiccup\_off), typically 5 times of (2/3 x tss + 76μs), and then attempts recovery for a predetermined on-time (thiccup\_on), typically 1 time (2/3 x tss + 76μs). If the fault is resolved before the soft-start completes, normal operation resumes. Otherwise, the device continues cycling through hiccup mode until the fault is cleared. This mechanism reduces input current and power dissipation, ensuring safe operation and smooth recovery.

Figure 3. Hiccup Mode Behavior

Copyright © 2025 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

### 17.11 Output Overvoltage Protection (OVP)

The RTQ2183-QA includes output overvoltage protection (OVP) to limit output voltage overshoot. If the VFB exceeds 115% of the reference voltage, the PG pin remains high. If the overvoltage condition persists, the low-side MOSFET remains on until the low-side MOSFET valley current reaches the negative current limit –1.2A (typical). If dynamic regulation cannot limit the increase in VOUT, and the input reaches the input OVP threshold (6.1V, typical), the RTQ2183-QA stops switching until the input voltage drops below 6V (typical). The RTQ2183-QA then resumes operation.

### 17.12 Over-Temperature Protection (OTP)

The RTQ2183-QA features over-temperature protection to prevent damage from excessive power dissipation. When the junction temperature exceeds the over-temperature threshold (Totp = 170°C), The converter shuts down switching operation. Normal operation resumes with a complete soft-start sequence once the junction temperature drops below the threshold by the hysteresis value (Totp Hys = 20°C).

Note that the over-temperature protection is designed as a secondary fail-safe for transient overload conditions. It is not intended for continuous operation outside the specified absolute maximum operating junction temperature range. Prolonged operation above the maximum rated temperature may impair device reliability or cause permanent damage.

### 18 Application Information

(Note 9)

The basic application circuit for the RTQ2183-QA is shown in <u>Typical Application Circuit</u>. The selection of external components is determined by the maximum load current. The process begins with selecting the appropriate inductor value and the operating frequency, followed by CIN and COUT.

#### 18.1 Inductor Selection

Inductor selection involves trade-offs among size, cost, efficiency, and transient response. Three key parameters should be considered: inductance value (L), inductor saturation current (ISAT), and DC resistance (DCR).

A common design guideline is to select an inductor that results in a peak-to-peak ripple current of approximately 30% of the IC's rated current, balancing size and power loss. However, the optimal value may vary depending on application constraints. The inductor value is determined by the switching frequency, input voltage, output voltage, and the desired inductor ripple current, using the following equation:

$$L(\mu H) = \frac{V_{OUT}(V) \times \left[V_{IN}(V) - V_{OUT}(V)\right]}{V_{IN}(V) \times f_{SW}(MHz) \times \Delta I_L(A)}$$

To maximize efficiency, choose a low-loss inductor with the lowest possible DC resistance that fits within the available space. The inductor's saturation current rating should exceed the device's peak current limit. The core must be large enough to avoid saturation at the peak inductor current (IL\_PEAK):

$$\Delta L(A) = \frac{V_{OUT}(V) \times \left[V_{IN}(V) - V_{OUT}(V)\right]}{V_{IN}(V) \times f_{SW}(MHz) \times L(\mu H)}$$

$$I_{L\_PEAK}(A) = I_{OUT\_MAX}(A) + \frac{1}{2}\Delta I_{L}(A)$$

The current flowing through the inductor is the inductor ripple current plus the output current. During power-up, faults, or transient load conditions, the inductor current may exceed the calculated peak inductor current value. For robust design, select an inductor with a saturation current rating equal to or greater than the device's switch current limit.

#### 18.2 Input Capacitor Selection

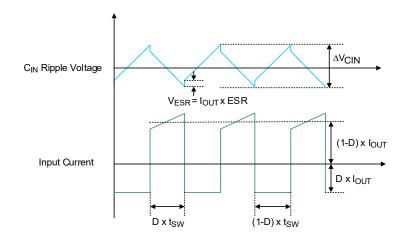

The Input capacitance, CIN, filters the pulsating current at the drain of the high-side power MOSFET. CIN should be sized to minimize input voltage variation. The waveform of CIN ripple voltage and current is shown in <u>Figure 4</u>. The peak-to-peak voltage ripple on the input capacitor can be estimated using the following equation:

$$\Delta V_{\text{CIN\_PP}}(V) = D \times I_{\text{OUT}}(A) \times \frac{1 - D}{C_{\text{IN}}(\mu F) \times f_{\text{SW}}(\text{MHz})} + 2 \times \left[I_{\text{OUT}}(A) \times \text{ESR}(\Omega)\right]$$

$$D = \frac{V_{OUT}(V)}{V_{IN}(V) \times \eta(\%)}, \text{ where } \eta \text{: Estimated efficiency at maximum load.}$$

For ceramic capacitors, the ESR-induced ripple is negligible due to their very low ESR. The minimum input capacitance can be estimated using the following equation:

$$C_{\text{IN\_MIN}}(\mu\text{F}) = I_{\text{OUT\_MAX}}(\text{A}) \times \frac{D \times (1-D)}{\Delta V_{\text{IN\_PP\_MAX}}(\text{V}) \times f_{\text{SW}}(\text{MHz})}$$

Figure 4. CIN Ripple Voltage and Input Current

In addition, the input capacitor must have a very low ESR and be rated to handle the worst-case RMS input current, calculated as:

$$I_{RMS}(A) \; \cong \; I_{OUT\_MAX}(A) \times \frac{V_{OUT}}{V_{IN}} \times \sqrt{\frac{V_{IN}}{V_{OUT}} - 1}$$

For design purposes, it is common to use the worse-case IRMS value, approximately IRMS  $\cong$  IOUT / 2 at VIN = 2 VOUT. Note that capacitor manufacturers often specify ripple current ratings based on a lifespan of only 2000 hours. It is advisable to further de-rate the capacitor, or select a capacitor rated for a higher temperature than required.

Multiple capacitors may be paralleled to meet size, height and thermal requirements. For low input voltage applications, sufficient bulk input capacitance is necessary to minimize transient effects during output load changes.

Ceramic capacitors are ideal for switching regulator applications because of their small size, robustness, and very low ESR. However, care must be taken when using ceramic capacitors at the input.

The input capacitor should be placed as close as possible to the VIN pin, with a low-inductance connection to the PGND of the IC. It is recommended to use a  $10\mu$ F, X7R capacitors between the VIN pin to the PGND pin.

#### 18.3 Output Capacitor Selection

The selection of C<sub>OUT</sub> is determined by the required ESR to minimize output voltage ripple. Additionally, the amount of bulk capacitance is critical to ensure loop stability. Loop stability can be verified by analyzing the load transient response.

The output voltage ripple,  $\Delta Vout$ , can be estimated using the following equation:

$$\Delta V_{OUT\_PP}(V) = \Delta I_{L}(A) \times \left( ESR(\Omega) + \frac{1}{8 \times C_{OUT}(\mu F) \times f_{SW}(MHz)} \right)$$

where fsw is the switching frequency and  $\Delta IL$  is the inductor ripple current. The output voltage ripple will be the highest at the maximum input voltage, as the  $\Delta IL$  increases with the input voltage. Multiple capacitors may be placed in parallel to meet the ESR and RMS current handling requirements. Ceramic capacitors are recommended due to their outstanding low ESR characteristics.

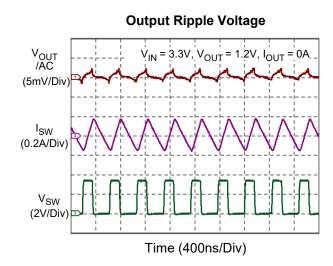

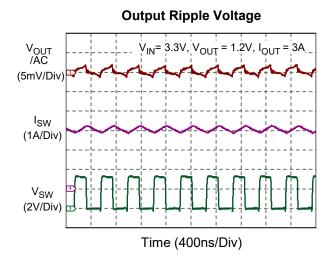

### 18.4 Output Ripple

The output voltage ripple at the switching frequency is determined by the inductor current ripple passing through the output capacitor's impedance. To derive the output voltage ripple, the output capacitor with capacitance, Cout, and its equivalent series resistance, ESR, must be taken into consideration. The total peak-to-peak output voltage ripple (VRIPPLE) consists of two components: the ESR-induced ripple (VRIPPLE(ESR)) and the capacitive ripple (VRIPPLE(C)), and can be expressed as follows:

$$\begin{split} & V_{RIPPLE}(V) = V_{RIPPLE(ESR)}(V) + V_{RIPPLE(C)}(V) \\ & V_{RIPPLE(ESR)}(V) = \Delta I_{L}(A) \times R_{ESR}(\Omega) \\ & V_{RIPPLE(C)}(V) = \frac{\Delta I_{L}(A)}{8 \times C_{OUT}(\mu F) \times f_{SW}(MHz)} \end{split}$$

If ceramic capacitors are used for output capacitors, both the components should be considered due to the extremely low ESR and relatively small capacitance.

### 18.5 Feedback Voltage Setting

Set the output voltage using a resistive divider from the output to ground, with the midpoint connected to FB, as shown in <u>Figure 5</u>. The output voltage is set according to the following equation:

$$V_{OUT} = 0.6V \times (1 + R_{FB1} / R_{FB2})$$

For optimal output voltage accuracy, use resistors with 1% or better tolerance And place the divider as close as possible to the FB pin.

Figure 5. Output Voltage Setting

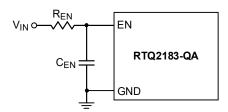

#### 18.6 EN Pin for Start-Up and Shutdown Operations

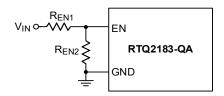

For automatic start-up, the EN pin can be connected to the input supply  $V_{IN}$  directly. The large built-in hysteresis band makes the EN pin suitable for implementing simple delay and timing circuits. To introduce a start-up delay, connect the EN pin to  $V_{IN}$  through a resistor  $R_{EN}$  and a capacitor  $C_{EN}$ , as shown in <u>Figure 6.</u> The delay time can be calculated based on the EN's internal threshold voltage, which determines when switching operation begins.

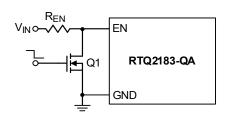

For logic-controlled enable, an external MOSFET can be used, as shown in <u>Figure 7</u>. In this case, a pull-up resistor, REN, connects VIN to the EN pin, while the MOSFET (Q1) pulls the EN pin low under logic control. To prevent the device from being enabled when VIN is below the desired voltage (e.g., less than the Vout target), a resistive

Copyright © 2025 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

divider (REN1 and REN2) can be used to externally set a custom input undervoltage-lockout threshold, as shown in Figure 8.

Figure 6. Enable Timing Control

Figure 7. Logic Control for the EN Pin

Figure 8. Resistive Divider for Undervoltage-Lockout Threshold Setting

#### 18.7 Power-Good (PG)

The PG pin is an open-drain power-good indication output and should be connected to an external voltage source through a pull-up resistor.

The external voltage source can be either an independent supply below 5.5V or the input of the RTQ2183-QA, provided the input voltage is regulated below 5.5V. For reliable operation, it is recommended to keep the PG pullup voltage  $\leq$  VIN. A 300k $\Omega$  pull-up resistor is recommended between the external voltage source and the PG pin.

#### 18.8 **Thermal Considerations**

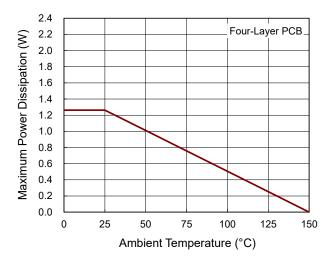

The junction temperature should never exceed the absolute maximum junction temperature TJ(MAX), listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation is influenced by the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_{A}) / \theta_{JA}$$

where TJ(MAX) is the maximum junction temperature, TA is the ambient temperature, and  $\theta$ JA is the junction-toambient thermal resistance. For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 150°C. The junction-to-ambient thermal resistance, θJA, is highly package dependent. For a WET-VDFN-8J2L 2x1.5 (FC) package, the thermal resistance, θJA, is 99°C/W on a

RTQ2183-QA DS-00

standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at T<sub>A</sub> = 25°C can be calculated as below:

$P_{D(MAX)} = (150^{\circ}C - 25^{\circ}C) / (99^{\circ}C/W) = 1.26W$  for a WET-VDFN-8J2L 2x1.5 (FC) package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in <u>Figure 9</u> allows the designer to estimate the effect of rising ambient temperature on the maximum power dissipation.

Figure 9. Derating Curve of Maximum Power Dissipation

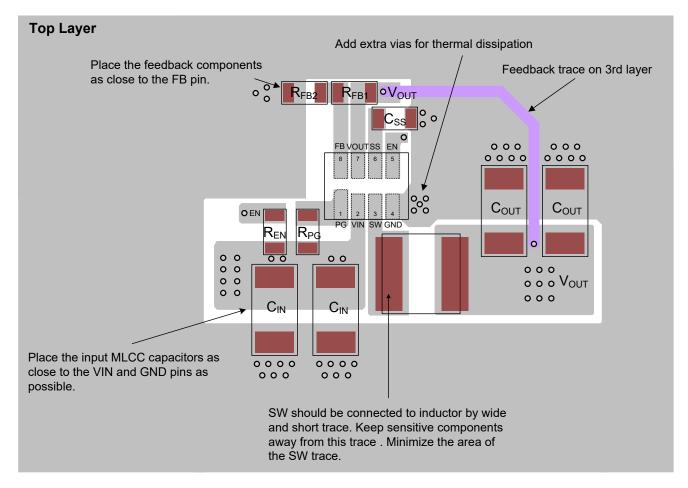

#### 18.9 Layout Considerations

For optimal performance of the RTQ2183-QA, the following layout guidelines must be strictly followed.

- The input capacitor must be placed as close as possible to the IC to minimize the power loop area. A typical 10μF decoupling capacitor is recommended to reduce high-frequency noise on VIN.

- The SW node experiences high-frequency voltage swings Keep the area around the SW node as small as

possible, and ensure analog components are placed away from the SW node to prevent stray capacitive noise

pickup.

- Ensure all power trace connections as wide as possible to improve thermal dissipation.

- Keep the feedback line as short as possible and route it away from the power inductor and other noisy areas.

An example PCB layout is shown in Figure 10.

Figure 10. PCB Layout Guide

**Note 9**. The information provided in this section is for reference only. The customer is solely responsible for the designing, validating, and testing your product incorporating Richtek's product and ensure such product meets applicable standards and any safety, security, or other requirements.

24

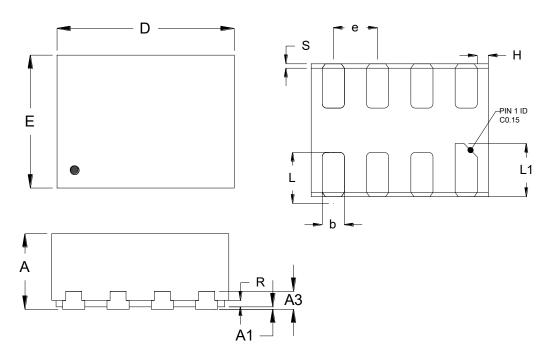

### 19 Outline Dimension

| Sumb al | Dimensions I | n Millimeters | Dimension | s In Inches |

|---------|--------------|---------------|-----------|-------------|

| Symbol  | Min          | Max           | Min       | Max         |

| А       | 0.800        | 1.000         | 0.031     | 0.039       |

| A1      | 0.000        | 0.050         | 0.000     | 0.002       |

| А3      | 0.175        | 0.250         | 0.007     | 0.010       |

| b       | 0.200        | 0.300         | 0.008     | 0.012       |

| D       | D 1.950      |               | 0.077     | 0.081       |

| E       | 1.450        | 1.550         | 0.057     | 0.061       |

| е       | 0.5          | 500           | 0.0       | )20         |

| L       | 0.450        | 0.550         | 0.018     | 0.022       |

| L1      | 0.550        | 0.650         | 0.022     | 0.026       |

| R       | 0.050        | 0.150         | 0.002     | 0.006       |

| S       | 0.001        | 0.090         | 0.000     | 0.004       |

| Н       | 0.1          | 25            | 0.0       | 005         |

WET V-Type 8J2L DFN 2x1.5 Package (FC)

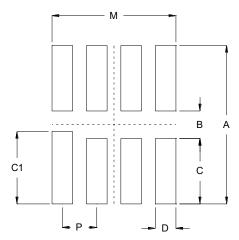

# 20 Footprint Information

|                       | Number of |      |      | Footprint | Dimens | ion (mm) |      |      | Toloropoo |

|-----------------------|-----------|------|------|-----------|--------|----------|------|------|-----------|

| Package               | Pins      | Р    | Α    | В         | С      | C1       | D    | М    | Tolerance |

| WET-VDFN2X1.5-8J2(FC) | 8         | 0.50 | 2.30 | 0.40      | 0.95   | 1.05     | 0.30 | 1.80 | ±0.05     |

## 21 Packing Information

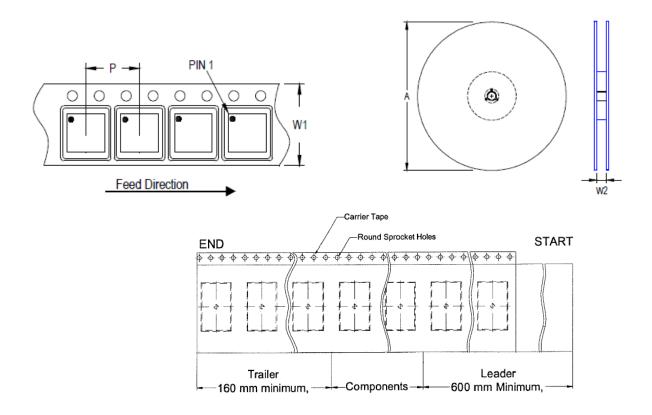

### 21.1 Tape and Reel Data

| D. J. T.                   | Tape Size | Pocket Pitch    | Reel Siz | ze (A) | Units    | Trailer | Leader | Reel Width (W2) |  |

|----------------------------|-----------|-----------------|----------|--------|----------|---------|--------|-----------------|--|

| Package Type               | (W1) (mm) | (P) (mm) (mm) ( |          | (in)   | per Reel | (mm)    | (mm)   | Min./Max. (mm)  |  |

| (V, W)<br>QFN/DFN<br>2x1.5 | 8         | 4               | 180      | 7      | 2,500    | 160     | 600    | 8.4/9.9         |  |

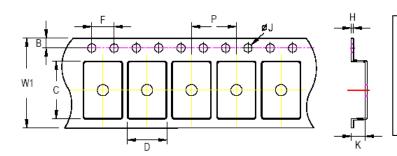

C, D, and K are determined by component size.

The clearance between the components and the cavity is as follows:

- For 8mm carrier tape: 0.5mm max.

| Tono Cizo | W1    | F     | )     | Е      | 3      | F     | -     | Q     | δl    | ŀ     | <     | Н     |

|-----------|-------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| Tape Size | Max.  | Min.  | Max.  | Min.   | Max.   | Min.  | Max.  | Min.  | Max.  | Min.  | Max.  | Max.  |

| 8mm       | 8.3mm | 3.9mm | 4.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 1.0mm | 1.3mm | 0.6mm |

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

**RICHTEK**

is a registered trademark of Richtek Technology Corporation.

#### 21.2 Tape and Reel Packing

| Step | Photo/Description                      | Step | Photo/Description                               |

|------|----------------------------------------|------|-------------------------------------------------|

| 1    | Reel 7"                                | 4    | RICHTEK MARY MARY MARY MARY MARY MARY MARY MARY |

| 2    | HIC & Desiccant (1 Unit) inside        | 5    | 12 inner boxes per outer box                    |

| 3    | Caution label is on backside of Al bag | 6    | Outer box Carton A                              |

| Container          | Reel |       | Вох   |       |       | Carton                        |       |        |

|--------------------|------|-------|-------|-------|-------|-------------------------------|-------|--------|

| Package            | Size | Units | Item  | Reels | Units | Item                          | Boxes | Unit   |

| (V, W)             | 7"   | 2,500 | Box A | 3     | 7,500 | Carton A                      | 12    | 90,000 |

| QFN & DFN<br>2x1.5 |      |       | Box E | 1     | 2,500 | For Combined or Partial Reel. |       |        |

#### 21.3 **Packing Material Anti-ESD Property**

| Surface<br>Resistance     | Aluminum Bag                        | Reel                                | Cover tape                          | Carrier tape                        | Tube                                | Protection Band                     |

|---------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| $\Omega$ /cm <sup>2</sup> | 10 <sup>4</sup> to 10 <sup>11</sup> |

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1st Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

# 22 Datasheet Revision History

| Version | Date       | Description   |

|---------|------------|---------------|

| 00      | 2025/11/12 | First Edition |