# **Automotive High-Accuracy Reset IC with Functional Safety Support**

### 1 General Description

The RTQ2588-QB is a high-accuracy, low-quiescent automotive reset IC. The RTQ2588-QB provides factory-set sensing options with 50mV steps ranging from 0.5V to 1.1V, and 0.1V steps ranging from 1.2V to 5V, covering most automotive applications. It features overvoltage and undervoltage window voltage sensing with factory-set thresholds of  $\pm 4\%$ ,  $\pm 5\%$ ,  $\pm 7\%$ ,  $\pm 9\%$ . The IC operates with a low supply current of 3.5 $\mu$ A.

The RTQ2588-QB does not require external divider resistors to sense the voltage, helping system designers save on solution size and cost while maintaining high accuracy performance. It also provides manual reset  $(\overline{MR})$  and capacitor time (CT) functions to facilitate easy system design.

For automotive functional safety applications, the RTQ2588-QB features a built-in self-test (BIST) as a safety mechanism to enhance system latent point fault metrics (LPFM) scores. The RTQ2588-QB is qualified for AEC-Q100 Grade 1 and is an automotive quality-managed (QM) product from Richtek. It is available in a WDFN-6L 1.5x1.5 (COL) package.

The recommended junction temperature range is  $-40^{\circ}$ C to  $125^{\circ}$ C, and the ambient temperature range is  $-40^{\circ}$ C to  $125^{\circ}$ C.

### 2 Applications

- Advanced Driver Assistance Systems (ADAS)

- DSP, Microcontrollers, SoC Applications

- Body Control Modules (BCM)

- In-Vehicle Infotainment (IVI) Systems

- Digital Instrument Clusters

- Telematics Boxes (T-Box)

#### **3 Features**

- AEC-Q100 Grade 1 Qualified

- Input Voltage Range: 1.7V to 5.5V

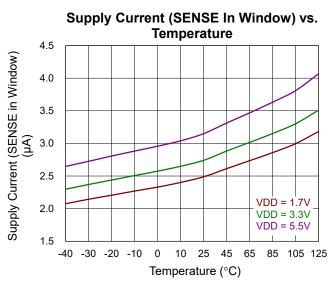

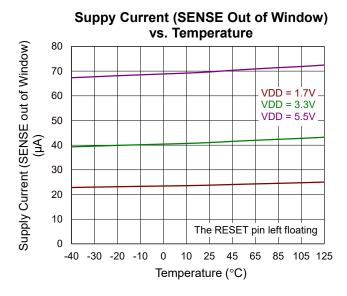

- Low Supply Current: 3.5μA (Typical)

- Undervoltage-Lockout (UVLO): 1.65V Falling Threshold

- High Threshold Accuracy

- ±0.25% Typical

- ±0.78% Full Temperature Range

- Factory-Set Wide Voltage-Sensing Range

- 0.5V to 1.1V in 50mV/step, 1.2V to 5V in 0.1V/step

- Factory-Set Input Threshold Levels

- Available in UV Only and Window Configurations

- Factory-Set Threshold Options Available: ±4%, ±5%, ±7%, ±9%

- Factory-Set Output Type

- Open-Drain (Active-Low); Push-Pull (Active-High or Low)

- Manual Reset Capable

- Factory-Set Fixed Options for Reset Recovery Time Delay

- Option A, E: 50μs, 200μs

- Option B, F: 1ms, 20ms

- Option C, G: 5ms, 100ms

- Option D, H: 10ms, 200ms

- Programmable Reset Recovery Time Delay Option via an External Capacitor

- Support Systematic Capability up to ASIL B Target

- Built-In Self-Test (BIST) for OV/UV Monitors

- Ambient Temperature Range: –40°C to 125°C

- Junction Temperature Range: –40°C to 125°C

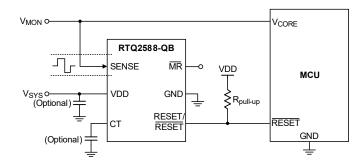

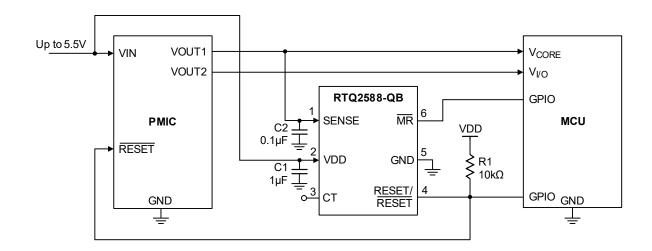

### 4 Simplified Application Circuit

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

RICHTEK

# 5 Marking Information

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

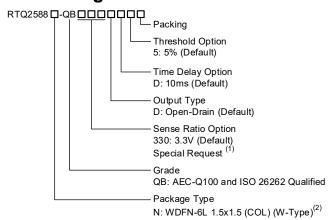

### **6 Ordering Information**

#### Note 1.

- Marked with <sup>(1)</sup> indicated Special Request: Available sensing voltage target with 50mV steps ranging from 0.5V to 1.1V; with 0.1V steps ranging from 1.2V to 5V under specific business agreement.

- Richtek products are Richtek Green Policy compliant and marked with <sup>(2)</sup> indicates compatible with the current requirements of IPC/JEDEC J-STD-020.

#### 6.1 Output Type

| Code | Function                    |

|------|-----------------------------|

| D    | Open-drain type, active-low |

| L    | Push-pull type, active-low  |

| Н    | Push-pull type, active-high |

#### 6.2 Protection Type and Time Delay Option

| Code | Function                                                         |  |

|------|------------------------------------------------------------------|--|

| А    | Window, CT pin left floating = 50μs, CT pin tied to VDD = 200μs  |  |

| В    | Window, CT pin left floating = 1ms, CT pin tied to VDD = 20ms    |  |

| С    | Window, CT pin left floating = 5ms, CT pin tied to VDD = 100ms   |  |

| D    | Window, CT pin left floating = 10ms, CT pin tied to VDD = 200ms  |  |

| Е    | UV only, CT pin left floating = 50μs, CT pin tied to VDD = 200μs |  |

| F    | UV only, CT pin left floating = 1ms, CT pin tied to VDD = 20ms   |  |

| G    | UV only, CT pin left floating = 5ms, CT pin tied to VDD = 100ms  |  |

| Н    | UV only, CT pin left floating = 10ms, CT pin tied to VDD = 200ms |  |

#### 6.3 **Threshold Option**

| Code | Function                               |  |

|------|----------------------------------------|--|

| 4    | UV/OV = ± 4% protection threshold      |  |

| 5    | $UV/OV = \pm 5\%$ protection threshold |  |

| 7    | V/OV = $\pm$ 7% protection threshold   |  |

| 9    | UV/OV = ± 9% protection threshold      |  |

# **RTQ2588-QB**

### **Table of Contents**

| 1  | General Description1                        | 17 | Operation                                    | 16 |

|----|---------------------------------------------|----|----------------------------------------------|----|

| 2  | Applications1                               |    | 17.1 SENSE                                   | 16 |

| 3  | Features 1                                  |    | 17.2 Capacitor Time (CT)                     | 16 |

| 4  | Simplified Application Circuit1             |    | 17.3 RESET/RESET                             | 16 |

| 5  | Marking Information2                        |    | 17.4 Manual Reset (MR)                       | 17 |

| 6  | Ordering Information2                       | 18 | Application Information                      | 18 |

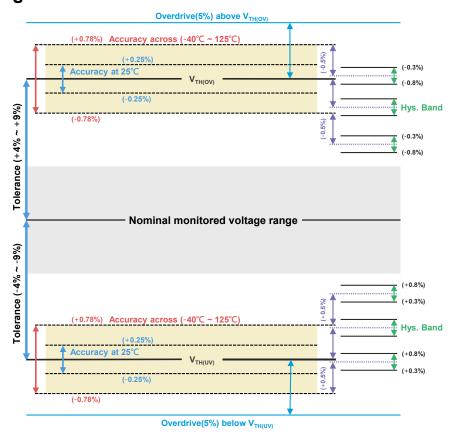

|    | 6.1 Output Type                             |    | 18.1 Voltage Protection Threshold Accuracy   | 18 |

|    | 6.2 Protection Type and Time Delay Option 2 |    | 18.2 Reset Recovery Time Delay Determination | 18 |

|    | 6.3 Threshold Option                        |    | 18.3 Latch Mode on the RESET/RESET Pin       | 19 |

| 7  | Pin Configuration5                          |    | 18.4 Functional Safety Support Capable       | 19 |

| 8  | Functional Pin Description5                 |    | 18.5 Thermal Considerations                  | 19 |

| 9  | Functional Block Diagram6                   |    | 18.6 Layout Considerations                   | 20 |

| 10 | Absolute Maximum Ratings7                   | 19 | Outline Dimension                            | 22 |

| 11 | Recommended Operating Conditions7           | 20 | Footprint Information                        | 23 |

| 12 | Thermal Information7                        | 21 | Packing Information                          | 24 |

| 13 | Electrical Characteristics 8                |    | 21.1 Tape and Reel Data                      | 24 |

| 14 | Typical Application Circuit11               |    | 21.2 Tape and Reel Packing                   | 25 |

| 15 | Timing Diagram12                            |    | 21.3 Packing Material Anti-ESD Property      | 26 |

| 16 | Typical Operating Characteristics13         | 22 | Datasheet Revision History                   | 27 |

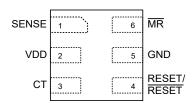

# 7 Pin Configuration

(TOP VIEW)

WDFN-6L 1.5x1.5 (COL)

### **Functional Pin Description**

| Pin No. | Pin Name        | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SENSE           | Input for monitoring the voltage rail. When the SENSE detects OV or UV conditions, the RESET/ RESET pin is asserted. Place a 10nF/10V to 100nF/10V ceramic capacitor close to this pin to improve noisy immunity.                                                                                                                                                                                                                         |

| 2       | VDD             | Power supply input pin. Place a $0.1\mu F/10V$ to $1\mu F/10V$ bypass capacitor close to the VDD pin is recommended.                                                                                                                                                                                                                                                                                                                      |

| 3       | СТ              | Programmable pin for reset recovery time delay. When the CT pin is pulled up to VDD or left floating, it offers two fixed release time delays. Additionally, connecting an external capacitor to ground allows programming different time delays.                                                                                                                                                                                         |

| 4       | RESET/<br>RESET | Open-drain output type for active-low; push-pull output type for active-high or active -low. This pin will be asserted when an OV/UV fault is detected, the BIST fails, or the $\overline{\text{MR}}$ pin is asserted low. If the open-drain output type is in use, connect it to the desired pull-up voltage with a pull-up resistor. On the other hand, if the push-pull output type is in use, no external pull-up resistor is needed. |

| 5       | GND             | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6       | MR              | Manual reset pin. If this pin is pulled low, the RESET/RESET output will be asserted. After the $\overline{\text{MR}}$ pin is de-asserted, the output will go high or low after the reset recovery time delay (t <sub>D</sub> ) expires. It can be left floating when not in use.                                                                                                                                                         |

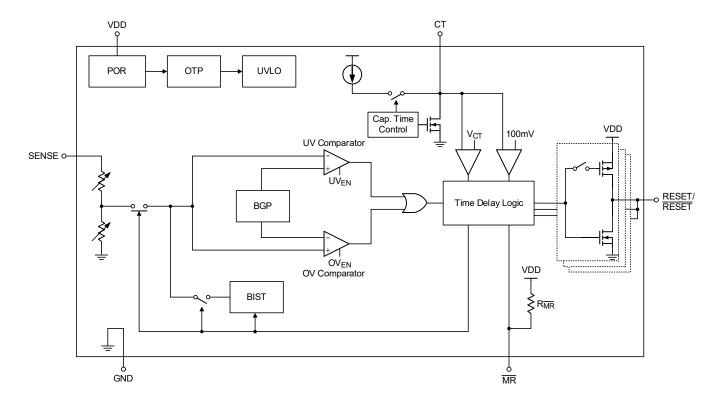

# 9 Functional Block Diagram

www.richtek.com

### 10 Absolute Maximum Ratings

#### (Note 2)

- • IRESET/RESET-----±20mA • Lead Temperature (Soldering, 10 sec.) ------ 260°C • Junction Temperature ------ 150°C ESD Susceptibility (Note 3) HBM (Human Body Model) ------ 2kV

- Note 2. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 3. Devices are ESD sensitive. Handling precautions are recommended.

### 11 Recommended Operating Conditions

#### (Note 4)

| • Supply Voltage, V <sub>DD</sub> | 1.7V to 5.5V                                   |

|-----------------------------------|------------------------------------------------|

| Sense Voltage, Vsense             | 0.5V to 5V                                     |

| Output Voltage, VRESET/RESET      | 0V to 5.5V                                     |

| • MR Voltage, VMR                 | 0V to 5.5V                                     |

| • CT Voltage, VcT                 | Follow to VDD                                  |

| • Ireset/reset                    | -5mA to 5mA                                    |

| Ambient Temperature Range         | $-40^{\circ}\text{C}$ to $125^{\circ}\text{C}$ |

| Junction Temperature Range        | -40°C to 125°C                                 |

**Note 4**. The device is not guaranteed to function outside its operating conditions.

#### 12 Thermal Information

#### (Note 5)

|                     | Thermal Parameter                                       | WDFN-6L 1.5x1.5 (COL) | Unit |

|---------------------|---------------------------------------------------------|-----------------------|------|

| θJΑ                 | Junction-to-ambient thermal resistance (JEDEC standard) | 169.67                | °C/W |

| $\theta$ JC(Top)    | Junction-to-case (top) thermal resistance               | 217.4                 | °C/W |

| $\theta$ JC(Bottom) | Junction-to-case (bottom) thermal resistance            | 42.4                  | °C/W |

| θЈВ                 | Junction-to-board thermal resistance                    | 71.9                  | °C/W |

Note 5. For more information about thermal parameter, see the Application and Definition of Thermal Resistances report, AN061.

### 13 Electrical Characteristics

$(T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C}, V_{\overline{RESET}} = 10\text{k}\Omega \text{ to } V_{DD}, \text{ the CT and } \overline{\text{MR}} \text{ pins are open, Reset load} = 10\text{pF. Typical condition is } V_{DD} = 3.3\text{V}, VDD \text{ ramp rate} \leq 270\text{mV/}\mu\text{s with } \Delta\text{V} = 0.6\text{V} \text{ (Note 6)}, \text{ unless otherwise specified.)}$

| Parameter                                     | Symbol              | Test Conditions                                                  | Min                      | Тур   | Max  | Unit |  |

|-----------------------------------------------|---------------------|------------------------------------------------------------------|--------------------------|-------|------|------|--|

| Supply Voltage                                | VDD                 |                                                                  | 1.7                      |       | 5.5  | V    |  |

| Supply Current                                | IDD                 | 1.7V ≤ V <sub>DD</sub> ≤ 5.5V                                    |                          | 3.5   | 7    | μА   |  |

| Power-On Reset Voltage (Note 7)               | VPOR                | V <sub>OL(max)</sub> = 250mV, I <sub>OUT</sub> = 15μA            |                          |       | 1    | V    |  |

| Undervoltage-Lockout                          | UVLOF               |                                                                  | 1.548                    | 1.62  | 1.65 |      |  |

| ( <u>Note 8</u> )                             | UVLOR               |                                                                  | 1.6                      | 1.65  | 1.7  | V    |  |

| Sensing Current                               | ISENSE              | Vsense = 5V                                                      |                          | 1     | 1.5  | μА   |  |

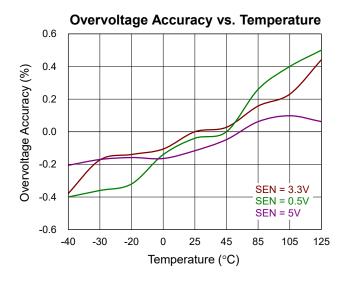

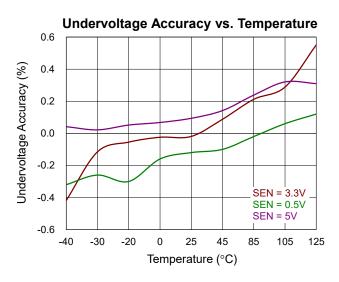

| Positive-Going Threshold Voltage Accuracy     | VACC_P              |                                                                  | -0.78                    | ±0.25 | 0.78 | %    |  |

| Negative-Going Threshold Voltage Accuracy     | VACC_N              |                                                                  | -0.78                    | ±0.25 | 0.78 | %    |  |

| Trimmoned Threehold Donne                     | VTH(OV)             |                                                                  | 4                        |       | 9    | 0/   |  |

| Triggered Threshold Range                     | V <sub>TH(UV)</sub> |                                                                  | -9                       |       | -4   | %    |  |

| Hysteresis Voltage (Note 9)                   | VHYS                |                                                                  | 0.3                      | 0.5   | 0.8  | %    |  |

| Low Level Output Voltage                      | VoL                 | V <sub>DD</sub> = 1.7V, I <sub>OUT</sub> = 0.4mA                 |                          |       | 350  | mV   |  |

|                                               |                     | V <sub>DD</sub> = 2V, I <sub>OUT</sub> = 3mA                     |                          |       | 350  |      |  |

|                                               |                     | V <sub>DD</sub> = 5V, I <sub>OUT</sub> = 5mA                     |                          |       | 350  |      |  |

|                                               |                     | V <sub>DD</sub> = 1.7V, I <sub>OUT</sub> = -0.4mA                | 0.8 x<br>VDD             |       |      |      |  |

| High Level Output Voltage                     | Vон                 | V <sub>DD</sub> = 2V, I <sub>OUT</sub> = -3mA                    | 0.8 x<br>V <sub>DD</sub> |       |      | V    |  |

|                                               |                     | V <sub>DD</sub> = 5V, I <sub>OUT</sub> = -5mA                    | 0.8 x<br>VDD             |       |      |      |  |

| Output Leakage Current                        | ILEAK               | V <sub>DD</sub> = V <sub>RESET</sub> = 5.5V<br>(Open-Drain Type) |                          |       | 300  | nA   |  |

| Comparator Threshold<br>Voltage of the CT Pin | Vст_тн              |                                                                  | 1.14                     | 1.21  | 1.28 | V    |  |

| High Level Voltage of the CT Pin              | Vст_н               |                                                                  | 1.4                      |       |      | V    |  |

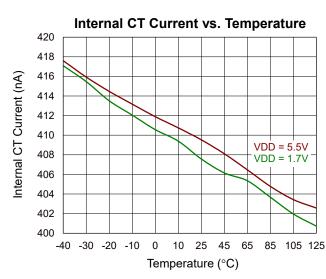

| Charging Current of the CT<br>Pin             | Іст                 |                                                                  | 320                      | 400   | 495  | nA   |  |

| MR Logic-Low Input                            | VMR_L               |                                                                  |                          |       | 0.3  | V    |  |

| MR Logic-High Input                           | VMR_H               |                                                                  | 1.4                      |       |      | V    |  |

| Internal Pull-Up Resistance of the MR Pin     | RMR                 |                                                                  |                          | 100   |      | kΩ   |  |

| Timing Requirements                           |                     |                                                                  |                          |       |      |      |  |

| Reset Recovery Time                           | to                  | CT = Floating                                                    | 35                       | 50    | 65   |      |  |

| Delay (A, E)                                  | t <sub>D</sub>      | CT = 10kΩ to V <sub>DD</sub>                                     | 140                      | 200   | 260  | μS   |  |

| Parameter                                                                              | Symbol              | Test Conditions                        | Min  | Тур           | Max | Unit |

|----------------------------------------------------------------------------------------|---------------------|----------------------------------------|------|---------------|-----|------|

| Reset Recovery Time                                                                    | 4-                  | CT = Floating                          | 0.7  | 1             | 1.3 |      |

| Delay (B, F)                                                                           | tD                  | CT = $10k\Omega$ to $V_{DD}$           | 14   | 20            | 26  | ms   |

| Reset Recovery Time                                                                    | 4-5                 | CT = Floating                          | 3.5  | 5             | 6.5 |      |

| Delay (C, G)                                                                           | tD                  | CT = 10kΩ to VDD                       | 70   | 100           | 130 | ms   |

| Reset Recovery Time                                                                    | to                  | CT = Floating                          | 7    | 10            | 13  | ma   |

| Delay (D, H)                                                                           | tD                  | CT = $10k\Omega$ to VDD                | 140  | 200           | 260 | ms   |

| Deglitch Time for<br>Undervoltage V <sub>TH(UV)</sub> ,<br>(5% Overdrive)<br>(Note 10) | tDG(VTH-)           |                                        |      | 3             | 1   | μs   |

| Deglitch Time for<br>Overvoltage VTH(OV),<br>(5% Overdrive)<br>(Note 10)               | tDG(VTH+)           |                                        |      | 3             | 1   | μs   |

| Output Rising Time<br>(Open-Drain Type)<br>(Note 10) (Note 11)                         | tR                  |                                        |      | 300           | ł   | ns   |

| Output Rising Time<br>(Push-Pull Type)<br>(Note 10) (Note 11)                          | tR                  |                                        |      |               | 25  | ns   |

| Output Falling Time (Note 10) (Note 11)                                                | tF                  |                                        |      |               | 25  | ns   |

| Propagation Time Delay (Note 10) (Note 12)                                             | tPD                 |                                        |      | 17            | 45  | μS   |

| Deglitch Time for the $\overline{MR}$<br>Pin Low                                       | tDG(MR_L)           |                                        | 0.45 |               | 3.8 | μS   |

| Propagation Time Delay from the MR Pin Low to Assert RESET/RESET                       | t <sub>PD(MR)</sub> |                                        |      | 1.6           | 4.3 | μS   |

| Pulse Low Width Duration Time of the MR Pin Low to Assert RESET/RESET                  | tpwd(MR)            |                                        | 4.5  |               |     | μS   |

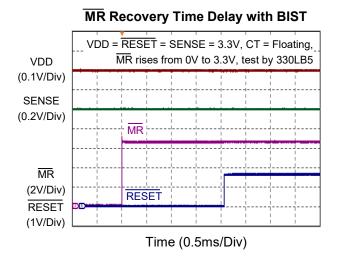

| MR Release Recovery Time Delay                                                         | tD(MR)              |                                        |      | tbist<br>+ td | -1  | ms   |

| BIST Time ( Note 13)                                                                   | tBIST               |                                        | 0.7  | 1             | 1.3 | ms   |

| Startup Time Delay (Note 14)                                                           | tsp                 | Starts up when V <sub>DD</sub> > UVLOR |      | 150           |     | μS   |

- **Note 6.** The voltage on the SENSE pin remains within a  $\pm 1\%$  range.

- **Note 7.** VPOR is the minimum V<sub>DD</sub> voltage level required for a controlled output state.

- Note 8. The RESET/ $\overline{RESET}$  pin is driven low when  $V_{DD}$  falls below UVLO<sub>F</sub>.

- Note 9. V<sub>HYS</sub> is defined with respect to the triggered points of V<sub>TH(OV)</sub> and V<sub>TH(UV)</sub>.

- **Note 10.** 5% overdrive from threshold voltage. Overdrive (%) = |(V<sub>SENSE</sub> V<sub>NOMINAL</sub>)/V<sub>NOMINAL</sub> × 100%| |V<sub>TH(OV or UV)</sub>|, where the V<sub>NOMINAL</sub> is the nominal setting of the sense target.

- Note 11. The RESET/RESET output transitions from V<sub>OH</sub> x 90% to V<sub>OL</sub> for falling time, and from V<sub>OL</sub> to V<sub>OH</sub> x 90% for rising time.

- **Note 12.**  $t_{PD}$  is measured from the triggered point  $V_{TH(OV)}$  or  $V_{TH(UV)}$  until RESET/RESET is asserted.

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

# **RTQ2588-QB**

- Note 13. Built-in self-test is initiated once  $V_{DD}$  rises above  $UVLO_R$  and reaches  $V_{DD(min)}$  or after the  $\overline{MR}$  pin state changes from asserted to de-asserted.

- **Note 14.** During the power-on sequence,  $V_{DD}$  must be at or above  $V_{DD(min)}$  for a duration of  $t_{SD}$  +  $t_{BIST}$  +  $t_{D}$  before the output reaches the correct state.

- **Note 15**. If the  $\overline{MR}$  is driven to a voltage less than  $V_{DD}$ , additional current will flow into  $V_{DD}$  and out of  $\overline{MR}$ .

- **Note 16**. When the CT pin is connected to the VDD pin, a pull-up resistor is required; a  $10k\Omega$  is recommended.

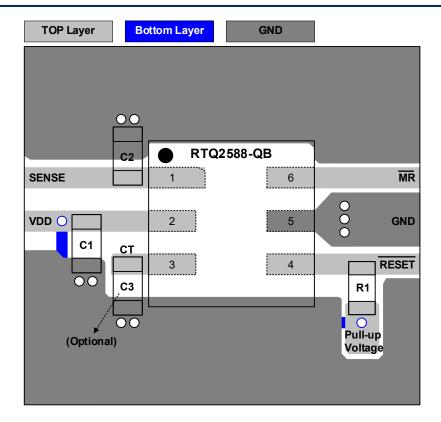

# 14 Typical Application Circuit

**Table 1. Component List for Evaluation Board**

| Reference | Qty | Part Number       | Description   | Package | Manufacturer |

|-----------|-----|-------------------|---------------|---------|--------------|

| C1        | 1   | GCM155C71A105KE38 | 1.0μF/10V/X7S | 0402    | MURATA       |

| C2        | 1   | GCM155R71A104KA01 | 0.1µF/10V/X7R | 0402    | MURATA       |

| R1        | 1   | MR02X1002FAL      | 10kΩ/1%       | 0201    | WALSIN       |

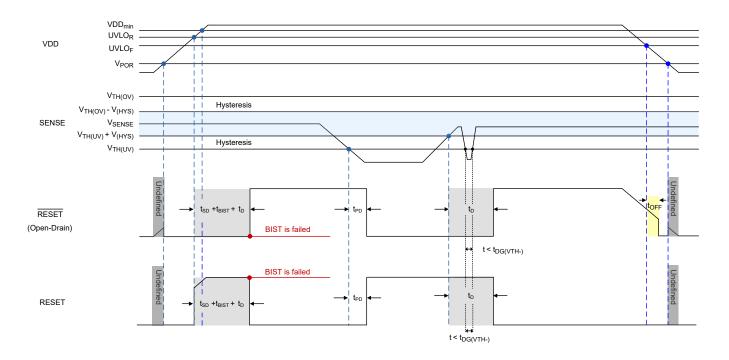

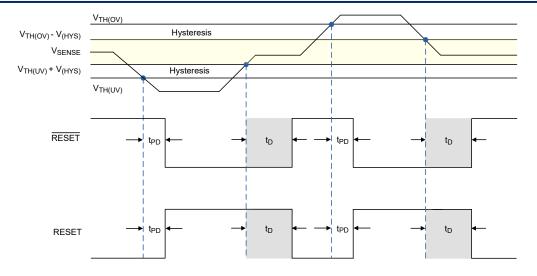

### 15 Timing Diagram

#### Note 17.

- $\bullet$  In open-drain timing diagram, the  $\,\overline{\mbox{RESET}}\,$  pin is connected to  $V_{DD}$  via an external pull-up resistor.

- Advised that the V<sub>DD</sub> falling and rising time are much longer than the propagation time delay (t<sub>PD</sub>) time.

- $\bullet\,$  The typical turn-off time is  $10\mu s$  when  $V_{DD}$  goes below the UVLOF threshold.

### 16 Typical Operating Characteristics

RTQ2588-QB DS-01T02 November 2025

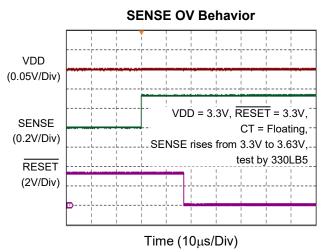

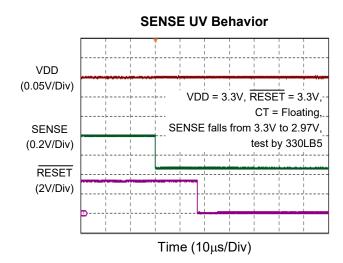

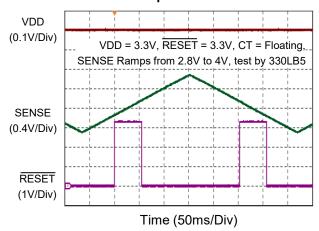

#### **SENSE Ramp OV and UV Behavior**

### 17 Operation

The RTQ2588-QB features an internal window comparator that accurately monitors overvoltage and undervoltage conditions within a maximum tolerance of  $\pm 0.78\%$ . It supports a variety of sensing voltage targets without requiring external voltage divider resistors, offering protection threshold options to facilitate easy integration for system designers.

The device provides four reset recovery time settings: each setting offers a different fixed recovery times depending on whether the CT pin is left floating, or connected to VDD through a resistor, and supports programmable recovery times depending on whether the CT pin is connected to GND through a capacitor.

System designers can choose between two output types: open-drain and push-pull, depending on the application requirements.

For automotive functional safety, the RTQ2588-QB includes a Built-In Self-Test (BIST) function that serves as a safety mechanism to improve the system's latent point fault metrics (LPFM) scores.

#### **17.1 SENSE**

The RTQ2588-QB is equipped with precision-trimmed voltage-divider resistors and a high-accuracy reference voltage, making the internal window comparator ideal for high-precision applications. To enhance noise immunity, despite the inherent hysteresis band of the comparator, it is recommended to place a bypass MLCC capacitor ranging from 10nF to 100nF at the SENSE pin to reduce the impact of transient voltages on the monitored signal.

#### 17.2 Capacitor Time (CT)

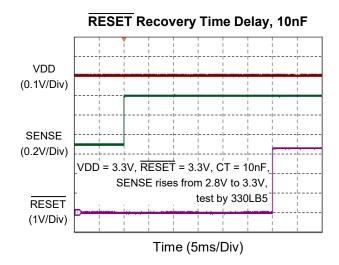

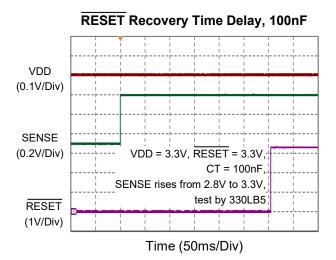

The RTQ2588-QB offers four factory-trimmed settings, allowing system designers to select the appropriate reset recovery time delay for their applications. For added flexibility, the CT pin can be left floating, connected to VDD via a resistor, or grounded through a capacitor, with each configuration yielding a different reset recovery time delay.

The reset recovery time delay is re-evaluated each time the monitored voltage transitions from outside to inside the window (V<sub>TH(UV)</sub> < V<sub>SENSE</sub> / V<sub>NOMINAL</sub> (%) < V<sub>TH(OV)</sub>). This assessment is managed by an internal state machine that determines the setting based on the CT pin configuration.

If the CT pin is required to be pulled up to VDD, a  $10k\Omega$  pull-up resistor is recommended.

#### 17.3 RESET/RESET

The RTQ2588-QB provides two factory-trimmed output type options to suit application needs, allowing selection of the appropriate output asserted behavior for overvoltage (OV) or undervoltage (UV) conditions.

For the open-drain output type, requiring a pull-up resistor to connect to the appropriate voltage rail, with a  $10k\Omega$  resistor being the recommended value. Normally, the output remains high by default and is driven low when a fault is detected or  $\overline{MR}$  is asserted.

Conversely, the push-pull output type eliminates the need for a pull-up resistor and offers two asserted behaviors: active-low and active-high, accommodating different design requirements.

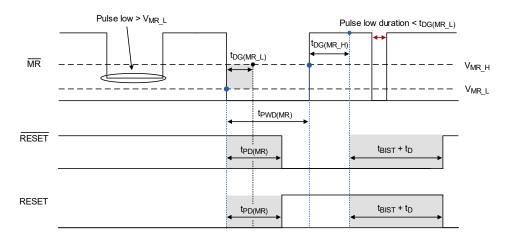

#### 17.4 Manual Reset (MR)

The manual reset (MR) input pin can be utilized by a processor or other logic circuits to initiate a hard reset.

A logic-low control input will assert the reset output; Conversely, a logic-high control input, combined with the monitored voltage on the SENSE pin being within the window (VTH(UV) < VSENSE / VNOMINAL (%) < VTH(OV)), will deassert the reset output after the reset recovery time delay (tD) and built-in self-test (BIST) time (tbist). If the  $\overline{\text{MR}}$  pin is not in use, it can either be left floating or connected to VDD.

- a. The monitored voltage on SENSE is within the window.

- b. Following condition "a",  $\overline{MR}$  must be at or above  $\overline{V_{MR}}_H$  for the time reset counter to be initiated.

- c.  $\overline{\text{MR}}$  is ignored while the reset output is asserted.

### 18 Application Information

(Note 18)

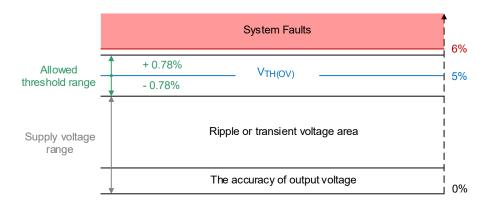

#### 18.1 Voltage Protection Threshold Accuracy

The RTQ2588-QB features high voltage accuracy, making it suitable for loose power supply designs. This flexibility allows system designers to use the smaller passive components (for example, capacitors or inductors) for tight voltage margin applications.

#### 18.2 Reset Recovery Time Delay Determination

The RTQ2588-QB offers factory-set timing options with high-precision reset recovery delay, providing system designers with reliable settings. The recommended settings are shown below.

| Ontion | RESET                                      | Unit |                       |       |

|--------|--------------------------------------------|------|-----------------------|-------|

| Option | CT = Floating CT = $10k\Omega$ to VDD CT = |      | CT = Capacitor        | Oilit |

| A, E   | 50                                         | 200  | N/A                   | μs    |

| B, F   | 1                                          | 20   | Depends on cap. value | ms    |

| C, G   | 5                                          | 100  | Depends on cap. value | ms    |

| D, H   | 10                                         | 200  | Depends on cap. value | ms    |

In addition, the RTQ2588-QB reset recovery time delay can be programed by using the internal current source (ICT) to charge external capacitor, and through the internal comparator to compare and determine. The ideal capacitor value can be calculated using Equation 1 to determine the reset recovery time delay, where the external capacitor is in nanofarad (nF) and to is in millisecond (ms):

$$t_{D(Typ)}$$

(ms) = 1.21 (V) × C (nF) / 0.4 ( $\mu$ A) (1)

When the faults/manual reset conditions are cleared, the internal current source is enabled to charge the external capacitor on the CT pin until Vct\_th = 1.21V (typical) and RESET/RESET is deasserted.

Note that it is suggested to use a X7R, or C0G capacitor and minimize the board parasitic capacitance on the CT pin to achieve precise reset recovery time delay.

| Capacitor on the CT Pin | Reset Recovery Time Delay<br>(Typical) |

|-------------------------|----------------------------------------|

| 660pF                   | 2ms                                    |

| 1nF                     | 3ms                                    |

| 3.3nF                   | 10ms                                   |

| 100nF                   | 302.5ms                                |

| 1μF                     | 3025ms                                 |

The selection of the minimum capacitor value is constrained by the preset time of the floating state in different reset recovery time delay options.

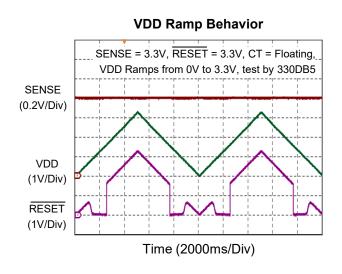

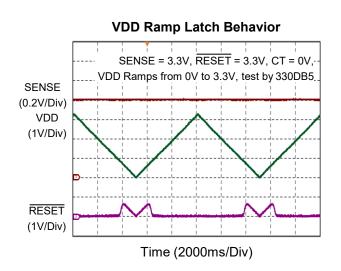

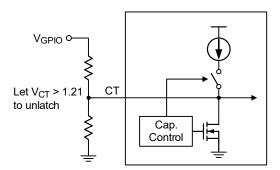

#### 18.3 Latch Mode on the RESET/RESET Pin

The RTQ2588-QB features a latch mode on the RESET/RESET pin when the CT pin is pulled low to ground. In this mode, the RESET/RESET pin remains in an asserted state regardless of VSENSE being within the in-window range, until a voltage exceeding VCT\_TH is applied to the CT pin. This action immediately releases the latch, causing the RESET/RESET pin to go to a deasserted state with no delay. For effective unlatching, apply a voltage greater than 1.21V to the CT pin, using a series voltage-divider resistor to limit the current.

#### 18.4 Functional Safety Support Capable

To enhance the latent point fault metric (LPFM) score of function safety systems, the RTQ2588-QB features the built-in self-test (BIST) function to diagnose the internal OV and UV functions, and ensure they maintain normal functionality. This safety mechanism is enabled and performs a one-time BIST (typical 1ms duration) when VDD rises above UVLOR or when the manual reset ( $\overline{\text{MR}}$ ) is cleared by an external device. If the BIST fails, the RESET/RESET pin will remain in an asserted state.

Furthermore, to improve product reliability, the RTQ2588-QB incorporates a redundant, parallel push-pull structure with multiple sets.

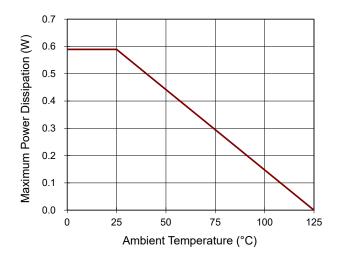

#### 18.5 Thermal Considerations

The junction temperature should never exceed the absolute maximum junction temperature T<sub>J</sub>(MAX), listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula:

$PD(MAX) = (TJ(MAX) - TA) / \theta JA$

RTQ2588-QB DS-01T02 November 2025

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Junction Conditions is  $125^{\circ}$ C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a WDFN-6L 1.5x1.5 (COL) package, the thermal resistance,  $\theta_{JA}$ , is  $169.67^{\circ}$ C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A = 25^{\circ}$ C can be calculated as below:

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (169.67^{\circ}C/W) = 0.59W$  for a WDFN-6L 1.5x1.5 (COL) package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curve in <u>Figure 1</u> allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 1. Derating Curve of Maximum Power Dissipation

#### 18.6 Layout Considerations

To ensure accurate voltage monitoring, adhere to the following PCB layout guidelines:

- Keep the trace from the sensing target as short as possible to minimize the effects of parasitic resistance and inductance.

- Position the capacitors near the VDD, SENSE, and CT pins to enhance noise immunity and achieve precise programmable reset recovery time delays.

- Do not place the RTQ2588-QB above layers with high-speed switching traces; it should be separated by a ground layer.

- Ensure the SENSE trace is as far away from high-speed signal traces as possible to avoid interference.

Figure 2. Layout Guide

Note 18. The information provided in this section is for reference only. The customer is solely responsible for designing, validating, and testing any applications incorporating Richtek's product(s). The customer is also responsible for applicable standards and any safety, security, or other requirements.

RTQ2588-QB\_DS-01T02 November 2025

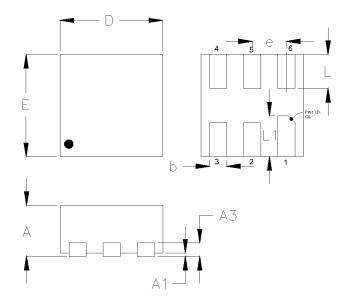

# 19 Outline Dimension

| O mak al | Dimen | sions In Millin | neters | Dimensions In Inches |       |       |  |

|----------|-------|-----------------|--------|----------------------|-------|-------|--|

| Symbol   | Min   | Тур             | Max    | Min                  | Тур   | Max   |  |

| Α        | 0.700 | 0.750           | 0.800  | 0.028                | 0.030 | 0.031 |  |

| A1       | 0.000 | -               | 0.050  | 0.000                | -     | 0.002 |  |

| A3       | 0.175 | 0.203           | 0.250  | 0.007                | 0.008 | 0.010 |  |

| b        | 0.200 | 0.250           | 0.300  | 0.008                | 0.010 | 0.012 |  |

| D        | 1.450 | 1.500           | 1.550  | 0.057                | 0.059 | 0.061 |  |

| E        | 1.450 | 1.500           | 1.550  | 0.057                | 0.059 | 0.061 |  |

| е        |       | 0.500           |        | 0.020                |       |       |  |

| L        | 0.450 | 0.500           | 0.550  | 0.018                | 0.020 | 0.022 |  |

| L1       | 0.550 | 0.600           | 0.650  | 0.022                | 0.024 | 0.026 |  |

W-Type 6L DFN 1.5x1.5 Package (COL)

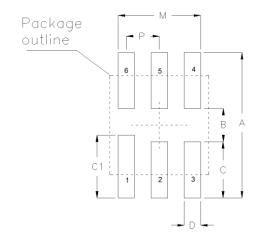

# **20 Footprint Information**

| Dookaga                  | Number of | lumber of Footprint Dimension (mm) |      |      |      |      |      |      |           |

|--------------------------|-----------|------------------------------------|------|------|------|------|------|------|-----------|

| Package                  | Pin       | Р                                  | Α    | В    | С    | C1   | D    | М    | Tolerance |

| V/W/U/XDFN1.5x1.5-6(COL) | 6         | 0.50                               | 2.20 | 0.50 | 0.85 | 0.95 | 0.25 | 1.25 | ±0.05     |

# 21 Packing Information

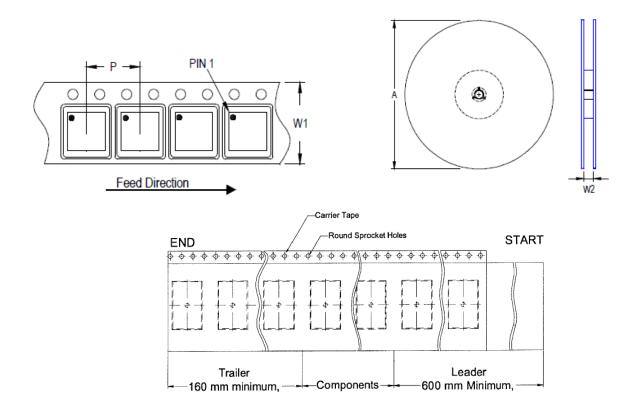

#### 21.1 Tape and Reel Data

| Package Type                 | Tape Size | Pocket Pitch | Reel Si | ze (A) | Units    | Trailer | Leader | Reel Width (W2) |

|------------------------------|-----------|--------------|---------|--------|----------|---------|--------|-----------------|

|                              | (W1) (mm) | (P) (mm)     | (mm)    | (in)   | per Reel | (mm)    | (mm)   | Min/Max (mm)    |

| (V, W)<br>QFN/DFN<br>1.5x1.5 | 8         | 4            | 180     | 7      | 3,000    | 160     | 600    | 8.4/9.9         |

C, D, and K are determined by component size.

The clearance between the components and the cavity is as follows:

- For 8mm carrier tape: 0.5mm maximum

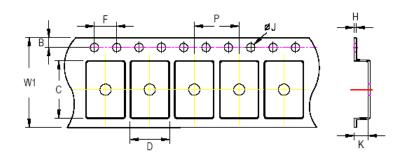

| Tape Size | W1    | F     | )     | Е      | 3      | F     |       | ØJ    |       | K     |       | Н     |

|-----------|-------|-------|-------|--------|--------|-------|-------|-------|-------|-------|-------|-------|

| Tape Size | Max   | Min   | Max   | Min    | Max    | Min   | Max   | Min   | Max   | Min   | Max   | Max   |

| 8mm       | 8.3mm | 3.9mm | 4.1mm | 1.65mm | 1.85mm | 3.9mm | 4.1mm | 1.5mm | 1.6mm | 1.0mm | 1.3mm | 0.6mm |

#### 21.2 Tape and Reel Packing

| Step | Photo/Description                      | Step | Photo/Description            |

|------|----------------------------------------|------|------------------------------|

| 1    | Reel 7"                                | 4    | 3 reels per inner box Box A  |

| 2    | HIC & Desiccant (1 Unit) inside        | 5    | 12 inner boxes per outer box |

| 3    | Caution label is on backside of Al bag | 6    | Outer box Carton A           |

| Container        | Re   | eel   |       | Box   |       | Carton                  |       |           |  |

|------------------|------|-------|-------|-------|-------|-------------------------|-------|-----------|--|

| Package          | Size | Units | Item  | Reels | Units | Item                    | Boxes | Unit      |  |

| (V, W) QFN & DFN | 7"   | 2.000 | Box A | 3     | 9,000 | Carton A                | 12    | 108,000   |  |

| 1.5x1.5          | /    | 3,000 | Box E | 1     | 3,000 | For Combined or Partial |       | ial Reel. |  |

#### 21.3 Packing Material Anti-ESD Property

|   | urface<br>sistance | Aluminum Bag                        | Reel                                | Cover tape                          | Carrier tape                        | Tube                                | Protection Band                     |

|---|--------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| 2 | ᠒/cm²              | 10 <sup>4</sup> to 10 <sup>11</sup> |

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

Copyright © 2025 Richtek Technology Corporation. All rights reserved.

# 22 Datasheet Revision History

| Version | Date       | Description                                                                                                                                                                                                       |

|---------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00      | 2024/5/29  | Title on P1 Ordering Information on P2 Functional Block Diagram on P6 Electrical Characteristics on P8 Note 10 on P9 Typical Operating Characteristics on P14 Operation on P16, 17 Application Information on P19 |

| 01      | 2025/11/21 | Updated <u>Electrical Characteristics</u> and <u>Packing Information</u> .                                                                                                                                        |