## **Audio Amplifier with IV Sense**

### **General Description**

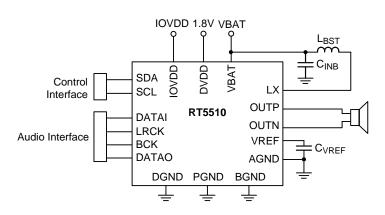

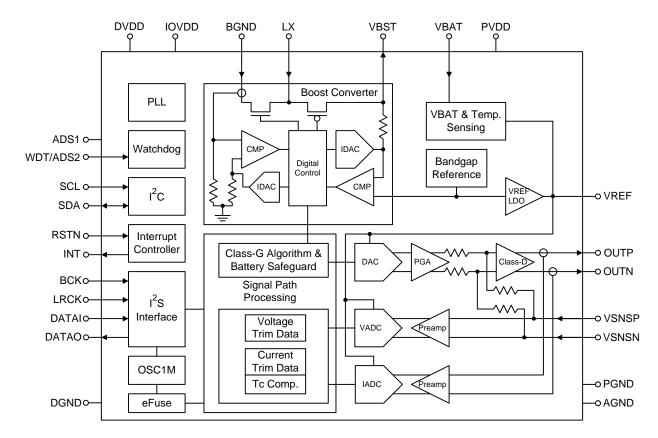

The RT5510 is a boosted BTL class-D amplifier with V/I sensing. A built-in DC-DC step-up converter is used to provide efficient power for class-D amplifier with multi-level class-G operation. The digital audio interface supports I<sup>2</sup>S, left-justified, right-justified, TDM and DSP A/B format for audio in with a data out used for chip information like voltage sense and current sense, which are able to be monitored via DATAO through proper register setting.

### **Ordering Information**

RT5510

Package Type WSC : WL-CSP-30B 2.25x2.60 (BSC)

Note :

Richtek products are :

- ► RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

### **Applications**

- Smart Phone

- Tablet

### Features

- Class-D Speaker AMP

- ▶ 4.8W Output Power @ 9.5V, 8Ω Load, THD < 1%</p>

- ▶ 6.5W Output Power @ 9.5V, 4Ω Load, THD < 1%</p>

- ▶ 0/3/6/9/12/15/18dB Boost Gain

- ▶ 20µV Output Noise

- Add DRE to Reduce Output Noise

- Boost Converter

- Adaptive Boost for Speaker, Boost from Battery Supply Up to Programmed Voltage, Max 9.5V

- ► Accurate Input Current Limit

- Analog Part : Current Sense, Slope Compensation, Feedback ADC

- Alternate Mode Supported

- Digital Part : Voltage Loop and End-Point Prediction in Boost Mode

- Digital

- Digital Audio Interface Support I<sup>2</sup>S, Left-Justified, Right-Justified, TDM and DSPA/B

- Flexible Interrupt Controller

- Clip Control (Battery Safeguard) to Prevent Drawing Larger Current from Battery When Low VBAT

- Watchdog to Monitor Application Process

Status and Shutdown the System

- Volume Control

- RoHS Compliant and Halogen Free

### **Simplified Application Circuit**

### **Marking Information**

5H YM DNN 5H : Product Code YMDNN : Date Code

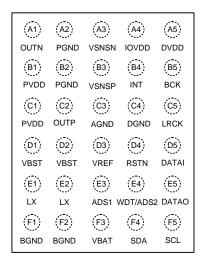

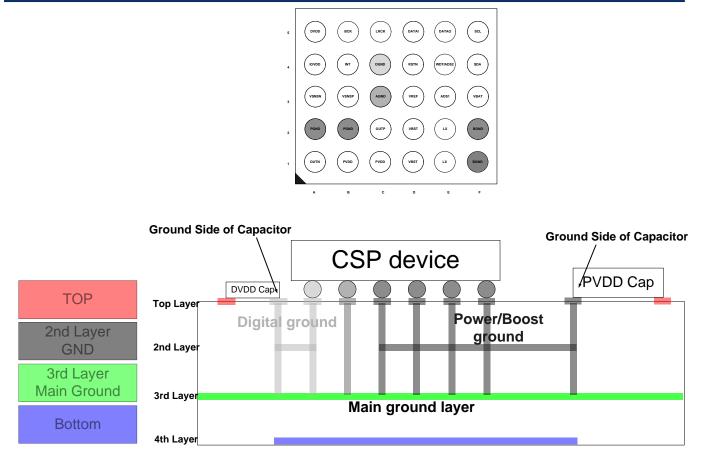

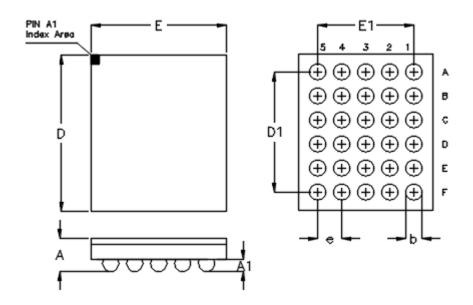

### **Pin Configuration**

(TOP VIEW)

WL-CSP-30B 2.25x2.60 (BSC)

### **Functional Pin Description**

| Pin No. | Pin Name | Туре | Pin Function                                                                                         |  |

|---------|----------|------|------------------------------------------------------------------------------------------------------|--|

| A1      | OUTN     | 0    | Class-D inverting output.                                                                            |  |

| A2, B2  | PGND     | Р    | Power ground.                                                                                        |  |

| A3      | VSNSN    | I    | Voltage sense negative input.                                                                        |  |

| A4      | IOVDD    | Р    | Digital I/O supply voltage. A $0.1\mu F$ external capacitor is required.                             |  |

| A5      | DVDD     | Р    | Digital supply voltage. A 0.1µF external capacitor is required.                                      |  |

| B1, C1  | PVDD     | Р    | Class-D supply voltage. Voltage is provided by VBST pin. A $22\mu F$ external capacitor is required. |  |

| B3      | VSNSP    | I    | Voltage sense positive input.                                                                        |  |

| B4      | INT      | 0    | Interrupt output.                                                                                    |  |

| B5      | BCK      | I    | I <sup>2</sup> S interface bit clock data input.                                                     |  |

| C2      | OUTP     | 0    | Class-D non-inverting output.                                                                        |  |

| C3      | AGND     | G    | Analog ground.                                                                                       |  |

| C4      | DGND     | G    | Digital ground.                                                                                      |  |

| C5      | LRCK     | I    | I <sup>2</sup> S interface word select data input.                                                   |  |

| D1, D2  | VBST     | 0    | Boost converter output voltage.                                                                      |  |

| D3      | VREF     | Р    | Reference voltage output. A $1\mu F$ external capacitor is required.                                 |  |

| D4      | RSTN     | I    | Hardware reset input, high active. Normally keep low level, go high level for hardware reset.        |  |

| D5      | DATAI    | I    | I <sup>2</sup> S interface digital audio data input.                                                 |  |

| E1, E2  | LX       | Р    | Boost converter switch input node.                                                                   |  |

| E3      | ADS1     | I    | Address select input 1.                                                                              |  |

| Pin No. | Pin Name | Туре | Pin Function                                                                                                                                                                                                                 |

|---------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E4      | WDT/ADS2 | I    | Watchdog input/Address select 2. The RT5510 will latch the level of WDT/ADS2 once 768 $\mu$ s after the edge of RSTN pin or analog POR goes from low to high or software reset from high to low for address select function. |

| E5      | DATAO    | 0    | I <sup>2</sup> S interface digital audio data output.                                                                                                                                                                        |

| F1, F2  | BGND     | G    | Boost converter ground.                                                                                                                                                                                                      |

| F3      | VBAT     | Ρ    | Battery supply voltage. Connect 2.7V to 5.5 V battery supply. A $0.1\mu F$ external capacitor is required.                                                                                                                   |

| F4      | SDA      | I/O  | $I^2C$ interface data input, Open drain structure. A 4.7k $\Omega$ external pull-up resistor is required.                                                                                                                    |

| F5      | SCL      | I    | ${\rm I}^2{\rm C}$ interface clock input, Open drain structure. A 4.7k $\Omega$ external pull-up resistor is required.                                                                                                       |

### **Functional Block Diagram**

**RT5510**

### Operation

#### **Class-D Audio Amplifier**

The RT5510 is a 9.5V boosted class-D audio amplifier capable of delivering up to 4.8Wrms output power into an  $8\Omega$  speaker at a supply voltage of 3.6V. The audio amplifier features low noise ( $20\mu$ Vrms). Signal gains are configurable through analog (D\_SPK\_BOOST[2:0] 0 to 18dB, 3dB/step) and digital (VOLUME[7:0] 12 to -115.5dB, -0.5dB/step) circuits.

Over-current protection with threshold of 3A is also implemented in the high efficiency bridge-tied-load (BTL) devices to provide additional protection alongside the current limit of boost converter. The 3-level PWM scheme supports filter less speaker drive.

#### PLL

The on-chip PLL generates the 24.576MHz clock as the internal operating clock source. The PLL uses the BCK of I<sup>2</sup>S interface as the reference clock and the programmability of the PLL allows the support of various sample rate of audio data, like 8k / 11.025k / 12k / 16k / 22.05k / 24k / 32k / 44.1k / 48k / 88.2k / 96kHz. Combining PLL\_N\_I and PLL\_N\_F forms an unsigned number in u13.16 format, which specifies the ratio of 24.576MHz clock over the reference clock, BCK.

PLL\_CLK = BCK × (PLL\_N\_I +

$$\frac{PLL_N_F}{2^{16}}$$

)

BCK  $\xrightarrow{PLL}$  PLL\_CLK = 24.576MHz

#### **Over-Voltage Protection**

The over-voltage (OV) protection detects whether the PVDD voltage exceeds 11.5V to 12.5V. If the OV flag is raised, analog circuits will be shut down. System will check the PVDD voltage and update the status every 200ms.

#### **Over-Current Protection**

The over-current protection can detect the over-current fault on class-D. The fault on the class-D which causes a large current over 3A triggers the OC flag to the digital control system and disables the analog blocks by 200ms. After 200ms cooling time, the OC protection detects the current again to determinate if the OC event is finished.

#### **Under-Voltage Protection**

The under-voltage protection can detect the under-voltage fault on power supply VBAT. The UV flag is triggered when VBAT is lower than UVLO, then digital control system disables the analog blocks by 200ms. After 200ms cooling time, the UV protection detects the voltage again to determinate if the UV event is finished.

#### **Over-Temperature Protection**

The over-temperature protection can detect the over-temperature fault on the chip. The OT protection is triggered when temperature sensed by TEMP sense is higher than 150°C, then the digital control system disables the analog blocks by 200ms. After 200ms cooling time, the OT protection detects the temperature again to determinate if the OT event is finished with the hysteresis threshold 120°C.

#### **VBAT Sense**

The VBAT sense monitors the battery voltage between the range from 2V to 6.375V with 8bit resolution, the output is shown in the register " 0x48 VBAT" with the equation battery voltage (V) = VBAT code (DEC) / 40.

#### Temp. Sensing

Temperature sense monitors the temperature of the chip with the range between  $-40^{\circ}$ C to  $175^{\circ}$ C with 9-bit resolution, the output is shown in the register "VPTAT" with the equation code = temperature (K) = temperature (°C) + 273.

Copyright © 2019 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation

www.richtek.com

DS5510-00

October

2019

| Absolute Maximum Ratings (Note 1)              |                        |

|------------------------------------------------|------------------------|

| • VBST, PVDD                                   | - –0.3 to 13V          |

| OUTP, OUTN, LX, VSNSP, VSNSN                   | - –0.3V to 13V         |

| VBAT, IOVDD                                    | - –0.3V to 6V          |

| DVDD, VREF                                     | - –0.3V to 2.5V        |

| LRCK, BCK, DATAI, DATAO, ADS1, WDT/ADS2        | 0.3V to (IOVDD + 0.3V) |

| SCL, SDA, INT                                  | - –0.3V to 6V          |

| • RSTN                                         | 0.3V to (IOVDD + 0.3V) |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                        |

| WL-CSP-30B 2.25x2.60 (BSC)                     | - 3.44W                |

| Package Thermal Resistance (Note 2)            |                        |

| WL-CSP-30B 2.25x2.60 (BSC), θJA                | - 29°C/W               |

| Lead Temperature (Soldering, 10 sec.)          | - 260°C                |

| Junction Temperature                           | - 150°C                |

| Storage Temperature Range                      | - –65°C to 150°C       |

| ESD Susceptibility (Note 3)                    |                        |

| HBM (Human Body Model)                         | - 2kV                  |

| Recommended Operating Conditions (Note 4)      |                        |

### **Recommended Operating Conditions** (Note 4)

| ٠ | VBAT                       | 2.7V to 5.5V   |

|---|----------------------------|----------------|

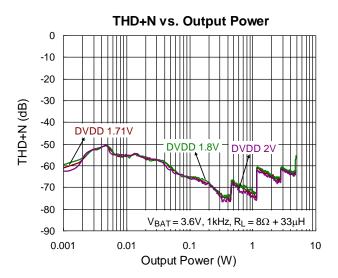

| • | DVDD                       | 1.71V to 2V    |

| • | Ambient Temperature Range  | –40°C to 85°C  |

| • | Junction Temperature Range | –40°C to 125°C |

### **Electrical Characteristics**

(VBAT = 3.6V, Data bit = 24 bits, BCK mode = 64fs, SR = 48kHz, T<sub>A</sub> = 25°C, unless otherwise specified)

| Parameter                  | Symbol               | Test Conditions                                           | Min  | Тур | Max | Unit |

|----------------------------|----------------------|-----------------------------------------------------------|------|-----|-----|------|

| System                     |                      |                                                           |      |     |     |      |

| Digital I/O Voltage        | Iovdd                |                                                           | 1.71 | 1.8 | 3.6 | V    |

| Digital Supply Voltage     | DVDD                 |                                                           | 1.71 | 1.8 | 2   | V    |

| Speaker Amp Supply Voltage | PVDD                 |                                                           | 2.7  | 3.6 | 9.5 | V    |

| Battery Supply Voltage     | VBAT                 |                                                           | 2.7  | 3.6 | 5.5 | V    |

| UVLO for VBAT              | UVLO                 |                                                           | 2.1  | 2.3 | 2.4 | V    |

| Iq, Boost in Battery Mode  | IQ_VBAT              | VBAT and LX                                               | 1    | 3   | 5   | ~^   |

| (Note 5)                   | Iq_dvdd              |                                                           | 9    | 12  | 15  | mA   |

| ISD on VBAT                | I <sub>SD_VBAT</sub> | DVDD = 1.8V                                               | 0    | 0.5 | 1   | μA   |

| ISD on DVDD                | Isd_dvdd             | VBAT = 2.7 to 5.5V, DVDD =<br>1.8V, BCK = LRCK = DAI = 0V | 0    | 4   | 20  | μΑ   |

| ILEAK in Shipping Mode     | I <sub>LEAK</sub>    | VBAT = 4.2V, DVDD = 0V                                    | 0    | 0.5 | 1   | μA   |

## RT5510

| Parameter                                 | Symbol               | Test Conditions                                                   | Min  | Тур  | Max  | Unit |

|-------------------------------------------|----------------------|-------------------------------------------------------------------|------|------|------|------|

| System Efficiency                         | η                    | $P_{O} = 2.5W$ , including DC to DC converter, 100Hz audio signal | 76   | 80   | 84   | %    |

| Over-Temperature Protection               | OTP                  |                                                                   |      | 150  |      | °C   |

| Over-Temperature Protection<br>Hysteresis | ΔΟΤΡ                 |                                                                   |      | 30   |      | °C   |

| Boost                                     |                      |                                                                   |      |      |      |      |

| Boost Output Voltage                      | VBST                 |                                                                   | 2.7  |      | 9.5  | V    |

| VBST Accuracy                             | ΔVBST                |                                                                   | -0.1 |      | 0.1  | V    |

| Class-D                                   |                      |                                                                   |      |      |      |      |

|                                           |                      | 1kHz, PVDD = 3.6V, 8Ω load,<br>1% THD + N                         | 0.6  | 0.65 | 0.7  |      |

| Maximum Output Power                      | Po                   | 1kHz, PVDD = 9.5V, 8Ω load,<br>1% THD + N                         | 4.7  | 4.8  | 4.9  | w    |

|                                           |                      | 1kHz, PVDD = 9.5V, 4Ω load @<br>1% THD + N, VBAT = 4.2V           |      | 6.5  |      |      |

| Output Offset Voltage                     | Offset Voltage Vos   |                                                                   |      | 1    | 3    | mV   |

| Output Noise                              | Vn                   | A-weighting                                                       | 15   | 20   | 25   | μV   |

| Signal to Noise Ratio                     | SNR                  | PVDD = 9.5V, THD + N < 1%,<br>Gain = 15dB, A-weighting            | 107  | 109  | 111  | dB   |

| Dynamic Range                             | DR                   | –60dBFS, 1kHz, A-weighting,<br>Gain = 15dB                        | 107  | 109  | 111  | dB   |

| Total Harmonic Distortion + Noise         | THD+N                | 1kHz, $P_0 = 350$ mW, $8\Omega$ load                              | -90  | -70  | -50  | dB   |

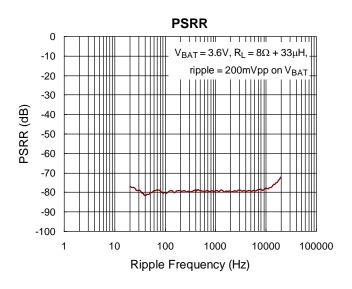

| Power Supply Rejection Ratio              | PSRR <sub>VBAT</sub> | 217Hz, VBAT ripple = 200mVpp                                      | 70   | 80   | 95   | dB   |

| Over-Current Protection of Speaker        | OCP_SPK              | OUTP/OUTN short to PVDD or PGND, or OUTP short to OUTN            | 2.7  | 3    | 3.3  | А    |

| Over-Voltage Protection                   | OVP                  |                                                                   | 11.5 | 12   | 12.5 | V    |

| Current Sense                             |                      |                                                                   |      |      |      |      |

| Resolution                                |                      |                                                                   |      | 16   |      | Bits |

| Accuracy                                  |                      | 1A Ipeak, 25°C, PVDD = 3.6 to<br>9.5V                             | -3   |      | 3    | %    |

| Temperature Variation                     |                      | 1A Ipeak, 25 to +85°C, PVDD = 3.6 to 9.5V                         | -5   |      | 5    | %    |

| Signal to Noise Ratio                     | SNR                  |                                                                   | 65   | 70   | 75   | dB   |

| Total Harmonic Distortion + Noise         | THD+N                | $f = 1 kHz, P_0 = 3W$                                             | -50  | -45  | -40  | dB   |

| Current Sense Full Scale                  |                      | Peak current which will give full scale digital output            | -3   |      | 3    | A    |

| Current Sense Gain Linearity              |                      | f = 1kHz from 50mAp to 1Ap                                        | -1.5 |      | 1.5  | %    |

| Voltage Sense                             |                      |                                                                   |      | •    |      | ·    |

| Resolution                                |                      |                                                                   |      | 16   |      | Bits |

| Accuracy                                  |                      | 8V peak voltage                                                   | -3   |      | 3    | %    |

| Signal to Noise Ratio                     | SNR                  | A-weighting                                                       | 77   | 82   | 87   | dB   |

| Total Harmonic Distortion + Noise         | THD+N                | f = 1kHz, Po = 3W                                                 | -60  | -55  | -50  | dB   |

Copyright © 2019 Richtek Technology Corporation. All rights reserved.

## RT5510

| Parameter                                       | Symbol                    | Test Conditions            | Min           | Тур   | Max           | Unit |

|-------------------------------------------------|---------------------------|----------------------------|---------------|-------|---------------|------|

| Voltage Sense Full scale                        |                           |                            | -12           |       | 12            | V    |

| Voltage Sense Gain linearity                    |                           | f = 1kHz from 0.4Vp to 8Vp |               | 1     |               | %    |

| Battery Sense                                   |                           |                            |               |       |               |      |

| Resolution                                      |                           |                            |               | 8     |               | Bits |

| Voltage Resolution                              |                           |                            | -50           |       | 50            | mV   |

| Full Scale Input Voltage                        |                           |                            |               | 6.375 |               | V    |

| Accuracy                                        |                           | VBAT = 3.6V                | -1            |       | 1             | %    |

| VREF LDO                                        |                           |                            |               |       |               |      |

| Voltage                                         |                           |                            |               | 1.5   |               | V    |

| Output Capacitor                                |                           | Output is stable           | 0.5           | 1     | 2.5           | μF   |

| I <sup>2</sup> C Interface Electrical Character | ristics (Note             | 9 6)                       |               |       |               |      |

| SDA, SCL Input Threshold                        | Vih                       |                            | 0.7 x<br>DVDD |       |               | V    |

| SDA, SCE input miesiloid                        | VIL                       |                            |               |       | 0.3 x<br>DVDD | v    |

| Pull-Down Current                               | I <sub>FO2</sub>          |                            |               | 2     |               | μΑ   |

| Digital Output Low (SDA)                        | V <sub>OL</sub>           | I <sub>PULLUP</sub> = 3mA  |               |       | 0.4           | V    |

| Clock Operating Frequency                       | f <sub>SCL</sub>          |                            |               |       | 400           | kHz  |

| Bus Free Time Between Stop and Start Condition  | tBUF                      |                            | 1.3           |       |               | μs   |

| Hold Time After (Repeated) Start Condition      | thd,sta                   |                            | 0.6           |       |               | μs   |

| Repeated Start Condition Setup Time             | tsu,sta                   |                            | 0.6           |       |               | μs   |

| Stop Condition Time                             | tsu,std                   |                            | 0.6           |       | -             | μS   |

| Data Hold Time                                  | t <sub>HD,DAT</sub> (OUT) |                            | 225           |       |               | ns   |

| Input Data Hold Time                            | thd,dat (in)              |                            | 0             |       | 900           | ns   |

| Data Setup Time                                 | tsu,dat                   |                            | 100           |       | -             | ns   |

| Clock Low Period                                | tLOW                      |                            | 1.3           |       |               | μS   |

| Clock High Period                               | tнigн                     |                            | 0.6           |       |               | μS   |

| Clock Data Falling Time                         | tF                        |                            | 20            |       | 300           | ns   |

| Clock Data Rising Time                          | t <sub>R</sub>            |                            | 20            |       | 300           | ns   |

| Spike Suppression Time                          | t <sub>SP</sub>           |                            |               |       | 50            | ns   |

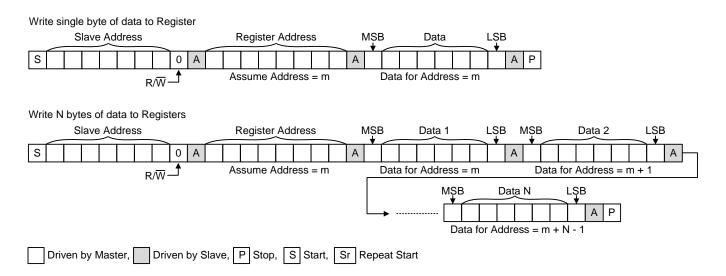

| I <sup>2</sup> S Interface Electrical Character | istics (Note              | : 6)                       |               |       |               |      |

| High-Level Input Voltage                        | VIH                       |                            | 0.7 x<br>DVDD |       |               | V    |

| Low-Level Input Voltage                         | VIL                       |                            |               |       | 0.3 x<br>DVDD | V    |

| Setup Time, LRCK to SCLK<br>Rising Edge         | t <sub>su1</sub>          |                            | 10            |       |               | ns   |

Copyright © 2019 Richtek Technology Corporation. All rights reserved.

## RT5510

## RICHTEK

| Parameter                                | Symbol           | Test Conditions | Min | Тур | Мах | Unit |

|------------------------------------------|------------------|-----------------|-----|-----|-----|------|

| Hold Time, LRCK from SCLK<br>Rising Edge | t <sub>h1</sub>  |                 | 10  |     |     | ns   |

| Setup Time, SDIN to SCLK Rising Edge     | t <sub>su2</sub> |                 | 10  |     |     | ns   |

| Hold Time, SDIN from SCLK<br>Rising Edge | t <sub>h2</sub>  |                 | 10  |     |     | ns   |

| Rise/fall Time for SCLK/LRCLK            | tr               |                 |     |     | 8   | ns   |

**Note 1.** Continuously stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- **Note 5.** Quiescent, or ground current, is the difference between input and output currents. It is defined by  $I_Q = I_{IN} I_{OUT}$  under no load condition ( $I_{OUT} = 0$ mA). The total current drawn from the supply is the sum of the load current plus the ground pin current.

- Note 6. Guaranteed by design.

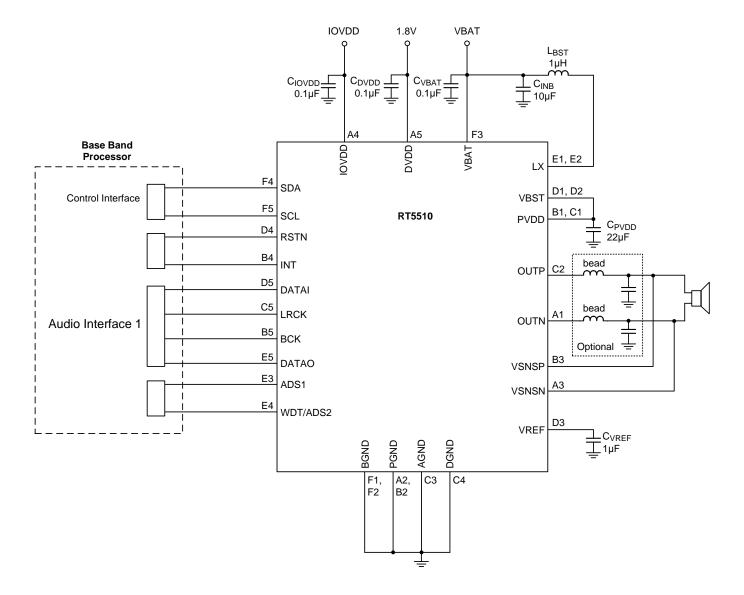

### **Typical Application Circuit**

| Reference         | Part Number        | Description           | Package     | Manufacturer |

|-------------------|--------------------|-----------------------|-------------|--------------|

| CINB              | GRM155R61A106ME11D | 10μF/10V/X5R          | 0402        | muRata       |

| Cpvdd             | GRM219R61C226ME15L | 22µF/16V/X5R          | 0805        | muRata       |

| C <sub>PVDD</sub> | GRM187R61A226ME15D | 22µF/10V/X5R          | 0603        | muRata       |

| L <sub>BST</sub>  | CIGT252010EH1R0MNE | 1μH, 4.7A, 30mΩ, ±20% | 2.5x2x1.2mm | Samsung      |

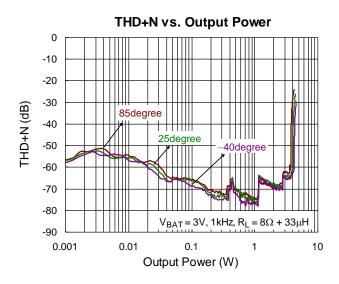

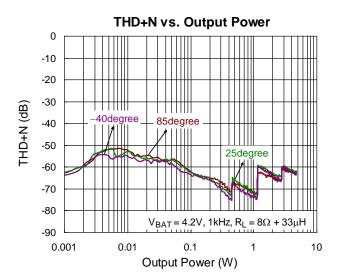

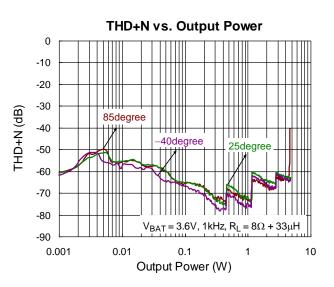

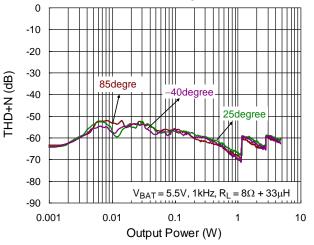

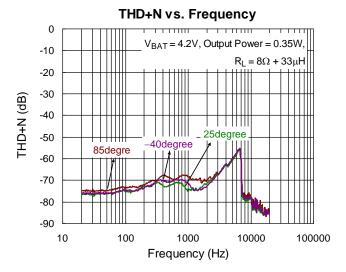

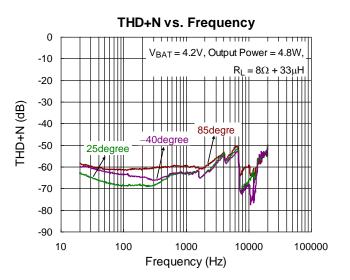

### **Typical Operating Characteristics**

THD+N vs. Output Power

Copyright © 2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation www.richtek.com DS5510-00 October

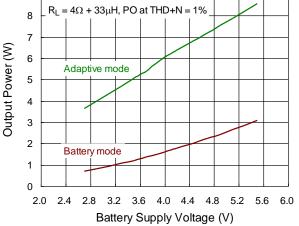

**Output Power vs. Battery Supply Voltage** 7.0  $R_L = 8\Omega + 33\mu H$ , PO at THD+N = 1% 6.3 5.6 Adaptive mode Output Power (W) 4.9 4.2 3.5 2.8 2.1 Battery mode 1.4 0.7 0.0 2.8 3.2 3.6 4.0 4.4 4.8 5.2 5.6 6.0 2.4 2.0 Battery Supply Voltage (V)

Output Power vs. Battery Supply Voltage

Copyright © 2019 Richtek Technology Corporation. All rights reserved.

12

### I<sup>2</sup>C Interface Device Addressing

The RT5510 supports  $I^2C$  control interface. The default device address is accessed via ADS1 pin and WDT/ADS2 pin, see Table 2. Address selection via ADS1 pin and WDT/ADS2 pin with four separate address are supported for stereo mode application. The levels on ADS1 pin and WDT/ADS2 pin determine the values of bits 1 and 2, respectively. Note that the RT5510 always monitors the level of ADS1 to change its  $I^2C$  ID, but the RT5510 will latch the level of WDT/ADS2 once 768µs after the edge of RSTN pin or analog POR goes from low to high or software reset from high to low.

| WDT/ADS2 Pin (V) | ADS1 Pin (V) | Address        | Function (bit 0)    |  |  |  |  |  |

|------------------|--------------|----------------|---------------------|--|--|--|--|--|

| 0                | 0            | 0110100x (34H) | 0 : write, 1 : read |  |  |  |  |  |

| 0                | DVDD         | 0110101x (35H) | 0 : write, 1 : read |  |  |  |  |  |

| DVDD             | 0            | 0110110x (36H) | 0 : write, 1 : read |  |  |  |  |  |

| DVDD             | DVDD         | 0110111x (37H) | 0 : write, 1 : read |  |  |  |  |  |

#### Table 2. Address Selection Via Pins ADS1 and WDT/ADS2

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1 | Bit 0 = LSB |

|-------|-------|-------|-------|-------|----------|-------|-------------|

| 0     | 1     | 1     | 0     | 1     | WDT/ADS2 | ADS1  | Bit 0 = LSB |

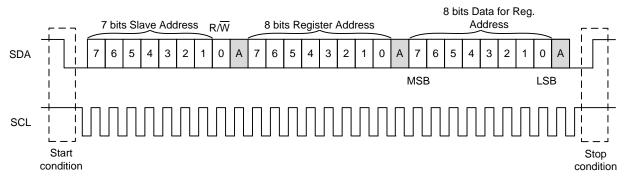

I<sup>2</sup>C bus wiring is very simple. Only two signal lines SDA (Serial Data Line, Data or address signal) and SCL (Serial Clock Line, Clock signal) are used to perform serial communication between integrated circuits in the system.

The corresponding  $I^2C$  communication pins in the RT5510 are SDA and SCL.

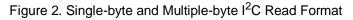

Typical I<sup>2</sup>C format is (Start)-[Slave Address]-[Register Address]-[Data]-(Stop). After writing the slave address first, it needs to be written again to specify the register address for reading and writing. The start and stop conditions of I<sup>2</sup>C are determined by the SDA transition state, while SCL is at logic high level. When SCL is high, the SDA transition from high to low is Start condition. Otherwise, SDA transition from low to high is Stop condition. The I<sup>2</sup>C Bus protocol stipulates that in addition to the start signal and the stop signal, all signal transmissions are fixed in groups of 8 bits (1 Byte), and the MSB is sent first. After each group (8 bits) signal is sent, the sender needs to read an ACK bit (acknowledged) that the receiver responds. ACK low indicates that the data has been received. ACK is an important basis for judging whether the communication between Master/Slave is normal. For valid I<sup>2</sup>C data read or write, SDA must keep the signal stable and can't change state when SCL is high in order to correctly read (latch) the data. SDA only allows transitions when SCL is low level.

The serial interface also supports single-byte and multiple-byte read/write function. Please refer to the next paragraph for the RT5510 Read / Write function description.

Figure 1. Typical I<sup>2</sup>C Format

#### **Read and Write Function**

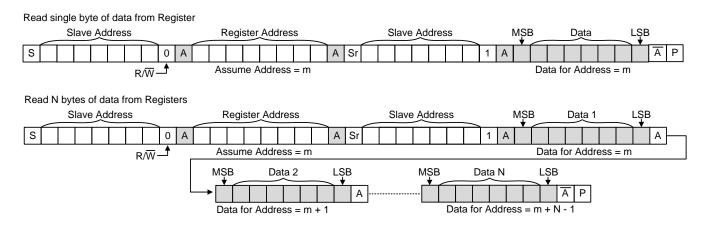

The RT5510 single-byte data-read function format is shown in Figure 2.

Data transfer is initiated when the master device transmits a start condition: SDA is pulled low while SCL stays high, followed by the slave address. The data is sampled when SCL rises for the first bit. The read/write bit is set to 0 to declare the RT5510 address byte to be read. After slave device address and the read/write bit, the RT5510 device responds an acknowledge bit. In second step, the master device sends the RT5510 internal memory address to be read and the RT5510 responds with an acknowledge bit. Then the master device sends start condition again followed by setting the RT5510 device address and read/write bit to 1, and the RT5510 device responds an acknowledge bit. (Setting the read/write bit to 1 represents read internal memory address data.)

The RT5510 sends out data from the register to read. After receiving register data, the master device replies no-acknowledge bit (SDA go high) to indicate that it has not continued to read the data. Then master device sends stop condition (when SDA is pulled high while SCL is high) to complete the single-byte data reading function.

About read multiple data byte, the format is the same as reading a single data byte, and the only difference is the data byte amount sent form slave device. The master device replies with an acknowledge bit after receiving each data byte. After the RT5510 sends the last data byte, the master device replies no-acknowledge bit and transmits a stop condition.

## RT5510

The RT5510 single-byte data-write function format is shown in Figure 3.

Data transfer is initiated when the master device transmit a start condition: SDA is pulled low while SCL stays high, followed by the slave address. The data is sampled when SCL rises for the first bit. The read/write bit is set to 0 to declare the RT5510 address byte to be write. After slave device address and the read/write bit, the RT5510 device responds an acknowledge bit. In second step, the master device sends the RT5510 internal memory address to be written and the RT5510 responds with an acknowledge bit. Then master device sends out data to write in RT5510 internal memory address. After receiving register data, the RT5510 replies an acknowledge bit to indicate that the data is received. Then master device sends stop condition (when SDA is pulled high while SCL is high) to complete the single-byte data write function.

About write multiple data byte, the format is the same as write a single data byte, and the only difference is the data byte amount sent form master device. The slave device replies with an acknowledge bit after receiving each data byte. After the RT5510 receives the last data byte, the RT5510 replies an acknowledge bit and master device transmits a stop condition.

Figure 3. Single-byte and Multiple-byte I<sup>2</sup>C Format

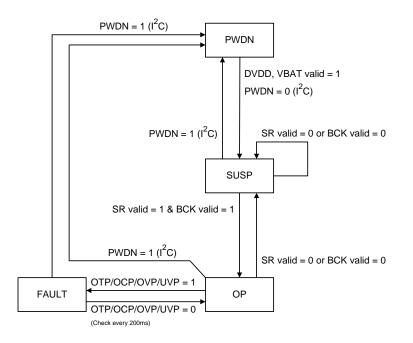

### I<sup>2</sup>C Waveform Information

Figure 4. Timing Diagram of I<sup>2</sup>C Interface

Figure 5. Timing Diagram of Slave Mode I<sup>2</sup>S Interface

### **Operation Mode Modes**

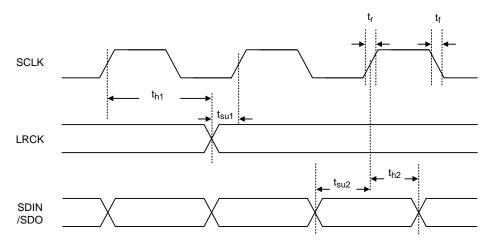

The RT5510 can operate in four different modes which are power-down/suspend/operating/fault. Internal functional block operational status in different modes is depicted in Figure 6.

| Mode<br>Blk      | PWDN     | SUSP     | OP | FAULT    |

|------------------|----------|----------|----|----------|

| PLL              | $\times$ | 0        | 0  | 0        |

| I <sup>2</sup> C | 0        | 0        | 0  | 0        |

| I <sup>2</sup> S | $\times$ | $\times$ | 0  | 0        |

| AMP              | Х        | $\times$ | 0  | $\times$ |

○ : Normal operation

X : Power down

Figure 6. Operation Mode

| Mode       | Condition                              | Description                                                                                                                                                                                                                                                                                 |

|------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-down | PWDN = 1                               | <ol> <li>When PWDN is set to 1, chip will enter power-down mode.</li> <li>Power consumption is minimum and PWM outputs are floating.</li> <li>I<sup>2</sup>C bus remains awake.</li> <li>I<sup>2</sup>S path is disable.</li> </ol>                                                         |

| Suspend    | BCK/SR invalid                         | <ol> <li>Chip will enter suspend mode.</li> <li>Most of the data path are off, and PWM outputs are floating.</li> <li>I<sup>2</sup>C bus remains awake.</li> <li>PLL keeps in free-run mode and CK1M is used to monitor BCK/SR on I<sup>2</sup>S bus to see if they are correct.</li> </ol> |

| Operating  | BCK & SR valid<br>PWDN = 0<br>AMPE = 1 | 1. If set PWDN/AMPE at register 0x03 as condition, chip will enter operating mode when BCK and sampling rate are valid.                                                                                                                                                                     |

| Fault      | OV/OT/OC/UV = 1                        | <ol> <li>Chip enters fault mode when an error event of physical protection<br/>mechanisms occurs (OCP/OVP/UVP/OTP).</li> <li>The boost and AMP are OFF.</li> <li>The system exits from Fault mode after the protection event<br/>released for a checking cycle of about 200ms.</li> </ol>   |

#### **Mode Transition**

The state machine of mode transition is shown in Figure 7. After power on, the control bit will always be reset to PWDN mode.

Figure 7. Mode Transition

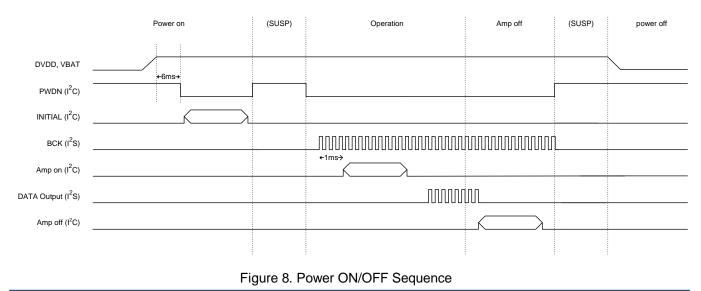

#### **Power ON/OFF Sequence**

The power on sequence is shown in Figure 8. After power is valid, two groups of control signals should be set.

I<sup>2</sup>C : PWDN and AMPE should be programmed. These two bits can be programmed by single command since they are at the same byte address.

I<sup>2</sup>S : BCK should be valid on the specified interface.

If the PWDN is set to 0 before the BCK is valid, it will go to SUSP mode automatically. The output of amplifier will be valid after entering OP mode Signal ramp up will always be implemented when the mode transits from PWDN or SUSP mode to OP mode.

#### Copyright © 2019 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation DS5510-00 October 2019

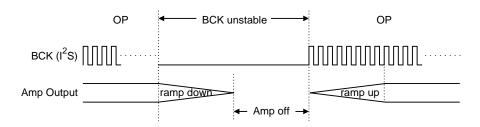

#### I<sup>2</sup>S Mode Change without PWDN

When I<sup>2</sup>S mode change, like BCK and LRCK frequency relationship, the chip will not be shut down. If the clock source from I<sup>2</sup>S changes, I<sup>2</sup>S invalid is detected. In this case, soft muting is implemented before entering Amp off situation. In the opposite situation, if the clock source from I<sup>2</sup>S is detected valid again, signal ramp up is implemented at the start after it enters the operating mode.

The above procedure is shown in Figure 9 and ramp is setting by register 0x 28 bit [2:0].

Figure 9. I<sup>2</sup>S Mode Change without PWDN

| Register | Bits | Bits Name | Description                                                                                                                                                                                                                                                                                                           |

|----------|------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x28     | 2:0  | VOLCTRL   | Ramp control when new volume setting is<br>different from old setting :<br>000 : No ramp up/down (default)<br>001 : 0.5db per sample<br>010 : 0.5db per 2 samples<br>011 : 0.5dB per 4 samples<br>100 : 0.5dB per 8 samples<br>101 : 0.5dB per 16 samples<br>110 : 0.5dB per 32 samples<br>111 : 0.5dB per 64 samples |

#### Table 3. Ramp Control Setting

Copyright © 2019 Richtek Technology Corporation. All rights reserved. www.richtek.com

### Data (I<sup>2</sup>S) Interface

#### Data Format

The  $\mathsf{I}^2\mathsf{S}$  formats supported by the RT5510 are listed below :

| Interface                 | Data Format | BCK Frequency |

|---------------------------|-------------|---------------|

| I <sup>2</sup> S Standard | up to 16bit | 32fs          |

| I <sup>2</sup> S Standard | up to 24bit | 48fs          |

| I <sup>2</sup> S Standard | up to 24bit | 64fs          |

| Left-justified            | up to 16bit | 32fs          |

| Left-justified            | up to 24bit | 48fs          |

| Left-justified            | up to 24bit | 64fs          |

| Right-justified (16-bit)  | 16bit       | 32fs          |

| Right-justified (16-bit)  | 16bit       | 48fs          |

| Right-justified (16-bit)  | 16bit       | 64fs          |

| Right-justified (18-bit)  | 18bit       | 48fs          |

| Right-justified (18-bit)  | 18bit       | 64fs          |

| Right-justified (20-bit)  | 20bit       | 48fs          |

| Right-justified (20-bit)  | 20bit       | 64fs          |

| Right-justified (24-bit)  | 24bit       | 48fs          |

| Right-justified (24-bit)  | 24bit       | 64fs          |

| TDM 8-slot                | 64bit       | 64fs          |

| TDM 16-slot               | 128bit      | 128fs         |

| TDM 32-slot               | 256bit      | 256fs         |

fs : 8kHz, 11.025kHz, 12kHz, 16kHz, 22.05kHz, 24kHz, 32kHz, 44.1kHz, 48kHz, 88.2kHz, 96kHz

#### I<sup>2</sup>S Sampling Rate

I<sup>2</sup>S can support sampling rate of 8kHz, 11.025kHz, 12kHz, 16kHz, 22.05kHz, 24kHz, 32kHz, 44.1kHz, 48kHz, 88.2kHz and 96kHz.

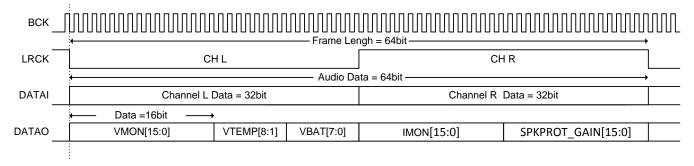

#### **Output Path**

DATAO uses BCK as the reference clock to transmit selected data. The LRCK is treated as channel select for I<sup>2</sup>S mode and frame synchronizer in TDM mode.

The Digital Audio interface supports  $I^2S$  and TDM formats at various sample rates from 8kHz to 96kHz. The interface is compliant with all  $I^2S$  interface configurations and supports a wide range of TDM interface configurations (up to 16-channel at fs = 48kHz). The LSB and MSB must be supported. The signal name is defined as :

- 1. IMON : The current sense signal.

- 2. VMON : The voltage sense signal.

- 3. VBAT : The voltage sense for battery.

- 4. VTEMP : The temperature sense of chip.

Copyright © 2019 Richtek Technology Corporation. All rights reserved.

**RT5510**

5. SPKPROT\_GAIN : The gain of safeguard for speaker protection.

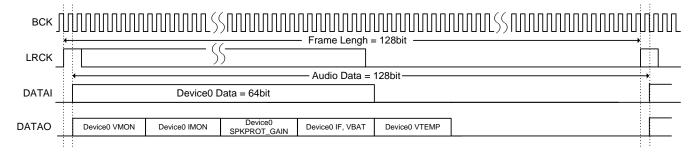

When only one smart PA is connected, I<sup>2</sup>S bus is recommended. At this situation, signal sequence should be VMON, VTEMP, VBAT, IMON and SPKPROT\_GAIN. The SDI signal is only 16bit available for each channel.

The sequence is shown as below :

Figure 10. Only One Smart PA I<sup>2</sup>S Left-Justified Format

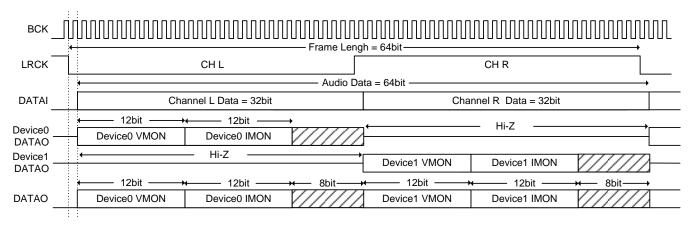

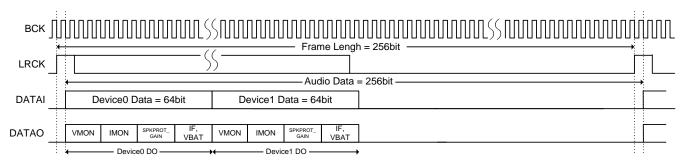

When two smart PA is connected and the I<sup>2</sup>S is used, the VTEMP, VBAT and SPKPROT\_GAIN signal must be disabled. The SDI signal is only 16bit available for each channel.

The sequence is shown as below :

Figure 11. Two Smart PA I<sup>2</sup>S Standard Format

#### TX Data Structuring in I<sup>2</sup>S Mode

| Table 5. TX | Data | Structuring | in I <sup>2</sup> S Mode |

|-------------|------|-------------|--------------------------|

|-------------|------|-------------|--------------------------|

| I <sup>2</sup> SDOLS | I <sup>2</sup> SDOLS Left Channe |                            |           |            |            | Right Channel |          |

|----------------------|----------------------------------|----------------------------|-----------|------------|------------|---------------|----------|

| I <sup>2</sup> SDORS | bit 0-7 bit 8-15                 |                            | bit 16-23 | bit 24-31  | bit 0-15   | bit           | 16-31    |

| 000                  | VMON[15:0] VTEMP[8:1]            |                            | VBAT[7:0] | IMON[15:0] | SPKPRO     | T_GAIN[15:0]  |          |

| 001                  | DAC_BIQ[23:0]                    |                            |           | 8'h0       | {DC_C      | UT_DATA[25:0  | ], 8'h0} |

| 010                  | Hi-Z[31:0]                       |                            |           |            | VMON[15:4] | IMON[15:4]    | 8'h00    |

| 011                  | VMON[                            | VMON[15:4] IMON[15:4] 8'h0 |           |            |            | Hi-Z[31:0]    |          |

RICHTEK is a registered trademark of Richtek Technology Corporation Copyright © 2019 Richtek Technology Corporation. All rights reserved. www.richtek.com DS5510-00

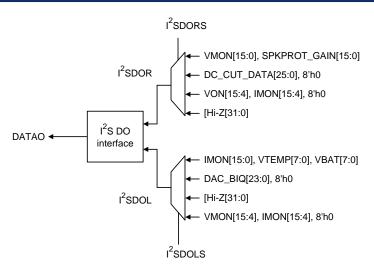

Figure 12. I<sup>2</sup>S Output Mux

When two smart PA is connected and TDM mode is used. At this mode, the frame length should be set to 128bit. The SDI signal is only 16bit available for each channel. The minimum LRCK length is 2 BCK length.

The sequence is shown as below :

Figure 13. One Smart PA TDM Standard Format

The TDM\_TX\_LOC register indicates the starting slot to put the data stream on SDOUT pin and the TDM\_TX\_LEN whose unit is byte (slot) determines how many bytes will be transmitted. Please refer to the TX Data Structuring in I<sup>2</sup>S Mode section.

#### TX Data Structuring in TDM Mode

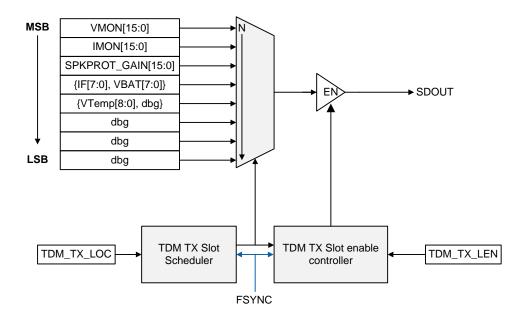

The RT5510 can transmit {VMON[15:0], IMON[15:0], SPKPROT\_GAIN[15:0], IF[7:0], VBAT[7:0], VTemp[8:0], dbg[54:0]} to I<sup>2</sup>S SDOUT in TDM mode. The TDM\_TX\_LOC register indicates the starting slot to put the data stream on SDOUT pin. The sequence of data stream in TDM mode is {VMON[15:0], IMON[15:0], SPKPROT\_GAIN[15:0], IF[7:0], VBAT[7:0], VTemp[8:0], dbg[54:0]} and MSB-first. The TDM\_TX\_LEN whose unit is byte (slot) determines how many bytes will be transmitted, from MSB to the (TDM\_TX\_LEN)th slot. The rest of slots outside of the transmitted data stream shall be keep Hi-Z.

- \* IF[7:0] is the register 0x05 interrupt flag.

- \* dbg is only for testing.

Figure 15. TX Data Structuring in TDM Mode

#### **RX Data in TDM Mode**

The data in the TDM stream that is allocated for assignment to the internal data registers is extracted using the TDM\_RX\_LOC and TDM\_RX\_LEN controls. Data is extracted MSB-first, starting at the TDM\_RX\_LOC location and placing it into its respective internal data register. This process continues until TDM\_RX\_LEN bits are extracted from the TDM stream or another data extraction begins.

Figure 16. RX Data Structuring in TDM Mode

### **Application Information**

#### Watchdog

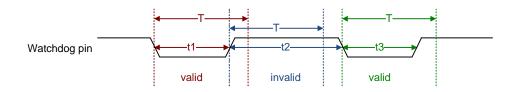

When enable, the watchdog block monitors the edge-to-edge period of the watchdog input signal. If the period between edges is greater than the watchdog timer setting, the watchdog input signal is invalid. It means the protection algorithm is no longer function normally. The boost and speaker amplifier should be automatically disable to prevent damage. When the period between edges of watchdog input signal becomes less than the timer setting, the boost and speaker amplifier will be automatically enable. Please refer to Table 6.

| Name         | Description                                                                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| WD_RESP = 00 | The Amp neither mutes nor shut down when the watchdog is triggered.<br>The boost converter's output voltage is not affected.                           |

| WD_RESP = 01 | The Amp shuts down immediately and the output transition is Hi-Z.<br>The boost converter ramps down to VBAT then enters bypass mode.                   |

| WD_RESP = 10 | The Amp mutes according to the configuration of VOLCTRL, instant mute or soft mute.<br>The boost converter ramps down to VBAT then enters bypass mode. |

| WD_RESP = 11 | Signal in is multiplied by WD_RP when watchdog timeout is happened, instead of R_VOLUME.                                                               |

| Table 6. Amp | Behavior | Configuration | at Watchdog | Timeout |

|--------------|----------|---------------|-------------|---------|

|--------------|----------|---------------|-------------|---------|

Figure 17. Watchdog Timeout Edge Rate Configuration

In the Figure 17, the period t1 between edges is less the timer setting T. The watchdog input signal is valid, so the chip keeps functioning normally. However, in the next period, t2 is larger than T. The watchdog input signal becomes invalid and the boost and speak amplifier are turned off. In the following period, t3 turns to be less than T. Then, the boost and speaker amplifier are turned on again.

#### Boost Mode and Signal Tracking Behavior

The RT5510 boost converter has three modes of operation : battery mode, fixed mode and adaptive mode. The operating mode is usually set to adaptive mode for optimum efficiency. Please refer to below table to set the operating mode :

| Register | Bits | Bits Name | Description                                                                          |

|----------|------|-----------|--------------------------------------------------------------------------------------|

| 0x40     | 1:0  | BST mode  | 00 : Disable (default)<br>01 : Battery mode<br>10 : Fixed mode<br>11 : Adaptive mode |

#### Table 7. Boost Mode Selection

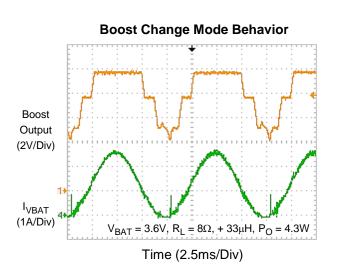

According to the I<sup>2</sup>S input signal change, the RT5510 boost class-G algorithm can determine the voltage required by the speaker output signal to achieve the best efficiency.

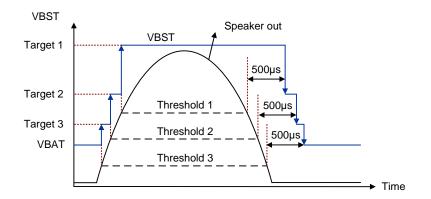

The boost algorithm calculates the voltage of the speaker output signal and compares it with the threshold voltage of the boost converter change mode to determine whether the boost converter output voltage needs to be changed. The boost converter has up to three output voltage configurations that can be set by the user.

When the boost converter is configured in adaptive mode, the speaker output signal is lower than threshold 3 voltage. The boost converter is bypassed and supplied directly to the load by the battery. When the speaker output signal is higher than threshold 3 voltage, boost converter enable and the boost output is set to target 3 voltage. This is for the speaker output signal to have a margin and avoid the phenomenon of clipping. In the same way, when the speaker output signal is higher than threshold 2 voltage, boost converter enables and the boost output is set to target 3 voltage to target 2 voltage. The boost converter has a maximum configurable voltage of 9.5V.

When estimating the voltage drop of the output signal, the Boost algorithm is compared to the threshold voltage to determine whether to change the output voltage of the boost converter.

When the Boost algorithm determines that the speaker output signal is lower than the threshold 1 voltage, the boost converter output voltage has a hold time of  $500\mu$ s to maintain the original output voltage to ensure that the signal becomes larger again. After the hold time, the boost converter reduces the output voltage to the target 2 voltage. In the same way, the speaker output signal is below the threshold 3 voltage. After the hold time, the boost converter reduces the output voltage and is configured to bypass, supplying the load energy directly from the battery.

Figure 18. Boost Behavior

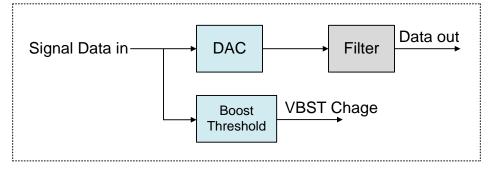

The RT5510  $I^2S$  input signal is converted and processed by the DAC to a speaker output with a delay time of approximately 430µs. The boost algorithm calculates the voltage of the speaker output signal from  $I^2S$  to directly control the boost converter output voltage. This means that the boost output voltage is 430µs faster than the speaker output signal. This ensures that the speaker output signal gets enough voltage level from boost converter.

Figure 19. DAC and Processing Time

Boost output voltage and change mode threshold register are shown in below table. BST\_TH indicates the threshold at which the boost converter changes the output voltage, and BST\_THT indicates the target voltage to be outputted by the boost converter.

| Register | Bits | Bits Name | Description                                                                                                                                                                                                         |

|----------|------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.44     | 11:6 | BST_THT1  | VBST target in fixed mode or highest<br>VBST target in adaptive mode<br>000000 : Disabled<br>000001 to 100001 : 2.9 + BST_THT1 x 0.2V<br>e.g. 000001 : 3.1V, 100001 : 9.5V (default)<br>100010 to 111111 : Reserved |

| 0x41     | 5:0  | BST_TH1   | Boost threshold for BST_THT1<br>000000 : Disabled<br>000001 to 100001 : 1.3+ BST_TH1 x 0.2V<br>e.g. 000001 : 1.5V, 100001 : 7.9V<br>011011 : 6.7V (default)<br>100010 to 111111 : Reserved                          |

|          | 11:6 | BST_THT2  | Middle VBST target in adaptive mode<br>000000 : Disabled<br>000001 to 100001 : 2.9 + BST_THT2 x 0.2V<br>e.g. 000001 : 3.1V, 100001 : 9.5V 010111 : 7.5V<br>(default)<br>100010 to 111111 : Reserved                 |

| 0x42     | 5:0  | BST_TH2   | Boost threshold for BST_THT2<br>000000 : Disabled<br>000001 to 100001 : 1.3+ BST_TH2 x 0.2V<br>e.g. 000001 : 1.5V, 100001 : 7.9V<br>001111 : 4.3V (default)<br>100010 to 111111 : Reserved                          |

Table 8. Boost Output Voltage and Change Mode Threshold

| Register | Bits | Bits Name | Description                                                                                                                                                                                         |

|----------|------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x43     | 11:6 | BST_THT3  | Lowest VBST target in adaptive mode<br>000000 : Disabled<br>000001 to 100001 : 2.9 + BST_THT3 x 0.2V<br>e.g. 000001 : 3.1V, 100001 : 9.5V 001011 : 5.1V<br>(default)<br>100010 to 111111 : Reserved |

|          | 5:0  | BST_TH3   | Boost threshold for BST_THT3<br>000000 : Disabled<br>000001 to 100001 : 1.3+ BST_TH3 x 0.2V<br>e.g. 000001 : 1.5V, 100001 : 7.9V<br>000111 : 2.7V (default)<br>100010 to 111111 : Reserved          |

#### **Boost Current Limit**

The RT5510 boost converter has a configurable current limit function. The default current limit is 4A. This setting can meet the application of  $R_L = 8\Omega$  and output 4.8W. This limit value can be set lower according to the selected inductor. Please refer to Table 9 to set the required limit value. If the CC\_MAX set value is small, the output power will be limited. The CC\_MAX value from 0000000 to 0110100 and 1111110 to 1111111 are not allowed for use.

| Register | Bits | Bits Name | Description                                                                                                                  |  |

|----------|------|-----------|------------------------------------------------------------------------------------------------------------------------------|--|

| 0x45     | 6:0  | CC_MAX    | 0110101 : 2A<br>1000011 : 2.5A<br>1010001 : 3A<br>1011111 : 3.5A<br>1100111 : 4A (default)<br>1101111 : 4.5A<br>1111101 : 5A |  |

#### Table 9. Boost Current Limitation

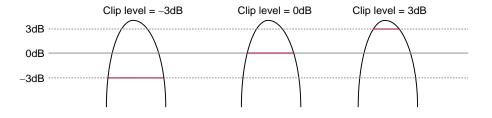

#### **Clip Control**

When the battery voltage is low, playing music causes an instantaneous voltage drop of the battery voltage, which may cause the system to malfunction or restart.

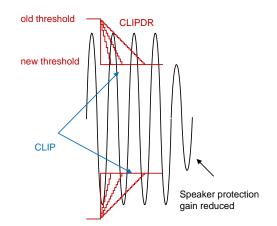

To avoid similar issue, the RT5510 has built-in battery sense and safeguard features. By detecting the battery voltage, the safeguard function is activated when VBAT is low. The RT5510 class-D output voltage upper limit is controlled according to the set clip slope. When the output voltage is lower than the upper limit of clip slop, the class-D output voltage will not be attenuated. When the class-D output voltage exceeds the upper limit of clip slop, the safeguard will start to attenuate the gain and cause the class-D output voltage to drop to the upper limit of the clip slop set value. In the working range of the safeguard function, the upper limit of the class-D output voltage will decay. Since the output voltage is lower, the current consumption is reduced, the battery voltage doesn't have excessive voltage drop when playing music.

To enable the safeguard function on the RT5510, it can be set by the register 0x30 bit 0 setting1 (Enable clip means safeguard function enable). If register 0x30 bit 0 setting is 0, the RT5510 does not execute safeguard, then the excessive output signal will be clipped according to the set clip control parameter.

| Table To. Saleguard Function Mode Selection |      |           |                                          |  |  |  |

|---------------------------------------------|------|-----------|------------------------------------------|--|--|--|

| Register                                    | Bits | Bits Name | Description                              |  |  |  |

| 0x30                                        | 0    | CLPE      | 0 : Disable<br>1 : Enable clip (default) |  |  |  |

Table 10. Safeguard Function Mode Selection

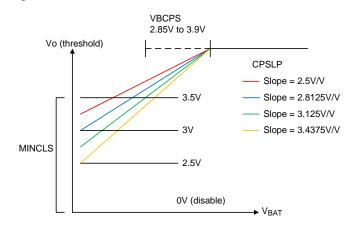

The safeguard is executed according to the parameter of the clip control. Clip control related parameters are VBCPS (Battery Clip Threshold), CPSLP (Clip Slope), MINCLS (Minimum Battery Clip Threshold, VOMIN).

In addition to the above parameters, the user can configure battery voltage recovery hysteresis, rate of VO threshold recovery when VBAT returns and rate of VO threshold drops when VBAT is low, making the operation more flexible. The clip control is shown in Figure 20.

Figure 20. Clip Control

The slope of clip threshold (Vo/VBAT) can be set by CPSLP from 2.5V/V to 3.4375V/V. A Vo stop point (0, 2.5V, 3V or 3.5V) for clip threshold can be set via MINCLS. The output voltage drop will stops at this point. The clip threshold is calculated through the following equation :

ClipThres = SIGMAX - (VBCPS - VBAT) x CPSLP for clip threshold  $\geq$  MINCLS

ClipThres = MINCLS for clip threshold ≤ MINCLS

The detail function is shown below, the dropping rate of threshold can be set via CLIPDR register.

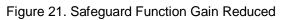

If battery voltage returns to a hysteresis level, ClipThres will increase by a rate of CLIPRR to a certain level which is defined by VBCPS, CPSLP and VBAT. The battery voltage hysteresis can be set via BVHYS register.

Figure 22. Clip Threshold Depend on VBAT

#### Hard Clipping

When Hard clip is enabled (Register 0x24 bit 8), if the digital signal is larger than HARD\_CLIP\_TH, the signal will be clamped to HARD\_CLIP\_TH.

| Register | Bits | Bits Name    | Description                                                                                                                                |  |  |

|----------|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          | 8    | HARD_CLIP_EN | 0 : Disable hard clipping<br>1 : Enable hard clipping (default)                                                                            |  |  |

| 0x24     | 7:0  | HARD_CLIP_TH | Hard clip threshold if HARD_CLIP_EN = 1<br>downward, 12 to -115.5dB in -0.5dB<br>step, (default 00000000 = 12dB)<br>e.g. 00000001 = 11.5dB |  |  |

#### Table 11. Hard Clipping

Figure 23. Signal Hard Clipping

#### DRE

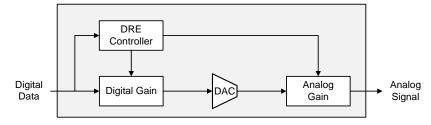

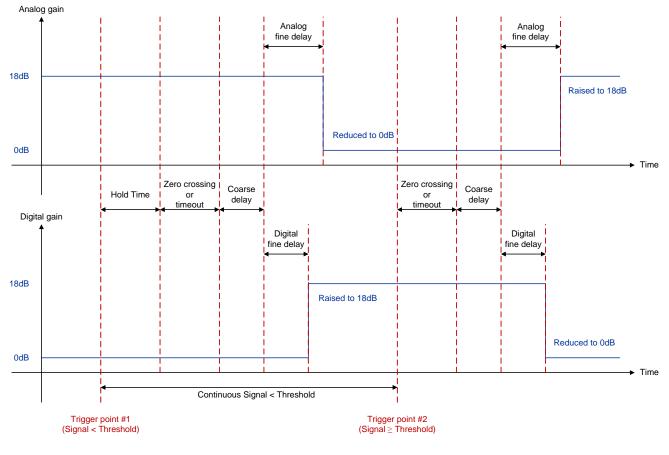

In the signal path, the noise floor of SPK output is related to the analog gain. If decreasing the analog gain, the noise floor decreases, and vice versa. However, increasing the digital gain will not affect the noise floor. To help eliminating unwanted low level noise caused by analog circuit when incoming signal is below a certain threshold, a DRE technique is used. The DRE, Dynamic Range Expansion, stands for expanding the dynamic range of a signal. Any signal before entering analog circuit below the threshold is expanded by the specified ratio, and also the analog end is compressed by the inverse of this ratio.

The function block is depicted as below. DRE controller will monitor the signal and check if it is smaller than the threshold. If the signal is continuously smaller than the threshold for a certain time, the digital gain will be raised to current analog gain and the analog gain will be reduced to 0dB to keep the overall path gain unchanged.

Figure 24. DRE Function Block

There are some parameters necessary to be configured before enabling DRE. The Threshold, (0x69), is the trigger point to enter or leave DRE. Before entering DRE, the Hold Time, (0x68[2:1]), is the time before starting to find zero cross point when signal < Threshold is triggered. In Zero crossing stage, the Hold Time is also used to timeout this stage if no zero cross is detected. The Coarse delay, (0x6B[4:0]), is used to delay the gain-changing time of digital and analog end after finding zero cross stage. The gain-changing time for digital, (0x6A[9:0]), and analog end, (0x6A[29:20]), can be both fine-tuned to compensate the path delay from digital end to analog end. During DRE, if any signal is detected as larger than Threshold, it is going to leaving DRE after zero cross point is detected or Hold Time is expired. Also, the Coarse delay, Analog fine delay and Digital fine delay are applied to compensate the path delay between digital end and analog end.

RICHTEK is a registered trademark of Richtek Technology Corporation Copyright © 2019 Richtek Technology Corporation. All rights reserved. DS5510-00

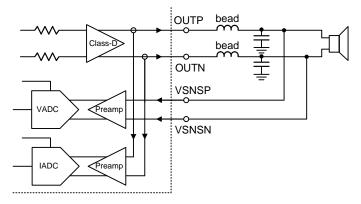

#### V/I Sensing

The RT5510 has built-in voltage and current sensing to monitor speaker behavior in real time. The VSNSP and VSNSN pins are speaker voltage sensing application and it should be connected after ferrite bead filter. In addition to getting the output voltage on speaker, the V-Sense connections can eliminate output trace and ferrite bead filter resistance IR drop between output pin to V-Sense terminal. The voltage sense monitors the speaker load voltage signal via an amplifier and an A/D converter. The current sense monitors the speaker load current with a small resistor, this signal via an amplifier and an A/D converter. Both signal output are pin DATAO.

This feature can be set to disable in the register 0xA3 bit'[3:2] to reduce the quiescent current. Please refer to Table 12.

| Register | Bits | Bits Name  | Description                                              |

|----------|------|------------|----------------------------------------------------------|

| 0xA3     | 3    | D_CSADC_EN | Current sense ADC<br>0 : Disable<br>1 : Enable (default) |

|          | 2    | D_VSADC_EN | Voltage sense ADC<br>0 : Disable (default)<br>1 : Enable |

Users can use the algorithm and the RT5510 to reach speaker protection.

If the system has a speaker protection algorithm, the voltage and current sensing data can be used to achieve speaker excursion and temperature protection. Regarding the temperature protection of the speaker, the speaker resistance can be estimated by voltage and current sensing data, and the temperature of the speaker is calculated from the temperature coefficient of resistance of the coil material. Current sensing data obtains the current variation to estimate the speaker excursion.

#### **Boost Capacitor Selection**

The RT5510 VBAT power is from battery in real cell phone, and the trace is not shortest and battery provide to other device on phone mother board. The current peak drop and voltage ripple is predictable on VBAT pin. In order to reduce the ripple from battery and boost converter, the boost input voltage should be stable. Place a  $10\mu$ F ceramic capacitor close to the VBAT pin and inductor. For cell phone applications, ceramic capacitor has small size and low ESR. Choose X5R or X7R temperature characteristic to keep capacitance in higher temperature.

When select capacitor, users have to ensure the DC bias characteristics in component datasheet, it will show the capacitance reduction percentage from rating. It is suggested to choose capacitor voltage rating at least 2x the maximum DC voltage application range to avoid capacitance reduction. For boost VBST = 9.5V application, a 10µF for input capacitor and a 100nF for DVDD decoupling capacitor are recommended.

Boost output capacitor is important for supply Class-D amplifier PVDD power. This capacitor can reduce boost output voltage ripple and keep the boost output voltage stable. If the output capacitance drops to low, the supply power PVDD for class-D amplifier will be too low and get worst performance.

The output ripple can be determined as following equation :

$$\Delta V_{OUT} = \frac{D \times I_{OUT} \times T_{S}}{\eta \times C_{OUT}} + (\frac{I_{OUT}}{1 - D} + \frac{V_{IN} \times D \times T_{S}}{2 \times L_{Boost}}) \times r_{C\_esr}$$

Boost capacitor connected to BST is important for stability. The CPVDD capacitance is changed by DC bias. When select capacitor, please notice the DC bias characteristics. The recommended minimum CPVDD capacitance is 6µF for 3.6W output power, 8µF for 4.3W output power, and 10µF for 5W output power.

#### **Boost Inductor Selection**

Small size and better efficiency are the major concerns for portable devices, such as the RT5510 is used for mobile phone. The inductor should have low core loss at 1MHz (Min.) and low DCR for better efficiency.

The maximum current of inductor is highly depends on the speaker impedance which determines the output current of the boost converter. The inductor saturation current rating should be considered to cover the inductor peak current which can be approximated by the following equation :

$$I_{L\_max} = \frac{V_{OUT} \times I_{OUT}}{\eta \times V_{IN}} + \frac{V_{IN} \times D \times T_S}{2 \times L_{Boost}}$$

The following is the inductor selection reference. The recommended typical inductance is 1µH for the RT5510 boost converter. Inductor selection must consider the saturation current and DC resistance specifications. The rating inductance might be reduced by inductor current and heat, please refer to the inductance decrease current and temperature rise current in inductor datasheet. Therefore, please note the input current limit, and don't let the inductor into saturation state. For system efficiency, it is suggested to choose a low DC resistance component.

#### **Thermal Considerations**

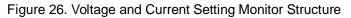

The junction temperature should never exceed the absolute maximum junction temperature TJ(MAX), listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula :

#### $P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a WL-CSP-30B 2.25x2.60 (BSC) package, the thermal resistance,  $\theta_{JA}$ , is 22.8°C/W on a standard JEDEC 51-7 high effective-thermal-conductivity four-layer test board. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated as below :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (29^{\circ}C/W) = 3.44W$  for a WL-CSP-30B 2.25x2.60 (BSC) package.

## RT5510

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 27 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 27. Derating Curve of Maximum Power Dissipation

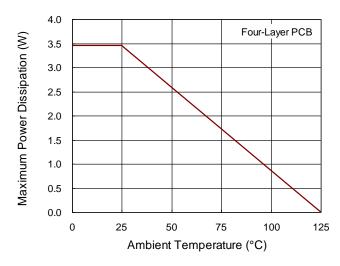

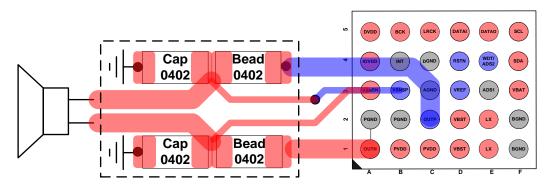

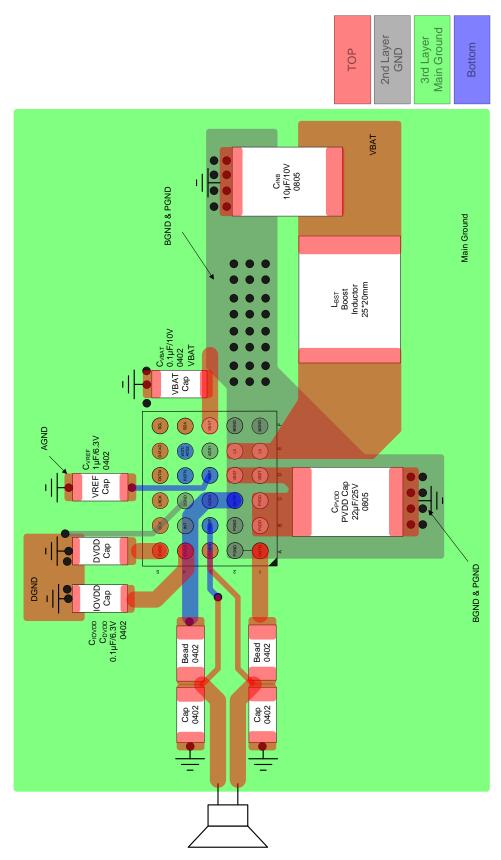

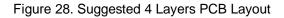

#### **Layout Considerations**

For the best performance of the RT5510, the below PCB layout guidelines including the below items must be strictly followed.

VBAT connect to LX through the boost inductor. Place the inductor as close as possible to the chip with 80 mil width at least. The shorter and wider trace provides lower parasitic inductance and resistance for achieving better efficiency. The VBAT pin only consumes few micro amperes for internal analog circuit, so the trace with 6 mil width is enough for VBAT of the RT5510. The VBAT capacitor handling high noisy current for boost circuit, please connect it to BGND and PGND first for shorten the current path and minimize the influence to digital circuit.

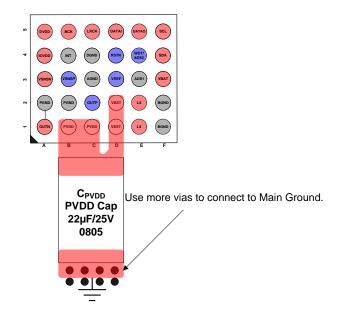

Place the filter capacitor as close as possible to the VBST pin, then use shortest trace to link the capacitors and the trace width is 20mil at least. Use more vias to connect to main ground to reduce parasitic inductance and resistance.

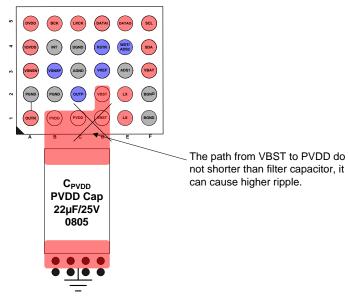

Connect PVDD to the VBST filter capacitor from an independent path to make sure the voltage feed into PVDD is well filtered. The shortest path may bypass the filter capacitor so that causes higher voltage ripple than expected on PVDD.

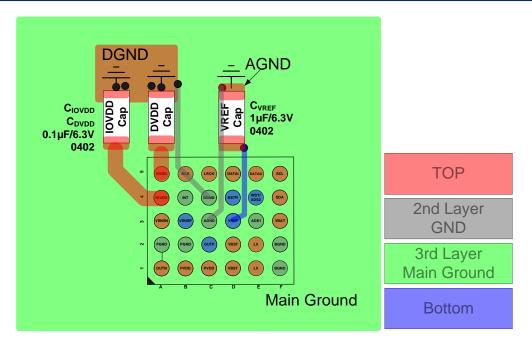

▶ For achieving good audio quality, the ground connection of decoupling capacitors (IOVDD and DVDD caps) should be linked to DGND first before going to main ground. Identically the VREF decoupling capacitor ground connection should be linked to AGND first before going to main ground. The trace width of IOVDD, DVDD and VREF are 6 mil at least.

Separate three ground planes (PGND and BGND, DGND and AGND) to isolate the noisy ground from other sensitive grounds and route the shortest path for high current return from Power/Boost ground plane before connecting to main ground to make sure the digital and analog circuit get a sufficient clean ground before influence by noisy high current path.

Analog ground:

- Dedicate a GND plane or trace to isolate other noisy ground.

- GND side of VREF decoupling capacitor should be connected to AGND first before going to main ground or connect to main ground directly from GND side of capacitor.

Copyright © 2019 Richtek Technology Corporation. All rights reserved.

Power and Boost ground :

- Dedicate a GND plane to isolate the noisy ground from other sensitive grounds.

- Use multiple vias to connect main ground.

Digital ground :

- Dedicate a GND plane or trace to isolate other noisy ground.

- GND side of DVDD decoupling capacitor should be connected to DGND

- first before going to main ground or connect to main ground directly

from GND side of capacitor.

▶ The traces of OUTA and OUTB should be kept equal width and length. When using the ferrite bead filter, it should be placed close to chip for better EMI performance. For achieving good accuracy for speaker protection, route separates trace from VSNSP and VSNSN to SPK side.

## **RT5510**

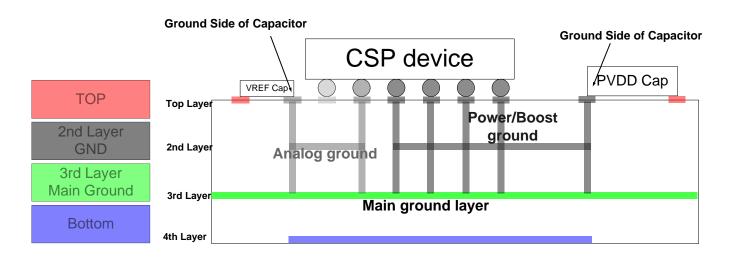

The RT5510 layout suggestion for 4 layers evaluation board is shown in Figure 28.

Copyright © 2019 Richtek Technology Corporation. All rights reserved. DS5510-00 www.richtek.com

#### **Register Table**

**Registers Description**

| Address | Byte | Bits  | Bits Name        | Default  | Туре | Description                                                                                                                                              |

|---------|------|-------|------------------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |      | 15:12 | Reserved         | 0000     | R    | Reserved                                                                                                                                                 |

|         |      | 11:8  | DEVICE_ID        | 0000     | R/W  | Device ID                                                                                                                                                |

| 0x00    | 2    | 7:0   | CHIP_ID[7:0]     | 11100000 | R    | Chip Revision ID<br>E0 : First version<br>E1 : 2 <sup>nd</sup> version<br>E2 : 3 <sup>rd</sup> version                                                   |

|         |      | 7:5   | Reserved         | 000      | R    | Reserved                                                                                                                                                 |

|         |      | 4     | PLL_LOCK         | 0        | R    | 0 : PLL is locked to BCK (default)<br>1 : PLL is unlocked to BCK                                                                                         |

|         |      | 3     | BCK_CLOCK_STABLE | 0        | R    | 0 : BCK rate stable (default)<br>1 : BCK rate unstable                                                                                                   |

| 0x01    | 1    | 2     | BCK_VALID        | 0        | R    | <ul><li>0 : BCK stable and match with</li><li>BCK_MODE setting (default)</li><li>1 : BCK unstable and miss match with</li><li>BCK_MODE setting</li></ul> |

|         |      | 1     | BCK_LOSS         | 0        | R    | 0 : BCK no loss(default)<br>1 : BCK loss                                                                                                                 |

|         |      | 0     | LRCK_LOSS        | 0        | R    | 0 : LRCK no loss(default)<br>1 : LRCK loss                                                                                                               |

|         |      | 7     | SW_RESET         | 0        | R/W  | 0 : Chip doesn't Software reset<br>(default)<br>1 : Chip reset by Software reset                                                                         |

|         |      | 6:4   | Reserved         | 000      | R    | Reserved                                                                                                                                                 |

| 0.02    |      | 3     | AMPDS            | 0        | R/W  | Soft off mode enable<br>0 : Enter soft mode before off mode<br>(enable ramp control) (default)<br>1 : Enter off mode directly (disable<br>ramp control)  |

| 0x03    | 1    | 2     | AMPE             | 0        | R/W  | Class-D enable<br>0 : Disable Class-D (default)<br>1 : Enable Class-D                                                                                    |

|         |      | 1     | SPKM             | 0        | R/W  | 0 : Unmute (default)<br>1 : Force speaker mute (with ramp<br>control)                                                                                    |

|         |      | 0     | PWDN             | 1        | R/W  | Chip power down control<br>0 : Chip enable<br>1 : Chip power down (default)                                                                              |

| Address | Byte | Bits | Bits Name        | Default | Туре  | Description                                                                                                                       |

|---------|------|------|------------------|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------|

|         |      | 7    | IF_WDT_EN        | 1       | R/W   | 0 : Watchdog interrupt disable<br>1 : Watchdog interrupt enable (default)                                                         |

|         |      | 6    | IF_BCK_STABLE_EN | 1       | R/W   | 0 : BCK un-stable interrupt disable<br>1 : BCK un-stable interrupt enable<br>(default)                                            |

|         |      | 5    | IF_PLL_LOCK_EN   | 1       | R/W   | 0 : PLL unlock interrupt disable<br>1 : PLL unlock interrupt enable<br>(default)                                                  |

|         |      | 4    | IF_UV_EN         | 1       | R/W   | 0 : Under-voltage interrupt disable<br>1 : Under-voltage interrupt<br>enable(default)                                             |

| 0x04    | 1    | 3    | IF_OV_EN         | 1       | R/W   | 0 : Over-voltage interrupt disable<br>1 : Over-voltage interrupt enable<br>(default)                                              |

|         |      | 2    | IF_OCP_EN        | 1       | R/W   | 0 : AMP NMOS or PMOS over-current<br>interrupt disable<br>1 : AMP NMOS or PMOS over-current<br>interrupt enable (default)         |

|         |      | 1    | IF_BST_OC_EN     | 1       | R/W   | 0 : Boost over-current interrupt disable<br>1 : Boost over-current interrupt enable<br>(default)                                  |

|         |      | 0    | IF_OT_EN         | 1       | R/W   | 0 : Over-temperature interrupt disable<br>1 : Over-temperature interrupt enable<br>(default)                                      |

|         |      | 7    | IF_WDT           | 0       | R/W1C | Watchdog interrupt flag, write 1 to<br>clear<br>0 : Chip operating mode (default)<br>1 : Interrupt flag = 1, WDT invalid          |

|         |      | 6    | IF_BCK_STABLE    | 0       | R/C   | BCK un-stable interrupt flag<br>0 : Chip operating mode (default)<br>1 : Interrupt flag = 1, BCK un-stable                        |

|         |      | 5    | IF_PLL_LOCK      | 0       | R/C   | PLL unlock interrupt flag<br>0 : Chip operating mode (default)<br>1 : Interrupt flag = 1, PLL unlock                              |