### High-Integration VOOC (Voltage Open Loop Multi-Step Constant-Current Charging) Protocol Controller with Internal Feedback Compensation

### **General Description**

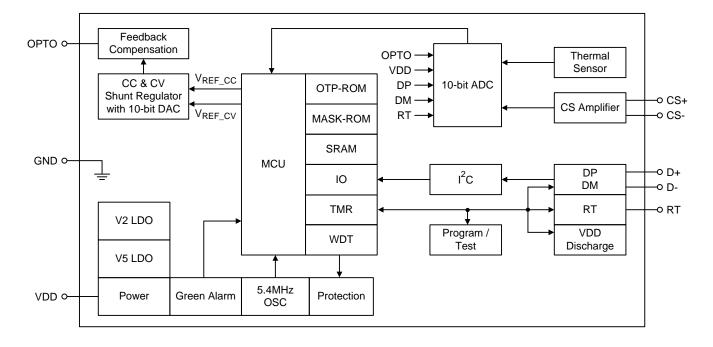

The RT7203V is a programmable controller with integration of VOOC protocol, and the built-in feedback compensation. An internal MCU is designed in to handle various proprietary protocols via the D+/D-interface.

This controller is a specific design with high integration for off-line AC-DC converters possessing high power density. The RT7203V integrates a constant voltage loop, a constant current loop and the built-in compensation in feedback control to better regulate the design, this IC not only possesses a feature of component saving via its feedback compensation, but also provides an enhanced transient response and safety protections via the integration of diverse functions.

In applications of high precision control, dual operational amplifiers are adopted in the Digital-to-Analog Converter (DAC) to provide reference voltages used for regulation of voltage loop and current loop in programming the constant voltage (CV) and the constant current (CC), respectively.

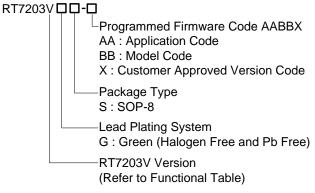

### **Ordering Information**

#### Note :

The products are :

- ► RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ► Suitable for use in SnPb or Pb-free soldering processes.

### Features

- Protocol Support

- Proprietary Protocols

- Highly Integrated

- Suited for 3.3V to 13V VDD Range

- Embedded MCU with an Mask ROM of 20kB, an OTP-ROM of 4kB, and an SRAM of 0.75kB

- Built-in Shunt Regulators for Constant Voltage and Constant Current Control

- Built-in Feedback Compensation

- Built-in Temperature Sensing

- Built-in 10-bit Analog-to-Digital Converter

- VDD Pin for Quick Discharge of Output Capacitor

- < 3mA Operating Current in Normal Mode</p>

- < 1.5mA Operating Current in Sleep Mode</p>

- ► < 900µA Operating Current in Green Mode

- Protection

- Adaptive Output Over-Voltage Protection

- Adaptive Under-Voltage Protection

- D+/D- Over-Voltage Protection

- Firmware-Programmable Contant Current Protection

- Firmware-Programmable Over-Current Protection

- Firmware-Programmable Over-Temperature Protection

### Applications

Travel Adapters with VOOC Protocol

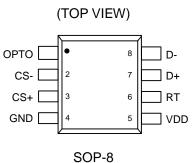

### **Pin Configuration**

### **Marking Information**

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

### **RT7203V Functional Table**

| Version                                                                                      | RT7203V               |  |  |  |  |

|----------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|

| Output Voltage Supported                                                                     | 3.3V to 13V           |  |  |  |  |

| V <sub>OUT</sub> Scaling Factor<br>R <sub>FB2</sub> / (R <sub>FB1</sub> + R <sub>FB2</sub> ) | 1/6                   |  |  |  |  |

| Built-in FB Resistor                                                                         | 0                     |  |  |  |  |

| Application                                                                                  | Proprietary Protocols |  |  |  |  |

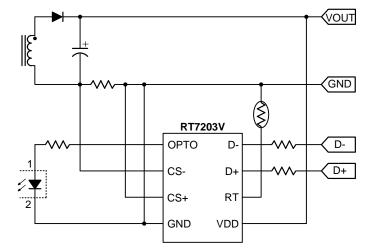

### **Simplified Application Circuit**

### **Functional Pin Description**

| Pin No. | Pin Name | Туре   | Pin Function                                                            |

|---------|----------|--------|-------------------------------------------------------------------------|

| 1       | OPTO     | AO     | Current source output for optocoupler connection.                       |

| 2       | CS-      | AI     | Negative input of a current-sense amplifier for output current sensing. |

| 3       | CS+      | AI     | Positive input of a current-sense amplifier for output current sensing. |

| 4       | GND      | GND    | Ground.                                                                 |

| 5       | VDD      | PWR    | Supply input voltage.                                                   |

| 6       | RT       | A/D IO | Remote thermal sensor connection node for over-temperature protection.  |

| 7       | D+       | A/D IO | USB D+ channel.                                                         |

| 8       | D-       | A/D IO | USB D- channel.                                                         |

### **Functional Block Diagram**

### Operation

The RT7203V is a highly integrated programmable secondary-side controller for VOOC protocol featured with innovative functions and protections for off-line AC-DC converters.

#### **Power Structure**

Biased by the VDD pin, the RT7203V has two regulated DC output voltages,  $V_5$  and  $V_2$ , to supply the internal circuit and the internal microprocessor (MCU). A bypass capacitor at the VDD is required to improve stability of the internal LDO and to minimize regulated ripple voltages.

# Constant Voltage and Constant Current (CV/CC) Regulators

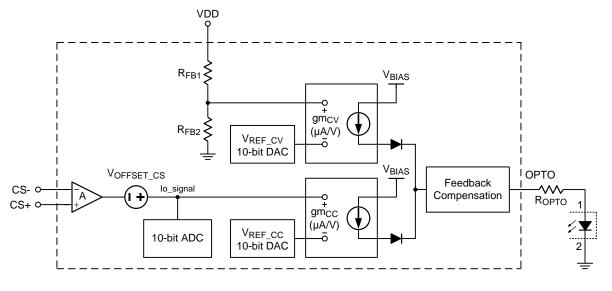

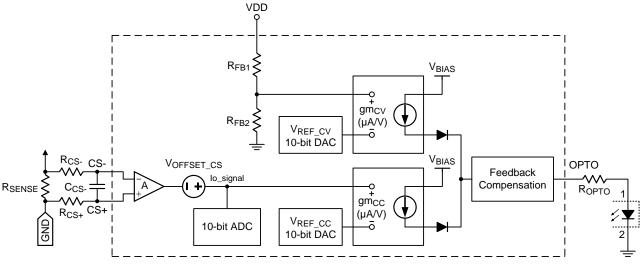

The RT7203V has two transconductance amplifiers

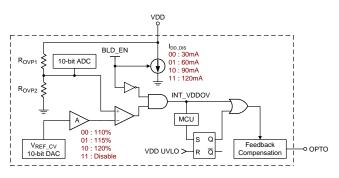

parallel connected to the feedback compensator. The feedback compensator sends signal to the OPTO pin to regulate the output voltage and the output current. The operation of each feedback loop is opposite to that of a traditional TL431 shunt regulator. The OPTO pin is in high impedance state, if the VDD voltage is still below a UVLO threshold V<sub>VDD\_ON</sub>, which ensures a smooth power-on sequence. The reference voltages of the voltage feedback loop and the current feedback loop (V<sub>REF\_CV</sub> and V<sub>REF\_CC</sub>, respectively) are analog output voltages from a 10-bit DAC. In this loop, the analog output voltage of the 10-bit DAC ranges from V<sub>DAC\_MIN</sub> = 0.523V to V<sub>DAC\_MAX</sub> (typical 2.3V), which makes output voltage resolution as small as 10mV scale to achieve high-precision CV regulation.

Figure 1. CV/CC Loops and Current Sense

#### **Current Sense**

To minimize power loss of the current sense resistor in the converter, the RT7203V employs an amplifier with virtually zero input offset voltage a voltage gain of 20 or 40. The sensed output current is amplified by the current-sense amplifier, shown as the "lo\_signal" in Figure 1, which is then sent to the current-loop regulator for constant-current regulation and also sent to the MCU, via a 10-bit ADC for analog-to-digital conversion, to update the output current status for the MCU.

#### **External Temperature Sensing**

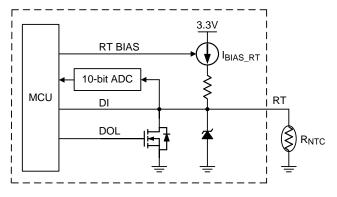

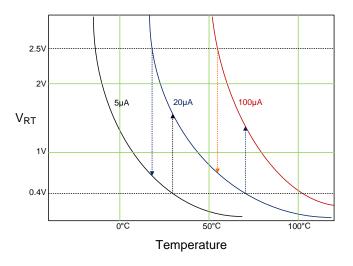

The RT7203V equips the RT pin, as a registerprogrammable current source to bias a remote thermal sensor, such as a thermistor (NTC) shown in Figure 2. If the RT voltage is lower than the over-temperature protection (OTP) threshold, and this condition sustains for a period of the programmed time delay, the OTP is then activated and triggered.

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

DS7203V-00

February

2021

## RT7203V

Figure 2. External Temperature Sensing

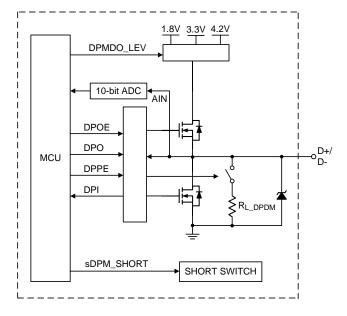

#### Interface of D+ and D-

The D+ and D- pins are used for BC1.2 compliance or for communication with other proprietary protocols. The D+ and D- pins, connected to the MCU via an ADC, can be reprogrammed for other purposes. These two pins can also be used as an analog/digital input or output, as shown in Figure 3.

Figure 3. Interface of D+ and D-

| Absolute Maximum Ratings (Note 1)              |                |

|------------------------------------------------|----------------|

| VDD to GND                                     | -0.3V to 17V   |

| • OPTO, CS-, CS+, RT, D+, D- to GND            | -0.3V to 6.5V  |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                |

| SOP-8C                                         | ).38W          |

| Package Thermal Resistance (Note 2)            |                |

| SOP-8, θJA2                                    | 261.1°C/W      |

| SOP-8, θ <sub>JC</sub> 4                       | I7°C/W         |

| Junction Temperature1                          | 50°C           |

| Lead Temperature (Soldering, 10sec.)2          | 260°C          |

| Storage Temperature Range                      | -65°C to 150°C |

| ESD Susceptibility (Note 3)                    |                |

| HBM (Human Body Model)2                        | 2kV            |

### Recommended Operating Conditions (Note 4)

| Supply Input Voltage, VDD  | 3.3V to 13V   |

|----------------------------|---------------|

| Junction Temperature Range | 40°C to 125°C |

| Ambient Temperature Range  | 40°C to 105°C |

### **Electrical Characteristics**

$(T_A = 25^{\circ}C, \text{ unless otherwise specified})$

| Parameter                                           | Symbol                | Test Conditions                     |          | Min     | Тур  | Max   | Unit |

|-----------------------------------------------------|-----------------------|-------------------------------------|----------|---------|------|-------|------|

| VDD Section                                         |                       |                                     |          |         |      |       | •    |

| VDD Turn-On Threshold                               | V <sub>VDD_ON</sub>   |                                     |          | 3.4     | 3.5  | 3.6   | V    |

| VDD Turn-Off Threshold                              | V <sub>VDD_OFF</sub>  |                                     |          | 2.85    | 2.95 | 3.05  | V    |

| VDD Turn-On/Off<br>Hysteresis                       | VVDD_HYS              |                                     |          | 0.55    |      | V     |      |

| VDD Start-Up Current                                | I <sub>DD_START</sub> | V <sub>DD</sub> = 3.2V              |          |         | 200  | 300   | μΑ   |

| VDD Operating Current                               | I <sub>DD_OP</sub>    | $V_{DD} = 5V$                       |          |         | 4.5  | mA    |      |

| VDD Green-Mode<br>Current                           | IDD_GREEN             | V <sub>DD</sub> = 5V                |          |         | 700  | 900   | μΑ   |

| Maximum VDD<br>Over-Voltage Protection<br>Threshold | VMAX_VDD_OVP          |                                     |          |         | 15.5 | 16.5  | V    |

|                                                     |                       |                                     | 00       | 104.5   | 110  | 115.5 |      |

| Register-Programmable                               | V                     | M ith roop of to $M = 1$            | 01       | 109.2   | 115  | 120.8 | %    |

| Over-Voltage Protection<br>Threshold                | V <sub>VOUT_OVP</sub> | With respect to V <sub>REF_CV</sub> | 10       | 114     | 120  | 126   | 70   |

|                                                     |                       | 11                                  |          | Disable |      |       |      |

| VDD Over-Voltage<br>Protection Deglitch Time        | t <sub>D_VDDOVP</sub> | (Note 5)                            | (Note 5) |         | 30   | 35    | μS   |

## RT7203V

| Parameter                                          | Symbol                | Test Conditions                                                                     |       | Min   | Тур   | Max   | Unit |

|----------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------|-------|-------|-------|-------|------|

| Register-Programmable                              |                       | With respect to V <sub>REF_CV</sub> .                                               | 0     | 85.5  | 90    | 94.5  |      |

| VDD Under-Voltage<br>Wake-Up Threshold             | Vdd_uv_wk             | It can be disabled by firmware.                                                     | 1     | 80.75 | 85    | 89.25 | %    |

| VDD Under-Voltage<br>Deglitch Time                 | t <sub>D_VDD_UV</sub> |                                                                                     |       |       | 50    |       | μs   |

|                                                    |                       | It is necessary to                                                                  | 00    | 15    | 30    | 45    |      |

| Register-Programmable                              | IDD_DIS               | gradually reduce the                                                                | 01    | 42    | 60    | 78    | mA   |

| VDD Discharge Current                              | 8ום_סטי               | discharge current before closing IDD_DIS.                                           | 10    | 63    | 90    | 117   |      |

|                                                    |                       |                                                                                     | 11    | 84    | 120   | 156   |      |

| VDD Discharge Current<br>Step Change Delay Time    | tSTEP_BLD             | When BLD is disabled.<br>(Note 5)                                                   | 80    | 100   | 120   | μs    |      |

| MCU Operating<br>Frequency                         | fosc_mcu              | V <sub>DD</sub> > 3V                                                                | 5.13  | 5.4   | 5.67  | MHz   |      |

| Regulator Section                                  |                       |                                                                                     |       |       |       |       |      |

| V <sub>DD</sub> Divider Resistor                   | R <sub>FB</sub>       | $R_{FB} = R_{FB1} + R_{FB2}$ $R_{FB1} : VDD to VFB$ $R_{FB2} : VFB to GND$ (Note 5) |       | 336   | 420   | 504   | kΩ   |

| V <sub>OUT</sub> Scaling Factor                    | K <sub>FB</sub>       | (R <sub>FB1</sub> + R <sub>FB2</sub> ) / R <sub>FB2</sub><br>(Note 5)               | 5.94  | 6     | 6.06  |       |      |

| Reference Voltage for<br>Standby CV Regulators     | VST_REF_CV            |                                                                                     | 0.808 | 0.833 | 0.858 | V     |      |

| Minimum DAC Output<br>Voltage for CV<br>Regulators | Vdac_min_cv           | With 10-bit digital to analo                                                        | og    |       | 0.523 |       | V    |

| Maximum DAC Output<br>Voltage for CV<br>Regulators | Vdac_max_cv           | converter.                                                                          | -     | 2.277 | 2.3   | 2.323 | V    |

| Minimum DAC Output<br>Voltage for CC<br>Regulators | Vdac_miin_cc          | With 10-bit digital to analo                                                        | DQ    |       | 0     |       |      |

| Maximum DAC Output<br>Voltage for CC<br>Regulators | Vdac_max_cc           | converter.                                                                          | -     | 1.863 | 1.882 | 1.901 | V    |

| Maximum ADC Sense<br>Voltage                       | V <sub>ADC_MAX</sub>  | With 10-bit analog to digit converter                                               | al    | 2.277 | 2.3   | 2.323 | V    |

| Maximum OPTO Output<br>Voltage                     | νορτο_μαχ             | V <sub>DD</sub> = 3.2V to 13V,<br>Isrc_opto = 1mA                                   |       | 1.8   |       |       | V    |

| Maximum OPTO Output<br>Clamping Voltage            | VOPTO_MAX_CLAMP       | V <sub>DD</sub> = 5V,<br>Isrc_opto = 1mA                                            |       | 2.1   | 2.4   | 2.7   | V    |

| Maximum OPTO<br>Sourcing Current                   | Ιορτο_μαχ             |                                                                                     |       | 2     |       | 40    | mA   |

| Internal Resistor<br>between OPTO and<br>GND       | Ropto_gnd             |                                                                                     |       | 48    | 60    | 72    | kΩ   |

RICHTEK

| Parameter                                              | Symbol                | Test Conditions                            |      | Min   | Тур        | Max   | Unit |

|--------------------------------------------------------|-----------------------|--------------------------------------------|------|-------|------------|-------|------|

| Current Sense Amplifier                                |                       |                                            |      |       |            | I     |      |

| Current Sense Voltage                                  | Kaa                   |                                            | 0    |       | 20         |       |      |

| Gain                                                   | Kcs                   |                                            | 1    |       | 40         |       | V/V  |

| Unit Gain Bandwidth                                    |                       | (Note 5)                                   |      | 1000  |            |       | kHz  |

| Current Sense Amplifier<br>Output Offset Voltage       | Voffset_cs            |                                            |      |       | 0.523      |       | V    |

| Internal Compensation                                  | Section               |                                            | -    |       |            |       | -    |

|                                                        |                       |                                            | 000  | 8     | 10         | 12    |      |

|                                                        |                       |                                            | 001  | 24    | 30         | 36    | _    |

|                                                        |                       |                                            | 010  | 40    | 50         | 60    | _    |

| Register-Programmable                                  | Rz                    | (Note 5)                                   | 011  | 64    | 80         | 96    | kΩ   |

| Rz for Zero Point                                      |                       |                                            | 100  | 96    | 120        | 144   | N2 2 |

|                                                        |                       |                                            | 101  | 136   | 170        | 204   | -    |

|                                                        |                       |                                            | 110  | 184   | 230        | 276   |      |

|                                                        |                       |                                            | 111  | 248   | 310        | 372   |      |

| Register-Programmable<br>C <sub>Z</sub> for Zero Point | Cz                    | It can be programmed by firmware. (Note 5) | ,    | 4.16  |            | 4770  | nF   |

| Register-Programmable<br>Zero Point                    | fzero                 | It can be programmed by firmware. (Note 5) | ,    | 0.10  |            | 3830  | Hz   |

| Register-Programmable<br>Middle Gain                   |                       | It can be programmed by firmware. (Note 5) | 1    | -20   |            | 27.89 | dB   |

| Overshoot Clamping<br>Comparator                       |                       | Ratio of V <sub>REF_CV</sub>               |      | 104.5 | 110        | 115.5 | %    |

| Debounce Time of<br>Overshoot Clamping                 | tovc                  |                                            |      | 25    | 30         | 35    | μS   |

| D+, D- Section                                         | ·                     |                                            |      |       |            |       | •    |

| Pull-Low Resistance                                    | R <sub>L_DPDM</sub>   | Disable/enable by firmwa                   | are. | 16    | 20         | 24    | kΩ   |

| Leakage Current                                        | I <sub>LKG_DPDM</sub> | Disable/enable by firmwa                   | are. | 0.5   | 1          | 1.5   | μΑ   |

|                                                        | Voh_op                |                                            | 00   | (     | Open Drain |       |      |

| Register-Programmable                                  | Voh_3.3V              |                                            | 01   | 2.97  | 3.3        | 3.63  | V    |

| Output High Voltage                                    | Voh_1.8V              | $V_{DD} = 5V, R_L = 15k\Omega$             | 10   | 1.62  | 1.8        | 1.98  | v    |

|                                                        | V <sub>OH_4.2V</sub>  |                                            | 11   | 3.78  | 4.2        | 4.62  |      |

|                                                        | Vol_op                |                                            |      |       |            |       |      |

|                                                        | V <sub>OL_3.3V</sub>  | - $ 15kO$                                  |      |       |            | 0.2   | V    |

| Output Low Voltage                                     | Vol_1.8V              | $$ R <sub>L</sub> = 15k $\Omega$           |      |       |            | 0.2   | V    |

|                                                        | Vol_4.2V              |                                            |      |       |            |       |      |

| Register-Programmable                                  |                       |                                            | 0    |       | 0          |       | V    |

| DP and DM Input Level                                  | VIN_LEV               |                                            | 1    |       | 0.4        |       | v    |

| Parameter                                         | Symbol              | Test Conditions                                                                                         |     | Min                          | Тур                          | Max                          | Unit |

|---------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------|-----|------------------------------|------------------------------|------------------------------|------|

|                                                   |                     |                                                                                                         | 00  | 0.7 +<br>V <sub>IN_LEV</sub> | 0.8 +<br>V <sub>IN_LEV</sub> | 0.9 +<br>V <sub>IN_LEV</sub> |      |

| Register-Programmable                             |                     |                                                                                                         | 01  | 1.3 +<br>VIN_LEV             | 1.4 +<br>VIN_LEV             | 1.5 +<br>VIN_LEV             | v    |

| Input High Trip Voltage                           | Vih_dpdm            |                                                                                                         | 10  | 1.8 +<br>Vin_lev             | 1.9 +<br>Vin_lev             | 2 +<br>Vin_lev               | v    |

|                                                   |                     |                                                                                                         | 11  | 2 +<br>VIN_LEV               | 2.1 +<br>Vin_lev             | 2.2 +<br>Vin_lev             |      |

|                                                   |                     |                                                                                                         | 00  | 0.5 +<br>VIN_LEV             | 0.6 +<br>V <sub>IN_LEV</sub> | 0.7 +<br>V <sub>IN_LEV</sub> |      |

| Register-Programmable                             | Vil dpdm            |                                                                                                         | 01  | 1.0 +<br>Vin_lev             | 1.1 +<br>V <sub>IN_LEV</sub> | 1.2 +<br>V <sub>IN_LEV</sub> | V    |

| Input Low Trip Voltage                            |                     |                                                                                                         | 10  | 1.7 +<br>Vin_lev             | 1.8 +<br>Vin_lev             | 1.9 +<br>Vin_lev             | ·    |

|                                                   |                     |                                                                                                         | 11  | 1.8 +<br>Vin_lev             | 1.9 +<br>Vin_lev             | 2.0 +<br>Vin_lev             |      |

| DPDM Switch<br>On-Resistance                      | Ron_dpdm            |                                                                                                         |     |                              |                              | 40                           | Ω    |

| DP Comparison<br>Threshold for Cable<br>Detection | Vvth_dp_cd          | Send an interrupt to MCU<br>when cable detached.<br>Disable/enable cable<br>detection by register.      | I   | 0.2                          | 0.3                          | 0.4                          | V    |

|                                                   | tdp_cd              |                                                                                                         | 00  | 0.475                        | 0.5                          | 0.525                        | ms   |

| Register-Programmable<br>Cable Detection          |                     | (Note 5)                                                                                                | 01  | 0.95                         | 1                            | 1.05                         |      |

| Debounce Time                                     |                     |                                                                                                         | 10  | 1.9                          | 2                            | 2.1                          |      |

|                                                   |                     |                                                                                                         | 11  | 3.8                          | 4                            | 4.2                          |      |

| Register-Programmable<br>Input Debounce Time      | tD_DPDMIN           | Debounce time = 0 Disable<br>tD_DPDMIN X KtD_DPDMIN                                                     |     |                              | μs                           |                              |      |

|                                                   |                     | (Note 5)                                                                                                | 1   | 142.5                        | 150                          | 157.5                        |      |

| DP/DM Over-Voltage<br>Protection Threshold        | Vdpdm_ovp           | Send a flag to MCU.                                                                                     |     | 4.5                          | 4.75                         | 5                            | V    |

| Register-Programmable                             |                     |                                                                                                         | 00  | 0.095                        | 0.1                          | 0.105                        |      |

| DP/DM Over-Voltage                                |                     | (Note 5)                                                                                                | 01  | 0.95                         | 1                            | 1.05                         | ms   |

| Protection Debounce<br>Time                       | tdpdm_ovp           |                                                                                                         | 10  | 4.75                         | 5                            | 5.25                         |      |

|                                                   |                     |                                                                                                         | 11  | 14.25                        | 15                           | 15.75                        |      |

| RT Section                                        |                     |                                                                                                         |     |                              |                              |                              |      |

| Open Loop Voltage                                 | V <sub>RT_OP</sub>  | $V_{DD} = 5V$                                                                                           | 1   | 2.6                          | 3                            | 3.4                          | V    |

|                                                   |                     |                                                                                                         | 00  | 95                           | 100                          | 105                          |      |

| Register-Programmable                             | IBIAS_RT            |                                                                                                         | 01  | 18                           | 20                           | 22                           | μA   |

| Internal Bias Current                             | IDIAS_RI            |                                                                                                         | 10  | 4.5                          | 5                            | 5.5                          | μΑ   |

|                                                   |                     |                                                                                                         | 11  |                              | Open                         |                              |      |

| RT Over-Voltage<br>Protection Threshold           | V <sub>RT_OVP</sub> | <ol> <li>Turn-off blocking MOSI<br/>or not by register setting.</li> <li>Send a flag to MCU.</li> </ol> | FET | 4.5                          | 4.75                         | 5                            | V    |

| Parameter                                                               | Symbol  | Symbol Test Conditions |     | Тур | Max | Unit |

|-------------------------------------------------------------------------|---------|------------------------|-----|-----|-----|------|

| Register-Programmable<br>RT Over-Voltage<br>Protection Debounce<br>Time | trt_ovp | (Note 5)               | 30  | 50  | 70  | μs   |

| Thermal Sensor Section                                                  |         |                        |     |     |     |      |

| Thermal Sensor Error                                                    |         | 25°C to 105°C          | -10 |     | 10  | °C   |

- **Note1**. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a low effective-thermal-conductivity single-layer test board on a JEDEC 51-3 thermal measurement standard.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- Note 5. Guaranteed by design.

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

RICHTEK is a registered trademark of Richtek Technology Corporation.

www.richtek.com

DS7203V-00

February

2021

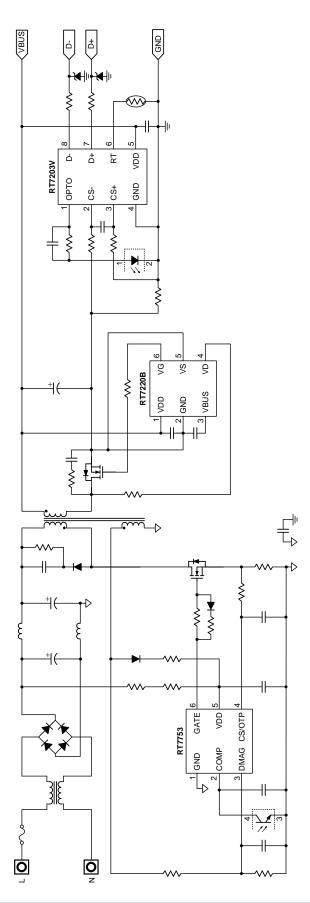

## **Typical Application Circuit**

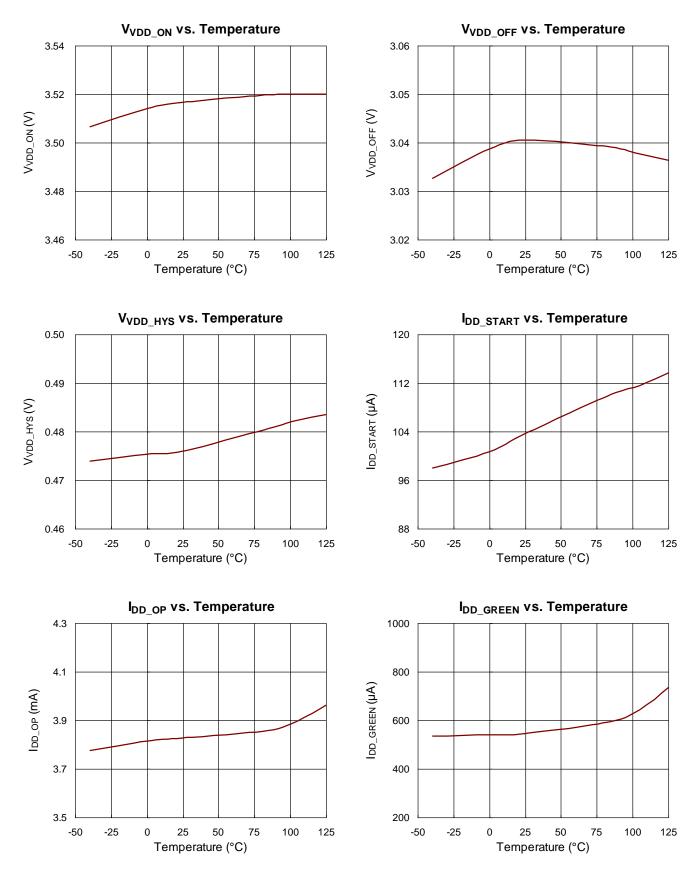

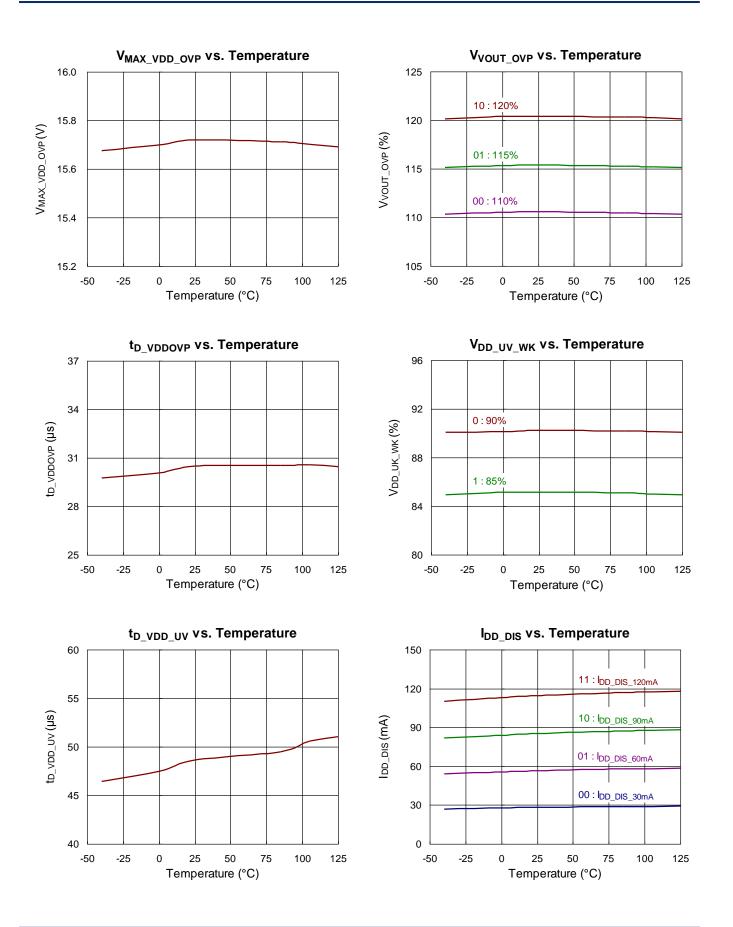

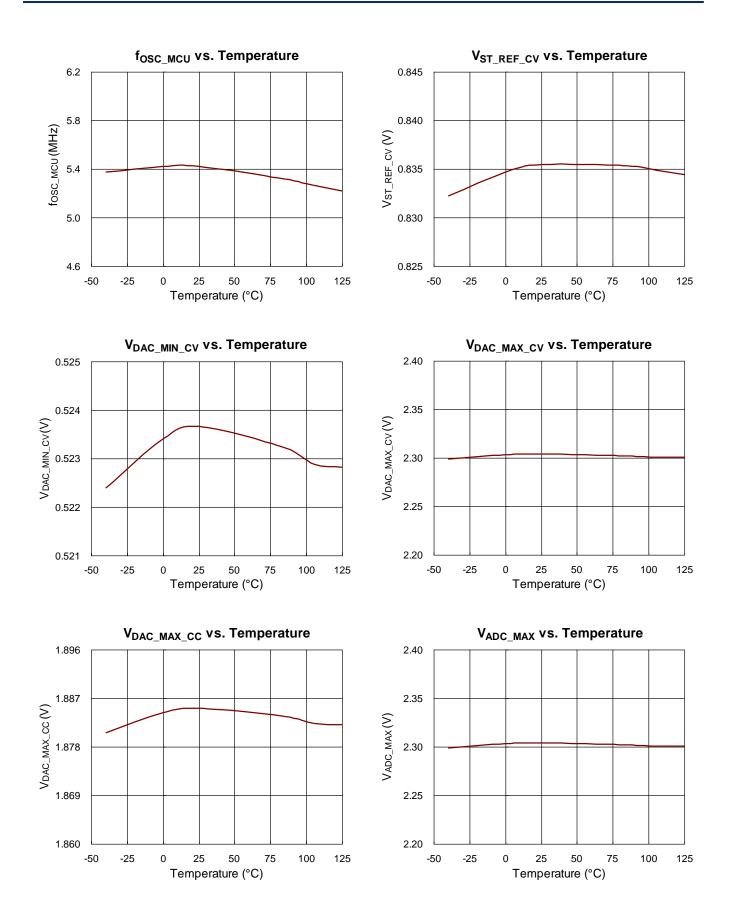

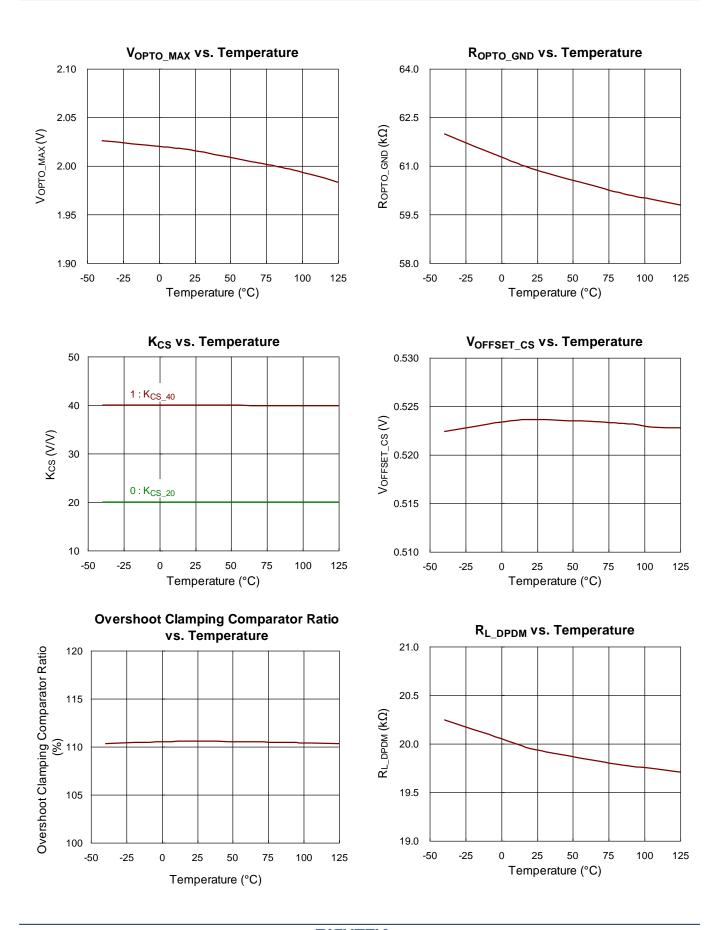

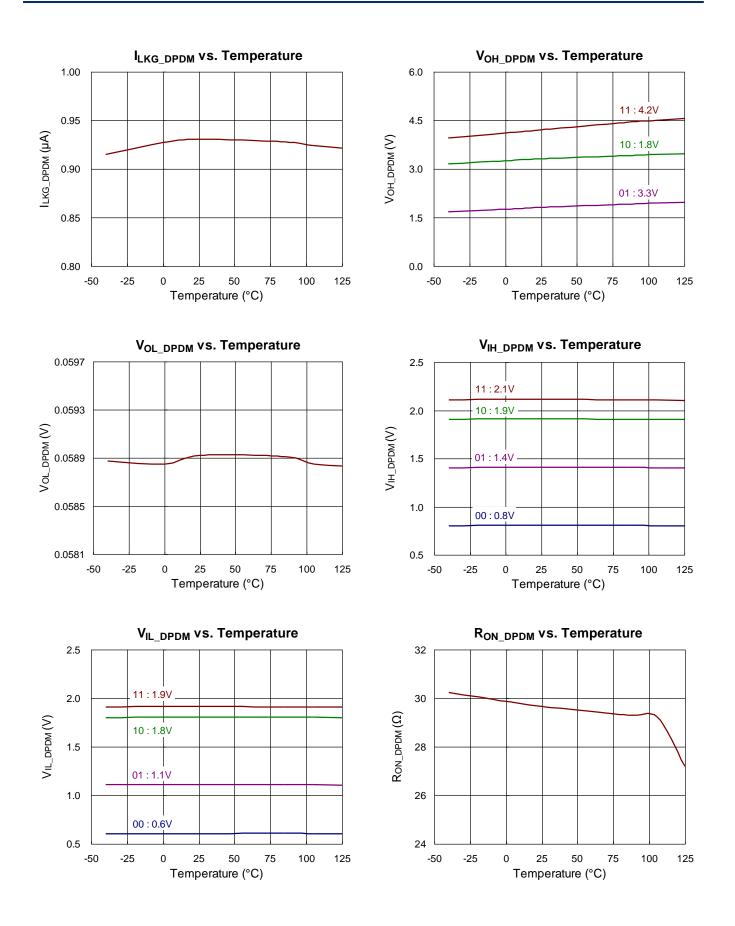

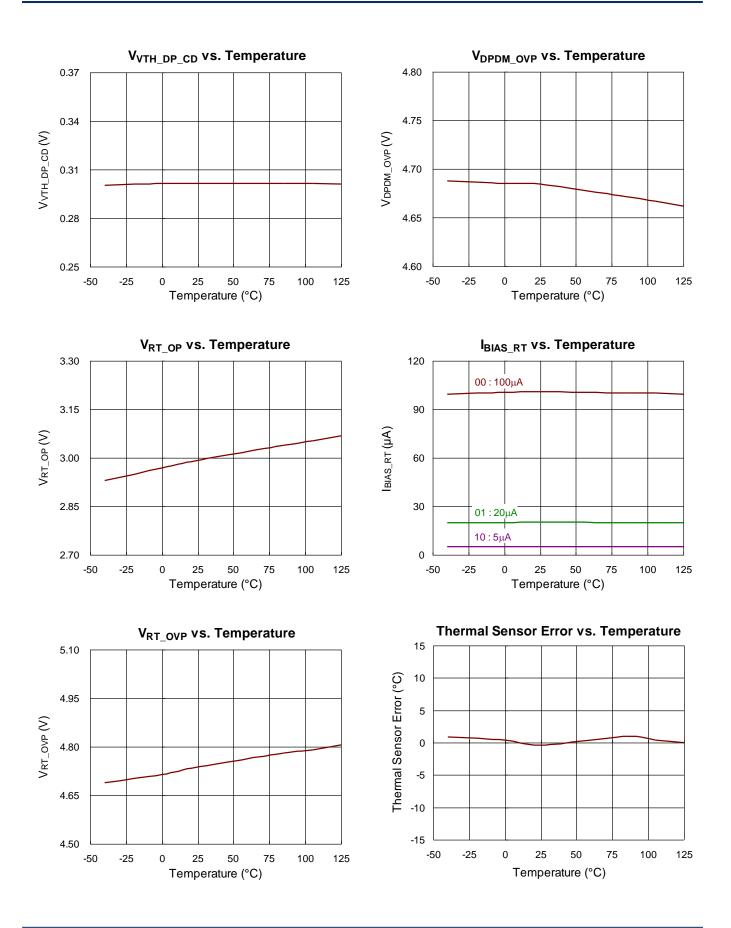

### **Typical Operating Characteristics**

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

RICHTEK

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

DS7203V-00

February

2021

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. DS7203V-00 February 2021 www.richtek.com

Copyright © 2021 Richtek Technology Corporation. All rights reserved.

RICHTEK

is a registered trademark of Richtek Technology Corporation.

www.richtek.com

DS7203V-00

February

2021

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. www.richtek.com DS7203V-00 February 2021

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation. DS7203V-00 February 2021 www.richtek.com

### **Application Information**

#### Constant Voltage (CV) Loop

As shown in Figure 4, the RT7203V incorporates two transconductance amplifiers which are connected to feedback compensation to regulate output voltage and current, respectively. The output voltage is determined as :

$V_{OUT} = K_{FB} \times V_{REF_CV}$

Where

#### $K_{FB} = (R_{FB1} + R_{FB2}) / R_{FB2} = 6$

Therefore, the  $V_{OUT}$  is determined by  $V_{REF_CV}$ , the analog output from the DAC, and its digital counterpart, which is controlled by the MCU, as shown in the Functional Block Diagram.

#### Constant Current (CC) Loop and Current Sense

Both the constant voltage and constant current compensation loops are connected to feedback compensation. The OPTO driver is sourced the current

through an external resistor R<sub>OPTO</sub> and an optocoupler, which isolates the secondary side from the primary side and then feedbacks the compensation signal to the primary side. Note that for better linearity of the loop compensation range, R<sub>OPTO</sub> should be designed to cover the operation at the minimum output voltage.

RICHTEK

$$\frac{(V_{OPTO}MAX}{R_{OPTO}} \times CTR \geq I_{COMP}MAX$$

CTR : Current transfer ratio of the optocoupler

VF : Forward voltage of the optocoupler

$V_{OPTO\_MAX}$  : The maximum OPTO voltage for the OPTO driver at sourcing 1mA.

I<sub>COMP\_MAX</sub> : The maximum COMP sourcing current of a traditional PWM controller in the primary side. It is a current sourced from an internal bias through a built-in pull-high resistor connected the COMP pin in the PWM controller.

Figure 4. CV and CC Loops

#### Internal Feedback Compensation

The RT7203V has a built-in feedback compensator that optimizes system stability and response for different applications, and furthermore can reduce external components.

The feedback compensation design is based on the system operation mode and component parameters. An off-line flyback converter mostly uses a Type-II compensator to compensate for the feedback loop. It has a zero frequency pole, a low frequency zero and a

high frequency pole. The feedback compensation design is to make the low frequency zero point of compensator to compensate the low frequency pole point of system and make the high frequency pole point to compensate the ESR zero point of output capacitor, by doing this the system can possess a better phase margin. In addition to phase margin, a proper middle gain of compensator is chosen to get the better transient response, and improve the system stability.

The RT7203V provides a simple and flexible design for the feedback compensation. The  $R_Z$ ,  $C_Z$  and the middle gain of the compensator can be programmed according to different output conditions. With this feature, one can easily achieve a stable system by using this flexible design for compensation.

#### **Power-Up Sequence**

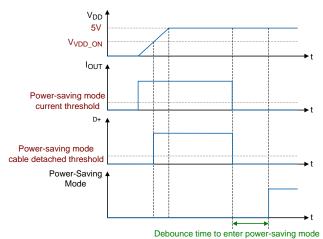

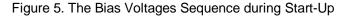

Figure 5 shows the timing diagram for the power-up sequence. When start-up, the default output voltage is set at 5V. Once a device via the proprietary protocol is attached, the UFP will deliver voltage and current settings to the RT7203V for the MCU to decode. The controller simultaneously programs reference voltages, VREF CV and VREF CC, for the CV and CC loops, respectively. Those voltages are the analog outputs converted by the DAC. If the devise via the proprietary protocol is detached and the output current is lower than the power-saving mode threshold, which is typically programmed as 200mA, the RT7203V will enter the power-saving mode, under which the RT7203V operates at an ultra-low operating current and thus the total input power can be saved. Meanwhile, if the output current increases and exceeds the power-saving mode threshold, or any input/output signal is toggled, or a proprietary protocol device is attached, the RT7203V will exit from the power-saving mode.

#### **Output Voltage Rises and Falls**

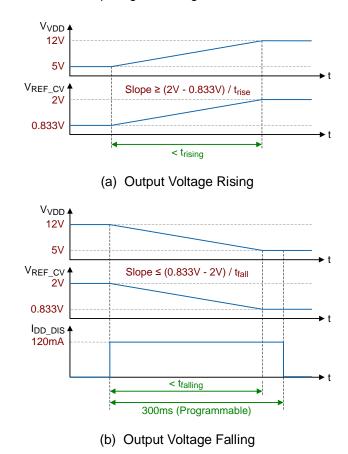

When the protocol is detected, the reference voltage  $V_{REF_CV}$  can be set by the request of the UFP. Both the rise time and fall time of output voltages should be

RT7203V

less than the spec. given in Figure 6.

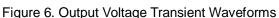

The RT7203V provides a control for the discharge current from the VDD pin. This function utilizes a bleeder to help discharge of the output capacitor to  $V_{safe5V}$  upon the detachment of a connected device, or to a lower desired output voltage level upon a UFP request, such as VOUT from 12V to 5V. The discharge current can be programmed by the internal register according to the VDD voltage level, as shown in Figure 7.

Figure 7. Discharge Current Control from VDD Pin

# RICHTEK

#### **Output Over-Voltage Protection**

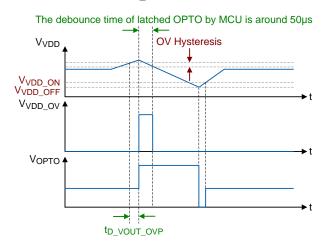

As shown in the Figure 8 and Figure 9, in case the optocoupler of the feedback loop is in malfunction due to aging. If the internal voltage related to VDD is higher than the programmable threshold  $V_{VOUT_OVP}$ . The OPTO pin voltage will be latched high and the VDD discharge current function will be enabled by a period until the VDD voltage drops below the VDD turn-off threshold  $V_{VDD_OFF}$ .

#### Figure 8. Timing Sequence of the OVP Function

Figure 9. OVP Functional Diagram

#### **Temperature Sensing and Thermal Protection**

The RT7203V provides the RT pin for over-temperature protection or thermal monitoring. As shown in Figure 2, the RT pin sources a constant bias current for the remote thermal sensor of a NTC thermistor, connected from the RT pin to GND for temperature sensing. If the RT voltage is lower than the programmable threshold voltage and the condition sustains for a programmable deglitch time, the over-temperature protection can then be activated and triggered.

The bias current through the RT pin can be programmed as  $100\mu A$ ,  $20\mu A$ , or  $5\mu A$  by setting the

internal register. With an appropriate bias current setting, linearity of temperature sensing over the temperature range of 25°C to 100°C can be significantly improved. In addition, the RT7203V can deliver the sensed RT voltage data back to the UFP via the protocol (Vendor Defined Message), if necessary. Figure 10 shows the RT voltages vary with temperature at three different bias currents, using the NTC thermistor TTC104 as an example.

Figure 10. The RT Voltages vs. Temperature at Three Bias Currents

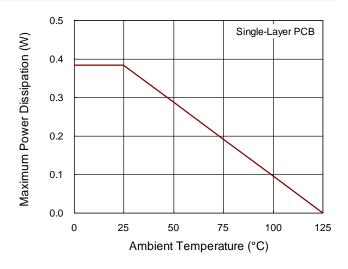

#### Thermal Considerations

The junction temperature should never exceed the absolute maximum junction temperature  $T_{J(MAX)}$ , listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula :

$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) \ / \ \theta_{\mathsf{J}\mathsf{A}}$

where  $T_{J(MAX)}$  is the maximum junction temperature, T<sub>A</sub> is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent.

For a SOP-8 package, the thermal resistance,  $\theta_{JA}$ , is 261.1°C/W on a standard JEDEC 51-3 low effective thermal conductivity single layer test board. The maximum power dissipation at  $T_A = 25^{\circ}$ C can be calculated as below :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (261.1^{\circ}C/W) = 0.38W$  for a SOP-8 package.

The maximum power dissipation depends on the operating ambient temperature for the fixed  $T_{J(MAX)}$  and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 11 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 11. Derating Curve of Maximum Power Dissipation

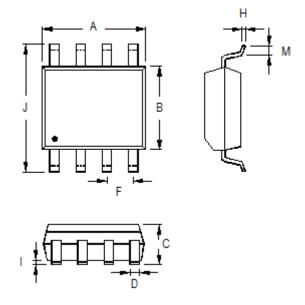

### **Outline Dimension**

| Cumb al | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|---------|--------------|---------------|----------------------|-------|--|

| Symbol  | Min          | Max           | Min                  | Max   |  |

| А       | 4.801        | 5.004         | 0.189                | 0.197 |  |

| В       | 3.810        | 3.988         | 0.150                | 0.157 |  |

| С       | 1.346        | 1.753         | 0.053                | 0.069 |  |

| D       | 0.330        | 0.508         | 0.013                | 0.020 |  |

| F       | 1.194        | 1.346         | 0.047                | 0.053 |  |

| Н       | 0.170        | 0.254         | 0.007                | 0.010 |  |

| I       | 0.050        | 0.254         | 0.002                | 0.010 |  |

| J       | 5.791        | 6.200         | 0.228                | 0.244 |  |

| М       | 0.400        | 1.270         | 0.016                | 0.050 |  |

8-Lead SOP Plastic Package

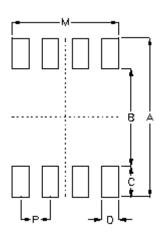

# **Footprint Information**

RICHTEK

| Numbe           |     | Footprint Dimension (mm) |      |      |      |      | Toloropoo |           |

|-----------------|-----|--------------------------|------|------|------|------|-----------|-----------|

| Package         | Pin | Ρ                        | А    | В    | С    | D    | М         | Tolerance |

| SOP-8/SOP-8(FC) | 8   | 1.27                     | 6.80 | 4.20 | 1.30 | 0.70 | 4.51      | ±0.10     |

#### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

#### RICHTEK

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and result from its use. No license is granted by implication or otherwise under any patent or patent or patents of patents of subsidiaries.

Copyright © 2021 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.