# 1A, 5.5V, Ultra Low Dropout Linear Regulator

### **General Description**

The RT9085A is a high performance positive voltage regulator with separated bias voltage ( $V_{BIAS}$ ), designed for applications requiring low input voltage and ultra low dropout voltage, output current up to 1A. The feature of ultra low dropout voltage is ideal for applications where output voltage is very close to input voltage. The input voltage can be as low as 0.8V and the output voltage is adjustable by an external resistive divider. The RT9085A features very low quiescent current consumption for portable applications. The device is available in the WL-CSP-6B 0.8x1.2 (BSC) package.

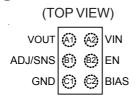

### **Pin Configuration**

WL-CSP-6B 0.8x1.2 (BSC)

## **Marking Information**

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

### **Features**

• Input Voltage Range: 0.8V to 5.5V

Bias Voltage Range: 3V to 5.5V

• Available in Fixed and Adjustable (0.5V to 3V)

• Ultra Low Dropout Voltage: 60mV at 1A

Accurate Output Voltage Accuracy (1%) Over Line, Load @ 25°C

Low Bias Input Current

→ Typ 35µA in Operating Mode

Typ 0.5μA in Shutdown Mode

Output Active Discharge Function

• Enable Control

• Stable with a 10µF Output Ceramic Capacitor

• RoHS Compliant and Halogen/Pb Free

### **Applications**

- Battery Powered Systems

- Portable Electronic Device

- · Digital Set Top Boxes

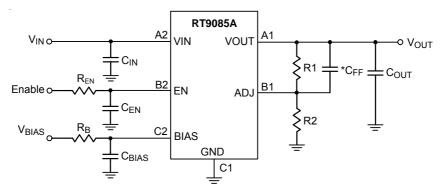

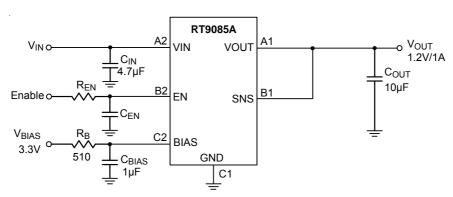

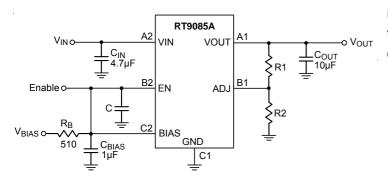

# **Simplified Application Circuit**

# **Ordering Information**

| Product No.   | Nominal Output<br>Voltage | Package                                |

|---------------|---------------------------|----------------------------------------|

| RT9085A-07WSC | 0.70V                     |                                        |

| RT9085A-0GWSC | 0.75V                     |                                        |

| RT9085A-08WSC | 0.80V                     |                                        |

| RT9085A-0HWSC | 0.85V                     | -                                      |

| RT9085A-09WSC | 0.90V                     | -                                      |

| RT9085A-0JWSC | 0.95V                     |                                        |

| RT9085A-10WSC | 1.00V                     |                                        |

| RT9085A-1KWSC | 1.05V                     | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

| RT9085A-11WSC | 1.10V                     | - WL-CSP-6B 0.8x1.2 (BSC)              |

| RT9085A-1AWSC | 1.15V                     |                                        |

| RT9085A-12WSC | 1.20V                     |                                        |

| RT9085A-1BWSC | 1.25V                     |                                        |

| RT9085A-13WSC | 1.30V                     |                                        |

| RT9085A-15WSC | 1.50V                     |                                        |

| RT9085A-18WSC | 1.80V                     |                                        |

| RT9085AWSC    | Adjustable                |                                        |

# **Functional Pin Description**

| Pin No. | Pin Name               | Pin Function                                                                                                                                                                                                                                                                                                                                                                        |

|---------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1      | VOUT                   | Regulator output pin. A 10μF capacitor should be placed directly at this pin.                                                                                                                                                                                                                                                                                                       |

| A2      | VIN                    | Regulator input pin. A 4.7μF capacitor should be placed directly at this pin.                                                                                                                                                                                                                                                                                                       |

| D4      | ADJ (ADJ devices)      | Adjustable output voltage feedback input pin.                                                                                                                                                                                                                                                                                                                                       |

| B1      | SNS (Fix Vlot devices) | Output voltage sensing input, connect to the output terminal on the PCB.                                                                                                                                                                                                                                                                                                            |

| B2      | EN                     | Chip enable pin. Pulling this pin below 0.54V turns the regulator off, reducing the quiescent current to a fraction of its operating value. This pin must not be left unconnected, connect to the RC filter after BIAS if not being used. If EN is an external signal, it suggest connect RC filter for operation. Keep $V_{\rm EN} < V_{\rm BIAS} + 0.5 V$ to prevent malfunction. |

| C1      | GND                    | Ground pin. This pin must be connected to ground.                                                                                                                                                                                                                                                                                                                                   |

| C2      | BIAS                   | Supply V <sub>BIAS</sub> ripple should be less than 30mV (5mV/ $\mu$ s) to secure safe stabilization of internal control circuitry. Apply RC filter consists of (500 to 1k) $\Omega$ + 1 $\mu$ F at the pin input. The V <sub>BIAS</sub> must be higher than 3V and ensure V <sub>BIAS</sub> $\geq$ V <sub>OUT</sub> + 1.6V for normal operation.                                   |

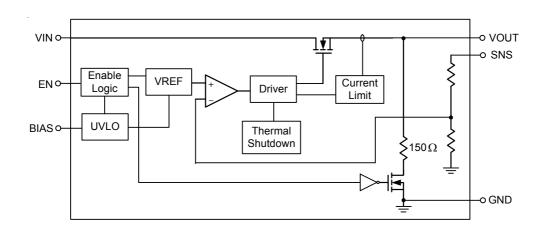

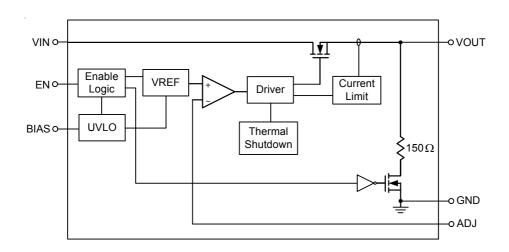

# **Functional Block Diagram**

### **V<sub>OUT</sub> Fixed Version**

### **V<sub>OUT</sub> Adjustable Version**

### Operation

The RT9085A is using N-MOSFET pass transistor for output voltage regulation from VIN voltage. The separated bias voltage (V<sub>BIAS</sub>) power the low current internal control circuit for applications requiring low input voltage and ultra low dropout voltage.

In steady-state operation, the feedback voltage is regulated to the reference voltage by the internal regulator. When the feedback voltage signal is less than the reference, the output current passes through the power MOSFET will be increased. The extra amount of the current is sent to the output until the voltage level of ADJ pin returns to the reference. On the other hand, if the feedback voltage is higher than the reference, the power MOSFET current is decreased. The excess charge at the output can be released by the loading current.

#### Chip Enable and Shutdown

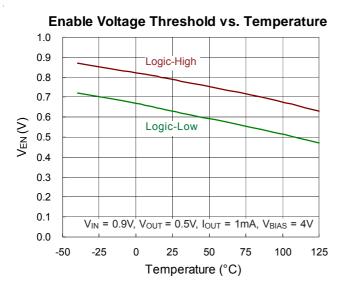

The RT9085A provides an EN pin, as an external chip enable control, to enable or disable the device. VEN below 0.54V turns the regulator off and enters the shutdown mode, while V<sub>EN</sub> above 0.93V turns the regulator on. When the regulator is shutdown, the ground current is reduced to a maximum of 1µA.

#### **Output Active Discharge**

When the RT9085A is operating at shutdown mode, the device has an internal active pull down circuit that connects the output to GND through a 150 $\Omega$  resistor for output discharging purpose.

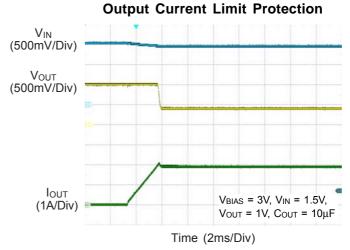

#### **Current Limit**

The RT9085A continuously monitors the output current to protect the pass transistor against abnormal operations. When an overload or short circuit is encountered, the current limit circuitry controls the pass transistor's gate voltage to limit the output within the predefined range.

#### **Over-Temperature Protection (OTP)**

The RT9085A has an over-temperature protection. When the device triggers the OTP, the device shuts down until the temperature back to normal state.

## Absolute Maximum Ratings (Note 1)

| Supply Input Voltage, VIN                                                   | –0.3V to 6V           |

|-----------------------------------------------------------------------------|-----------------------|

| • Enable Input Voltage, EN                                                  | 0.3V to (BIAS + 0.5V) |

| • All Other Pins                                                            | –0.3V to 6V           |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                       |

| WL-CSP-6B 0.8x1.2 (BSC) (Note 2)                                            | 1.29W                 |

| WL-CSP-6B 0.8x1.2 (BSC) (Note 3)                                            | 1.25W                 |

| Package Thermal Resistance (Note 2)                                         |                       |

| WL-CSP-6B 0.8x1.2 (BSC), $\theta_{JA}$ (Note 2)                             | 77°C/W                |

| WL-CSP-6B 0.8x1.2 (BSC), $\theta_{JA}$ (Note 3)                             | 80°C/W                |

| Junction Temperature                                                        | 150°C                 |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C                 |

| Storage Temperature Range                                                   | –65°C to 150°C        |

| ESD Susceptibility (Note 4)                                                 |                       |

## **Recommended Operating Conditions** (Note 5)

| <ul> <li>Supply Input Voltage</li> </ul> | , VIN | N 0.8V to 5.5V |  |

|------------------------------------------|-------|----------------|--|

|------------------------------------------|-------|----------------|--|

• Supply Input Voltage, BIAS ----- 3V to 5.5V

HBM (Human Body Model)------2kV

• Junction Temperature Range ----- --- -40°C to 125°C

### **Electrical Characteristics**

$(V_{BIAS} \ge 3V, \text{ and } V_{BIAS} \ge V_{OUT} + 1.6V, V_{IN} = V_{OUT(NOMI)} + 0.3V, I_{OUT} = 1mA, V_{EN} = 1V, C_{IN} = 4.7\mu\text{F}, C_{OUT} = 10\mu\text{F}, C_{BIAS} = 1\mu\text{F}, T_A = 25^{\circ}\text{C}, \text{ unless otherwise specified)}.$  (Note 7)

| Parameter                            | Symbol                                  | Test Conditions                                                        | Min  | Тур  | Max  | Unit |

|--------------------------------------|-----------------------------------------|------------------------------------------------------------------------|------|------|------|------|

| Operating Input<br>Voltage Range     |                                         |                                                                        | 0.8  |      | 5.5  | ٧    |

| Operating Bias<br>Voltage Range      | VBIAS                                   |                                                                        | 3    |      | 5.5  | ٧    |

| Under-Voltage                        | V                                       | V <sub>BIAS</sub> rising                                               |      | 1.6  | -    | ٧    |

| Lockout                              | V <sub>UVLO</sub>                       | Hysteresis                                                             | -    | 0.2  | 1    | ٧    |

| Reference Voltage (Adj devices only) | V <sub>REF</sub>                        |                                                                        | 0.49 | 0.5  | 0.51 | V    |

| Output Voltage<br>Accuracy (Note 6)  |                                         |                                                                        | -0.5 |      | 0.5  | %    |

| Output Voltage<br>Accuracy (Note 6)  | · · · · · · · · · · · · · · · · · · · · |                                                                        | -1   | 1    | 1    | %    |

| V <sub>IN</sub> Line Regulation      | ΔVLINE_VIN                              | $V_{OUT(NOM)} + 0.3V \le V_{IN} \le 5V$                                | 1    | 0.01 |      | %/V  |

| V <sub>BIAS</sub> Line<br>Regulation | ΔV <sub>BIAS_VIN</sub>                  | $V_{BIAS} \geq 3V$ and $V_{OUT(NOM)}$ + $1.6V \leq V_{BIAS} \leq 5.5V$ |      | 0.01 |      | %/V  |

| Paramete                                        | r              | Symbol                 | Test Conditions                                                                                                          | Min   | Тур                   | Max  | Unit              |

|-------------------------------------------------|----------------|------------------------|--------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|------|-------------------|

| Load Regulation                                 |                | $\Delta V_{LOAD}$      | I <sub>OUT</sub> = 1mA to 1A                                                                                             | 2     |                       | mV   |                   |

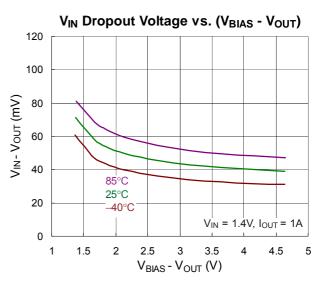

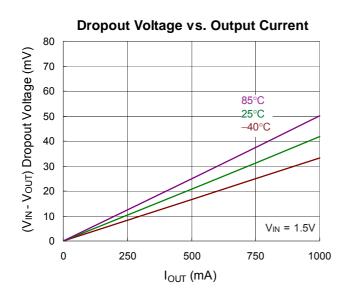

| V <sub>IN</sub> Dropout Voltag                  | je             | V <sub>DROP_VIN</sub>  | I <sub>OUT</sub> = 1A (Note 10)                                                                                          | 60 75 |                       | mV   |                   |

| VBIAS Dropout Volt                              | age            | VDROP_BIAS             | I <sub>OUT</sub> = 1A, V <sub>IN</sub> = V <sub>BIAS</sub><br>(Note 8, Note 9)                                           |       | 1.05                  | 1.5V | V                 |

| Output Current Lin                              | nit            | I <sub>LIM</sub>       | Vout = 90% of Vout(NOM)                                                                                                  |       | 2000                  |      | mA                |

| ADJ Pin Operating (ADJ devices only)            |                | I <sub>ADJ</sub>       |                                                                                                                          |       | 0.1                   | 0.5  | μΑ                |

| Bias Pin Quiescen                               | t Current      | I <sub>BIAS</sub>      | V <sub>BIAS</sub> = 3V                                                                                                   |       | 35                    | 50   | μА                |

| Bias Pin Shutdowr                               | Current        | I <sub>BIAS(DIS)</sub> | V <sub>EN</sub> ≤ 0.4 V                                                                                                  |       | 0.5                   | 1    | μА                |

| V <sub>IN</sub> Pin Shutdown                    | Current        | I <sub>VIN(DIS)</sub>  | V <sub>EN</sub> ≤ 0.4 V                                                                                                  |       | 0.5                   | 1    | μА                |

| Enable Threshold                                | H-Level        | VENH                   |                                                                                                                          | 0.69  | 0.81                  | 0.93 | \<br>\            |

| Voltage                                         | No Thi General |                        | 0.54                                                                                                                     | 0.68  | 0.87                  | ]    |                   |

| EN Pull Down Curi                               | rent           | I <sub>EN</sub>        | V <sub>EN</sub> = 5.5V, V <sub>BIAS</sub> = 5.5V                                                                         |       | 0.3                   |      | μА                |

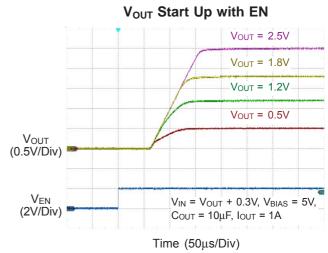

| Turn-On Time                                    |                | ton                    | From assertion of V <sub>EN</sub> to V <sub>OUT</sub> = 90% of V <sub>OUT</sub> (NOM). V <sub>OUT</sub> (NOM) = 1V       |       | 150                   |      | μS                |

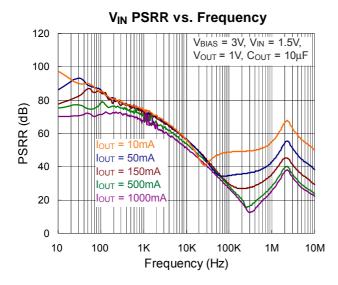

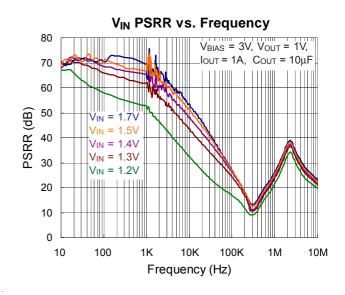

| Power Supply Rejection                          |                | PSRR_V <sub>IN</sub>   | $V_{IN}$ to $V_{OUT}$ , f = 1kHz,<br>$I_{OUT}$ = 150mA, $VIN \ge V_{OUT}$ + 0.5V                                         |       | 70                    |      | dB                |

| Ratio (Note 11)                                 |                | PSRR_V <sub>BIAS</sub> | V <sub>BIAS</sub> to V <sub>OUT</sub> , f = 1kHz,<br>I <sub>OUT</sub> = 150mA, V <sub>IN</sub> ≥ V <sub>OUT</sub> + 0.5V |       | 70                    |      | dB                |

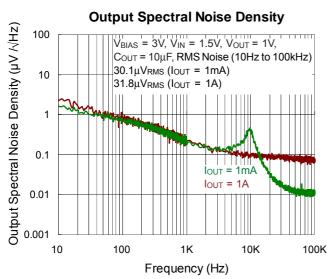

| Output Noise Volta<br>Volt.) (Note 11)          | ige (Fixed     | eno_fixed              | V <sub>IN</sub> = V <sub>OUT</sub> +0.5 V, V <sub>OUT</sub> (NOM) = 1V,<br>f = 10Hz to 100kHz                            |       | 60                    |      | μV <sub>RMS</sub> |

| Output Noise Voltage (Adj<br>devices) (Note 11) |                | eno_adj                | V <sub>IN</sub> = V <sub>OUT</sub> + 0.5V, f = 10Hz to<br>100kHz                                                         | 1     | 30 x<br>Vout/<br>VREF | -    | μVRMS             |

| Thermal Shutdown<br>Threshold                   |                | T <sub>SD</sub>        | Shutdown temperature                                                                                                     |       | 160                   |      | °C                |

| Thermal Shutdown<br>Hysteresis                  |                | ΔT <sub>SD</sub>       |                                                                                                                          |       | 20                    |      | °C                |

| Output Discharge<br>Pull- Down                  |                | RDISCH                 | V <sub>EN</sub> ≤ 0.4V, V <sub>OUT</sub> = 0.5V                                                                          |       | 150                   |      | Ω                 |

- **Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  = 77°C/W is measured under natural convection (still air) at  $T_A$  = 25°C with the component mounted on a high effective-thermal-conductivity four-layer test board on a JEDEC thermal measurement standard.

- Note 3.  $\theta_{JA}$  = 80°C/W is measured under natural convection (still air) at  $T_A$  = 25°C with the component mounted on a two-layer Richtek Evaluation Board.

- Note 4. Devices are ESD sensitive. Handling precaution is recommended.

- Note 5. The device is not guaranteed to function outside its operating conditions.

- Note 6. Adjustable devices tested at 0.5V; external resistor tolerance is not taken into account.

- **Note 7.** Performance guaranteed over the indicated operating temperature range by design and/or characterization. Production tested at  $T_A = 25$ °C. Low duty cycle pulse techniques are used during the testing to maintain the junction temperature as close to ambient as possible.

- Note 8. Dropout voltage is characterized when V<sub>OUT</sub> falls 3% below V<sub>OUT</sub>(Normal).

- Note 9. For output voltages below 0.9V, V<sub>BIAS</sub> dropout voltage does not apply due to a minimum Bias operating voltage of 3V.

- Note 10. For adjustable devices, VIN dropout voltage tested at V<sub>OUT(NOM)</sub> = 2 x V<sub>REF</sub>.

- Note 11. Guaranteed by design.

## **Typical Application Circuit**

Figure 1. Fixed Voltage Regulator

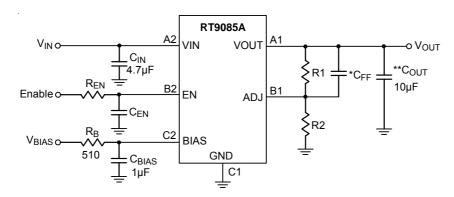

Figure 2. Adjustable Voltage Regulator

| Component         | Description           | Vendor P/N                                              |

|-------------------|-----------------------|---------------------------------------------------------|

| C <sub>BIAS</sub> | 1μF, 16V, X5R, 0402   | CGB2A1X5R1C105M033BC(TDK)<br>GRM155R61C105MA12D(Murata) |

| Cin               | 4.7μF, 10V, X5R, 0603 | C1608X5R1A475K080AE(TDK)<br>GRM155R61A475MEAA(Murata)   |

| **Соит            | 10μF, 6.3V, X5R, 0603 | GRM185R60J106ME15(Murata)<br>0603X106M6R3(WASLIN)       |

Table 1. Recommended External components

<sup>\*\*:</sup> Considering the effective capacitance derated with biased voltage level, the C<sub>OUT</sub> component needs satisfy the effective capacitance at least 4.7µF or above at targeted output level for stable and normal operation.

| V <sub>OUT</sub> (V) | <b>R1 (k</b> Ω) | <b>R2 (k</b> Ω) | * C <sub>FF</sub> (pF) |  |  |  |  |  |

|----------------------|-----------------|-----------------|------------------------|--|--|--|--|--|

| 0.75                 | 20              | 40              | 120                    |  |  |  |  |  |

| 1                    | 20              | 20              | 120                    |  |  |  |  |  |

| 1.8                  | 20              | 7.69            | 120                    |  |  |  |  |  |

| 2.5                  | 20              | 5               |                        |  |  |  |  |  |

**Table 2. Suggested Component Values**

<sup>\* :</sup> The feedforward capacitor C<sub>FF</sub> is optional for the optimization of transient response by increasing bandwidth and acceptable phase margin.

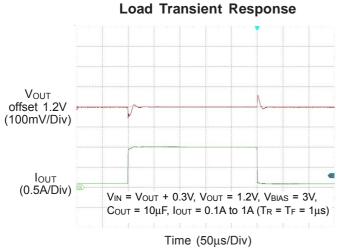

# **Typical Operating Characteristics**

Copyright ©2020 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9085A-04 December 2020 www.richtek.com

### **Application Information**

The RT9085A is a low voltage, low dropout linear regulator with input voltage  $V_{IN}$  from 0.8V to 5.5V,  $V_{BIAS}$  from 3V to 5.5V and adjusted output voltage from 0.5V to  $(V_{IN} - V_{DROP})$ . Keep  $V_{EN} < V_{BIAS} + 0.5V$  to prevent malfunction.

### **Output Voltage Setting**

For the RT9085A, the voltage on the ADJ pin sets the output voltage and is determined by the values of R1 and R2. The values of R1 and R2 can be calculated for any voltage using the formula given in Equation:

$$V_{OUT} = 0.5V \times \left(\frac{R1 + R2}{R2}\right)$$

Using lower values for R1 and R2 is recommended to reduces the noise injected from the ADJ pin. Note that R1 is connected from VOUT pin to ADJ pin, and R2 is connected from ADJ to GND.

#### **BIAS Pin Input**

The  $V_{BIAS}$  supply rail that powers the LDO control circuit sinks very low current (approximately the quiescent current of the LDO), which must be higher than 3V and ensure  $V_{BIAS} \ge V_{OUT} + 1.6V$  for normal operation.

#### **Dropout Voltage**

The dropout voltage refers to the voltage difference between the VIN and VOUT pins while operating at specific output current. The dropout voltage  $V_{DROP}$  also can be expressed as the voltage drop on the pass-FET at specific output current ( $I_{RATED}$ ) while the pass-FET is fully operating at ohmic region and the pass-FET can be characterized as an resistance  $R_{DS(ON)}$ . Thus the dropout voltage can be defined as ( $V_{DROP} = V_{IN} - V_{OUT} = R_{DS(ON)} \times I_{RATED}$ ). For normal operation, the suggested LDO operating range is ( $V_{IN} > V_{OUT} + V_{DROP}$ ) for good transient response and PSRR ability. Vice versa, while operating at the ohmic region will degrade the performance severely.

#### CIN and COUT Selection

The RT9085A is designed specifically to work with low ESR ceramic output capacitor for space saving and performance consideration. Using a ceramic capacitor with effective capacitance range from  $4.7\mu F$  to  $22\mu F$  on the RT9085A output ensures stability. The input capacitor must

be located at a distance of no more than 0.5 inch from the input pin of the chip. However, a capacitor with larger value and lower ESR (Equivalent Series Resistance) is recommended since it will provide better PSRR and line transient response. Any good quality ceramic capacitor can be used,  $C_{\text{IN}}$  = 4.7 $\mu\text{F}$  or greater is recommended.  $V_{\text{BIAS}}$  pin is suggested connecting with a 510 $\Omega$  resistor and  $C_{\text{BIAS}}$  = 1 $\mu\text{F}$  as a low-pass filter for good noise immunity.

#### Feedback Network with Feed-forward Capacitor

The feed-forward capacitor ( $C_{FF}$ ) introduced one zero and one pole within the feedback loop, which is optional for the optimization of transient response by increasing bandwidth and acceptable phase margin. The RT9085A is designed to be stable without the external feed-forward capacitor. However, an external feed-forward capacitor also can be used, adding a 120pF external feed-forward capacitor optimizes the transient, noise, and PSRR performances.

#### **Sequencing Requirements**

The RT9085A supports power on the input  $V_{IN}$ ,  $V_{BIAS}$ , and EN pins in any order without damage the device. However, for the output soft start procedure works as intended, it is mandatory to ensure  $V_{IN} \geq V_{OUT} + 0.1 V$  before  $V_{BIAS} \geq V_{OUT} + 1.6 V$ , the device enabled by  $V_{EN}$  ( $V_{EN} > V_{ENH}$ ) eventually. The BIAS pin supplies voltage for the LDO control circuit, and powering up  $V_{BIAS}$  first will ensure turn on time ( $t_{ON}$ ) and output voltage accuracy to follow datasheet spec.

Figure 3 also shows the use of an RC-delay circuit that hold off  $V_{EN}$  until  $V_{BIAS}$  has ramped up to target value. This technique can also be used to drive  $V_{EN}$  from  $V_{IN}$ . An external control signal can also be used to enable the device after  $V_{IN}$  and  $V_{BIAS}$  are present.

Figure 3. Soft-Start Delay Using an RC Circuit to Enable the Device

#### **Thermal Considerations**

The junction temperature should never exceed the absolute maximum junction temperature T<sub>J(MAX)</sub>, listed under Absolute Maximum Ratings, to avoid permanent damage to the device. The maximum allowable power dissipation depends on the thermal resistance of the IC package, the PCB layout, the rate of surrounding airflow, and the difference between the junction and ambient temperatures. The maximum power dissipation can be calculated using the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction-to-ambient thermal resistance.

For continuous operation, the maximum operating junction temperature indicated under Recommended Operating Conditions is 125°C. The junction-to-ambient thermal resistance,  $\theta_{JA}$ , is highly package dependent. For a WL-CSP-6B 0.8x1.2 (BSC) package, the thermal resistance, θ<sub>JA</sub>, is 77°C/W on a standard JEDEC high effective-thermalconductivity four-layer test board and the thermal resistance.  $\theta_{JA}$ , is 80°C/W on a two-layer Richtek evaluation board. The maximum power dissipation at  $T_A$  = 25°C can be calculated as below:

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (77^{\circ}C/W) = 1.29W$  for a standard JEDEC four-layer test board.

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (80^{\circ}C/W) = 1.25W$  for a two-layer Richtek evaluation board.

The maximum power dissipation depends on the operating ambient temperature for the fixed T<sub>J(MAX)</sub> and the thermal resistance,  $\theta_{JA}$ . The derating curves in Figure 4 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 4. Derating Curve of Maximum Power Dissipation

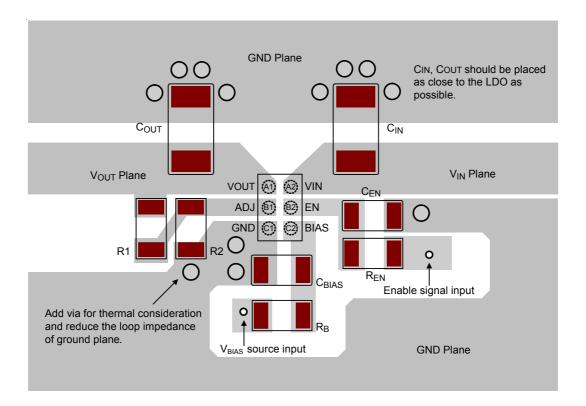

#### **Layout Considerations**

For best performance of the RT9085A, the PCB layout suggestions below are highly recommend.

- All circuit components placed on the same side and as near to the respective LDO pin as possible, place the ground return path connection to the input and output capacitor.

- The ground plane connected by a wide copper surface for good thermal dissipation.

- Using vias and long power traces for the input and output capacitors connection is discouraged and have negatively affects on performance.

Figure 5 shows an example for the layout reference that reduce conduction trace loop, helping inductive parasitic minimize, load transient reduction and good circuit stability.

Figure 5. PCB Layout Guide

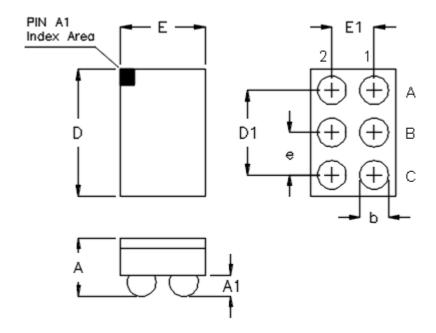

# **Outline Dimension**

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

| Symbol | Min          | Max           | Min                  | Max   |  |

| Α      | 0.500        | 0.600         | 0.020                | 0.024 |  |

| A1     | 0.170        | 0.230         | 0.007                | 0.009 |  |

| b      | 0.240        | 0.300         | 0.009                | 0.012 |  |

| D      | 1.160        | 1.240         | 0.046                | 0.049 |  |

| D1     | 0.800        |               | 0.0                  | )31   |  |

| E      | 0.760        | 0.840         | 0.030                | 0.033 |  |

| E1     | 0.400        |               | 0.016                |       |  |

| е      | 0.4          | 100           | 0.0                  | )16   |  |

6B WL-CSP 0.8x1.2 Package (BSC)

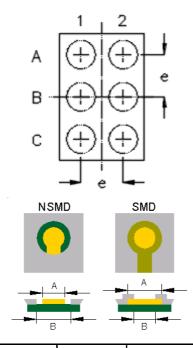

# **Footprint Information**

| Package              | Number of Type |      | Footprint Dimension (mm) |       |       | Tolerance |  |

|----------------------|----------------|------|--------------------------|-------|-------|-----------|--|

| 1 ackage             | Pin            | Туре | е                        | Α     | В     | Tolerance |  |

| WL-CSP0.8*1.2-6(BSC) | 6              | NSMD | 0.400                    | 0.240 | 0.340 | ±0.025    |  |

| WL-C3F0.6 1.2-0(B3C) | O              | SMD  | 0.400                    | 0.270 | 0.240 | ±0.025    |  |

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1 $^{\rm st}$  Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

RICHTEK

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.