# RT9471/D

# 3A Single Cell Switching Battery Charger

# 1 General Description

The RT9471/D is a highly-integrated 3A switch mode battery charge management, and system power path management device for single cell Li-lon and Li-Polymer batteries. The low impedance power path optimizes switch-mode operation efficiency, reduces battery charging time, and extends battery life during the discharging phase. The I<sup>2</sup>C serial interface with charging and system settings makes the device a truly flexible solution.

The recommended junction temperature range is  $-40^{\circ}$ C to 125°C, and the ambient temperature range is  $-40^{\circ}$ C to 85°C.

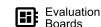

# 2 Ordering Information

### Note 1.

- Marked with <sup>(1)</sup> indicated: Empty means Pin 1 orientation is Quadrant 1.

- Marked with <sup>(2)</sup> indicated: Compatible with the current requirements of IPC/JEDEC J-STD-020.

- Marked with <sup>(3)</sup> indicated: Richtek products are Richtek Green Policy compliant.

# 3 Features

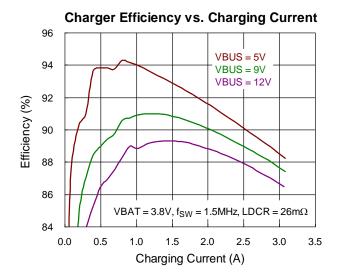

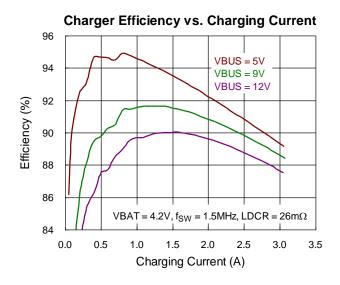

- High Efficiency, 1.5MHz, Synchronous Switch-Mode Buck Charger

- 92% Charge Efficiency at 2A with 5V Input and 3.8V Battery

- Support 3.9V to 13.5V Input Voltage Range

- Average Input Current Regulation (AICR)

- Minimum Input Voltage Regulation (MIVR)

- Minimum Input Voltage Regulation Track (MIVR Track)

- Charge Current Regulation (CCR)

- Charge Voltage Regulation (CVR)

- Charge Voltage Regulation Track (CVR Track)

- Junction Thermal Regulation (JTR)

- Supports USB On-The-Go (OTG)

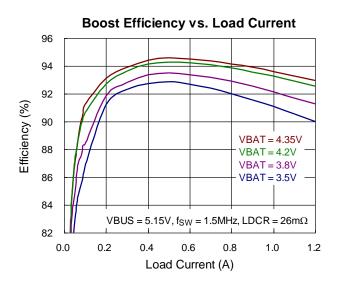

- 92% Boost Efficiency at 1A with 3.8V Battery and 5.15V Output

- OTG Current Limit Regulation (OCLR)

- OTG Voltage Limit Regulation (OVLR)

- Protection

- Over-Temperature Protection (OTP)

- VBUS Overvoltage Protection (VBUS OVP)

- Battery Overvoltage Protection (VBAT OVP)

- System Overvoltage Protection (VSYS OVP)

- System Undervoltage Protection (VSYS UVP)

- System Over-Load Protection (VSYS OLP)

- Cycle-by-Cycle Overcurrent Protection (OCP)

- OTG Low Battery Protection (OTG LBP)

# 4 Applications

- Smartphones/Tablet PCs

- Personal Information Appliances

- Portable Device and Accessory

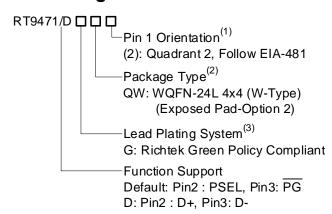

# 5 Simplified Application Circuit

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

RICHTEK

is a registered trademark of Richtek Technology Corporation.

# 6 Marking Information

8P=YM DNN

8P=: Product Code YMDNN: Date Code

8Q=: Product Code YMDNN: Date Code

# **Table of Contents**

| 1  | Gener  | ral Description1               | 15 | Applic | cation Information                 | 20 |

|----|--------|--------------------------------|----|--------|------------------------------------|----|

| 2  | Order  | ing Information1               |    | 15.1   | Power Up                           | 20 |

| 3  | Featu  | res1                           |    | 15.2   | Watchdog Timer (WDT)               | 23 |

| 4  | Applic | cations1                       |    | 15.3   | Power Path Management              | 23 |

| 5  | Simpl  | ified Application Circuit1     |    | 15.4   | Battery Charging Management        | 24 |

| 6  | Markii | ng Information2                |    | 15.5   | Status Outputs                     | 30 |

| 7  | Pin Co | onfiguration4                  |    | 15.6   | Protections                        | 31 |

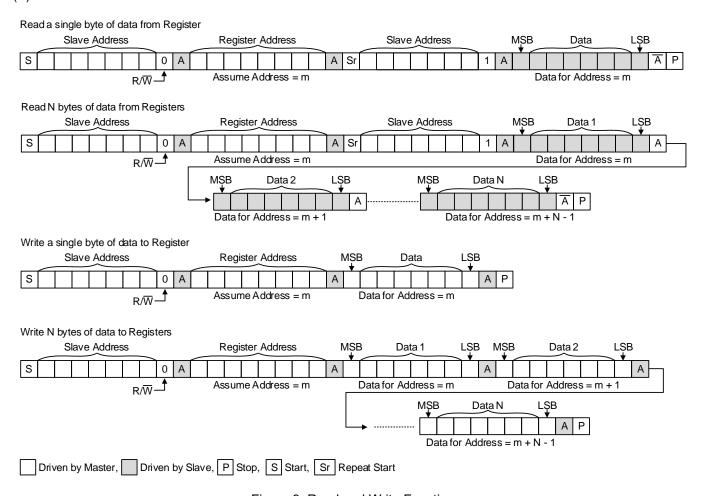

| 8  | Funct  | ional Pin Description4         |    | 15.7   | Communicate Interface              | 33 |

| 9  | Funct  | ional Block Diagram6           |    | 15.8   | Thermal Considerations             | 34 |

|    | 9.1    | For the RT94716                |    | 15.9   | Layout Considerations              | 34 |

|    | 9.2    | For the RT9471D7               | 16 | Funct  | ional Register Description         | 37 |

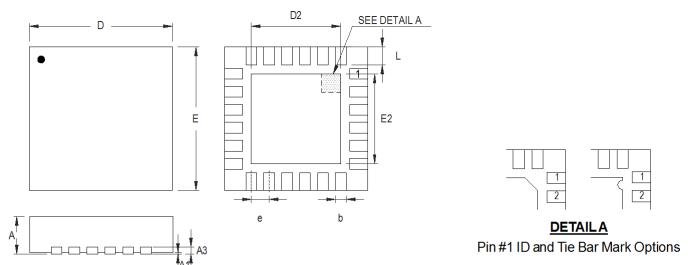

| 10 | Absol  | ute Maximum Ratings8           | 17 | Outlin | ne Dimension                       | 50 |

| 11 | Recor  | nmended Operating Conditions8  | 18 | Footp  | rint Information                   | 51 |

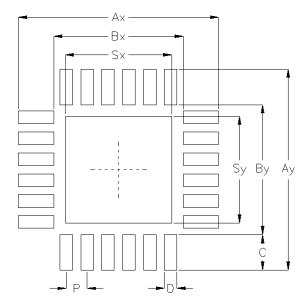

| 12 | Electr | ical Characteristics9          | 19 | Packi  | ng Information                     | 52 |

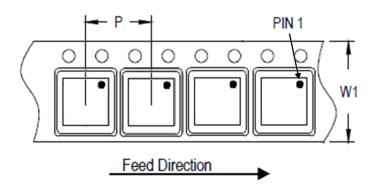

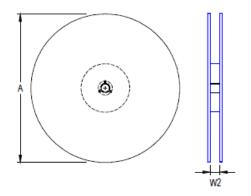

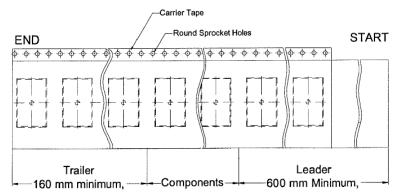

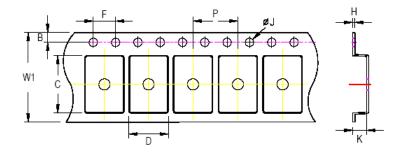

| 13 | Typica | al Application Circuit15       |    | 19.1   | Tape and Reel Data                 | 52 |

|    | 13.1   | For the RT947115               |    | 19.2   | Tape and Reel Packing              | 53 |

|    | 13.2   | For the RT9471D15              |    | 19.3   | Packing Material Anti-ESD Property | 54 |

| 14 | Typica | al Operating Characteristics17 | 20 | Datas  | heet Revision History              | 55 |

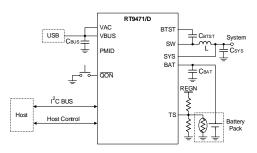

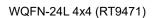

# 7 Pin Configuration

(TOP VIEW)

WQFN-24L 4x4 (RT9471D)

# **8 Functional Pin Description**

| Pin No. |         | Pin Name I/O |     | Pin Function                                                                                                                                                                                                                                              |

|---------|---------|--------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RT9471  | RT9471D | Pili Naille  | 1/0 | FinFunction                                                                                                                                                                                                                                               |

| 1       | 24      | VAC          | Al  | Input voltage sensing. This pin must be tied to VBUS.                                                                                                                                                                                                     |

| 2       |         | PSEL         | DI  | Power source selection input. A high level indicates a 0.5A input current limit, while a low level indicates a 2.4A input current limit. Once the device enters host mode, the host can program a different input current limit to the AICR register.     |

| 3       |         | PG           | DO  | Open-drain active-low power-good indicator. Connect the PG $\overline{\text{pin}}$ to a logic rail via a 2.2k $\Omega$ to 10k $\Omega$ resistor.                                                                                                          |

|         | 2       | D+           | AIO | Positive line of the USB data line pair. D+/D- based USB host/charging port detection includes data contact detection (DCD), primary detection, and secondary detection in BC1.2.                                                                         |

|         | 3       | D-           | AIO | Negative line of the USB data line pair. D+/D- based USB host/charging port detection includes data contact detection (DCD), primary detection, and secondary detection in BC1.2.                                                                         |

| 4       | 4       | STAT         | DO  | Open-drain charger status output. Connect the STAT pin to a logic rail via a 2.2k $\Omega$ to 10k $\Omega$ resistor. The STAT pin indicates the charger status.                                                                                           |

| 5       | 5       | SCL          | DI  | $\mbox{I}^2\mbox{C}$ interface clock. Connect SCL to the logic rail through a $10\mbox{k}\Omega$ resistor.                                                                                                                                                |

| 6       | 6       | SDA          | DIO | $\mbox{I}^2\mbox{C}$ interface clock. Connect SDA to the logic rail through a $10\mbox{k}\Omega$ resistor.                                                                                                                                                |

| 7       | 7       | ĪNT          | DO  | Open-drain active-low interrupt output. Connect the $\overline{\text{INT}}$ pin to a logic rail through a $10 \text{k}\Omega$ resistor. The $\overline{\text{INT}}$ pin sends an active-low pulse to the host to report charger device status and faults. |

| 8, 10   | 8, 10   | NC           |     | No internal connection.                                                                                                                                                                                                                                   |

| Pin No.  RT9471 RT9471D |                     | Pin Name I/O                                                           |    | Din Function                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|---------------------|------------------------------------------------------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                     | Pin Name                                                               | 2  | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9                       | 9                   | CE                                                                     | DI | Charge enable pin. When this pin is driven low, battery charging is enabled.                                                                                                                                                                                                                                                                                                                                      |

| 11                      | 11                  | TS AI resistor divider from suspends when the TS the TS pin is not use |    | Temperature qualification voltage input to support the JEITA profile. Connect a negative temperature coefficient thermistor. Program the temperature window with a resistor divider from REGN to TS to GND. Charging suspends when the TS pin voltage is out of range. When the TS pin is not used, connect a $10 \mathrm{k}\Omega$ resistor from REGN to TS and a $10 \mathrm{k}\Omega$ resistor from TS to GND. |

| 12                      | 12                  | QON                                                                    | DI | BATFET (Q4) enable control input. When BATFET is in ship mode, a logic low duration turns on BATFET (Q4) to exit shipping mode. When there is no VBUS, a logic low for tQON_RST turns off the BATFET for tBATFET_RST, and then re-enables BATFET to provide a system reset. Pull-High to the internal bias circuit via a $250 \mathrm{k}\Omega$ resistor.                                                         |

| 13, 14                  | 13, 14              | BAT                                                                    | Р  | Battery connection point to the positive terminal of the battery pack. The internal current sensing resistor is connected between SYS and BAT. Connect a $10\mu F$ capacitor closely to the BAT pin.                                                                                                                                                                                                              |

| 15, 16                  | 15, 16              | SYS                                                                    | Р  | Converter output connection point. The internal current sensing resistor is connected between SYS and BAT. Connect two $10\mu F$ capacitors closely to the SYS pin.                                                                                                                                                                                                                                               |

| 17, 18                  | 17, 18              | GND                                                                    | Р  | Power ground.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 19, 20                  | 19, 20              | SW                                                                     | Р  | Switching node connecting to the output inductor. Internally, SW is connected to the source of the high-side switching MOSFET (Q2) and the drain of the low-side switching MOSFET (Q3). Connect a 47nF bootstrap capacitor from SW to BTST.                                                                                                                                                                       |

| 21                      | 21                  | BTST                                                                   | Р  | PWM high-side driver positive supply. Internally, BTST is connected to the cathode of the bootstrap diode. Connect the 47nF bootstrap capacitor from SW to BTST.                                                                                                                                                                                                                                                  |

| 22                      | 22                  | REGN                                                                   | Ρ  | PWM low-side driver and internal supply output. Internally, REGN is connected to the anode of the bootstrap diode. Connect a $4.7\mu F$ capacitor from REGN to GND. The capacitor should be placed close to the IC.                                                                                                                                                                                               |

| 23                      | 23                  | PMID                                                                   | Р  | Connected to the drain of the reverse blocking MOSFET (Q1) and the drain of the high-side switching MOSFET (Q2). Connect a $10\mu F$ capacitor from PMID to GND.                                                                                                                                                                                                                                                  |

| 24                      | 1                   | VBUS                                                                   | Р  | Charger input voltage. The internal reverse block MOSFET (Q1) is connected between VBUS and PMID, with VBUS on the source. Connect a $1\mu F$ capacitor from VBUS to GND and place it as close as possible to the IC.                                                                                                                                                                                             |

| 25<br>(Exposed Pad)     | 25<br>(Exposed Pad) | Thermal Pad                                                            | Р  | Thermal pad and ground reference. The thermal pad must be connected to GND and well soldered to a large PCB copper area for maximum power dissipation.                                                                                                                                                                                                                                                            |

DS9471/D-04 May 2024 www.richtek.com

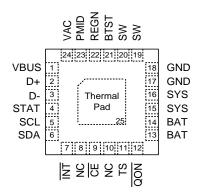

# 9 Functional Block Diagram

#### 9.1 For the RT9471

DS9471/D-04

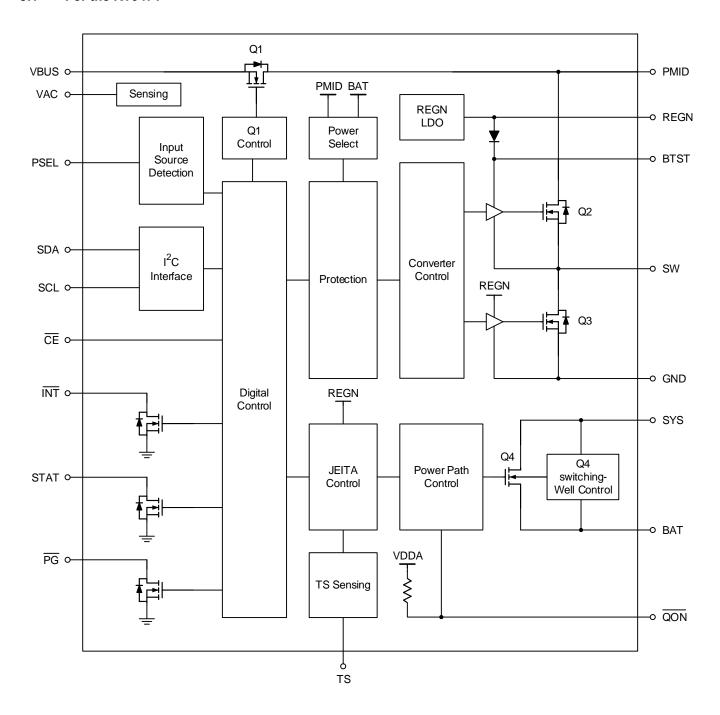

## 9.2 For the RT9471D

May 2024

DS9471/D-04

# 10 Absolute Maximum Ratings

## (Note 2)

| Voltage Sense Pin Voltage, VAC                               | 1.4V to 26V   |

|--------------------------------------------------------------|---------------|

| Supply Pin Voltage, VBUS                                     | -1.4V to 26V  |

| Terminal Pin Voltage, PMID                                   | 0.3V to 26V   |

| Terminal Pin Voltage, SW                                     | 0.3V to 16V   |

| Terminal Pin Voltage, BTST-SW                                | 0.3V to 6V    |

| Terminal Pin Voltage, SYS                                    | 0.3V to 6V    |

| Supply Pin Voltage, BAT                                      | 0.3V to 6V    |

| • Other Pins Voltage, STAT, SCL, SDA, INT, CE, TS, QON, REGN | 0.3V to 6V    |

| Other Pins Voltage for RT9471, PSEL, PG                      | 0.3V to 6V    |

| • Other Pins Voltage for RT9471D, D+, D-                     | 0.3V to 6V    |

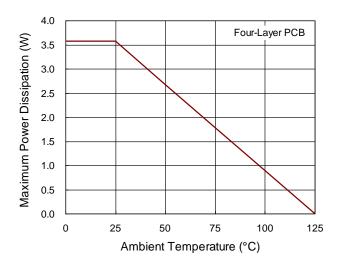

| <ul> <li>Power Dissipation, PD @ TA = 25°C</li> </ul>        |               |

| WQFN-24L 4x4                                                 | - 3.57W       |

| Package Thermal Resistance (Note 3)                          |               |

| WQFN-24L 4x4, θJA                                            | - 28°C/W      |

| WQFN-24L 4x4, θJC                                            | - 7.1°C/W     |

| • Lead Temperature (Soldering, 10 sec.)                      | - 260°C       |

| • Junction Temperature                                       | - 150°C       |

| Storage Temperature Range                                    | 65°C to 150°C |

| • ESD Susceptibility (Note 4)                                |               |

| HBM (Human Body Model)                                       | - 2kV         |

- Note 2. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 3. θJA is measured under natural convection (still air) at TA = 25°C with the component mounted on a high effective-thermalconductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.  $\theta_{JC}$  is measured at the top of the package.

- Note 4. Devices are ESD sensitive. Handling precautions are recommended.

# 11 Recommended Operating Conditions

## (Note 5)

| Voltage Sense Pin Voltage, VAC           | - 3.9V to 13.5V |

|------------------------------------------|-----------------|

| Supply Input Voltage Range, VBUS         | - 3.9V to 13.5V |

| Maximum Input Current, IBUS              | - 3.2A          |

| Maximum Input Current, IBUS (VBUS ≥ 12V) | - 2A            |

| Maximum Output Current (SW), ISYS        | - 3.2A          |

| Maximum Battery Voltage, VBAT            | - 4.7V          |

| Maximum Charge Current, IBAT             | - 3.15A         |

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

- Maximum Discharge Current, IBAT------ 6A

**Note 5**. The device is not guaranteed to function outside its operating conditions.

# 12 Electrical Characteristics

(VBUS\_MIN\_RISE < VAC < VAC\_OVP\_RISE and VAC > VBAT + VSLEEP\_RISE,  $T_J = -40^{\circ}C$  to 85°C, unless otherwise specified.) (Note 6)

| Parameter                                            | Symbol       | Test Conditions                                                                    | Min  | Тур  | Max  | Unit |  |

|------------------------------------------------------|--------------|------------------------------------------------------------------------------------|------|------|------|------|--|

| Quiescent Current                                    |              |                                                                                    |      |      |      |      |  |

| Battery Discharge<br>Current (BAT) in Q4<br>Disabled | IBAT_Q4_DIS  | VBAT = 4.5V, High-Z mode and I <sup>2</sup> C disabled, Q4 disabled                | 1    | 15   | 32   | μΑ   |  |

| Battery Discharge<br>Current (BAT) in Q4<br>Enable   | IBAT_Q4_EN   | $V_{BAT} = 4.5V$ , High-Z mode and $I^2C$ disabled, Q4 enabled                     |      | 55   | 85   | μА   |  |

| Input Supply Current                                 | Inuo 1117    | VBUS = 5V, High-Z mode and no battery                                              | 1    | 50   | 86   |      |  |

| (VBUS) in Buck Mode                                  | IBUS_HIZ     | V <sub>BUS</sub> = 12V, High-Z mode and no battery                                 | 1    | 52   | 88   | μΑ   |  |

| Input Supply Current (VBUS) in Buck Mode             | IBUS_BUCK    | VBUS > VBUS_MIN_RISE, VBUS > VBAT, converter switching, VBAT = 3.8V, ISYS = 0A     |      | 5    | 7    | mA   |  |

| Battery Discharge<br>Current (BAT) in Boost<br>Mode  | IBAT_BOOST   | V <sub>BAT</sub> = 4.2V, boost mode,<br>I <sub>BUS</sub> = 0A, converter switching |      | 4    | 5    | mA   |  |

| VAC, VBUS, and BAT Po                                | wer          |                                                                                    |      |      |      |      |  |

| VBUS Operating Range                                 | VBUS_OP      | V <sub>B</sub> U <sub>S</sub> rising                                               | 3.9  |      | 13.5 | V    |  |

| REGN Turn Off Level with Only VBUS                   | VBUS_UVLO    | V <sub>B</sub> us falling                                                          | 3.0  | 3.3  | 3.6  | V    |  |

| Sleep Mode Falling<br>Threshold                      | VSLEEP_FALL  | VAC falling, VAC – VBAT                                                            | 10   | 60   | 120  | mV   |  |

| Sleep Mode Rising<br>Threshold                       | VSLEEP_RISE  | VAC rising, VAC – VBAT                                                             | 160  | 250  | 340  | mV   |  |

| VAC 5.65V Overvoltage<br>Rising Threshold            |              | VAC rising                                                                         | 5.4  | 5.65 | 5.9  |      |  |

| VAC 6.35V Overvoltage<br>Rising Threshold            | ]<br>        | VAC rising                                                                         | 6.1  | 6.35 | 6.6  |      |  |

| VAC 10.8V Overvoltage<br>Rising Threshold            | VAC_OVP_RISE | VAC rising                                                                         | 10.3 | 10.8 | 11.5 | V    |  |

| VAC 14V Overvoltage<br>Rising Threshold              |              | VAC rising                                                                         | 13.3 | 14   | 14.7 |      |  |

RICHTEK

is a registered trademark of Richtek Technology Corporation.

DS9471/D-04 May 2024

| Parameter                                                                | Symbol         | Test Conditions                                                  | Min          | Тур            | Max  | Unit |  |

|--------------------------------------------------------------------------|----------------|------------------------------------------------------------------|--------------|----------------|------|------|--|

| VAC 5.65V Overvoltage<br>Hysteresis                                      |                | Vac falling                                                      |              | 300            |      |      |  |

| VAC 6.35V Overvoltage<br>Hysteresis                                      | VAC OVE UVO    | VAC falling                                                      |              | 300            |      | - mV |  |

| VAC 10.8V Overvoltage<br>Hysteresis                                      | VAC_OVP_HYS    | Vac falling                                                      |              | 300            |      | IIIV |  |

| VAC 14V Overvoltage<br>Hysteresis                                        |                | Vac falling                                                      |              | 300            |      |      |  |

| BAT for Active I <sup>2</sup> C, No<br>Adapter                           | VBAT_UVLO      | VBAT rising                                                      | 1.85         | 2.2            | 2.45 | ٧    |  |

| Battery Depletion Falling<br>Threshold                                   | VBAT_DPL_FALL  | VBAT falling                                                     | 2.15         | 2.38           | 2.65 | V    |  |

| Battery Depletion Rising<br>Threshold                                    | VBAT_DPL_RISE  | VBAT rising                                                      | 2.4          | 2.6            | 2.8  | V    |  |

| Battery Depletion Rising<br>Hysteresis                                   | VBAT_DPL_HYS   | VBAT rising                                                      |              | 220            |      | mV   |  |

| Bad Adapter Detection<br>Rising Threshold                                | VBUS_MIN_RISE  | V <sub>B</sub> us rising                                         | 3.5          | 3.7            | 3.9  | V    |  |

| Bad Adapter Detection<br>Hysteresis                                      | VBUS_MIN_HYS   | VBus falling                                                     |              | 210            |      | mV   |  |

| Bad Adapter Detection<br>Current Source                                  | IBADSRC        | Sink current from V <sub>BUS</sub> to GND                        |              | 50             |      | mA   |  |

| Power Path                                                               |                |                                                                  |              |                |      |      |  |

| System Regulation                                                        | VSYS_MIN       | VBAT < VSYS_MIN = 3.5V, Q4 disabled/enable                       | 3.5          | 3.5<br>+ 0.2   |      |      |  |

| Voltage                                                                  | Vsys           | Isys = 0A, VBAT > VSYS_MIN = 3.5V,<br>Q4 disabled                |              | VBAT<br>+ 0.06 |      | V    |  |

| Top Reverse Blocking<br>MOSFET On-Resistance<br>Between VBUS and<br>PMID | Ron(Q1)        |                                                                  |              | 28             |      | mΩ   |  |

| Top Switching MOSFET<br>On-Resistance Between<br>PMID and SW             | Ron(Q2)        | VREGN = 5V                                                       |              | 42             |      | mΩ   |  |

| Bottom Switching<br>MOSFET On-Resistance<br>Between SW and GND           | Ron(Q3)        | VREGN = 5V                                                       |              | 44             |      | mΩ   |  |

| SYS-BAT MOSFET On-<br>Resistance                                         | RON(BAT-SYS)   | Measured from BAT to SYS,<br>VBAT = 4.2V                         |              | 18             | 25   | mΩ   |  |

| Battery Charger                                                          |                |                                                                  |              |                |      |      |  |

| Charge Voltage Range                                                     | VBAT_REG_RANGE | Default = 4.2V                                                   | 3.9          |                | 4.7  | V    |  |

| Charge Voltage Step                                                      | VBAT_REG_STEP  |                                                                  |              | 10             |      | mV   |  |

| Charge Voltage Setting Accuracy                                          | VBAT_REG_ACC   | $T_J = 25^{\circ}C$ $T_J = -40^{\circ}C \text{ to } 85^{\circ}C$ | -0.4<br>-0.8 |                | 0.4  | %    |  |

| Charge Current Regulation Range                                          | ICHG_REG_RANGE | Default = 2000mA                                                 | 0            |                | 3150 | mA   |  |

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

| Parameter                                    | Symbol                | Test Conditions                                  | Min  | Тур  | Max  | Unit |  |

|----------------------------------------------|-----------------------|--------------------------------------------------|------|------|------|------|--|

| Charge Current<br>Regulation Step            | ICHG_REG_STEP         |                                                  |      | 50   |      | mA   |  |

|                                              |                       | VBAT = 3.8V, ICHG_REG = 50mA                     | 30   |      | 75   |      |  |

|                                              |                       | VBAT = 3.8V, ICHG_REG = 100mA                    | 70   |      | 135  |      |  |

| Charge Current Regulation Accuracy           | ICHG_REG_ACC          | VBAT = 3.8V, ICHG_REG = 600mA                    | 540  |      | 660  | mA   |  |

| r togulation / toouraby                      |                       | VBAT = 3.8V, ICHG_REG = 1300mA                   | 1235 |      | 1365 |      |  |

|                                              |                       | VBAT = 3.8V, ICHG_REG = 1500mA                   | 1425 |      | 1575 |      |  |

| Pre-Charge Falling<br>Threshold              | VPRE_CHG_FALL         | ICHG = 200mA, VPRE_CHG = 3.1V                    | 2.75 | 2.9  | 3.05 | V    |  |

| Pre-Charge Rising<br>Threshold               | VPRE_CHG_RISE         | Pre-charge to fast charge,<br>VPRE_CHG = 3.1V    | 2.95 | 3.1  | 3.25 | V    |  |

| Pre-Charge Current<br>Range                  | IPRE_CHG_RANGE        | Default = 150mA                                  | 50   |      | 800  | mA   |  |

| Pre-Charge Current Step                      | IPRE_CHG_STEP         |                                                  |      | 50   |      | mA   |  |

| Pre-Charge Accuracy                          | IPRE_CHG_ACC          | VBUS = 5V, IPRE_CHG = 150mA                      | 100  |      | 200  | mA   |  |

| End-Of-Charge Current<br>Range               | IEOC_CHG_RANGE        | Default = 200mA                                  | 50   |      | 800  | mA   |  |

| End-Of-Charge Current<br>Step                | IEOC_CHG_STEP         |                                                  |      | 50   |      | mA   |  |

|                                              | y IEOC_CHG_ACC        | ICHG_REG > 700mA, IEOC_CHG = 200mA, VBAT = 4.2V  | 160  |      | 240  | mA   |  |

| End-Of-Charge Accuracy                       |                       | ICHG_REG ≤ 700mA, IEOC_CHG = 200mA, VBAT = 4.2V  | 175  |      | 225  |      |  |

|                                              |                       | ICHG_REG = 600mA, IEOC_CHG = 50mA, VBAT = 4.2V   | 37.5 |      | 62.5 |      |  |

| Trickle-Charge Falling<br>Threshold          | VTRICKLE_CHG_<br>FALL | VBAT falling                                     | 1.8  | 2    | 2.2  | ٧    |  |

| Trickle-Charge Rising<br>Threshold           | VTRICKLE_CHG_<br>RISE | VBAT rising                                      | 2.05 | 2.25 | 2.45 | V    |  |

| Trickle-Charge Current                       | ITRICKLE_CHG          | VBAT < VTRICKLE_CHG_RISE                         | 70   | 100  | 135  | mA   |  |

| Re-Charge Threshold                          | N==                   | VBAT falling, VRECHG = 100mV                     | 60   | 100  | 140  | >/   |  |

| Below VBAT_REG                               | VRE_CHG               | VBAT falling, VRECHG = 200mV                     | 160  | 200  | 240  | mV   |  |

| System Discharge Load<br>Current             | ISYS_LOAD             | Vsys = 4.2V                                      |      | 30   |      | mA   |  |

| Input Voltage and Curre                      | nt Regulation         |                                                  | •    |      | •    | •    |  |

| Minimum Input Voltage<br>Regulation Range    | VMIVR_RANGE           | Default = 4.5V                                   | 3.9  |      | 5.4  | V    |  |

| Minimum Input Voltage<br>Regulation Step     | VMIVR_STEP            |                                                  |      | 100  |      | mV   |  |

| Minimum Input Voltage<br>Regulation Accuracy | VMIVR_ACC             | VMIVR = 3.9V and 4.5V                            | -1.5 |      | 1.5  | %    |  |

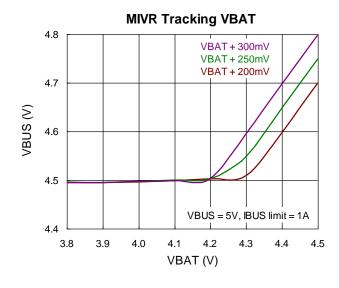

| MIVR Tracking VBAT                           | VMIVR_BAT_TRACK       | VMIVR = 3.9V, VMIVR_BAT_TRACK = 300mV, VBAT = 4V |      | 4.3  |      | V    |  |

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

| Parameter                                                 | Symbol                  | Test Conditions                                  | Min  | Тур  | Max  | Unit |  |

|-----------------------------------------------------------|-------------------------|--------------------------------------------------|------|------|------|------|--|

| MIVR Tracking VBAT<br>Accuracy                            | VMIVR_BAT_TRACK<br>_ACC |                                                  | -3   |      | 3    | %    |  |

| Average Input Current Regulation Range                    | IAICR_RANGE             | Default = 0.5A                                   | 0.05 |      | 3.2  | Α    |  |

| Average Input Current Regulation Step                     | IAICR_STEP              |                                                  |      | 50   |      | mA   |  |

|                                                           |                         | VBUS = 5V, IAICR = 500mA                         | 450  |      | 500  |      |  |

| Average Input Current Regulation Accuracy                 | IAICR_ACC               | V <sub>BUS</sub> = 5V, I <sub>AICR</sub> = 900mA | 780  |      | 900  | mA   |  |

|                                                           |                         | VBUS = 5V, IAICR = 1500mA                        | 1300 |      | 1500 |      |  |

| <b>BAT Overvoltage Protec</b>                             | tion                    |                                                  |      |      |      |      |  |

| Battery Overvoltage<br>Rising                             | VBAT_OVP_RISE           | VBAT rising, as percentage of VBAT_REG           | 103  | 104  | 105  | %    |  |

| Battery Overvoltage Falling                               | VBAT_OVP_FALL           | VBAT falling, as percentage of VBAT_REG          | 101  | 102  | 103  | %    |  |

| Input Reverse Blocking                                    | NFET and Regulati       | on                                               |      |      |      |      |  |

| Junction Thermal<br>Regulation Range                      | TJ_THREG_RANGE          | Default = 120°C                                  | 100  |      | 120  | °C   |  |

| Junction Thermal<br>Regulation Step                       | TJ_THREG_STEP           |                                                  |      | 20   |      | °C   |  |

| Thermal Shutdown<br>Rising                                | Тотр                    | Temperature rising                               |      | 160  |      | °C   |  |

| Thermal Shutdown<br>Hysteresis                            | TOTP_HYS                | Temperature falling                              |      | 30   |      | °C   |  |

| NTC Monitor (Charger M                                    | ode)                    |                                                  |      |      |      |      |  |

| Battery Temperature<br>COLD Threshold (0°C)               | VVTS_COLD               | VTS rising, the ratio of VREGN                   | 72.5 | 73.5 | 74.5 | %    |  |

| Battery Temperature<br>COOL Threshold (10°C)              | VVTS_COOL               | VTS rising, the ratio of VREGN                   | 67.5 | 68.5 | 69.5 | %    |  |

| Battery Temperature<br>WARM Threshold (45°C)              | VVTS_WARM               | VTS falling, the ratio of VREGN                  | 44   | 45   | 46   | %    |  |

| Battery Temperature<br>HOT Threshold (60°C)               | Vvts_hot                | VTS falling, the ratio of VREGN                  | 33.5 | 34.5 | 35.5 | %    |  |

| Battery Temperature<br>Hysteresis                         | VVTS_HYS                |                                                  |      | 1.5  |      | %    |  |

| NTC Monitor (OTG Mode)                                    |                         |                                                  |      |      |      |      |  |

| Battery Temperature<br>COLD Threshold OTG<br>mode (-20°C) | Vvts_cold_otg           | VTS rising, the ratio of VREGN                   | 79   | 80   | 81   | %    |  |

| Battery Temperature<br>HOT Threshold OTG<br>mode (60°C)   | Vvts_hot_otg            | VTS falling, the ratio of VREGN                  | 33.5 | 34.5 | 35.5 | %    |  |

| Battery Temperature<br>Hysteresis OTG mode                | VVTS_HYS_OTG            |                                                  |      | 1.5  |      | %    |  |

RT9471/D

| Parameter                                     | Symbol           | Test Conditions                           | Min  | Тур     | Max  | Unit                |

|-----------------------------------------------|------------------|-------------------------------------------|------|---------|------|---------------------|

| Charger Overcurrent Th                        | reshold          |                                           |      |         |      |                     |

| UGFET Cycle-by-Cycle<br>Overcurrent Threshold | IOCP_UG          |                                           | 4.9  | 6.6     | 8.2  | А                   |

| System Over-Load<br>Threshold                 | IOCP_BATFET      |                                           | 5.8  |         |      | А                   |

| USB On-The-Go (OTG)                           |                  |                                           |      |         |      |                     |

|                                               |                  | VBAT falling, VOTG_LBP = 2.8V             | 2.65 | 2.8     | 2.95 |                     |

| OTG Low Battery                               | Voza 155         | VBAT rising, VOTG_LBP = 2.8V              | 2.75 | 2.9     | 3.05 | $  $ $_{\vee} $ $ $ |

| Protection                                    | VOTG_LBP         | VBAT falling, VOTG_LBP = 2.5V             | 2.35 | 2.5     | 2.65 | ]                   |

|                                               |                  | VBAT rising, VOTG_LBP = 2.5V              | 2.45 | 2.6     | 2.75 |                     |

| OTG Voltage Limit<br>Regulation Range         | VOTG_CV_RANGE    | Default = 5.15V                           | 4.85 |         | 5.3  | V                   |

| OTG Voltage Limit<br>Regulation Step          | VOTG_CV_STEP     |                                           |      | 150     |      | mV                  |

| OTG Voltage Limit<br>Regulation Accuracy      | VOTG_CV_ACC      | VBAT = 3.8V, IPMID = 0A, VOTG_REG = 5.15V | -3   |         | 3    | %                   |

| OTG Current Limit                             | Іотд_сс          | IOTG_LIMIT_REG_SEL = 1.2A                 | 1.2  | 1.4     | 1.6  | ۸                   |

| Regulation Accuracy                           |                  | IOTG_LIMIT_REG_SEL = 0.5A                 | 0.5  | 0.6     | 0.7  | Α                   |

| OTG Overvoltage<br>Threshold                  | VOTG_OVP         | VAC rising, VAC_OVP = 6.35V               | 6.1  | 6.35    | 6.6  | V                   |

| PWM                                           |                  |                                           |      |         |      |                     |

| PWM Switching                                 | fsw_buck         | Oscillator frequency, buck mode           | 1350 | 1500    | 1650 | kHz                 |

| Frequency                                     | fsw_boost        | Oscillator frequency, boost mode          | 1350 | 1500    | 1650 | KI IZ               |

| Maximum PWM Duty<br>Cycle                     | DMAX             |                                           | -    | 97      |      | %                   |

| REGN                                          |                  |                                           |      |         |      |                     |

| REGN LDO Output                               | VREGN            | VBUS = 9V, IREGN = 40mA                   | 4.5  | 4.9 5.3 |      | V                   |

| Voltage                                       | VICEON           | VBUS = 5V, IREGN = 20mA                   | 4.5  | 4.9     | 5    | V                   |

| Control I/O Pin (CE, PSE                      | L, SCL, and SDA) |                                           |      |         |      |                     |

| Input High Threshold<br>Voltage               | VIH_CTRL         |                                           | 1.3  |         |      | V                   |

| Input Low Threshold<br>Voltage                | VIL_CTRL         |                                           |      |         | 0.4  | V                   |

| High Level Leakage<br>Current                 | IBIAS            | Pull high to 1.8V                         |      |         | 1    | μА                  |

| Control I/O Pin (PG, STA                      | T, and INT)      |                                           |      |         |      |                     |

| Output Low Threshold Voltage                  | VOL_CTRL         |                                           |      |         | 0.4  | V                   |

| INT Pull Low Time                             | tINT_PULL_LOW    | INT pull low time                         | 1    | 256     |      | μS                  |

| D+/D- Detection                               |                  |                                           |      |         |      |                     |

| Data Detect Voltage                           | VDAT_REF         |                                           | 0.25 | 0.325   | 0.4  | V                   |

| D- Current Sink                               | IDISNK           |                                           | 50   | 100     | 150  | μА                  |

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

DS9471/D-04 May 2024 www.richtek.com

| Parameter                                          | Symbol                | Test Conditions    | Min   | Тур   | Max  | Unit  |  |

|----------------------------------------------------|-----------------------|--------------------|-------|-------|------|-------|--|

| D+D- Leakage Current                               | ID+DLKG               |                    | -1    |       | 1    | μΑ    |  |

| D- Pulldown for<br>Connection Check                | RD19K                 |                    | 14.25 | 19.53 | 24.8 | kΩ    |  |

| D+D- Threshold for Non-<br>Standard Adapter (1.2V) | VD+D1P2               |                    |       | 1.2   |      | V     |  |

| D+D- Threshold for Non-<br>Standard Adapter (2.0V) | VD+D2P0               |                    |       | 2     |      | V     |  |

| D+D- Threshold for Non-<br>Standard Adapter (2.8V) | VD+D2P8               |                    |       | 2.8   |      | V     |  |

| Timing Requirements                                |                       |                    |       |       |      |       |  |

| VAC OVP Reaction Time                              | tVAC_OVP              | (Note 6)           |       | 200   |      | ns    |  |

| Bad Adapter Detection<br>Duration                  | tBAD_AD_<br>DETECTION |                    |       | 30    |      | ms    |  |

| Deglitch Time for Charger EOC                      | tEOC_DGL              |                    |       | 256   |      | ms    |  |

| Deglitch Time for Re-<br>Charge                    | tre_chg_dgl           |                    |       | 256   |      | ms    |  |

| Charge Safe Timer                                  | tCHG_SAFE_TMR         | Timer = 10hr       | 9     | 10    | 11   | hr    |  |

| Back-Ground Charge<br>Timer                        | tBG_CHG_TMR           | Timer = 30min      | 29    | 30    | 31   | min   |  |

| QON Timing                                         |                       |                    |       |       |      |       |  |

| QON Low Time to Exit<br>Shipping Mode              | tshipmode_exit        |                    | 0.9   | 1.1   | 1.3  | s     |  |

| QON Low Time to Reset<br>System                    | tQON_RST              |                    | 9     | 10    | 11   | s     |  |

| BATFET Reset Time                                  | tBATFET_RST           |                    | 430   | 453   | 480  | ms    |  |

| Enter Shipping Mode<br>Delay Time                  | tship_mode_<br>enter  |                    | 11    | 12    | 13   | S     |  |

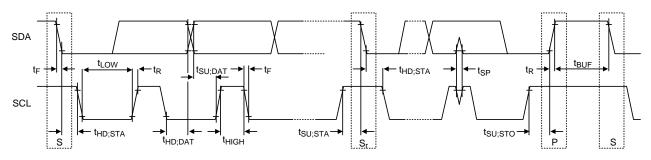

| I <sup>2</sup> C Clock and Watchdog Timer          |                       |                    |       |       |      |       |  |

| SCL Clock                                          | fect                  | CB ≤ 100pF         |       |       | 3.4  | MHz   |  |

|                                                    | fscl 1                | 100pF < CB ≤ 400pF |       |       | 1.7  | IVIMZ |  |

| Watchdog Timer                                     | twdt                  | Default = 40s      |       | 40    |      | s     |  |

| Watchdog Reset Wait<br>Time                        | twdt_wait             |                    |       | 500   |      | ms    |  |

Note 6. Specification is guaranteed by design and/or correlation with statistical process control.

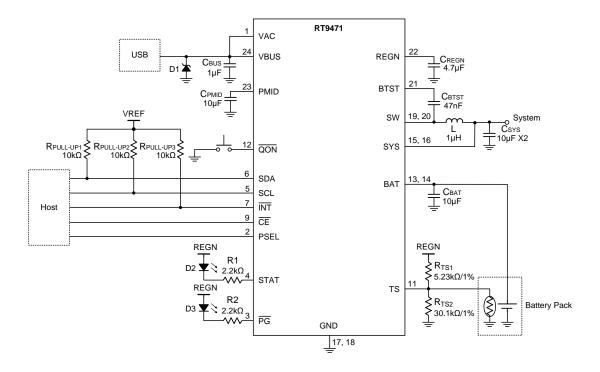

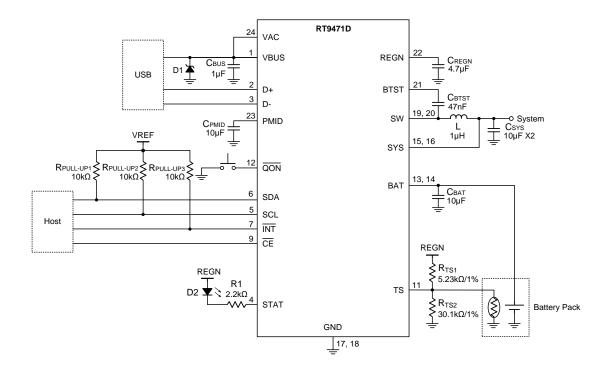

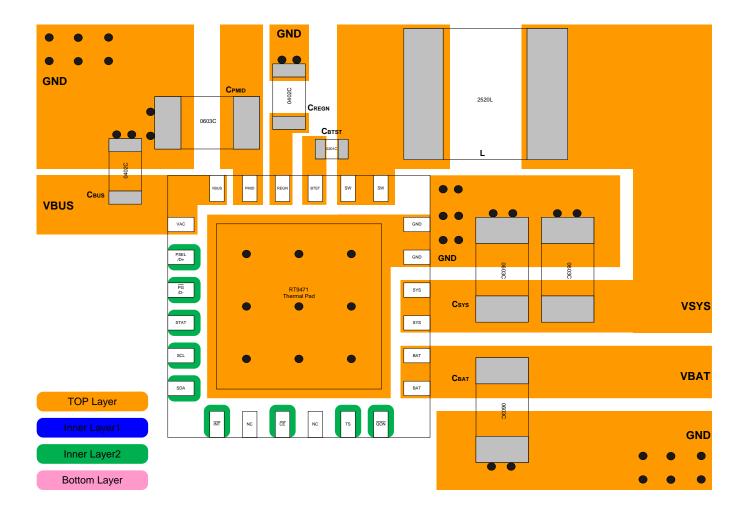

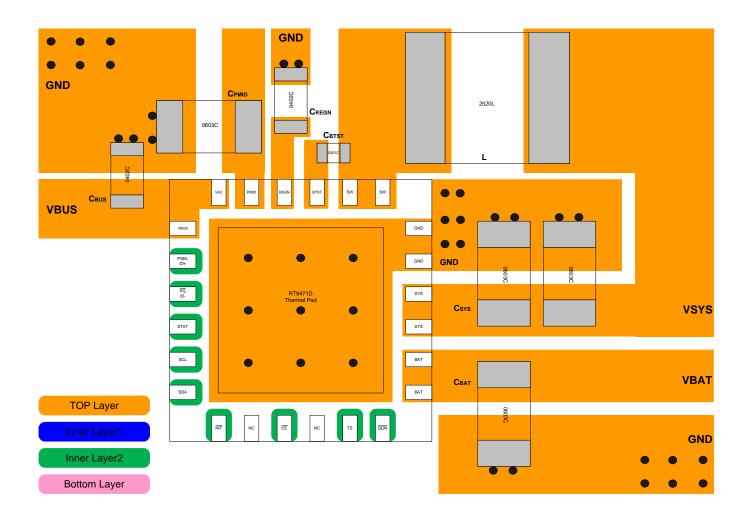

# 13 Typical Application Circuit

#### 13.1 For the RT9471

(Refer to Table 2 for PSEL Detect Setting Result)

#### 13.2 For the RT9471D

(Refer to Table 3 for D+/D- Detect Setting Result)

RICHTEK

May 2024

DS9471/D-04

# **Table 1. Recommended Components Information**

| Name  | Part Number        | Description    | Package           | Manufacturer |

|-------|--------------------|----------------|-------------------|--------------|

| CBUS  | GRM155R61E105KA12  | 1μF/25V/X5R    | 0402              | muRata       |

| СРМІО | GRM188R61E106MA73  | 10μF/25V/X5R   | 0603              | muRata       |

| Свтѕт | GRM033R61C473KE84  | 47nF/16V/X5R   | 0201              | muRata       |

| Csys  | GRM185R60J106ME15  | 10μF/6.3V/X5R  | 0603              | muRata       |

| Сват  | GRM185R60J106ME15  | 10μF/6.3V/X5R  | 0603              | muRata       |

| CREGN | GRM155R60J475ME47  | 4.7μF/6.3V/X5R | 0402              | muRata       |

| L     | CIGT252010EH1R0MNE | 1μΗ/20%        | 2.5 x 2.0 x 1.0mm | Samsung      |

| D1    | PTVSHC3N12VU       | TVS Diode      | DFN2x2-3L         | Prisemi      |

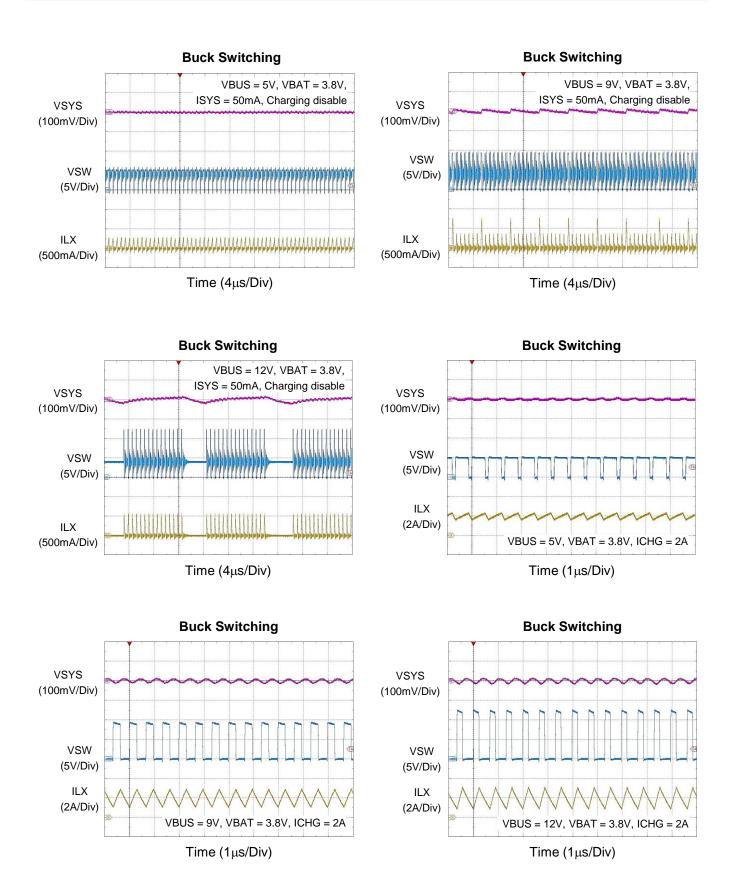

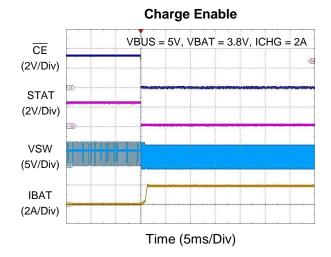

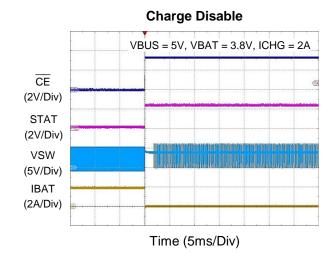

# 14 Typical Operating Characteristics

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

RICHTEK

is a registered trademark of Richtek Technology Corporation.

DS9471/D-04 May 2024 www.richtek.com

DS9471/D-04

eserved. RICHTEK

is a registered trademark of Richtek Technology Corporation.

Copyright © 2024 Richtek Technology Corporation. All rights reserved.

DS9471/D-04 May 2024 www.richtek.com

# 15 Application Information

(Note 7)

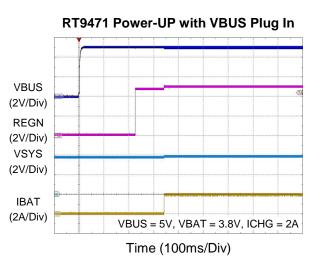

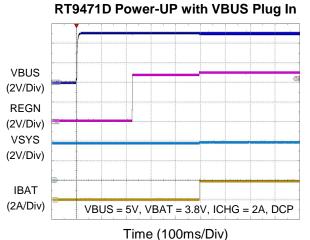

#### 15.1 **Power Up**

#### 15.1.1 Power-On-Reset (POR)

Upon power-up, the device initiates its internal bias circuits using the higher voltage sources: VBUS or VBAT. The Power-On-Reset sequence begins when VBUS exceeds 1.8V, or when VBAT rises above VBAT UVLO. Once the POR sequence starts, the I<sup>2</sup>C interface becomes operational, allowing for communication. Simultaneously, all registers are reset to the default values.

#### Device Power Up from Battery Only 15.1.2

When a battery is connected and the voltage at VBAT exceeds the threshold VBAT\_DPL\_RISE, the BATFET is activated. The activation connects VBAT to VSYS. The REGN stays off to minimize the quiescent current. The low quiescent current on VBAT and the low RDS(ON) of the BATFET reduce the device power consumption and conduction losses, thereby extending the battery life.

The device continuously monitors the discharge current passing through the BATFET in Battery Supply Mode. If the system experiences an overload or a short circuit condition (IBAT > IBATFET OCP), the device immediately deactivates the BATFET and sets BATFET\_DIS = 1. This action initiates Shipping Mode, which persists until VBUS is reconnected or specific procedures are followed to exit Shipping Mode to reactivate the BATFET.

#### **Device Power Up from VBUS** 15.1.3

When VBUS is connected, the device initiates the power-up sequence as follows:

- 1. Activate the REGN LDO.

- 2. Initiate Poor Source Detection.

- 3. Determine PORT\_STAT based on PSEL or the type of input source, and configure the default setting of the Average Input Current Regulation (AICR) register.

- 4. Set the Minimum Input Voltage Regulation (MIVR) setting.

- 5. Engage the Buck Converter.

#### 15.1.4 Power-Up REGN LDO

The REGN LDO provides power to the gate drives of both high-side and low-side MOSFETs. Additionally, it supplies bias to the external TS resistor and the pull-up rail for the STAT pin. The REGN is activated under the following conditions:

- 1. VAC exceeds VBAT + VSLEEP\_RISE in buck mode, or the OTG bit is set in boost mode.

- 2. After a delay of 220ms, VAC remains above VBAT + VSLEEP RISE.

- 3. The REGN LDO is deactivated when the device enters HZ mode, sleep mode, experiences VBUS overvoltage, or when OTG is disabled.

### 15.1.5 Poor Source Detection

After REGN is powered up, the device evaluates the current capability of the input source. The input source must meet the following requirements to enable the buck converter.

- VBUS must be below the VAC\_OVP\_RISE threshold.

- 2. VBUS must be above the VBUS\_BAD\_ADP threshold, which then triggers the device to pull IBADSRC (typical = 40mA).

When the input source satisfies these conditions, the ST\_VBUS\_GD and the FL\_VBUS\_GD signals go high, and the device generates a pulse on the  $\overline{\text{INT}}$  pin to trigger an interrupt on the host. If ST\_VBUS\_GD does not go high, the device will retry the poor source detection process every 2 seconds.

## 15.1.6 VBUS Source Type Detection

After ST\_VBUS\_GD goes high, the device initiates VBUS source type detection (for the RT9471D) or checks the status of the PSEL pin (for the RT9471). After the detection process is completed, both ST\_CHG\_RDY and FL\_CHG\_RDY signals turn to high, and the INT pin pulsed to interrupt the host system.

Then the following registers are changed:

- 1. The Average Input Current Regulation (AICR) register is automatically changed to the result of the VBUS source type detection or the PSEL pin status, provided that AUTO\_AICR = 1.

- 2. The PORT\_STAT bit is revised to indicate the detected VBUS source type.

### 15.1.7 Average Input Current Regulation (AICR)

The charger input current is limited by the AICR register with a range from 50mA to 3.2A and a resolution 50mA.

- If the AUTO\_AICR bit is set to 0, the device cannot adjust the AICR value automatically after detecting the VBUS source type.

- The host can overwrite the AICR register to set a new input current limit.

- For the RT9471, the PSEL value updates the AICR settings. In the RT9471D, the AICR is updated according to <a href="Table 2">Table 2</a> or based on D+/D- line detection (including standard USB BC 1.2). Refer to <a href="Table 3">Table 3</a>.

- In the RT9471, the AICR is updated in real-time with changes to the PSEL value.

- In the RT9471D, the AICR is updated by the D+/D- detection value after BC12\_EN is disabled and then re-enabled, or when VBUS is reconnected.

**Table 2. AICR Setting from PSEL**

| PSEL Pin | AICR Setting | PORT_STAT |

|----------|--------------|-----------|

| High     | 0.5 A        | 1101      |

| Low      | 2.4 A        | 1111      |

RICHTEK is a registered trademark of Richtek Technology Corporation.

Table 3. AICR Setting from D+/D- Detection

| Detection    | AICR Setting | PORT_STAT |

|--------------|--------------|-----------|

| Device 1     | 2.1A         | 1000      |

| Device 2     | 2A           | 1001      |

| Device 3     | 1A           | 1010      |

| Device 4     | 2.4A         | 1011      |

| Unknown/NSDP | 0.5A         | 1100      |

| SDP          | 0.5A         | 1101      |

| CDP          | 1.5A         | 1110      |

| DCP          | 2.4A         | 1111      |

# 15.1.8 Minimum Input Voltage Regulation (MIVR)

The MIVR function is designed to prevent input voltage drops that occur when the input power source cannot provide sufficient current. The VBUS voltage decreases to the level set by the VMIVR setting level when an overcurrent condition arises from the input power source. The default value of the VMIVR register is 4.5V. The value can be adjusted via the I<sup>2</sup>C interface, with a range from 3.9V to 5.4V in increments of 0.1V. Additionally, the device provides a MIVR tracking function that can be enabled through the VMIVR\_BAT\_TRACK register bits. When this tracking function is enabled, the MIVR will be set to the higher value between the VMIVR register setting and the VBAT+VMIVR\_BAT\_TRACK offset.

### 15.1.9 Buck Converter Power-Up

After the AICR is set, the converter is enabled, initiating the switching process. BATFET remains active unless the charger is disabled (CHG\_EN = 0) or the device enters shipping mode (BATFET\_DIS = 1).

The device integrates a synchronous PWM controller with a 1.5MHz switching frequency for high-accuracy current and voltage regulation. Additionally, the device supports PFM control to enhance efficiency under light-load conditions. The BUCK\_PFM\_DIS register bit allows users to disable PFM operation in the buck converter configuration.

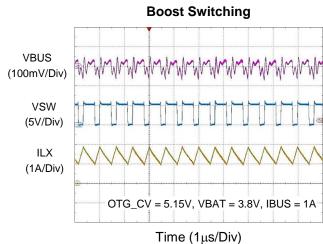

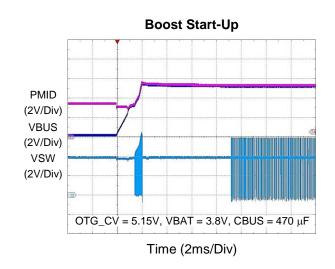

# 15.1.10 Boost Mode Operation (OTG)

The device supports OTG (On-The-Go) mode by utilizing a boost converter to facilitate power delivery from the battery to other portable devices. The maximum output current in boost mode is 1.2A, which satisfies the USB OTG requirement of 500mA.

The boost operation can be enabled by the following conditions:

- 1. VBAT must be above the VOTG LBP threshold.

- 2. VBUS must be less than VBAT + VSLEEP\_FALL value.

- 3. OTG\_EN must be set to high.

- 4. The voltage at the TS pin must be within the acceptable range, specifically VvTs\_HOT < VTS < VvTs\_COLD.

- 5. A 30ms delay must pass after setting OTG\_EN to high before the boost converter powers up.

In boost mode, the IC\_STAT register bits are updated to 1111, the VBUS output voltage is 5.15V, and the output limit current is 1.2A by default. Both the output voltage (OTG\_CV) and the output current limit (OTG\_CC) can be configured via I<sup>2</sup>C. The boost output remains active as long as VBAT stays above the Votg\_LBP threshold.

23

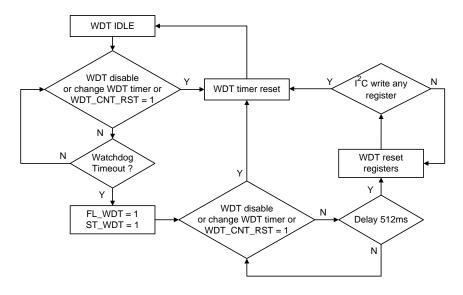

#### Watchdog Timer (WDT) 15.2

When the device is controlled by the host, most of the registers can be programmed by the host. The host must write WDT\_CNT\_RST = 1 to reset the counter before the watchdog timeout, and it can also disable the WDT function by setting the WDT bits to 00.

When the watchdog timer expires, ST WDT and FL WDT go high, and the INT pin is pulsed to interrupt the host. After a delay of 512ms, the related registers are reset to their default values (refer to Functional Register Description for details). If the device is in a watchdog timeout status, the host can write to any registers or set WDT\_CNT\_RST = 1 to reset the counter.

Figure 1. WDT Flow Chart

#### 15.3 **Power Path Management**

The device provides an automatic power path selection mechanism that enables the system power supply (VSYS) to be sourced from either VBUS, VBAT (battery), or both.

#### 15.3.1 Entering Shipping Mode (BATFET Disable)

To extend the battery life during shipping or storage, the device can disable BATFET to minimize the battery leakage current. The host can configure the BATFET\_DIS bit to disable BATFET immediately, or set the BATFET\_DIS\_DLY bit to introduce a delay tSHIP\_MODE\_ENTER before disabling the BATFET.

#### 15.3.2 Exiting Shipping Mode (BATFET Enable)

When the device is in shipping mode, one of the following methods can be used to exit shipping mode and restore power to the system:

- 1. Connect VBUS.

- 2. Set the BATFET\_DIS bit to 0.

- Set the REG\_RST bit to reset all registers to their default values.

- 4. Activate the QON pin by transitioning it from high to low for a duration exceeding tshipmode exit.

is a registered trademark of Richtek Technology Corporation. DS9471/D-04 May 2024 www.richtek.com

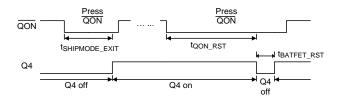

## 15.3.3 **QON** Pin Operations

The QON pin serves two functions to control BATFET.

- 1. BATFET Enable: Transitioning the  $\overline{\text{QON}}$  pin from high to low for a duration exceeding the tshipmode\_exit deglitch time threshold will turn on BATFET, allowing the device to exit shipping mode.

- 2. SYSTEM Reset: If the QON pin transitions from high to low for a duration exceeding the tQON\_RST deglitch time threshold, and if VBUS is not connected, BATFET is turned off for tBATFET\_RST. Subsequently, BATFET is re-enabled. This functionality allows the system connected to VSYS to perform a power-on reset. This feature can be deactivated by setting the QON\_RST\_EN bit to 0.

Figure 2. QON Timing

## 15.4 Battery Charging Management

The device supports a maximum charge current of 3.15A and incorporates an  $18m\Omega$  BATFET to enhance charging efficiency and reduce voltage drop during battery discharge.

## 15.4.1 Charging Cycle

When battery charging is enabled (the  $\overline{CE}$  pin is set to low and CHG\_EN = 1), the device autonomously completes a charging cycle without host controls. The default parameters for the device are detailed in  $\underline{Table\ 4}$ . Additionally, the host can modify the charging parameters via  $I^2C$ .

| Default Mode                | RT9471/D |  |

|-----------------------------|----------|--|

| Charging Voltage            | 4.2V     |  |

| Charging Current            | 2A       |  |

| Pre-Charge Current          | 150mA    |  |

| End of Charge (EOC) Current | 200mA    |  |

| Temperature Profile         | JEITA    |  |

| Fast Charge Safety Timer    | 10 Hours |  |

**Table 4. Default Charging Parameters**

A charging cycle starts with the following conditions:

- 1. The buck converter initiates operation.

- 2. Battery charging is enabled (the  $\overline{CE}$  pin is low, CHG\_EN = 1, and ICHG\_REG is not 0mA).

- 3. There are no thermal faults detected on TS.

- 4. There is no safety timer fault.

- 5. BATFET is active (BATFET\_DIS = 0).

The charger reaches the end-of-charge status when the charging current falls below the EOC current threshold, the battery voltage exceeds the recharge voltage threshold, and the device is not in AICR, MIVR, or thermal regulation.

If the battery voltage drops below the recharge threshold (threshold setting through the VRE\_CHG register bits), the device automatically initiates a new charging cycle. Once charging is complete, a new charging cycle can be started by toggling either the  $\overline{\text{CE}}$  pin or the CHG\_EN bit.

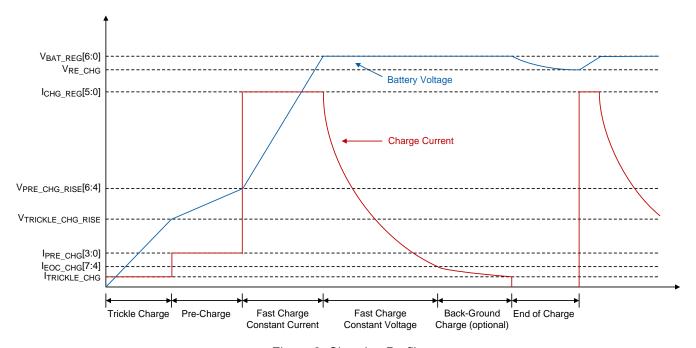

## 15.4.2 Battery Charging Profile

The device charges the battery in five statuses: trickle charge, pre-charge, constant current, constant voltage, and back-ground charge (optional).

| Current Parameter | Default Current Setting | IC_STAT |

|-------------------|-------------------------|---------|

| ITRICKLE_CHG      | 100mA                   | 0010    |

| IPRE_CHG          | 150mA                   | 0011    |

| ICHG_REG          | 2A                      | 0100    |

| IEOC_CHG          | 200mA                   | 0111    |

**Table 5. Charging Current Setting**

Figure 3. Charging Profile

## 15.4.3 End of Charge (EOC)

The charger enters the end of charge status when the battery voltage exceeds the recharge threshold and the charge current falls below IEOC\_CHG. The IEOC\_CHG can be set within a range from 50mA to 800mA in increments of 50mA. Upon reaching EOC, the BATFET is turned off with TE = 1 and BG\_CHG\_TMR = 00. Meanwhile, the buck converter continues to switch, providing power to the system. The BATFET will be re-enabled when the battery voltage drops below the recharge voltage threshold or when the device enters Battery Supply Mode during EOC.

When EOC is triggered, there are four conditions:

RICHTEK is a registered trademark of Richtek Technology Corporation.

| Table 6. E00 Status Scenario |                             |                              |                             |                                   |

|------------------------------|-----------------------------|------------------------------|-----------------------------|-----------------------------------|

|                              | TE = 1 BG_CHG_TMR (Disable) | TE = 1 BG_CHG_TMR (Counting) | TE = 1 BG_CHG_TMR (Timeout) | TE = 0<br>BG_CHG_TMR<br>(Disable) |

| ST_EOC                       | 1                           | 1                            | 1                           | 1                                 |

| ST_CHG_DONE                  | 1                           | 0                            | 1                           | 0                                 |

| ST_BG_CHG                    | 0                           | 1                            | 0                           | 0                                 |

| STAT Pin                     | High                        | High                         | High                        | Low                               |

| IC_STAT                      | 0111                        | 0110                         | 0111                        | 0101                              |

| BATFET                       | OFF                         | ON                           | OFF                         | ON                                |

Table 6. EOC Status Scenario

- 1. If the device triggers AICR, MIVR, JEITA, or thermal regulation status during charging, the actual charging current will be less than the programmed value. In this condition, the EOC function will be disabled, and the safety timer's counting rate will be halved.

- 2. Background charging can be initiated after EOC detection. To enable background charging, set both BG\_CHG\_TMR and TE = 1. When background charging is active, IC\_STAT is set to 0110, and the BATFET will turn off once the background charge timer expires.

- 3. The BG\_CHG\_TMR is reset under any of the following conditions:

- CHG\_EN is disabled and then re-enabled.

- · EOC status is triggered again.

- EOC\_RST bit is set.

- REG\_RST bit is set.

- The value of BG\_CHG\_TMR changes.

An INT pulse is sent to the host upon entering background charge mode and when the background charge timer expires.

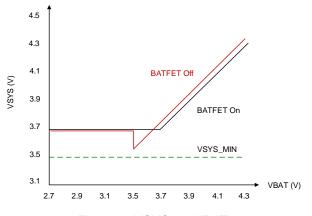

## 15.4.4 Optimized VDS on BATFET

The device incorporates a power path function featuring a BATFET that separates system from the battery. The minimum system voltage is determined by the VSYS\_MIN bits (default 3.5V).

When the battery voltage exceeds VSYS\_MIN, the BATFET is fully activated to minimize RDS(ON), thereby optimizing VDS (voltage difference between VSYS and VBAT) on the BATFET.

Figure 4. VSYS vs. VBAT

DS9471/D-04

When the BATFET is off and the battery voltage is above VSYS MIN, the system voltage is regulated to be typically 50mV higher than the battery voltage. The status register ST SYS MIN = 1 to indicate that the system is operating under the minimum system voltage regulation.

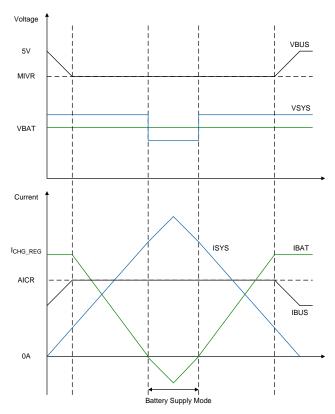

#### 15.4.5 Power Management System

To apply the maximum current and avoid overloading the power source on VBUS, the device's Power Management System continuously monitors the voltage and current of the power source. If the power source becomes overloaded, indicated by the current exceeding the AICR limit or the voltage dropping below MIVR, the device will reduce the charging current to prioritize power for the system's operations.

If the charging current is reduced to zero and the power source still triggers the AICR or MIVR conditions, VSYS begins to drop. Once VSYS falls below VBAT, the device automatically switches to battery supply mode. In this mode, the BATFET turns fully on, and the battery starts to discharge so that the system is supported from both the battery and the power source.

Figure 5. Power Management System

#### 15.4.6 **Battery Supply Mode**

When the voltage difference between VBAT and VSYS is above 50mV, the BATFET turns on, and the BATFET gate is regulated to keep VBAT-VSYS at 40mV to prevent frequent entry and exit from the battery supply mode. When the voltage of VBAT-VSYS drops below 0mV, the charger exits the battery supply mode and starts to charge the battery.

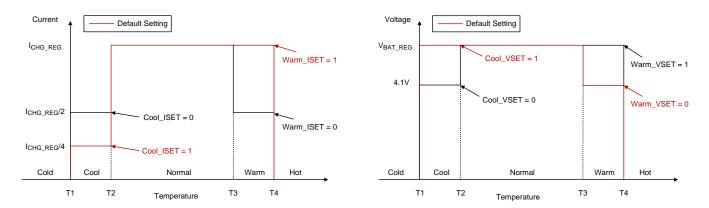

#### JEITA Protection During Charge Mode 15.4.7

The device incorporates a dedicated thermistor input for precise temperature monitoring.

To ensure battery thermal protection, the device adheres to the JEITA guidelines established in 2007.

DS9471/D-04 May 2024 www.richtek.com

is a registered trademark of Richtek Technology Corporation.

To initiate a charging cycle, the voltage on the TS pin must fall within the T1 to T4 range. The device will stop charging if the battery temperature drops below T1 (Cold) or rises above T4 (Hot) when JEITA\_COLD = 0 and JEITA\_HOT = 0

In this case, the IC\_STAT = 1000 to signal a charging fault, and an  $\overline{\text{INT}}$  will be sent to the host.

In the cool temperature range (T1 to T2), the charge current is reduced to either 50% or 25% of ICHG\_REG, as determined by JEITA\_COOL\_ISET.

In the warm temperature range (T3 to T4), the voltage setting of VBAT\_REG is lowered to 4.1V or maintained at the VBAT\_REG value, as determined by JEITA\_WARM\_VSET.

The device offers configuration options that exceed the standard JEITA requirements for added flexibility.

Within the cool temperature range (T1 to T2), the charger can set the voltage of VBAT\_REG down to 4.1V, as set by JEITA\_COOL\_VSET.

Within the warm temperature range (T3 to T4), the charge current can be reduced to 50% of ICHG\_REG, as set by JEITA\_WARM\_ISET.

Figure 6. JEITA Protect for Charging Current and Voltage

The JEITA protection feature is comprised of four sections. Herein, RHOT represents the NTC resistance at the battery over-temperature threshold, and RCOLD represents the NTC resistance at the battery under-temperature threshold. Based on RHOT and RCOLD, RTS1 and RTS2 can be calculated using equations (1) and (2).

$$R_{TS1} = V_{REGN} \times [(1/V_{T1} - 1/V_{T4})/(1/R_{COLD} - 1/R_{HOT})].....(1)$$

$$R_{TS2} = R_{TS1} \times [1/(V_{REGN} / V_{T1} - R_{T1} / R_{COLD} - 1)].....(2)$$

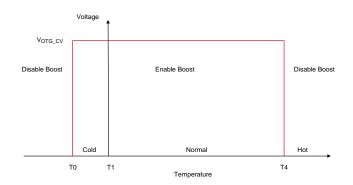

## 15.4.8 Thermal Protect During Boost Mode

To initiate boost mode to discharge from the battery, the voltage on the TS pin must fall within the T0 to T4 range. The device will stop the converter if the battery temperature falls below T0 (COLD\_OTG) or rises above T4 (HOT\_OTG). In this case, the IC\_STAT = 1000 for a charge fault, and an INT is asserted to the host.

Once the temperature re-enters the normal range, the boost mode will resume.

Figure 7. Thermal Protect During Boost Mode

## 15.4.9 Charging Safety Timer

The device incorporates a safety timer to prevent abnormal charging times due to a poor battery condition. The device can be set with the CHG\_SAFE\_TMR bits to change the timer for the fast charge cycle. When the safety timer expires, several events occur to ensure device safety. Firstly, the device stops charging process. Then, the IC\_STAT becomes 1000 to indicate a charge fault. Simultaneously, ST\_CHG\_TOUT is set to 1. Finally, an INT is asserted to the host. The safety timer can be disabled by setting CHG\_SAFE\_TMR\_EN to 0.

VBAT Safety Timer

< VPRE\_CHG 2 Hours

> VPRE\_CHG 5 Hours, 10 Hours (Default),

15 Hours, 20 Hours

**Table 7. Charging Safety Timer**

When the charger is in AICR, MIVR, JEITA cool, JEITA warm, or thermal regulation mode, the safety timer's counter clock rate will be halved. For example, if the charger is in AICR status and the timer setting is 10 hours, the actual safety timer will expire in 20 hours. The extended charge timer setting can be disabled by setting CHG\_SAFE\_TMR\_2XT to 0. The safety timer can be reset by any of the following actions:

- 1. Toggling the  $\overline{CE}$  pin.

- 2. Disabling and then enabling CHG\_EN.

- 3. Disabling and then enabling CHG\_SAFE\_TMR

- Setting REG\_RST.

# 15.4.10 MediaTek Pump Express+ (MTK, PE+)

The device can provide an input current pulse to communicate with an MTK-PE+ high voltage adapter. When the PE\_EN bit is enabled, the device can increase or decrease the adapter output voltage by setting PE10\_INC to the desired value. After enabling the PE function, the device will generate a VBUS current pattern for the MTK-PE+ adapter to automatically identify whether to increase or decrease the output voltage. After the PE pattern is completed, the PE\_EN bit will be cleared to 0, and an INT will be asserted to the host to indicate that the PE\_DONE event has occurred.

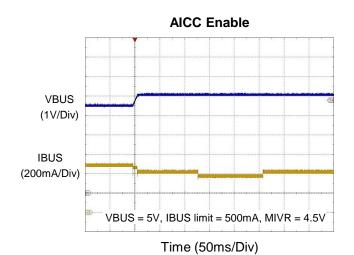

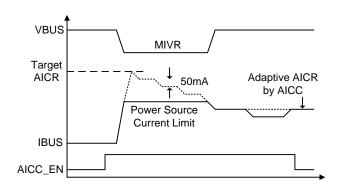

### 15.4.11 Adaptive Input Current Control (AICC)

The AICC function provides an adaptive AICR setting to prevent input voltage drops. When the input power source experiences an overcurrent and the VBUS drops to the MIVR level, setting the AICC\_EN bit to 1 will cause the device

RICHTEK is a registered trademark of Richtek Technology Corporation.

to automatically decrease the AICR level step by step until the MIVR event is exited. After the AICC process is completed, the AICC\_EN bit will be cleared to 0, and an  $\overline{\text{INT}}$  will be asserted to the host to indicate the AICC\_DONE has occurred.

Figure 8. AICC Enable

## 15.5 Status Outputs

# 15.5.1 Power Good Indicator (PG Pin and ST CHG RDY Bit)

The PG pin goes low to indicate a good power source under the following conditions:

- 1. VBUS is above the VBUS\_MIN\_RISE threshold, and IBADSRC is applied.

- 2. VBUS is above VBAT (not in sleep mode).

- 3. VBUS is below the VAC OVP threshold setting.

- 4. HZ = 0 (not in HZ mode).

- 5. The charger's temperature is under the THREG threshold setting.

- 6. VBUS Source Type Detection is completed.

## 15.5.2 Charging Status Indicator (STAT Pin)

The device indicates charging status IC\_STAT on the STAT pin. The STAT pin is an open-drain output that can be used to drive an LED. The STAT pin function can be disabled by setting STAT\_EN = 0.

IC\_STAT

Trickle, Pre, Fast charge, IEOC-charge (EOC and TE = 0)

Charge done, Back-Ground charge

High

HZ/SLEEP, VBUS ready for charge, OTG

Charge fault

Blinking at 1Hz

**Table 8. STAT Pin State**

# 15.5.3 Interrupt to Host (INT Pin)

The device reports IRQ to the host via the INT pin, which is configured as an open-drain output.

The INT pin generates a low pulse with 256µs when an IRQ event occurs. All IRQ events are masked by default.

When a fault occurs, the device triggers an  $\overline{\text{INT}}$  pulse to the host and retains the IRQ event details in registers 0x20 to 0x23. These details remain in the registers until the host reads the IRQ registers. The device will not send another  $\overline{\text{INT}}$  pulse until the host clears the IRQ events by reading the registers, unless a new event occurs.

Table 9 STATUS, FLAG, and MASK Register Map

| Name       | STAT | IRQ | MASK |

|------------|------|-----|------|

| VBUS_GD    | Υ    | Y   | Y    |

| CHG_RDY    | Υ    | Y   | Υ    |

| IEOC       | Υ    | Y   | Υ    |

| BK_CHG     | Υ    | Y   | Y    |

| CHG_DONE   | Υ    | Y   | Y    |

| RECHG      | N    | Y   | Y    |

| DETACH     | N    | Y   | Y    |

| BC12_DONE  | Y    | Y   | Y    |

| MIVR       | Y    | Y   | Y    |

| AICR       | Y    | Y   | Y    |

| CHG_THREG  | Υ    | Y   | Y    |

| CHG_BUSUV  | Υ    | Y   | Y    |

| CHG_TOUT   | Υ    | Y   | Y    |

| CHG_SYSOV  | Υ    | Y   | Y    |

| CHG_BATOV  | Υ    | Y   | Y    |

| JEITA_HOT  | Υ    | Υ   | Y    |

| JEITA_WARM | Υ    | Y   | Y    |

| JEITA_COOL | Υ    | Y   | Y    |

| JEITA_COLD | Υ    | Υ   | Y    |

| SYS_MIN    | Υ    | Y   | Υ    |

| SYS_SHORT  | N    | Y   | Υ    |

| OTP        | Υ    | Υ   | Y    |

| VAC_OV     | Υ    | Y   | Y    |

| WDT        | Υ    | Y   | Y    |

| OTG_CC     | Y    | Y   | Y    |

| OTG_LBP    | N    | Y   | Y    |

| OTG_FAULT  | N    | Υ   | Y    |

## 15.6 Protections

## 15.6.1 VBUS Overvoltage Protection in Buck Mode

If the VBUS voltage is over the VAC\_OVP setting (programmable by the VAC\_OVP bits), the device stops switching immediately and asserts an INT pulse to the host. When the VBUS overvoltage occurs, the status ST\_VAC\_OV is set to 1 and the IC\_STAT is set to 1000 to indicate a charge fault. The device resumes normal operation when the VBUS voltage drops below the VAC\_OVP threshold.

## 15.6.2 VBUS Overvoltage Protection in Boost Mode

When in boost mode, the VAC\_OVP setting is locked at 6.35V, even if the VAC\_OVP threshold is set at 10.8V or 14V. When the output voltage (VBUS) exceeds the VAC\_OVP threshold, the device stops switching immediately,

Copyright @ 2024 Richtek Technology Corporation. All rights reserved.

RICHTEK

is a registered trademark of Richtek Technology Corporation.

DS9471/D-04 May 2024 www.richtek.com

clears the OTG\_EN bit to 0, and exits boost mode. The fault (OTG\_FAULT) is set to high, and an INT pulse is asserted to the host. When the output voltage falls below VAC\_OVP\_HYS, the OTG\_EN bit can be set to 1 by the host.

#### 15.6.3 IBUS Overload Protection in Boost Mode

The device monitors the boost output voltage and current to provide VBUS short circuit protection. The device also includes built-in constant current regulation to allow OTG to adapt to various types of loads. If a short circuit is detected on VBUS, the boost will hiccup 7 times. If the boost retries are not successful, the OTG\_EN bit will be set to 0 to disable boost mode, and an INT pulse will be asserted to the host to indicate OTG\_FAULT.

#### 15.6.4 **VBUS Soft-Start**

When the boost function is enabled, the device initiates a soft-start from VBUS to avoid inrush current.

#### 15.6.5 VSYS Overvoltage Protection

The SYSOVP threshold is set at 5.2V. Once VSYS is above the SYSOVP level, the buck stops switching immediately, and an INT pulse is asserted to the host to indicate a CHG\_SYSOV fault. The device provides a 30mA current sink on VSYS to bring down the VSYS voltage.

#### 15.6.6 **VSYS Overcurrent Protection**

When the system is shorted or overloaded (IBAT > IOCP\_BATFET), the device latches off the BATFET (forcing entry into shipping mode), and an INT pulse is asserted to the host to indicate a SYS SHORT fault. Exiting shipping mode can reset the latch-off condition and turn on the BATFET.

## **Battery Overvoltage Protection**

The BAT\_OVP threshold is set at 4% above the VBAT\_REG setting. If the battery voltage exceeds this overvoltage threshold, the device immediately disables charging, and asserts an INT to the host to indicate a CHG\_BATOV event.

#### 15.6.8 **Battery Over-Discharge Protection**

If the battery is discharged below VBAT\_DPL\_FALL, the BATFET turns off to prevent over-discharge. Upon connection of VBUS, the BAFET is activated to allow battery charging.

#### 15.6.9 Over-Temperature Protection in Buck Mode

The device continuously monitors the internal junction temperature to prevent overheating. In buck mode, the thermal regulation threshold is set at 120°C (programmable by the register THREG bits). If the junction temperature rises above the thermal regulation threshold, the device reduces the charging current. During thermal regulation, the EOC function is disabled, the safety timer's counting rate is reduced by half, and an INT signal is asserted to the host to indicate CHG THREG.